Abstract

Substantial attention has been drawn over the past few years by high step-up dc-dc converters owing to their applications in a wide range. Apart from renewable energy applications, high voltage/ high pulse converters are efficiently used in water treatment applications. The converter suggested a combination of Quadratic and SEPIC converters with a diode-capacitor cell. This topology generates high-voltage repetitive pulses with a single semiconductor switch and reduced component count. The stress across the components is less than the high-gain converters reported in the literature. The topology has an extendable feature by increasing the number of diode-capacitor cells without affecting the stress. The superiority of the high pulse generating topology is validated with a similar converter in the literature. This paper discusses the nL5 simulator results for the proposed rated topology required for water treatment. A scaled-down 50 W prototype is tested for various input voltages to generate high voltage pulse, and the analytical study is validated.

Similar content being viewed by others

The necessity for water treatment is increasing due to various reasons like water pollution, climatic changes resulting from global warming, drinking water shortage, mainly due to the growing population, etc. Water treatment is crucial in protecting the terrestrial environment from contaminated water from industrial chemicals. The common methods for elimination of microbial contamination in water are chemical treatment1,2,3,4, application of intense heat5, filtration by UV6,7, electrodialysis8 and reverse osmosis process9. Conventional water treatment techniques have harmful chemical by-products during their processing. The appropriate solution to overcome the demerits of old water treatment techniques is the implementation of power electronic pulse generators, which can be used effectually for bacterial decontamination in water treatment applications. Three key water treatment techniques are involved: Electrolysis, Pulse discharging power technique and Pulse Electric field technique. The electrolysis technique used in wastewater treatment is based on the electrochemical reaction. Pulsed electric field techniques with high-voltage pulses are used to sterilize drinking water. Pulse discharge water treatment is utilized for sewage water treatment. The applications of these techniques in various water treatment sectors are illustrated in Fig. 1.

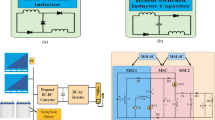

High gain conversion is generally achieved by increasing the multiplier cell stages. Topologies discussed in the literature include a modular bipolar high-voltage pulse generator capable of generating bipolar pulses with high voltage and output flexibility10,11,12,13. A two-stage high-voltage pulse generator converter topology with key features like scalability, modularity, and redundancy is used for electroporation applications is discussed14. Sequential pulse generators producing repetitive pulses were discussed as suitable for disinfection applications15. Pulsed Electric Field (PEF) method has had promising applications in several fields in the last few years. Pathogenic bacteria and other antibiotic–resistant microorganisms are treated with the high pulse of the electric field. For water treatment applications, pulsed arc discharge and underwater pulsed streamer corona discharge are the two main types of Pulsed Electric Field (PEF) treatments16,17. The effect of microorganisms and their removal by comparing the two methods is presented in17. It is also observed from the literature that the underwater pulsed streamer corona discharge requires lesser power compared to pulsed arc discharge. The application of bipolar pulses is even more effective compared to its counterpart. Even though electroporation successfully applies pulsed electric fields, permanent cell membrane damage is caused by the electric voltage of very high18,19,20. Generally, the pulse generation for water treatment based on power electronic switches can be classified into two types precisely classical and solid-state pule generation methodology. Different pulse generation methodologies are depicted in Fig. 2. The Chopper and Marx circuits generate pulses with capacitor storage in classical methods. In Magnetic Pulse Compressor (MPC), a storage capacitor and a magnetic switch is employed for pulse generation. PFL is a crucial method to generate high-power short pulses of the nanoseconds pulse width. For generating rectangular pulses with a pulse width greater than 500 ns, PFL is unsuitable; therefore, Pulse Forming Network (PFN) is used. Small and medium power pulses are generated in a dual resonant Tesla transformer circuit.

In solid-state pulse generation methodology, solid-state switches generate definite pulses. DC-DC isolated and non-isolated converters generate high-voltage pulses with single or multiple controls. This methodology can be used wherever high-voltage pulses are required in water treatment applications. Capacitor–diode voltage multipliers (CDVMs) are also used in electric pulse generators which are highly reliable, efficient, lightweight, and smaller in size19. However, they pose a risk of increasing voltage ripples of capacitors and falling output pulse frequency. Low pulsed dc voltages effectively deactivating microbes generally found diffused in water from dead animals is discussed in21,22,23. Taphylococcus aureus is deactivated with 50–80 V pulses for 5 min for 3 days21 followed by pichia rhodanensis with 400–500 V pulses22 and pseudomonas aeruginosa with 500 V pulses for 100 μs23.

An adjustable pulse magnitude, pulse width and pulse count electric pulse generator are validated with PSIM simulation for 1.5 kV to produce unipolar and bipolar pulses leading to longevity and reliability24. Apart from voltage source topology, a current source topology is made with a series-connected Bi-MOSFET switch. A repetitive pulse or single pulse is produced as desired and the current controls the voltage magnitudes of the output pulses through the inductor in every discharge cycle of the load25. A state-space model is derived for another continuous inductor current operation mode and results are validated with a 50W prototype26. A 10 kV and 1 kW prototype experimental results were presented for a solid-state pulse power modulator for producing short pulses with high switching speed using a new gate driving circuit27. The role of the pulsed electric field in the water treatment process is illustrated with a flow diagram in Fig. 3. Based on the challenges addressed in the literature28,29,30,31,32,33,34,35,36, the following topology is proposed in this paper.

In this paper, a novel high-voltage pulse generator based on Quadratic and SEPIC dc converters in combination with multiple diode-capacitor cell is proposed. The derived high pulse generator affords the following features:

-

(i)

Single switch topology

-

(ii)

Extendable feature

-

(iii)

Lesser component count.

Despite these advantages, the suggested high-pulse generator requires a high-voltage switch to chop the continuous dc voltage to a high-voltage pulse. However, this issue can be overcome by using a series-connected switch. The major contributions of the article are.

-

Proposed novel single switch topology with extendable features.

-

Reliability analysis of proposed topology is performed by considering annual mission profile of the water treatment plant and compared with similar topology in the literature.

-

With the process parameters, water sample is tested before and after treatment and the presence of microbes are analyzed.

-

Sample is tested with 360 V and 5000 V to observe the significance of the magnitude of pulsed voltage.

This paper is organized as follows: Following the introduction, a description of the proposed topology is presented in Section "Proposed repetitive high pulse generating topology". The design of the derived topology with the voltage stress across the components is illustrated in Section "Design and component analysis". The superiority of the suggested converter is highlighted by comparing it with a similar topology in the literature in Section "Performance analysis". Simulation results are presented in Section "Comparative Study" by using nL5 software. The scaled-down prototype is tested and the results are depicted in Section "Simulation results". Finally, the article is concluded in the last section.

Proposed repetitive high pulse generating topology

This section performs the derivation, operating principle, and steady-state analysis of the topology. The operating principle is discussed with a single diode-capacitor cell for simplicity.

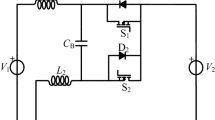

High pulse modified SEPIC-quadratic boost DC converter

The schematic circuit of the HPSQB converter is presented in Fig. 4. The converter's gain increases by proportionately increasing the voltage multiplier stages.

Operating principle

Based on the conducting and non-conducting conditions of the semiconductor switch, the working of the converter is divided into two modes.

Mode-I: Fig. 5a depicts the equivalent circuit of the proposed topology in the ON mode of the switch. In Fig. 5a, the Mode-I is from 0 to DTs, representing the duty cycle as ‘D’ and the switching period as Ts. The switch is in ‘ON’ condition in this mode. During this mode, the input supply, Vg, charges the inductor ‘L1’ and forms a closed circuit with diode D2 while diode D1 is not conducting. Inductor L2 is charged from the capacitor C1. The non-conducting state of the diodes D3 and D5 and conducting state of diode D4 connects the capacitors C2 and C3 in series and capacitors C4 and C5 in series. The series combination of C2, C3 and C4, C5 branches falls in parallel with each other and forms a closed circuit. The load at this condition is fed from the output capacitor ‘CO’. Diodes D1, D3, D5, and DO are in a non-conducting state during this mode. The key waveforms of the HPSQB converter are also depicted in Fig. 6. Vpulse is the voltage obtained after the high voltage switch which is used to chop the output voltage of the converter.

Mode-II: As given in Fig. 5b. The Mode-II is from DTs to Ts. In this mode, the inductors L1 and L2 discharges to the load along with the input supply Vg. Diodes D2 and D4 are in blocking state and diodes D2, D3, D5 and DO moves into conduction state. The output voltage in this mode is equal to VC5 + VC4–VC3.

Steady-state analysis in CCM

The voltage gain of the proposed converter is derived mathematically by applying the magnetic flux principle on charging and discharging state of the inductor. Considering the internal resistance of the proposed converter as zero or negligible. Table 1 presents the voltage expression of the inductor in ON and OFF modes. The derivation of the voltage gain is derived as follows:

On application of the volt-sec balance principle, the voltage gain of the proposed converter is thus derived as,

The generalized expression of the converter proposed with ‘M’ number of multiplier stages is given as,

The current gain of the converter proposed is obtained as,

The variation of voltage gain, Gv with the multiplier cell, M is presented in Fig. 7 for M = 1 to 5.

Design and component analysis

This section elaborates on the steps to design the proposed high-pulse generator. Since the required pulse for the water treatment application is observed to be in kV. Accordingly, the passive components of the converter are acquired. The stress across the topology components is also analyzed and presented to highlight the advantage of the derived topology.

Design of passive components

The design expression of the inductors (L1, L2 and L3) in the proposed topology (number of multiplier cell, M = 1) is

The capacitor (C1, C2, C3, C4, C5 and CO) formula

Stress across the components

The voltage and current stress of the passive and semiconductor components are derived from the steady-state analysis for designing the converter. Table 2 illustrates the voltage stress across the semiconductor devices for a different number of multiplier cells, M. From this Table, it is observed that the stress across the components is independent of the number of multiplier cells. The increase in the M number of multiplier cells does not affect the stress value.

Stress across the capacitors

Pulsed electric field application mainly depends on charging and discharging the capacitors in the converter. The voltage stress across the capacitors C1, C2, C3, C4, C5 and CO is

Current stress of the components

The RMS current through the inductor is given as

The RMS current through the switch, S1 is given as

Performance analysis

Efficiency analysis

Figure 8 presents the equivalent circuit of the HPSQB converter for efficiency analysis. For efficiency calculation of the proposed converter, the parasitic resistance of components is considered as shown in the equivalent circuit and the equations as follows:

The power rating of HPSQB converter is considered as 500 W. The input and output voltage are chosen as 300 V and 35.1 kV respectively as mentioned in simulation section.

Table 3 presents the specification considered for the efficiency study of the HPSQB converter. With (20–25), the losses across the converter components are obtained and the efficiency analysis is performed. Efficiency analysis is performed for the specification, as shown in Table 3, similar to the simulation study. The average and RMS current few diodes in the topology are given in Table 4, along with the losses in the components. Similarly, the capacitor loss is also performed and the total loss is observed to be 67 W. With this loss, the efficiency of the HPSQB topology is calculated as 87%.

Sensitivity analysis

Sensitivity analysis is recommended in designing a novel converter because it portrays the sensitivity of voltage gain for the change in D, duty cycle, and RL, the internal resistance of the inductor. The efficiency of the topology is

The voltage conversion ratio of the HPSQB topology with the RL of inductor is

The voltage conversion ratio is simplified by considering same internal resistance for all the inductor (RL1 = RL2 = RL3)

Sensitivity analysis of voltage gain is accomplished by differentiating (29) with respect to D. After mathematical manipulation, the final yielded equation is

Similarly, the sensitivity of the output voltage with respect to D is

The sensitivity analysis of voltage gain and output voltage for duty cycle D is performed and depicted in Fig. 9a,b. It is depicted in Fig. 9a that the variation of the non-ideal voltage gain of the HPSQB converter for a higher duty cycle is significant for the internal resistance of the inductor, RL. Similarly, the variation of ideal voltage gain for duty cycle D is predominant for the duty cycle greater than 0.5, which is illustrated in Fig. 9b.

Reliability analysis

This section determines the failure rate based on the equations given in Fig. 10a. The military handbook calcifies the failure rate in many applications to determine reliability. Accurate reliability predictions are essential in applications that depend on various parameters, such as the physical and operating characteristics of the converter and its environment. The reliability analysis of HPSQB topology determined that the semiconductor devices are failure prone compared to the passive components. Therefore, the failure rate of the switch and diodes are discussed and depicted in Fig. 10b. The failure rate of the switch is estimated to be greater than the diodes in the converter circuit considered.

The reliability analysis is extended by considering the annual mission profile of the water treatment plant in Chennai, Tamil Nadu and it is presented in Table 5. This analysis is validated by comparing the MTTF computation of Proposed HPSQB converter with the pulsed voltage converter proposed in19. Table 6 depicts the comparison performed in the MTTF calculation of HPSQB converter with the converter in19. From this comparative study, it is observed that HPSQB converter’s reliability is better compared to the topology presented in19.

Comparative Study

This section compares the topology with similar topologies in the literature and proves its superiority. First, the derived topology is compared with the voltage multiplier-based topology suggested for water treatment applications19. Figure 11a–d presents the comparison made on the derived topology with the topology in19. In Fig. 11a,b, the duty cycle is kept constant at 0.5 and the number of multiplier cells, M and the total component count is analyzed for various values of Gain, Gv. The comparative Table 7 shows that the proposed converter uses lesser components to achieve the same voltage gain as compared to the converter in19. In Fig. 11c, the total component count is kept constant at 16 and the duty cycle is compared for various values of Gain, Gv.

It is noted that the suggested topology requires a low duty cycle, D, to achieve the required voltage gain compared to the converter chosen for comparison19, which ultimately reduces the conduction losses of the semiconductor losses and increases the efficiency of the converter. Next, the required input voltage to achieve the desired output voltage is compared by setting the duty cycle to 0.5 and fixing the total component count as 16. This study depicts in Fig. 11d that the derived topology requires lesser input voltage, Vg, compared to the topology in19 for various output voltages, Vo. Since the losses across the power semiconductor devices are more compared to the passive component’s losses, the HPSQB topology offers better efficiency compared to19. It is observed that to achieve the voltage gain of 10, the number of semiconductor devices required for19 is 10 whereas the proposed topology is 7.

Finally, the comparative study is extended by choosing similar topologies with diode-capacitor cell and extendable capability. Figure 11e illustrates the analysis carried out and it shows that the derived topology exhibits high gain compared to other topologies. The gain expression and the component breakup are depicted in Table 8. Furthermore, topologies in literature are extended to derive the high voltage pulses in bipolar mode30. This bipolar pulse generation is extended as a future scope with the suggested topology.

Simulation results

The proposed topology is simulated with a 500 W power rating for generating a high voltage pulse of 5 kV. The specification of the derived topology is depicted in Table 9. The load resistance for the simulation study is obtained based on the dimension considered for analysis. The area of the plate and the distance between the plates are chosen as 1 cm and 1 cm, respectively. Considering the conductivity of water as 20 µs/cm, the equivalent resistance of the water sample is calculated as 50 kΩ. Figure 12a–e presents the simulation result obtained from the nL5 simulator.

Figure 12a depicts the output and switch voltage before the pulse forming unit for 300 V input voltage. The voltage stress across the switch is validated with the analytical study, Vsw = Vg/(1–D)2 = 1.9 kV. Similarly, the output voltage for M = 1 and D = 0.5 is (2 + D)/(1–D)2 = 5.1 kV. The diode voltage is obtained and illustrated in Fig. 12b. The voltage across diode D2 is Vg(1–D) = 0.8 kV. The voltage across diodes D3 and D4 is Vg/(1–D)2 = 1.9 kV, which is presented in Fig. 12b,c. The capacitor voltage is presented in Fig. 12d. Finally, the output high pulse is obtained after incorporating pulse forming unit. The acquired high voltage pulse of 5 kV is depicted in Fig. 12e. The switching frequency of the switch added in pulse forming unit is 500 Hz and the duty cycle is 10%. This is validated in Fig. 12e with the pulse width of 20 µs and the time period of 2 ms. The diode voltage is obtained and illustrated in Fig. 12b. The voltage across diode D2 is Vg(1–D) = 0.8 kV. The Voltage across diodes D3 and D4 is Vg/(1–D)2 = 1.9 kV which are presented in Fig. 12b,c. The capacitor voltage is presented in Fig. 12d. Finally, the output high pulse is obtained after incorporating pulse forming unit. The acquired high voltage pulse of 5 kV is depicted in Fig. 12e. The switching frequency of the switch added in pulse forming unit is 500 Hz and the duty cycle is 10%. This is validated in Fig. 12e with the pulse width of 20 µs and the time period of 2 ms.

Experimental results

The proposed converter is tested for 50 W power rating to validate the theoretical analysis carried out. The specification of the topology is presented in Table 10. The experimental study is scaled down to 50 W, 300 V for high pulse generation. The photograph of the setup tested is presented in Fig. 13a. The results obtained for the validation are presented in Fig. 13a–m. The input voltage varies from 12 to 36 V to obtain 120 V to 360 V results. The input voltage of 12 V, 24 V and 36 V is given to the converter, which is depicted in Fig. 13c,d. The duty cycle is kept constant for 0.5 and is observed in Fig. 13d. The corresponding high pulse generated from the inputs (12 V–36 V) is presented in Fig. 13e–g. The high voltage pulses of 120 V, 240 V and 360 V are presented in Fig. 13e–g, respectively. These output voltages are much suitable for treatment of microbes discussed in21,22,23. The capacitor C5 voltage (VC5) for the input 36 V is presented in Fig. 13h. It validates the steady-state analysis's theoretical result, which represents VC5 = 2Vg/(1–D)2. For 0.5 duty cycle and 36 V input, the capacitor voltage is 288 V which is justified in Fig. 13g. The capacitor C2 and C3 voltage (VC2 and VC3) is Vg/(1–D)2. This is validated for 24 V input voltage, and the result is presented in Fig. 13i. The voltage stress across the single switch in the suggested topology is observed for the input voltage of 36 V. The theoretical formula for the switch voltage stress is Vg/(1–D)2, which is validated in Fig. 13j. The inductor L2 voltage is presented in Fig. 13k to validate the volt-sec balance principle applied to the topology. Finally, the diode D1-D4 voltages are observed and presented in Fig. 13l–m.

Test results (a) Photograph of the setup tested (b) Photograph of the converter (c) 20 V/div-Input voltage, Vg (d) 10 V/div-Input voltage, Vg and 10 V/div-Gate pulse, Vgate (e), (f) and (g) 50 V/div-Output voltage, Vo (h) 100 V/div-Capacitor voltage, VC5 (i) 50 V/div-Capacitor voltage, VC2 and VC3 (j) 50 V/div-Switch voltage, VSW (k) 50 V/div- Inductor voltage, VL2 (l) 50 V/div-Diode voltage, VD1 and VD2 (m) 50 V/div-Diode voltage, VD3 and VD4.

From the above sections, it is noted that the simulation results are obtained for 5 kV output voltage and hardware results are worked for 360 V output voltage. To validate the significance of these magnitude of voltage in water treatment, we planned to take water sample from our kitchen which is supplied from the municipality and decided to go for testing. The specification of the pulsed voltage considered for testing is given in Table 11. Raw water sample and the water samples subjected to 360 V and 5 kV in pulsed electric field chamber are tested in Indian analytical testing Lab, Bangalore. Finally, the obtained result from the lab before and after treatment is presented in Table 12. From the results, it is observed that all the microbes are absent after the treatment with 5 kV. With 360 V output voltage, the Coliform Bacteria is reduced from 10 cfu/gm to 2 cfu/gm whereas other microbes are completely absent.

Conclusion

This paper validates the performance of high voltage pulse generating topology derived from quadratic and modified SEPIC converter with voltage multiplier cells for water treatment applications. A wide-ranging analysis of the operating principle and design of the HPSQB converter is conducted. The steady-state performance of the topology is mathematically proven with the test results. The derived topology generates a rectangular unipolar pulse with flexibility in the variation of pulse duration and amplitude. The proposed HPSQB converter has unique features such as (i) high gain is achieved with the lesser component count, (ii) it can be integrated into low voltage input supply even for domestic applications, (iii) more efficient and reliable, (iv) voltage stress across the power semiconductor devices is less. The comparative study indicates that the HPSQB converter requires a lesser component to achieve high voltage gain compared to similar topologies in the literature. The derived topology is extendable and flexible, where the desired gain of the converter is achieved by adjusting the number of multiplier cells, M. A scaled-down prototype of 50 W, 0.36 kV is tested to validate the analytical studies. Both experimental and simulation studies analyze the generation of the unipolar pulse from the pulse-forming unit. The obtained test results exhibit excellent accordance with theoretical and simulation analysis.

Data availability

The datasets used and/or analysed during the current study available from the corresponding author on reasonable request.

Abbreviations

- GV :

-

Voltage gain

- GI :

-

Current gain

- M:

-

Number of Multiplier cell

- CDVM:

-

Capacitor–diode voltage multiplier

- PEF:

-

Pulsed Electric Field

- PFN:

-

Pulse Forming Network

- D:

-

Duty Cycle

- Vg:

-

Input voltage

- Vo:

-

Output voltage

- VGate :

-

Gate pulse

- VC :

-

Capacitor voltage

- VL :

-

Inductor voltage

- RL :

-

Internal resistance of the inductor

- RO :

-

Load resistance

- CCM:

-

Continuous conduction mode

- HPSQB:

-

High pulse SEPIC–Quadratic Boost

References

Bergeron, S., Raj, B., Nathaniel, R., Corbin, A. & LaFleur, G. Presence of antibiotic resistance genes in raw source water of a drinking water treatment plant in a rural community of USA. Int. Biodeterior. Biodegrad. 124, 3–9 (2017).

Escobar-Hoyos, L. F. et al. Genotoxic and clastogenic effects of monohaloacetic acid drinking water disinfection by-products in primary humanm lymphocytes. Water Res. 47(10), 3282–3290 (2013).

Gorito, A. M., Ribeiro, A. R., Gomes, C. R., Almeida, C. M. R. & Silva, A. M. T. Constructed wetland microcosms for the removal of organic micropollutants from freshwater aquaculture effluents. Sci. Total Environ. 10(644), 1171–1180 (2018).

Yuan, Q. B., Guo, M. T. & Yang, J. Fate of antibiotic resistant bacteria and genes during wastewater chlorination: Implication for antibiotic resistance control. PLoS One 10(3), e0119403 (2015).

Cao, Y., Æsay, V. & Liang, Q. Green ballast water treatment utilizing waste heat recovery, OCEANS 2016 - Shanghai, pp. 1–7 (2016).

Rizzo, L. et al. Effect of solar simulated N-doped TiO2 photocatalysis on the inactivation and antibiotic resistance of an E. coli strain in biologically treated urban wastewater. Appl. Catal. B: Environ. 144, 369–378 (2014).

Saien, J., Osali, M. & Soleymani, A. R. UV/persulfate and UV/hydrogen peroxide processes for the treatment of salicylic acid: Effect ofoperating parameters, kinetic, and energy consumption. Desalin. WaterTreat. 56(11), 3087–095 (2015).

Abhishek, L., Karthick, R. A., Kumar, K. D. & Sivakumar, G. Efficient water treatment using smart materials. Int. Conf. Smart Struct. Syst. 2014, 94–99 (2014).

Tiwari, J., Singh, A. K., Yadav, A., & Jha, R. K. Sustainable power production and purification of water. In 2014 International Conference on Advances in Computing, Communications and Informatics (ICACCI) pp. 2258–2263 (2014).

Barcelon, L., Landicho, J., Lim, C., Tampis, D., Magwili, G. & Garcia, R. Implementation of multi-module high voltagepulse generator based on DC-DC boost converter and capacitor-diode voltage multipliers for elimination of Escherichia coli O157:H7 inwater. AIP Conference Proceedings. 2045. (2018)

Malviya, D. & Veerachary, M. A boost converter-based high-voltage pulsed-power supply. IEEE Trans. IndustryAppl. 56(5), 5222–5233 (2020).

Elserougi, A., Massoud, A. & Ahmed, S. Multimodule boost-converter-based pulse generators: Design and operation. IEEETrans. Plasma Sci. 48(1), 219–227 (2020).

Navamani, D., Krishnasamy, V. & Jegatheesan, R. Non-isolated high gain DC-DC converter by quadraticboost converter and voltage multiplier cell. Ain Shams Eng. J. https://doi.org/10.1016/j.asej.2016.09.007 (2016).

Delshad, M. R., Rezanejad, M. & Sheikholeslami, A. A new modular bipolar high-voltage pulse generator. IEEE Trans. Ind. Electron. 64(2), 1195–1203 (2017).

Elgenedy, M. A., Massoud, A. M., Ahmed, S., Williams, B. W. & High-Gain, A. High-voltage pulse generator using sequentially chargedmodular multilevel converter submodules, for water disinfection applications. IEEE J. Emerg. Sel. Topics Power Electron. 6(3), 1394–1406 (2018).

Dang, T. H., Denat, A., Lesaint, O. & Teissedre, G. Pulsed electrical discharges in water for removal of organic pollutants: A comparative study. Eur. Phys. J. Appl. Phys. 47(2), 1–7 (2009).

Yang, Y. Plasma discharge in water and its application for industrial cooling water treatment, PhD Thesis, Drexel University, (2011).

Elserougi, A., Ahmed, S., & Massoud, A. High-voltage pulse generator based on capacitor-diode voltage multiplier centrally fed from dc-dc boost converter. In 8th IET International Conference on Power Electronics, Machines and Drives (PEMD 2016), Glasgow, UK, pp. 1–4 (2016).

Elserougi, A., Ahmed, S., Massoud, A. High voltage pulse generator based on DC-to-DC boost converter with capacitor-diode voltage multipliers for bacterial decontamination, In IECON 2015 - 41st Annual Conference of the IEEE Industrial Electronics Society, pp. 000322–000326 (2015).

Elserougi, A., Abdel-Khalik, A. S., Ahmed, S., & Massoud, A. M. AC-powered multi-module high-voltage pusle-generator with sinusoidalinput current for water treatment via underwater pulsed arc discharge. In 2017 11th IEEE International Conference on Compatibility, PowerElectronics and Power Engineering (CPE-POWERENG), Cadiz, Spain, pp. 163–168 (2017).

Tirono, M., Hananto, F. S. & Abtokhi, A. Pulse voltage electrical stimulation for bacterial inactivation and wound healing in mice with diabetes. Avicenna J. Med. Biotechnol. 14(1), 95–101. https://doi.org/10.18502/ajmb.v14i1.8175 (2022).

Zhu, N. et al. Inactivation of Pichia rhodanensis in relation to membrane and intracellular compounds due to microchip pulsed electric field (MPEF) treatment. PLoS One 13(6), e0198467. https://doi.org/10.1371/journal.pone.0198467.PMID:29939985;PMCID:PMC6016922 (2018).

Wu, M. et al. High-voltage, pulsed electric fields eliminate Pseudomonas aeruginosa stable infection in a mouse burn model. Adv. Wound Care (New Rochelle) 10(9), 477–489. https://doi.org/10.1089/wound.2019.1147 (2021).

Malviya, D., & Veerachary, M. A novel boost converter based high-voltage pulsed-power supply. In 2019 IEEE international conference on sustainable energy technologies and systems (ICSETS), Bhubaneswar, India, pp. 353–358 (2019).

Nami, A., Sakamoto, T., Akiyama, M., & Akiyama, H. Development of a boost converter topology for a high repetition pulsed power generator. In 2011 IEEE Pulsed Power Conference, Chicago, IL, USA, pp. 1336–1341 (2011)

Veerachary, M. Design and analysis of a new quadratic boost converter. In 2017 National Power Electronics Conference (NPEC), Pune, India, pp. 307–313 (2017)

Yu, C. H., Jang, S. R., Kim, H. S., Bae, J. S., & Kim, S. Pulse Generator with fast switching speed and short pulse width based on semiconductor switches for wide applications. In IECON 2018-44th Annual Conference of the IEEE Industrial Electronics Society. IEEE, pp. 1418–1423. doi: https://doi.org/10.1109/IECON.2018.8592688 (2018).

Babaei, E., Mashinchi Maheri, H., Sabahi, M. & Hosseini, S. H. Extendable nonisolated high gain DC–DC converter based on active–passive inductor cells. IEEE Trans. Ind. Electron. 65(12), 9478–9487 (2018).

Shanthi, T., Prabha, S. U. & Sundaramoorthy, K. Non-isolated n-stage high step-up DC-DC converter for low voltage DC source integration. IEEE Trans. Energy Convers. 36(3), 1625–1634 (2021).

Elserougi, A., Massoud, A. M., Ibrahim, A. M. & Ahmed, S. A high voltage pulse-generator based on DC-to-DC converters and capacitor-diode voltage multipliers for water treatment applications. IEEE Trans. Dielectr. Electr. Insulation 22(6), 3290–3298. https://doi.org/10.1109/TDEI.2015.005376 (2015).

Abadi, M. R. Q. R., Marzebali, M. H., Abolghasemi, V. & Anisi, M. H. High-voltage pulse generators for electroporation applications: A systematic review. IEEE Access 10, 64933–64951 (2022).

Gu, Y., Zhang, C., Bian, W., Wu, S. & Xu, Z. A novel modular pulse generator with high voltage gain and reduced number of capacitors. IEEE Trans. Plasma Sci. 50(2), 394–400 (2022).

Sumathy, P. et al. PV powered high voltage pulse converter with switching cells for food processing application. Energies 16, 1010 (2023).

Lavanya, A., Divya Navamani, J., Nihal, A., Narain, A., & Aashi. Novel High Voltage Pulse Generator Structure for Water Treatment Applications. https://doi.org/10.1007/978-981-19-7728-2_8. (2023).

Koç, Y., Birbir, Y. & Bodur, H. Non-isolated high step-up DC/DC converters—An overview. Alex. Eng. J. 61, 1091–1132 (2021).

Li, Z., Liu, H., Jiang, S., Guo, L. & Rao, J. A high-current all solid-state pulse generator based on Marx structure. IEEE Trans. Plasma Sci. 48(10), 3629–3636 (2020).

Rahimi, T., Ding, L., Gholizadeh, H., Shahrivar, R. S. & Faraji, R. An ultrahigh step-up DC–DC converter based on the boost, Luo, and voltage doubler structure: Mathematical expression, simulation, and experimental, IEEE. Access 9, 132011–132024 (2021).

Subhani, N. et al. An improved non-isolated quadratic DC-DC boost converter with ultra high gain ability. IEEE Access 11, 11350–11363 (2023).

Acknowledgements

This article has been produced with the financial support of the European Union under the REFRESH – Research Excellence For Region Sustainability and High-tech Industries project number CZ.10.03.01/00/22_003/0000048 via the Operational Programme Just Transition and paper was supported by the following project TN02000025 National Centre for Energy II.

Author information

Authors and Affiliations

Contributions

S.P., D.N.J., J.S.M.A., L.A.: Conceptualization, Methodology, Software, Visualization, Investigation, Writing- Original draft preparation. P.V.: Data curation, Validation, Supervision, Resources, Writing—Review & Editing. M.B., L.P. and S.A.D.M.: Project administration, Supervision, Resources, Writing—Review & Editing.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher's note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Sumathy, P., Navamani, J.D., Mohamed Ali, J.S. et al. Extendable high gain low current/high pulse modified quadratic–SEPIC converter for water treatment applications. Sci Rep 14, 4899 (2024). https://doi.org/10.1038/s41598-024-55708-z

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-024-55708-z

Keywords

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.