Abstract

In this study, we perform simulations to demonstrate neural oscillations in a single silicon nanowire neuron device comprising a gated p–n–p–n diode structure with no external bias lines. The neuron device emulates a biological neuron using interlinked positive and negative feedback loops, enabling neural oscillations with a high firing frequency of ~ 8 MHz and a low energy consumption of ~ 4.5 × 10−15 J. The neuron device provides a high integration density and low energy consumption for neuromorphic hardware. The periodic and aperiodic patterns of the neural oscillations depend on the amplitudes of the analog and digital input signals. Furthermore, the device characteristics, energy band diagram, and leaky integrate-and-fire operation of the neuron device are discussed.

Similar content being viewed by others

Introduction

Neuromorphic computation inspired by human brain architecture has great potential to overcome technical challenges in centralized and sequential computation based on the von Neumann architecture1,2,3. The von Neumann architecture requires intrinsically separate physical units for computing (a central processing unit) and memory (static and dynamic random access memory), necessitating data to be carried back and forth between them through bus lines4. Busy bus lines cause a bottleneck in data transfer, resulting in a significant decrease in computing speed and a substantial increase in power consumption4. In contrast, biological neurons perform parallel, distributed, and event-driven computations, enabling energy-efficient operation5. Hence, neuromorphic computing aims to emulate the data processing paradigm found in the topology of the biological brain which can pave the way for massively parallel information processing with extremely low power consumption6,7.

In neuromorphic computation driven by spiking neural networks, an artificial neuron is an integral component that interlinks synapses, thus promoting fast and energy-efficient information processing. Emulation of neuron information transfer in biological signaling systems requires positive and negative feedback loops as common regulatory elements8,9,10. However, most artificial neurons demand dozens of transistors to emulate biological neuron operation, in turn, greatly sacrificing the advances in integration density and power consumption4,11,12,13. To improve the integration capabilities, diverse neuron devices and circuits have been widely researched: NPN devices with double gates on a silicon-on-insulator (SOI)14, feedback field-effect transistors (FBFETs)15,16,17, skyrmion devices based on magnetic tunnel junction18, resistive random access memory (ReRAM)19, conductive bridge random access memory (CBRAM)20, ferroelectric field-effect transistors (FeFET)21,22 and phase-change devices23. However, these neuron devices and circuits require numerous component transistors and consume considerable energy to operate in addition to external bias voltages necessary for tuning firing voltages. Moreover, the skyrmion is incompatible with CMOS technology, and the phase-change devices have reliability issues due to their harsh operating conditions24. Such devices also consume standby power constantly in the form of external bias voltages while anticipating signal application. Therefore, a single artificial neuron device without consistent power consumption is much more desirable as it can resolve both integration density and power consumption issues. In this paper, we propose a single silicon nanowire neuron device with no external bias voltage capable of normally-off integrate-and-fire operation technology, which achieves zero standby power.

Methods

Device structure and simulation

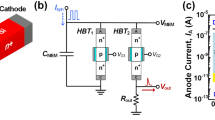

Figure 1a, b show, respectively, a schematic and cross-sectional view of a single silicon nanowire neuron device with a gated p-n-p-n diode structure. The dimensional parameters are channel length (LCH), gated channel length (LG), non-gated channel length (LNG), channel diameter (DSi), and gate oxide thickness (TOX) with values 50, 25, 25, 10, and 2 nm, respectively. The doping concentrations of the p-type drain, n-type non-gated channel, and n-type source regions were 5 × 1019 cm−3, and the gated channel region was lightly p-type doped (2 × 1015 cm−3). The device characteristics, energy band diagrams, and leaky integrate-and-fire (LIF) operations were investigated using a commercial TCAD simulation software (Synopsys Sentaurus, version O-2018.06-SP1)25. Fundamental device models were included in our TCAD simulations, including Fermi statistics model, bandgap narrowing model, carrier-carrier scattering, Shockey–Read–Hall recombination, and Auger recombination. Moreover, density gradient quantum potential model was used to treat the quantum effect occurring in ultrathin silicon nanowires25.

The single silicon nanowire neuron device operates as a two-terminal device with connected gate and drain terminals to accelerate the function of neural oscillations via interlinked positive and negative feedback loops. The IDS–VDS output characteristics from the simulation are shown in Fig. 1c. As the connected gate and drain voltage (input voltage) is swept forward from 0.00 to 1.50 V, the formation of a positive feedback loop triggers an abrupt increase in the drain current at 1.14 V. During the reverse bias sweep, the generation of a negative feedback loop leads to an abrupt decrease in the drain current at 0.57 V. In our neuron device, the positive and negative feedback loops generate neural oscillations, with the former causing a latch-up phenomenon, while the latter, a latch-down phenomenon. In the next section, we discuss the device characteristics and operating principles of this neuron device. Further, we analyze in detail the LIF operations of the interlinked positive and negative feedback loops occurring in the device.

Result and discussion

Device characteristics and operating principle

The fundamental operation of a single silicon nanowire neuron device is based on positive and negative feedback loops in the gated p-n-p-n diode structure. Figure 2 shows the energy band diagrams and recombination rates of the neuron device; these are associated with the IDS–VDS output characteristics (Fig. 1c). The input voltage (VIN) ranging from 0.00 to 1.00 V was applied to the connected gate and drain terminals for a leaky integration in the neuron device before triggering the positive feedback loop. The effect of the input voltage is divided into the gate voltage and drain voltage functions regarding the positive and negative feedback loops in the gated p-n-p-n diode structure. First, as the drain voltage increases in the gated p-n-p-n diode structure, both the drain and non-gated channel junction and the gated channel and source junction are forward biased, whereas the junction of non-gated and gated channels is more significantly reverse biased. At the drain and non-gated channel junction (the gated channel and source junction), electron–hole recombination increases from 1.3 × 1019 (9.4 × 1018) to 3.2 × 1019 (1.5 × 1019), lowering the height of the junction potential barrier. At the junction of non-gated and gated channels, electron–hole generation is increased by extension (≈ 4 nm) of the depletion region, as depicted in the bottom panel of Fig. 2a. The generated charge carriers accumulate in the potential wells of the non-gated and gated channels—electrons in the conduction band of the former, holes in the valence band of the latter (top panel of Fig. 2a). Second, as the gate voltage increases from 0.00 to 1.00 V in the gated p-n-p-n diode structure, the conduction band (the valence band) edge in the gated channel region is lowered from 1.03 to 0.37 eV (from − 0.02 to − 0.69 eV), allowing the injection of electrons into the potential well in the conduction band of the non-gated channel region26. The potential barrier modulation by the input voltage stimulates the electron injection from the source to the channel region; the injected electrons accumulate in the potential well in the non-gated channel region. The electron accumulation lowers the height of the potential barrier, which allows holes to be injected. The injected holes accumulate and encourage the injection of more electrons. The resulting accumulation of charge carriers induced by the input voltage emulate the leaky integration of biological systems.

Energy band diagrams and recombination rates of the single silicon nanowire neuron device during its integrate-and-fire and reset responses: (a) leaky integration states at VIN = 0.50, 0.70, and 1.00 V during forward sweep, (b) firing state at VIN = 1.15 V, and (c) reset states at VIN = 0.80, 0.70, and 0.50 V during reverse sweep.

As the input voltage exceeds the threshold voltage of 1.14 V, the lowering of the potential barrier by the accumulated charge carriers activates the positive feedback loop. The energy band diagram at VIN = 1.15 V (top panel of Fig. 2b) corresponds to the firing state. The positive feedback loop eliminates the potential well, and thereby, electron–hole recombination occurs in the entire region of the gated p-n-p-n diode structure (bottom panel of Fig. 2b). After the neuron device fires, the input voltage decreases from 1.15 to 0.70 V; nevertheless, the positive feedback loop persists until the negative feedback loop is initiated. The potential barrier modulation by the reduction of the input voltage stimulates the electron–hole recombination at the drain and non-gated junction, non-gated channel and gated channel junction, and gated-channel and source junction; the electron–hole recombination gradually regenerates a potential barrier in each junction, which impedes electrons to be injected. The charge carrier recombination increases the potential barrier height, blocking the electron injection. The mutual interaction between the potential barriers and charge carriers produces the negative feedback loop, which leads to the neuron device in the latch-down state. As the input voltage drops below the latch-down voltage, the potential barrier is regenerated by the negative feedback loop, as shown in the top panel of Fig. 2c. In contrast to the positive feedback loop which is generated by accumulated charge carriers in the potential well, the negative feedback loop removes the accumulated charge carriers, which is caused by electron–hole recombination at the junctions of non-gated and gated channels, as shown in the bottom panel of Fig. 2c.

Neural oscillation of single silicon nanowire neuron device

The dynamics of neural oscillation in a single silicon nanowire neuron device using interlinked positive and negative feedback loops were investigated by applying analog and digital input signals. Figure 3a shows a neuromorphic block diagram composed of a sensory system, synaptic devices, and a single silicon nanowire neuron device. The sensory system perceives an external stimulus and transmits analog AC and DC signals into the neuron device. Subsequently, the neuron device fires spike voltages (VSpike) toward the synapse devices. The spike and reset mechanisms of the neuron device enabling information transfer for synapse devices are explained using an equivalent circuit. The equivalent circuit of our neuron device consists of coupled bipolar junction transistors (BJTs) and an n-channel metal-oxide- semiconductor field-effect transistor (MOSFET)27, as shown in Fig. 3b, c. The input voltage, output spike voltage (VSpike), recombination rate, and electron density during the LIF operation are plotted as functions of time in Fig. 3d. When a constant DC input voltage of 1.15 V is applied to the input voltage node (VIN), the n-channel MOSFET is partially turned on and the current component INMOS is increased. Simultaneously, the electron density in the potential well of the non-gated region is increased because of an increase in the emitter current component IB1 in the p–n–p BJT and collector current component IB2 in the n–p–n BJT. Moreover, the recombination rate in the non-gated channel region increases with time owing to the accumulation of electrons in the potential well. When the positive feedback loop is initiated by accumulated charge carriers, spiking behavior with oscillations are generated by the latch-up phenomenon. After the generation of the positive feedback loop, as the voltage across the neuron device decreases with an increase in the source node voltage (VSpike), which is caused by the abrupt increase in the current, the accumulated charge carriers are removed. This phenomenon is the latch-down state, which is enabled by the negative feedback loop. After an effective refractory period, neural oscillations of the neuron device were present in the VSpike as a function of time. Following the spiking behavior in the neuron device induced by the positive feedback loop, the output spike voltage (VSpike) automatically returns to the initial state, which corresponds to the reset mechanism induced by the negative feedback loop.

(a) Block diagram of front-end neuromorphic hardware system, consisting of sensory system, synaptic devices, and neuron device, receiving external stimulus. (b) Spike and (c) reset mechanism in an equivalent circuit of the single silicon nanowire neuron device, and (d) electron density in the non-gated channel region, recombination rate in the non-gated channel region, spike voltage, and input voltage as functions of time. (e) A spike response of the neuron device to sinusoidal analog input signals.

Our neuron device produces digital output signals with neural oscillations for DC as well as analog AC input signals. Sinusoidal analog input signals, in which dynamic neural oscillations can be implemented using positive and negative feedback loops, were applied to the neuron device. When the VIN is above 1.15 V in the sinusoidal analog input signal, the neuron device produces neural oscillations (Fig. 3e). As the amplitude and frequency of the sinusoidal analog input signal range from 100 to 50 mV and 200 to 100 kHz, respectively, the number of spike events per time can be tuned by adjusting the input signal. Therefore, the modulation of the neural oscillation frequency is enabled by varying the amplitude, offset voltage, and period of the sinusoidal input signals.

The neuron device can deliver digital signals from pre-synaptic devices to post-synaptic devices (Fig. 4a). Figure 4b shows the input voltage (VIN), output spike voltage (Vspike), and output spike current (Ispike) as functions of time. The integration and firing operations are performed in the neuron device for the transmission of VIN pulses (with 1.15 V, a time width of 500 ns, and a period of 2 μs). As the VIN pulses are input to the neuron device, charge carriers constituting the VIN pulses accumulate (or integrate) in the potential well of the neuron device. The lowering of the potential barrier height by repeated VIN pulses initiates a positive feedback loop in the neuron device. Then, the generated Vspike (Ispike) rises rapidly from 0.00 V (2.6 × 10−10 A) to 0.14 V (2.9 × 10−7 A), which corresponds to the firing of Vspike (Ispike). In the reset stage, Vspike (Ispike) returns to the initial voltage (current) through a negative feedback loop. Thus, our neuron device effects periodic spike and reset operations on VIN pulses. Moreover, the firing frequency and Vspike can vary with the time width of the input voltage (tIN). As tIN decreases from 1 μs to 300 ns, the number of spikes within a defined time (20 μs) decreases from 9 to 3, while the firing frequency and Vspike decrease from 507 to 167 kHz and from 0.140 to 0.015 V, respectively (Fig. 4c). Because of the shorter tIN, fewer charge carriers integrate in the potential well of the neuron device, which in turn calls for a greater number of VIN pulses for integration and firing operations.

(a) Block diagram of artificial neuron device, pre- and post- synaptic devices constituting the neuromorphic hardware system. (b) Input voltage, spike voltage, and spike current as functions of time. (c) A spike response of the single silicon nanowire neuron device for time widths of input voltage pulse (tIN) of 1 μs, 800 ns,500 ns, and 300 ns.

The firing frequency and Vspike of our neuron device depend on the amplitude of VIN (Fig. 5). As VIN increases from 1.15 to 1.55 V, more charge carriers accumulate in the potential well leading to decrease in the time for triggering the positive feedback loop. Consequently, the firing frequency (Vspike) increases from 1.1 MHz (0.15 V) to 7.8 MHz (0.54 V). The adjustment of the amplitude of VIN enables our neuron device to control the firing frequency and Vspike. It should be noted that the firing frequency saturates at ~ 8 MHz despite the increment in VIN. This is caused by the inner capacitance components in our neuron device giving rise to RC delay.

In Table 1, our neuron device is compared with other neuron devices and circuits in terms of operating mechanism, number of components, number of external bias lines, supply voltage, energy consumption, and firing frequency. External bias lines are indispensable for tuning spiking voltages in neuron devices with independent double-gate field-effect transistors14; such devices have high energy consumption (9.5 × 10−13 J) and a low firing frequency (~ 300 Hz). Neuron circuits using a positive feedback mechanism15,16,17 reported by other research groups require more than five components and two external bias lines to implement their integration and firing operations. In addition, these neuron circuits15,16 consume substantial energy (2.5 × 10−13 J and 6.2 × 10−13 J) while having low firing frequencies (~ 300 Hz and ~ 30 kHz). Although our previous neuron circuit using a positive feedback mechanism28 had an energy consumption (2.9 × 10−15 J) lower than our present neuron device (4.5 × 10−15 J), the latter had a large area occupied by a membrane capacitor and needs one external bias line. The partially depleted SOI MOSFET neuron device based on the band-to-band tunneling mechanism requires an external reset circuit and a threshold detector circuit24, even though it has a relatively low energy consumption. As for capacitor-less ReRAM and PCRAM19, their neuron operation should need more than ten transistors with several external bias voltages. In the neuron operation of FeFETs21,22, 1 nF and 1 pF capacitors should be used as the membrane, making the neuron hard to achieve high integration density. Among these neuron devices and circuits, our neuron device using a gated p–n–p–n diode structure is the most energy-efficient owing to its low energy consumption (4.5 × 10−15 J), high firing frequency (~ 8 MHz), and absence of external bias voltage; note that neuron devices and circuits including our neuron device require peripheral circuits receiving synaptic pulses and delivering firing voltages. Our neuron device can implement a neuromorphic system by bidirectionally connecting with transposable synapstic SRAM using feedback field-effect transistor, and enables fast information transfer due to its high firing frequency30. Furthermore, our neuron device that is in normally-off state until synaptic pulses (analog and digital input signals) reach this device achieves zero standby power without external bias voltage.

Conclusion

In summary, our single silicon nanowire neuron device with a gated p–n–p–n structure emulates biological neurons using interlinked positive and negative feedback loops. The neuron device produces dynamic neural oscillations in its leaky integrate-and-fire operation. Moreover, the neuron device provides a high firing frequency and low energy consumption without the need for an external bias voltage. The neuron device that acts as a normally-off IF system achieves zero standby power. The high integration capability and remarkable energy efficiency mean that this neuron device can contribute to the achievement of hardware-based spiking neural networks in state-of-the-art neuromorphic architectures.

References

Furber, S. Large-scale neuromorphic computing systems. J. Neural Eng. 13(5), 051001 (2016).

Schemmel, J., Brüderle, D., Grübl, A., Hock, M., Meier, K., & Millner, S. A wafer-scale neuromorphic hardware system for large-scale neural modeling. In Proceedings of 2010 IEEE International Symposium on Circuits and Systems (ISCAS) 1947–1950 (2010).

Hasler, J. & Bo Marr, H. Finding a roadmap to achieve large neuromorphic hardware systems. Front. Neurosci. 7, 118 (2013).

Marković, D., Mizrahi, A., Querlioz, D. & Grollier, J. Physics for neuromorphic computing. Nat. Rev. Phys. 2(9), 499–510 (2020).

Boybat, I. et al. Neuromorphic computing with multi-memristive synapses. Nat. Commun. 9(1), 1–12 (2018).

Eryilmaz, S. B., Kuzum, D., Yu, S., Wong, H. S. P. Device and system level design considerations for analog-non-volatile-memory based neuromorphic architectures. In Proceedings of 2015 IEEE International Electron Devices Meeting (IEDM) , 4(1), 1–4 (2015).

Islam, R. et al. Device and materials requirements for neuromorphic computing. J. Phys. D Appl. Phys. 52(11), 113001 (2019).

Brandman, O. & Meyer, T. Feedback loops shape cellular signals in space and time. Science 322(5900), 390–395 (2008).

Tsai, T. Y. et al. Robust, tunable biological oscillations from interlinked positive and negative feedback loops. Science 321(5885), 126–129 (2008).

Ferrell, J. E. Jr. Feedback loops and reciprocal regulation: Recurring motifs in the systems biology of the cell cycle. Curr. Opin. Cell Biol. 25(6), 676–686 (2013).

Stoliar, P. et al. A leaky-integrate-and-fire neuron analog realized with a Mott insulator. Adv. Funct. Mater. 27(11), 1604740 (2017).

Mahowald, M. & Douglas, R. A silicon neuron. Nature 354(6354), 515–518 (1991).

Indiveri, G. et al. Neuromorphic silicon neuron circuits. Front. Neurosci. 5, 73 (2011).

Han, J. et al. A single transistor neuron with independently accessed double-gate for excitatory-inhibitory function and tunable firing threshold voltage. IEEE Electron Device Lett. 41(8), 1157–1160 (2020).

Choi, K. et al. A split-gate positive feedback device with an integrate-and-fire capability for a high-density low-power neuron circuit. Front. Neurosci. 12, 704 (2018).

Woo, S. et al. Low-power and high-density neuron device for simultaneous processing of excitatory and inhibitory signals in neuromorphic systems. IEEE Access 8, 202639–202647 (2020).

Lee, S., Woo, S. Y. & Lee, J. Low-power binary neuron circuit with adjustable threshold for binary neural networks using NAND flash memory. IEEE Access 8, 153334–153340 (2020).

Li, S. et al. Magnetic skyrmion-based artificial neuron device. Nanotechnology 28(31), 31LT01 (2017).

Lin, J. & Yuan, J.-S. "Analysis and simulation of capacitor-less ReRAM-based stochastic neurons for the in-memory spiking neural network. IEEE Trans. Biomed. Circuits Syst. 12(5), 1004–1017 (2018).

Palma, G., et al. Stochastic neuron design using conductive bridge RAM. In 2013 IEEE/ACM International Symposium on Nanoscale Architectures (NANOARCH) (IEEE, 2013).

Rajasekharan, D. et al. Ferroelectric FET-based implementation of Fitzhugh-Nagumo neuron model. IEEE Trans. Comput.-Aided Des. Integr. Circuits. Syst. https://doi.org/10.1109/TCAD.2021.3101407 (2021).

Eslahi, H., Hamilton, T. J. & Khandelwal, S. Energy-efficient ferroelectric field-effect transistor-based oscillators for neuromorphic system design. IEEE J. Explor. Solid-State Comput. Devices Circuits 6(2), 122–129 (2020).

Tuma, T., Pantazi, A., Le Gallo, M., Sebastian, A. & Eleftheriou, E. Stochastic phase-change neurons. Nat. Nanotechnol. 11(8), 693 (2016).

Phase change memory (Wong, H.S.P.,,,).

Synopsys Inc., Mountain View, CA, Sentaurus Device User Guide (2018).

Kim, M. et al. Steep switching characteristics of single-gated feedback field-effect transistors. Nanotechnology 28(5), 055205 (2016).

Woo, S. & Kim, S. Device design of single-gated feedback field-effect transistors to achieve latch-up behaviors with high current gains. Curr. Appl. Phys. 20(10), 1156–1162 (2020).

Woo, S. et al. Implementation and characterization of an integrate-and-fire neuron circuit using a silicon nanowire feedback field-effect transistor. IEEE Trans. Electron Devices 67(7), 2995–3000 (2020).

Chavan, T., Dutta, S., Mohapatra, N. & Ganguly, U. Band-to-band tunneling based ultra-energy-efficient silicon neuron. IEEE Trans. Electron Devices 67(6), 2614–2620 (2020).

Woo, S., Cho, J., Lim, D., Cho, K. & Kim, S. Transposable 3T-SRAM synaptic array using independent double-gate feedback field-effect transistors. IEEE Trans. Electron Devices 66(11), 4753–4758 (2019).

Acknowledgements

This research was supported in part by the Ministry of Trade, Industry & Energy (MOTIE; 10067791) and the Korea Semiconductor Research Consortium (KSRC) support program for the development of future semiconductor devices. It was also supported by a National Research Foundation of Korea (NRF) grant funded by the Korean government (MSIT; 2020R1A2C3004538), the Brain Korea 21 Plus Project of 2021 through the NRF funded by the Ministry of Science, ICT & Future Planning.

Author information

Authors and Affiliations

Contributions

S.W. and S.K. provided conceptualization and methodology. S.W. and S.K. analyzed the results and wrote the manuscript; S.K. supervised the research. All authors edited the manuscript and have given approval to the final version of the manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher's note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Woo, S., Kim, S. Neural oscillation of single silicon nanowire neuron device with no external bias voltage. Sci Rep 12, 3516 (2022). https://doi.org/10.1038/s41598-022-07374-2

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-022-07374-2

This article is cited by

-

Binarized neural network of diode array with high concordance to vector–matrix multiplication

Scientific Reports (2024)

-

Ultra-low power neuromorphic obstacle detection using a two-dimensional materials-based subthreshold transistor

npj 2D Materials and Applications (2023)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.