Abstract

This paper reports the catalyst-free coaxial TiO2/Ge-nanowire (NW) heterostructure synthesis using the glancing angle deposition (GLAD) technique integrated into an electron beam evaporator. The frequency and voltage dependence of the capacitance–voltage (C–V) and conductance–voltage (G/ω–V) characteristics of an Ag/TiO2-NW/Ge-NW/Si device over a wide range of frequency (10 kHz–5 MHz) and voltage (− 5 V to + 5 V) at room temperature were investigated. The study established strong dependence on the applied frequency and voltage bias. Both C–V and G/ω–V values showed wide dispersion in depletion region due to interface defect states (Dit) and series resistance (Rs). The C and G/ω value decreases with an increase in applied frequency. The voltage and frequency-dependent Dit and Rs were calculated from the Hill-Coleman and Nicollian–Brews methods, respectively. It is observed that the overall Dit and Rs for the device decrease with an increase in the frequency at different voltages. The dielectric properties such as dielectric constant (\(\upepsilon\)′), loss (\(\upepsilon\)″) and loss tangent (tan δ) were determined from the C–V and G/ω–V measurements. It is observed that \(\upepsilon\)′, \(\upepsilon\)″ decreases with the increase in frequency. Therefore, the proposed MOS structure provides a promising alternative approach to enhance the device capability in the opto-electronics industry.

Similar content being viewed by others

Introduction

One-dimensional (1D) nanostructures like nanowires and nanorods have attracted huge interest over the last few decades in the field of metal oxide semiconductor (MOS) for various applications like photodetectors1,2,3,4,5,6, sensors7,8, photovoltaic systems9, non-volatile memory applications10,11 etc. Following the Moore’s law, the current semiconductor based MOS devices are facing a technological limitation in the form of scalability and leakage current. In order to further improve the MOS device performance, the International Technology Roadmap for semiconductors (ITRS) for future technology has recommended the use of a high mobility material as an alternative solution. In this context, recent papers have reported Germanium (Ge) with high-k dielectric based MOS devices which show good overall performance12,13. This is because Ge has high electron and hole mobility compared to silicon (Si) and a low band gap which enables operation at low voltage14. This feature, together with the opportunity to co-integrate Ge with high-k dielectrics such as Al2O3, HfO2, TiO2 etc., makes Ge a practical candidate for future MOS device applications. However, the integration of Ge with a MOS capacitor is challenging due to the native unintentional formation of GeOx which is unstable compared to SiO2. This issue is mitigated by the integration of titanium dioxide (TiO2) which is a high dielectric material with Ge. The unstable GeOx is reduced by the diffusion of Ge into the TiO2. At the same time, rutile-TiO2 can be formed which has a high-dielectric constant15. Recent reports suggests that this approach can be achieved by various synthesis techniques for different applications16,17,18. Amongst these synthesis techniques, the glancing angle deposition (GLAD) is a catalyst free environment friendly technique which can synthesize numerous materials for various applications2,19,20,21. Furthermore, vertical nanowires can be easily achieved with the GLAD technique compared to other available techniques22.

In this work, a Ag/TiO2-NW/Ge-NW/Si (MOS) device is synthesized using the GLAD technique integrated into an electron-beam evaporator. The frequency and voltage dependence capacitance (C) and conductance (G/ω) at room-temperature are analyzed. The aim of the work is to investigate to the effect of interface state density (Dit), series resistance (Rs) on the C–V and G/ω–V characteristics as well as the dielectric parameters of the proposed MOS device with the applied bias voltage and frequency.

Results and discussion

The C–V and G/ω–V measurements of Ag/TiO2-NW/Ge-NW/Si MOS device are obtained for different frequencies and voltage ranges at room-temperature as shown in Fig. 1a,b. It is observed from Fig. 1a, that the MOS device displayed extensive distribution in depletion, inversion and accumulation regions. As seen in the figure, the MOS device showed an inversion region (-5 V to 0 V), a depletion region (0 V to 2 V) and an accumulation region (2 V to 5 V) at almost each frequency respectively. The voltage shift is due to the presence of surface states in the MOS device23. The measured capacitance (C) and conductance (G/ω) values showed strong dependence on frequency and voltage in the depletion region which might be due to the Dit and Rs in the MOS device. The decrease in C and G/ω with the increase in frequency as shown in Fig. 2a,b, might be because the Dit cannot follow the alternating current (ac) signal at high frequencies and hence the contribution of these states to capacitance and conductance decrease with the increase in frequency24. This makes the contribution of interface state capacitance to the total capacitance negligible25. Thus, the measured C–V and G/ω–V values are close to the ideal case at high frequencies. At low frequency, the wide dispersion present in depletion region for both the C–V and G/ω–V curves is due to the existence of Dit26.

The electrical parameters Dit and Rs could have attributed to the deviation in both the C–V and G/ω–V curves from the ideal behaviour. The unsymmetrical growth of nanowires due to the shadowing effect inherent in the GLAD technique may have induced inhomogeneous contact during the metallization process between the metal contact and the semiconductor junction. This also could be the reason for the deviation from the ideal behaviour of the MOS device. The Nicollian and Brews method25 is used to determine the parameters Rs in the measured voltage range of the MOS device. This method is reported to be more precise in comparison with Norde and Cheung functions and conductance and admittance methods as per previous report26. Rs is calculated using the Eq. (1) 25 given below:

where Cma and Gma are the measured C and G for any biased voltage and ω is the angular frequency. Figure 3a,b, show the Rs–V plots determined from Eq. 1. It is observed from Fig. 3a that Rs decreases with an increase in frequency and the presence of peak around − 0.5 V to 1.3 V at low frequencies is due to the presence of Dit. The changes in Rs from region to region clearly shows that Rs is dependent on both the applied frequency and voltage. The change in Rs is evident especially in the inversion and depletion regions from the low to the high frequency range. It should be noted that Rs is independent of frequency at the accumulation region from frequency greater than 30 kHz. Furthermore, the voltage dependent Rs show almost constant value at higher frequencies (frequency > 200 kHz). This shows that for Ag/TiO2-NW/Ge-NW/Si (MOS) device, the Rs is effective in the accumulation region in high voltage at high frequencies (frequency > 200 kHz).

The Dit is another parameter which affects the measured C–V and G/ω–V for the Ag/TiO2-NW/Ge-NW/Si (MOS) device. The frequency dependent Dit plot can be obtained using the Hill-Coleman method from Eq. (2)27 given below:

where Cox and (Gm/ω) max are the interlayer capacitance, maximum value of conductance which is corresponding to Cm and the value of Cox can be calculated from the measured C and G/ω values at the strong accumulation region using Eq. (3)28 as given below:

The frequency dependent Dit determined using Eqs. 2 and 3 is shown in Fig. 4. It is observed that the Dit decreases with an increase in frequency for the Ag/TiO2-NW/Ge-NW/Si (MOS) device which is due to the low power follow rate at high frequencies28. Furthermore, the obtained Dit value at high frequency ( frequency > 400 kHz) is found to be better in comparison with the reported values17,29,30 and thus addresses the serious issue of high interface state densities. The distinct peak seen in the Dit plot in Fig. 4 (inset) at 100 kHz and 300 kHz having Dit values of 1.73 × 1013 eV−1 cm−2 and 2.05 × 1010 eV−1 cm−2 with defect lifetime of ~ 10 μs and 3.3 μs, respectively. The difference in the lifetime of the defects observed from the Dit plot is primarily due to the slow traps and fast traps also known as interface traps corresponding to large defect lifetime and small defect lifetime, respectively29. It can be seen that the maximum value of Cm decreases with an increase in Rs which is in good agreement with the theoretical results stated by Chattopadhyay et al.31. Therefore, Dit at low frequency in the Ag/TiO2-NW/Ge-NW/Si (MOS) device can follow the ac signal and yield an excess capacitance, thus resulting in Dit being more pronounced compared to Rs. In contrast to the low frequency values, the Dit values at high frequency cannot follow the ac signal which makes the contribution of interface state capacitance to total capacitance negligible. This results in the contribution of Rs being more pronounced.

In order to obtain the corrected capacitance (Cc) and corrected conductance (Gc/ω) at different frequencies both measured C and G/ω are corrected considering the effect of series resistance (Rs) using the Eq. (4–6)28 given below:

Figure 5 represents the CC–V and Gc/ω–V plots for the Ag/TiO2-NW/Ge-NW/Si (MOS) device. It is observed after making the correction that is considering the effect of Rs in Cc versus V plot, there is no significant change in the corrected capacitance (Cc) values. However in the case of the corrected conductance (Gc), it is observed that there is a decrease in the Cc value with an increase in frequency and the existence of peaks in the Gc/ω–V plot confirms the charge transfer taking place at the interface28.

The dependence of the dielectric constant (\(\upepsilon\)′), dielectric loss (\(\upepsilon\)″) and dielectric loss tangent (tan(δ)) on the frequency and voltage are investigated in various frequencies (10 kHz to 5 MHz) at different voltage ranges (-5 V to 5 V) at room-temperature. The values of the dielectric constant (\(\upepsilon\)′) and dielectric loss (\(\upepsilon\)″) of the Ag/TiO2-NW/Ge-NW/Si (MOS) device are obtained using the measured C, G/ω, thickness of the oxide layer, area of diode and permittivity of free space (\(\upepsilon\)o). The complex dielectric constant (\(\varepsilon * = \varepsilon ^{\prime } - j\varepsilon ^{{\prime \prime }}\)), the real and imaginary parts could then be determined from the relations given in Eq. (7–8)32 given below:

where \(C_{o} = \varepsilon _{o} \left( {\frac{A}{{d_{{ox}} }}} \right)\); A is the area of the device, dox is the oxide layer thickness, \(\upepsilon\)o is the permittivity of free space (\(\upepsilon\)o = 8.85 × 10–14 F/cm), Gm is the conductivity of MOS structure and ω is the angular frequency and j is the imaginary root of − 1. The dielectric loss tangent can be determined by the relation given in Eq. (9)32 given below:

Both the real and imaginary parts are calculated from the measured C and G/ω. The dielectric loss is expressed as the energy loss caused by the heating of a dielectric material in a variable electric field26. The loss factor is known as the energy spent at the dielectric to avoid bound charge displacement to be in phase with the field alternations26. From Fig. 6a-c, it is observed that the \(\upepsilon\)′, \(\upepsilon\)″ and tan(δ) values show independent behaviour from frequency in the inversion region and then starts to increase from the depletion region to the accumulation region. Furthermore, the \(\upepsilon\)′, \(\upepsilon\)″ and tan(δ) values decrease with increasing frequency. This behaviour can be explained by the fact that when the frequency is increased, the interfacial dipoles in the dielectric have less time to orient themselves in the direction of the alternating electric field and alternatively, the polarization decreases with the increase in frequency and remains constant26. This implies that at higher frequencies, the contribution of Dit and dipole polarization could be neglected. In other words, the decrement in the \(\upepsilon\)′ is due to the fact that the dipoles do not have enough time to orient themselves in the direction of electric field and the Dit cannot follow the ac signal. Furthermore, the mix-phase established from the XRD plot, where both anatase and rutile type TiO2 are reported might also be the reason behind the decrement in the \(\upepsilon\)′33. The broad peak observed in the tan(δ) plot at frequencies less than 200 kHz could be attributed to the relaxation process and the Dit. In addition, the behaviour of decrease in the values of the measured capacitance (C), dielectric constant (\(\upepsilon\)′) and dielectric loss (\(\upepsilon\)″) decreases with the increase in frequency is attributed to the presence of the interfacial polarization mechanism28. Moreover, to show the effect of voltage on the dielectric parameters, frequency dependent plots are shown in Fig. 7a-c at different bias voltage, respectively. It is observed that the decrease in values of \(\upepsilon\)′, \(\upepsilon\)″ and tan(δ) with the increase in frequency is due to the decrease in polarization with the increase in frequency and the values remains constant at high frequency. This implies that the contribution of dipole polarization and Dit could be neglected at high frequency. Therefore, the Dit cannot follow the ac signal and the absence of any interfacial polarization mechanism in the MOS device makes the contribution to C, \(\upepsilon\)′ and \(\upepsilon\)″ negligible at high frequencies (> 200 kHz). The low frequency dielectric behaviour of the MOS device can be attributed to four possible mechanisms: electrode interface, dc conductivity, dipole-orientation and charge carriers34.

Experimental procedure

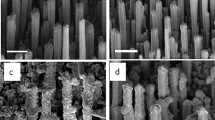

TiO2-NW/Ge-NW is fabricated on a 1 cm × 1 cm n-type Si (100) substrate using the GLAD technique incorporated into an electron-beam evaporator (Vacuum Coating Unit Model-BC-300). Using an ultra-sonicator, the Si substrates are cleaned in a 3-step sequence using electronic grade acetone, methanol, and rinsed with de-ionized (DI) water. During the synthesis process, the base pressure of ~ 2 × 10–6 mbar is maintained inside the electron-beam chamber. A deposition rate of 0.5 Å s−1 is maintained during the synthesis of TiO2-NW/Ge-NW using a digital thickness monitor (DTM). Firstly, a thin-film (TF) layer of Ge (30 nm) is deposited over the Si substrate using a pure 99.999% Ge source. Next the substrate is azimuthally rotated at.

30 rpm with substrate holder kept inclined at 85° with respect to the source where Ge-NW (200 nm) was synthesized. Subsequently the TiO2-NW (200 nm) is fabricated using pure 99.999% TiO2 source over the Ge-NW to obtain coaxial TiO2-NW/Ge-NW assembly. Finally, silver (Ag) metal contacts are fabricated using an aluminum mask with a hole area ~ 7 mm2 on both the samples. The schematic of the Ag/TiO2-NW/Ge-NW/Si MOS device is given in Fig. 8a-d. The electrical characterization of the devices is performed using a Keithly 4200 SCS from 10 kHz to 5 MHz.

Conclusion

The electrical and dielectric parameters of a GLAD synthesized Ag/TiO2-NW/Ge-NW/Si (MOS) device have been studied over a wide frequency and voltage ranges. It has been determined from the measured C and G/ω behaviour of the MOS device that the parameters were dependent on the applied frequencies and voltages. In addition, the wide dispersion exhibited in both C and G/ω curves in the depletion region was mainly attributed to the existence of the Dit. Furthermore, the measured C and G/ω behaviour with the applied frequency and voltage were dependent on the Dit, Rs and the polarization process. The Dit and Rs parameters were computed using the Hill-Coleman and Nicollian–Brews methods in wide frequency and voltage ranges. The dielectric properties analysis of the MOS device established that the \(\upepsilon\)′, \(\upepsilon\)″ and tan(δ) parameters were dependent on frequency and that the values decrease with the increase in frequency. Furthermore, it is observed at higher frequencies (> 200 kHz), the \(\upepsilon\)′ and \(\upepsilon\)″ values remains constant which is attributed to the interfacial polarization. Moreover, the decrement in the \(\upepsilon\)′ value for the MOS device is also due to the mix-phase of anatase and rutile type TiO2 present in the structure as determined from the XRD study reported earlier. Therefore, the study of the proposed MOS device has highlighted that it offers improved device capability for opto-electronics applications and also the potential for further improvement to obtain better device performance.

Data availability

The datasets generated during and/or analysed during the current study are available from the corresponding author on reasonable request.

References

Kim, C. et al. Highly responsive near-infrared photodetector with low dark current using graphene/germanium Schottky junction with Al2O3 interfacial layer. Nanophotonics 10, 1573–1579 (2021).

Pooja, P. & Chinnamuthu, P. Annealed n-TiO2/In2O3 nanowire metal-insulator-semiconductor for highly photosensitive low-noise ultraviolet photodetector. J. Alloys Compd. 854, 157229 (2021).

Chandra, A. et al. NIR photodetector based on p-silicon nanowires/n-cadmium sulfide nanoscale junctions. Appl. Surf. Sci. 548, 149256 (2021).

Shougaijam, B., Ngangbam, C. & Lenka, T. R. Enhancement of broad light detection based on annealed Al-NPs assisted TiO2-NWs deposited on p-Si by GLAD technique. IEEE Trans. Nanotechnol. 17, 285–292 (2018).

Chinnamuthu, P., Dhar, J. C., Mondal, A., Bhattacharyya, A. & Singh, N. K. Ultraviolet detection using TiO2 nanowire array with Ag Schottky contact. J. Phys. D. Appl. Phys. 45, 135102 (2012).

Liu, K., Sakurai, M., Liao, M. & Aono, M. Giant improvement of the performance of ZnO nanowire photodetectors by Au nanoparticles. J. Phys. Chem. C 114, 19835–19839 (2010).

Yang, W. et al. Silicon-compatible photodetectors: Trends to monolithically integrate photosensors with chip technology. Adv. Funct. Mater. 29, 1808182 (2019).

Singh, N. K. et al. 2D like photonic crystal using In2O3–SiOx heterostructure nanocolumn arrays and humidity sensing. Electron. Mater. Lett. 10, 975–980 (2014).

Mahala, P. et al. High-performing self-driven ultraviolet photodetector by TiO2/Co3O4 photovoltaics. J. Alloys Compd. 827, 154376 (2020).

Lahiri, R. & Mondal, A. Superior memory of Er-doped TiO2 nanowire MOS capacitor. IEEE Electron Device Lett. 39, 1856–1859 (2018).

Panigrahy, S. & Dhar, J. C. Non-volatile memory property of Er2O3 doped SnO2 nanowires synthesized using GLAD technique. J. Mater. Sci. Mater. Electron. 30, 8339–8347 (2019).

Dimoulas, A. et al. Interface engineering for Ge metal-oxide-semiconductor devices. Thin Solid Films 515, 6337–6343 (2007).

Moreau, M. et al. Investigation of capacitance–voltage characteristics in Ge/high-κ MOS devices. J. Non. Cryst. Solids 355, 1171–1175 (2009).

Kamata, Y. High-k/Ge MOSFETs for future nanoelectronics. Mater. Today 11, 30–38 (2008).

Bengi, A., Aydemir, U., Altindal, Ş, Özen, Y. & Özçelik, S. A comparative study on the electrical characteristics of Au/n-Si structures with anatase and rutile phase TiO2 interfacial insulator layer. J. Alloys Compd. 505, 628–633 (2010).

Kim, G. S. et al. Effective Schottky barrier height lowering of metal/n-Ge with a TiO2/GeO2 interlayer stack. ACS Appl. Mater. Interfaces 8, 35419–35425 (2016).

Khan, Z. N., Khan, S. A. & Shakeel, S. Incorporation of Ge on high K dielectric material for different fabrication technologies (HBT, CMOS) and their impact on electrical characteristics of the device. J. Nanomater. 2018, (2018).

Rahman, M. S. & Evangelou, E. K. Dielectric relaxation and charge trapping characteristics study in Germanium based MOS devices with HfO2/Dy2O3 gate stacks. IEEE Trans. Electron Devices 58, 3549–3558 (2011).

Singh, H. M., Choudhuri, B. & Chinnamuthu, P. Investigation of optoelectronic properties in germanium nanowire integrated silicon substrate using kelvin probe force microscopy. IEEE Trans. Nanotechnol. 19, 1–1 (2020).

Panigrahy, S. & Dhar, J. C. Suppression of leakage current using annealed Er2O3 nanowires as a superior dielectric material. J. Mater. Sci. Mater. Electron. 32, 3522–3528 (2021).

Rajkumari, R. & Singh, N. K. Ag nanoparticle-decorated WO3 nanowires for nonvolatile memory. ACS Appl. Nano Mater. 3, 12087–12094 (2020).

Zhao, Y., Ye, D., Wang, G.-C. & Lu, T.-M. Designing nanostructures by glancing angle deposition. In Nanotubes and Nanowires vol. 5219 59–73 (International Society for Optics and Photonics, 2003).

Tataroǧlu, A. & Altindal, Ş. Characterization of current-voltage (I–V) and capacitance–voltage–frequency (C–V–f) features of Al/SiO2/p-Si (MIS) Schottky diodes. Microelectron. Eng. 83, 582–588 (2006).

Tanrıkulu, E. E., Demirezen, S., Altındal & Uslu, I. On the anomalous peak and negative capacitance in the capacitance–voltage (C–V) plots of Al/(%7 Zn-PVA)/p-Si (MPS) structure. J. Mater. Sci. Mater. Electron. 29, 2890–2898 (2018)

Nicollian, E. H. & Goetzberger, A. MOS conductance technique for measuring surface state parameters. Appl. Phys. Lett. 7, 216–219 (1965).

Demirezen, S., Eroğlu, A., Azizian-Kalandaragh, Y. & Altındal, Ş. Electric and dielectric parameters in Au/n-Si (MS) capacitors with metal oxide-polymer interlayer as function of frequency and voltage. J. Mater. Sci. Mater. Electron. 31, 15589–15598 (2020).

Hill, W. A. & Coleman, C. C. A single-frequency approximation for interface-state density determination. Solid State Electron. 23, 987–993 (1980).

Yücedaǧ, I., Altindal, Ş & Tataroǧlu, A. On the profile of frequency dependent series resistance and dielectric constant in MIS structure. Microelectron. Eng. 84, 180–186 (2007).

Kuzum, D. et al. High-mobility Ge N-MOSFETs and mobility degradation mechanisms. IEEE Trans. Electron Devices 58, 59–66 (2011).

Zhang, L. et al. Selective passivation of GeO2/Ge interface defects in atomic layer deposited high-k MOS structures. ACS Appl. Mater. Interfaces 7, 20499–20506 (2015).

Chattopadhyay, P. & RayChaudhuri, B. Frequency dependence of forward capacitance-voltage characteristics of Schottky barrier diodes. Solid State Electron. 36, 605–610 (1993).

Demirezen, S. Frequency- and voltage-dependent dielectric properties and electrical conductivity of Au/PVA (Bi-doped)/n-Si Schottky barrier diodes at room temperature. Appl. Phys. A Mater. Sci. Process. 112, 827–833 (2013).

Manas, S. H., Choudhuri, B. & Chinnamuthu, P. Reduction of interface state density in coaxial TiO2/Ge nanowire assembly-based heterostructure and superior photodetection. J. Alloys Compd. 853, 157344 (2021).

Fanggao, C. et al. Temperature and frequency dependencies of the complex dielectric constant of poly(ethylene oxide) under hydrostatic pressure. J. Polym. Sci. Part B Polym. Phys. 34, 425–433 (1996).

Acknowledgements

The authors are grateful and would like to acknowledge NIT Nagaland for the synthesis, characterization facility as well as the financial assistance.

Author information

Authors and Affiliations

Contributions

H.M.S performed the investigation, data curation, formal analysis and written the original draft. L.Y.Y contributed in review and editing of the original draft. P.C, the corresponding author conceptualize, provided supervision, validation, review and editing of the original draft. All authors reviewed the manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher's note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Singh, H.M., Lim, Y.Y. & Chinnamuthu, P. Electrical and dielectric parameters in TiO2-NW/Ge-NW heterostructure MOS device synthesized by glancing angle deposition technique. Sci Rep 11, 19837 (2021). https://doi.org/10.1038/s41598-021-99354-1

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-021-99354-1

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.