Abstract

Although the demand for high-speed telecommunications has increased in recent years, the performance of transistors fabricated with traditional semiconductors such as silicon, gallium arsenide and gallium nitride have reached their physical performance limits. Therefore, new materials with high carrier velocities should be sought for the fabrication of next-generation, ultra-high-speed transistors. Indium nitride (InN) has attracted much attention for this purpose because of its high electron drift velocity under a high electric field. Thick InN films have been applied to the fabrication of field-effect transistors (FETs), but the performance of the thick InN transistors was discouraging, with no clear linear-saturation output characteristics and poor on/off current ratios. Here, we report the epitaxial deposition of ultrathin cubic InN on insulating oxide yttria-stabilized zirconia substrates and the first demonstration of ultrathin-InN-based FETs. The devices exhibit high on/off ratios and low off-current densities because of the high quality top and bottom interfaces between the ultrathin cubic InN and oxide insulators. This first demonstration of FETs using a ultrathin cubic indium nitride semiconductor will thus pave the way for the development of next-generation high-speed electronics.

Similar content being viewed by others

Introduction

Theoretical calculations based on optical measurements predict that InN possesses a high electron peak velocity exceeding 2 × 108 cm/s (ref. 1). This value is much higher than those for conventional semiconductor materials such as gallium arsenide, used in high-speed electronics. This nature of InN makes it a promising material for use in high-speed FETs. In fact, it is predicted that an InN-based metal-oxide-semiconductor FET (MOSFET) with a channel length of 100 nm can be theoretically operated at terahertz frequencies2. Despite these outstanding transport properties, the performance of FETs fabricated with thick InN (>20 nm) has been discouraging3. The transistors show poor on/off ratios and lack clear linear-saturation output characteristics. It is believed that the problems with these InN transistors stem from the poor quality of the thick InN films and their interfaces with the surrounding insulators. InN films are typically grown on foreign crystals such as GaN (refs. 4 and 5) or AlN (refs. 3 and 6), resulting in quite large lattice mismatches, which in turn leads to the formation of a high density of misfit dislocations at the interfaces7. These dislocations then propagate into the InN films and act as unintentional sources of electron8,9, making it difficult to modulate the source-drain current (IDS) in the FET via gating. Therefore, a new technique that enables the deposition of InN films with higher structural perfection must be developed for successful fabrication of high-performance InN-based FETs. The use of yttria-stabilized zirconia (YSZ) substrates can be a good option for this purpose because there is a very small lattice mismatch (2.7%) between YSZ and InN, which should provide a reduced defect density at the interfaces10,11. The other advantage of using YSZ substrates lies in their insulating nature, which is important for the fabrication of FETs because the use of semiconducting substrates may lead to an increase in the leakage current in the “off” state.

We report a newly developed method for the growth of ultrathin cubic InN(111) films on YSZ(111) substrates and the first demonstration of transistors using high-quality ultrathin cubic InN channel layers. The transistors fabricated with a 2-nm-thick cubic film exhibited an on/off IDS ratio of ~5 × 106 and a very low off-current IDS of the order of pA. The maximum IDS for devices fabricated in this study exceeded 60 mA/mm when flowing through a 5-nm-thick InN layer and the field-effect mobility was ~58 cm2 V−1s−1.

Results

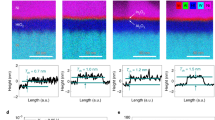

Prior to film growth, the YSZ(111) substrates were thermally treated at 1000°C in air so that InN films with atomically flat surfaces could grow on them. During annealing, the substrates were capped with a sapphire wafer. This capping step is essential for reproducibly obtaining high-quality InN films on YSZ. Figures 1a and 1b show atomic force microscopy (AFM) images of YSZ(111) substrates before and after the thermal treatment. The annealed surface possesses a clear step-and-terrace structure with a single step height of ~0.6 nm, which roughly corresponds to two monolayers of YSZ(111). The cross-sectional profile of the atomically flat YSZ(111) surface is provided in Supplementary Fig. S1b. Atomically flat surfaces are critical for epitaxial growth of high-quality InN films and the fabrication of transistors because surface roughness often leads to generation of defects.

AFM surface images of YSZ(111) and ultrathin InN.

(a) As-received YSZ(111) surface. (b) The surface of YSZ became atomically flat after thermal annealing at 1000°C. Atomic steps appeared on the surface. (c) Epitaxial InN film grown on the atomically flat YSZ(111). The root mean square roughness for the InN surface is 0.18 nm.

InN films were grown at 620°C via pulsed-sputtering deposition in an ultra-high vacuum chamber with a background pressure of ~2 × 10−10 Torr (refs. 11 and 12). An In metal target and purified nitrogen gas (99.9999% purity) were used as the sources for InN growth. The InN film thickness was controlled by varying the pulse number during sputtering. The average deposition rate of the film precursors was adjusted so that growth of an InN monolayer was completed in 2.7 s. The growth temperature is from a thermo-couple that locates near the substrate, which indicates that the actual temperature of the growing surface is slightly lower than that value. The epitaxial InN films formed on the YSZ(111) substrates are continuous and without cracks or pits on the surface (Fig. 1c). The root mean square value of the surface roughness for the films was as low as 0.18 nm, which is smooth enough to fabricate an abrupt interface with, for example, a gate oxide insulator used in the fabrication of FETs.

Figure 2a shows a cross-sectional transmission electron microscopic (TEM) image of ultrathin (2 nm) InN grown on a YSZ(111) substrate. Because the sample is part of FET, an amorphous HfO2 gate insulator is deposited on top of the InN film. It is well known that the stacking sequences of hexagonal (wurtzite) InN along the <0001> direction and cubic (zincblende) InN along the <111> direction are ..ABABAB.. and ..ABCABC.., respectively, where A, B and C denote In-N layers with different atom positions. Careful interpretation of the TEM image revealed that the stacking sequence of the InN is that of the (111)-oriented cubic (zincblende) structure. In addition, stacking sequence of the cubic InN replicated that of the YSZ substrate. The successful growth of cubic InN is likely because of the stacking sequence of fluorite structure in YSZ, which has a zincblende-like structure. White dots in the YSZ in the figure are Zr(Y) atoms stacked in the sequence ..ABCABC.., which is the same as that for cubic InN. Figures 2b and 2c show the Fourier transformed images of the InN and YSZ in Fig. 2a, respectively. The distribution of spots in Fig. 2b is quite similar to that of Fig. 2c, which indicates that the InN crystallized with the cubic structure. All these results support the conclusion that the growth of cubic InN(111) occurred on the cubic YSZ(111) substrates. Considering the successful growth of N-polar InN(000–1) films at 615°C by plasma-assisted molecular beam epitaxy13, we believe that the cubic InN is as stable as N-polar InN, at this moment.

(a) High-resolution transmission electron microscopy (TEM) image of an amorphous-HfO2/cubic-InN/YSZ interface. The expanded TEM image reveals that high-quality cubic InN(111) grows on YSZ(111) and that abrupt HfO2/InN and InN/YSZ interfaces are formed. The stacking sequence for YSZ is the same as that for InN. (b) Fourier-transformed image of InN, (c) Fourier-transformed image of YSZ in the TEM image. The symmetries in (b) and (c) are the same, indicating that the symmetry of the cubic YSZ was transferred to the InN film.

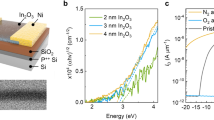

FETs with InN channel thicknesses of 2 and 5 nm were then fabricated. An optical microscopic image and schematic view of a FET are shown in Fig. 3. To fabricate the FETs, 100 μm × 50 μm islands in the ultrarhin InN films on the YSZ(111) substrates were formed using photolithography and inductively coupled plasma reactive ion etching techniques. A 50-nm-thick Au layer was then deposited on each of the InN surfaces and used as source and drain electrodes. A 20-nm-thick HfO2 gate insulator was then deposited at 200°C on each FET using atomic layer deposition. The HfO2 was in the amorphous phase, which was confirmed by analyzing the TEM images (Fig. 2a). It is well known that the quality of hetero-interfaces between gate insulators and semiconductors is critically important for the fabrication of high-performance FETs. Notably, the HfO2/InN interface was found to be abrupt. We have confirmed the formation of an electron accumulation layer at the HfO2/InN interface by x-ray photoelectron spectroscopy (see Supplementary Fig. S2). Finally, a Au film was deposited on the HfO2 and used as a gate electrode. The gate length LG and width WG of the FET varied from 5 to 50 μm.

Optical micrograph and schematic image of a cubic (zincblende) InN-based field-effect transistor.

Mesa etching of cubic InN epitaxially grown on YSZ substrates was performed using conventional photolithography and dry etching. The cubic InN channel layers were covered with Au (source and drain electrodes) and amorphous HfO2 (gate insulator).

Discussion

Figure 4a presents the output characteristics of the HfO2/2-nm-cubic-InN/YSZ FET. It can be seen that the current through the ultrathin InN can be well controlled by changing VG, which clearly has linear and saturation regions, indicating that the characteristics of this FET follow the conventional simple MOSFET theory. In addition, the FET operated in the depletion mode, indicating that the ultrathin cubic InN has a conduction channel for electrons even at zero bias. Figure 4b shows the transfer characteristics of the 2-nm-thick device. The on/off current ratio was ~5 × 106. In this sample, the electrons are well depleted by the negative gate bias in the “off” state and IDS decreases to the order of pA. The “off”-state characteristics of this FET are better than SiO2/InN/AlN FETs, whose “off” current is at the level of nA (ref. 6), which indicates that high-quality HfO2/InN/YSZ interfaces are formed using the newly developed process. With the assumption that the electron density in the ultrathin cubic InN is 2.1 × 1020 cm−3 (Ref. 14), the sheet electron density of that is 2.2 × 1013 cm−2. This coincides with the fixed charge density in HfO2 (2.2 × 1013 cm−2 for dielectric constant εr of 16 and thickness of 20 nm) with the gate voltage of −5 V. The field-effect mobility (μFE) calculated using the relationship for the linear region (IDS = (μFECiWG/LG) (VGS − VTH) VDS) was 0.17 cm2 V−1 s−1. Figures 4c and 4d show the output and transfer characteristics of the FET, respectively, with a channel thickness of 5 nm. The on/off current ratio of this device is 37 and the current density in “off”-state at VDS = 5 V and VG = −10 V is 0.70 mA/mm. The drain current is approximately two orders of magnitude larger than that of the 2-nm-thick InN FET, but the on/off ratio is considerably lowered. Maximum values for the IDS and μFE in this study are 61 mA/mm and 58 cm2 V−1 s−1, respectively, which are obtained for a FET with channel thickness of 5 nm, WG of 20 μm and LG of 50 μm. We have also fabricated a FET with 3-nm-thick InN channel (WG of 50 μm and LG of 20 μm), in which “on”-current density is 6.8 mA/mm (VDS = 5 V, VG = 2 V). When the same voltages of VDS and VG are applied in the FETs with channel thickness of 2 and 5 nm, the drain current IDS is 0.048 and 23 mA/mm, respectively. These values increase nonlinearly with an increase in the channel thickness. For comparison, we have fabricated a 4-nm-thick hexagonal InN FET on semi-insulating GaN substrates. The device characteristics are shown in Supplementary Fig. S3. The FET shows poor “off”-characteristics, probably due to a defective interface between InN and GaN. This result indicates that the abrupt cubic-InN/YSZ interface is responsible for the good characteristics of the ultrathin-InN-based FETs.

(a) Output and (b) transfer characteristics of a cubic InN FET with a 2-nm-thick channel. The width and length of the gate are 50 and 20 μm, respectively. The IDS on/off ratio at VDS = 5 V is ~5 × 106. (c) Output and (d) transfer characteristics of a cubic InN FET with a 5-nm-thick channel. The width and length of the gate are 10 and 50 μm, respectively. The field-effect mobility in the linear region is calculated to be 44 cm2 V−1 s−1.

In conclusion, we have successfully fabricated FETs using ultrathin cubic InN channels. The FETs exhibited reasonable output and transfer characteristics that can be well explained by conventional FET theory. FETs fabricated with 2-nm-thick cubic InN exhibited high current on/off ratios of ~5 × 106 and quite low off current densities at the pA level. The use of highly insulating YSZ substrates and the formation of abrupt HfO2/InN/YSZ interfaces are responsible for the good off-state characteristics. Maximum values of IDS and μFE of the FETs fabricated with 5-nm-thick InN are greater than 60 mA/mm and 50 cm2 V−1 s−1, respectively. These results indicate that the use of ultrathin cubic InN is promising for the fabrication of future high-speed electron devices.

References

Tsen, K. T., Poweleit, C., Ferry, D. K., Lu, H. & Schaff, W. J. Observation of large electron drift velocities in InN by ultrafast Raman spectroscopy. Appl. Phys. Lett. 86, 222103 (2005).

Kuzmik, J. & Georgakilas, A. Proposal of High-electron mobility transistors with strained InN channel. IEEE Trans. Electron Devices 58, 720–724 (2011).

Lin, Y.-S. et al. High current density InN/AlN heterojunction field-effect transistor with a SiNx gate dielectric layer. Appl. Phys. Lett. 90, 142111 (2007).

Ng, Y. F., Cao, Y. G., Xie, M. H., Wang, X. L. & Tong, S. Y. Growth mode and strain evolution during InN growth on GaN(0001) by molecular-beam epitaxy. Appl. Phys. Lett. 81, 3960 (2002).

Wang, X. et al. High-electron-mobility InN layers grown by boundary-temperature-controlled epitaxy. Appl. Phys. Express 5, 015502 (2012).

Khan, N., Sedhain, A., Li, J., Lin, J. Y. & Jiang, H. X. High mobility InN epilayers grown on AlN epilayer templates. Appl. Phys. Lett. 92, 172101 (2008).

Lu, C. J., Bendersky, L. A., Lu, H. & Schaff, W. J. Threading dislocations in epitaxial InN thin films grown on (0001) sapphire with a GaN buffer layer. Appl. Phys. Lett. 83, 2817 (2003).

Wang, X., Che, S.-B., Ishitani, Y. & Yoshikawa, A. Threading dislocations in In-polar InN films and their effects on surface morphology and electrical properties. Appl. Phys. Lett. 90, 151901 (2007).

Piper, L. F. J., Veal, T. D., McConville, C. F., Lu, H. & Schaff, W. J. Origin of the n-type conductivity of InN: The role of positively charged dislocations. Appl. Phys. Lett. 88, 252109 (2006).

Honke, T., Fujioka, H., Ohta, J. & Oshima, M. InN epitaxial growths on Yttria stabilized zirconia (111) step substrates. J. Vac. Sci. Technol. A Vacuum, Surfaces, Film. 22, 2487 (2004).

Okubo, K., Kobayashi, A., Ohta, J., Oshima, M. & Fujioka, H. Electron mobility of ultrathin InN on yttria-stabilized zirconia with two-dimensionally grown initial layers. Appl. Phys. Lett. 102, 022103 (2013).

Sato, K., Ohta, J., Inoue, S., Kobayashi, A. & Fujioka, H. Room-temperature epitaxial growth of high quality AlN on SiC by pulsed sputtering deposition. Appl. Phys. Express 2, 011003 (2009).

Koblmüller, G., Gallinat, C. S. & Speck, J. S. Surface kinetics and thermal instability of N-face InN grown by plasma-assisted molecular beam epitaxy. J. Appl. Phys. 101, 083516 (2007).

Mahboob, I. et al. Origin of electron accumulation at wurtzite InN surfaces. Phys. Rev. B 69, 201307 (2004).

Author information

Authors and Affiliations

Contributions

H.F. supervised the project. M.O. and K.O. performed film growth and device fabrication. A.K., J.O. and H.F. designed the experimental procedure. All the authors interpreted the data and wrote the paper.

Ethics declarations

Competing interests

The authors declare no competing financial interests.

Electronic supplementary material

Supplementary Information

SUPPLEMENTARY INFO

Rights and permissions

This work is licensed under a Creative Commons Attribution-NonCommercial-NoDerivs 3.0 Unported License. To view a copy of this license, visit http://creativecommons.org/licenses/by-nc-nd/3.0/

About this article

Cite this article

Oseki, M., Okubo, K., Kobayashi, A. et al. Field-effect transistors based on cubic indium nitride. Sci Rep 4, 3951 (2014). https://doi.org/10.1038/srep03951

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/srep03951

This article is cited by

-

Fabrication of InGaN thin-film transistors using pulsed sputtering deposition

Scientific Reports (2016)

-

[0001]-Oriented InN Nanoleaves and Nanowires: Synthesis, Growth Mechanism and Optical Properties

Acta Metallurgica Sinica (English Letters) (2016)

-

Highly-efficient GaN-based light-emitting diode wafers on La0.3Sr1.7AlTaO6 substrates

Scientific Reports (2015)

-

Fabrication of full-color InGaN-based light-emitting diodes on amorphous substrates by pulsed sputtering

Scientific Reports (2014)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.