Abstract

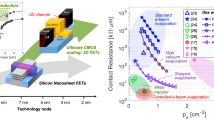

The International Roadmap for Devices and Systems (IRDS) forecasts that, for silicon-based metal–oxide–semiconductor (MOS) field-effect transistors (FETs), the scaling of the gate length will stop at 12 nm and the ultimate supply voltage will not decrease to less than 0.6 V (ref. 1). This defines the final integration density and power consumption at the end of the scaling process for silicon-based chips. In recent years, two-dimensional (2D) layered semiconductors with atom-scale thicknesses have been explored as potential channel materials to support further miniaturization and integrated electronics. However, so far, no 2D semiconductor-based FETs have exhibited performances that can surpass state-of-the-art silicon FETs. Here we report a FET with 2D indium selenide (InSe) with high thermal velocity as channel material that operates at 0.5 V and achieves record high transconductance of 6 mS μm−1 and a room-temperature ballistic ratio in the saturation region of 83%, surpassing those of any reported silicon FETs. An yttrium-doping-induced phase-transition method is developed for making ohmic contacts with InSe and the InSe FET is scaled down to 10 nm in channel length. Our InSe FETs can effectively suppress short-channel effects with a low subthreshold swing (SS) of 75 mV per decade and drain-induced barrier lowering (DIBL) of 22 mV V−1. Furthermore, low contact resistance of 62 Ω μm is reliably extracted in 10-nm ballistic InSe FETs, leading to a smaller intrinsic delay and much lower energy-delay product (EDP) than the predicted silicon limit.

This is a preview of subscription content, access via your institution

Access options

Access Nature and 54 other Nature Portfolio journals

Get Nature+, our best-value online-access subscription

$29.99 / 30 days

cancel any time

Subscribe to this journal

Receive 51 print issues and online access

$199.00 per year

only $3.90 per issue

Buy this article

- Purchase on Springer Link

- Instant access to full article PDF

Prices may be subject to local taxes which are calculated during checkout

Similar content being viewed by others

Data availability

The data that support the findings of this study are available from the corresponding author on reasonable request.

References

IEEE International Roadmap for Devices and Systems. https://irds.ieee.org/editions (2022).

Novoselov, K. S. et al. Electric field effect in atomically thin carbon films. Science 306, 666–669 (2004).

Liu, Y. et al. Promises and prospects of two-dimensional transistors. Nature 591, 43–53 (2021).

Radisavljevic, B., Radenovic, A., Brivio, J. & Kis, A. Single-layer MoS2 transistors. Nat. Nanotechnol. 6, 147–150 (2011).

Chhowalla, M., Jena, D. & Zhang, H. Two-dimensional semiconductors for transistors. Nat. Rev. Mater. 1, 16052 (2016).

Akinwande, D. et al. Graphene and two-dimensional materials for silicon technology. Nature 573, 507–518 (2019).

Wu, F. et al. Vertical MoS2 transistors with sub-1-nm gate lengths. Nature 603, 259–264 (2022).

Desai, S. B. et al. MoS2 transistors with 1-nanometer gate lengths. Science 354, 99 (2016).

Quhe, R. et al. Sub-10 nm two-dimensional transistors: theory and experiment. Phys. Rep. 938, 1–72 (2021).

Liu, L., Yang, L. & Guo, J. On monolayer MoS2 field-effect transistors at the scaling limit. IEEE Trans. Electron Devices 60, 4133–4139 (2013).

Yoon, Y., Ganapathi, K. & Salahuddin, S. How good can monolayer MoS2 transistors be? Nano Lett. 11, 3768–3773 (2011).

Li, W. et al. Uniform and ultrathin high-κ gate dielectrics for two-dimensional electronic devices. Nat. Electron. 2, 563–571 (2019).

Allain, A., Kang, J., Banerjee, K. & Kis, A. Electrical contacts to two-dimensional semiconductors. Nat. Mater. 14, 1195–1205 (2015).

Liu, Y. et al. Approaching the Schottky–Mott limit in van der Waals metal–semiconductor junctions. Nature 557, 696–700 (2018).

Wang, Y. et al. Van der Waals contacts between three-dimensional metals and two-dimensional semiconductors. Nature 568, 70–74 (2019).

Cho, S. et al. Phase patterning for ohmic homojunction contact in MoTe2. Science 349, 625–628 (2015).

McDonnell, S. et al. Defect-dominated doping and contact resistance in MoS2. ACS Nano 8, 2880–2888 (2014).

Gilardi, C. et al. Extended scale length theory for low-dimensional field-effect transistors. IEEE Trans. Electron Devices 69, 5302–5309 (2022).

Suryavanshi, S. V., English, C. D., Wong, H.-S. P. & Pop, E. Scaling theory of two-dimensional field effect transistors. Preprint at https://arxiv.org/abs/2105.10791 (2021).

Marin, E. G., Marian, D., Iannaccone, G. & Fiori, G. First-principles simulations of FETs based on two-dimensional InSe. IEEE Electron Device Lett. 39, 626–629 (2018).

Schauble, K. et al. Uncovering the effects of metal contacts on monolayer MoS2. ACS Nano 14, 14798–14808 (2020).

Zhu, J. et al. Argon plasma induced phase transition in monolayer MoS2. J. Am. Chem. Soc. 139, 10216–10219 (2017).

Zhu, Y. et al. Monolayer molybdenum disulfide transistors with single-atom-thick gates. Nano Lett. 18, 3807–3813 (2018).

Nourbakhsh, A. et al. MoS2 field-effect transistor with sub-10 nm channel length. Nano Lett. 16, 7798–7806 (2016).

Yang, L., Lee, R., Rao, S., Tsai, W. & Ye, P. D. in Proc. 2015 73rd Annual Device Research Conference (DRC) 237–238 (IEEE, 2015).

Pang, C.-S., Wu, P., Appenzeller, J. & Chen, Z. Sub-1nm EOT WS2-FET with IDS > 600 μA/μm at VDS = 1V and SS < 70 mV/dec at LG = 40 nm. IEDM Tech. Digest. 3.4.1–3.4.4 (2020).

Li, X. et al. High-speed black phosphorus field-effect transistors approaching ballistic limit. Sci. Adv. 5, eaau3194 (2019).

Shen, P. C. et al. Ultralow contact resistance between semimetal and monolayer semiconductors. Nature 593, 211–217 (2021).

Cheng, Z. et al. How to report and benchmark emerging field-effect transistors. Nat. Electron. 5, 416–423 (2022).

Javey, A. et al. Ballistic carbon nanotube field-effect transistors. Nature 424, 654–657 (2003).

Das, S., Chen, H.-Y., Penumatcha, A. V. & Appenzeller, J. High performance multilayer MoS2 transistors with scandium contacts. Nano Lett. 13, 100–105 (2013).

Auth, C. et al. A 10nm high performance and low-power CMOS technology featuring 3rd generation FinFET transistors, Self-Aligned Quad Patterning, contact over active gate and cobalt local interconnects. IEDM Tech. Digest 29.1.1–29.1.4 (2017).

Convertino, C. et al. InGaAs-on-insulator FinFETs with reduced off-current and record performance. IEDM Tech. Digest 39.2.1–39.2.4 (2018).

Jeon, J. et al. The first observation of shot noise characteristics in 10-nm scale MOSFETs. VLSI Tech. Digest 48–49 (2009).

Liow, T. et al. Carrier transport characteristics of sub-30 nm strained N-channel FinFETs featuring silicon-carbon source/drain regions and methods for further performance enhancement. IEDM Tech. Digest 1–4 (2006).

Barral, V. et al. Experimental determination of the channel backscattering coefficient on 10–70 nm-metal-gate double-gate transistors. Solid State Electron. 51, 537–542 (2007).

Natarajan, S. et al. A 14nm logic technology featuring 2nd-generation FinFET, air-gapped interconnects, self-aligned double patterning and a 0.0588 µm2 SRAM cell size. IEDM Tech. Digest 3.7.1–3.7.3 (2014).

Xie, R. et al. A 7nm FinFET technology featuring EUV patterning and dual strained high mobility channels. IEDM Tech. Digest 2.7.1–2.7.4 (2016).

Ahn, Y. & Shin, M. First-principles-based quantum transport simulations of monolayer indium selenide FETs in the ballistic limit. IEEE Trans. Electron Devices 64, 2129–2134 (2017).

Liu, L. et al. Uniform nucleation and epitaxy of bilayer molybdenum disulfide on sapphire. Nature 605, 69–75 (2022).

Wang, Y. et al. Many-body effect and device performance limit of monolayer InSe. ACS Appl. Mater. Interfaces 10, 23344–23352 (2018).

Xu, L. et al. Computational study of ohmic contact at bilayer InSe-metal interfaces: implications for field-effect transistors. ACS Appl. Nano Mater. 2, 6898–6908 (2019).

Uchida, K., Koga, J. & Takagi, S. Experimental study on carrier transport mechanisms in double- and single-gate ultrathin-body MOSFETs - Coulomb scattering, volume inversion, and /spl delta/T/sub SOI/-induced scattering. IEDM Tech. Digest 33.5.1–33.5.4 (2003).

Ahmadi, M. T. et al. Current–voltage characteristics of a silicon nanowire transistor. Microelectron. J. 40, 547–549 (2009).

Bandurin, D. A. et al. High electron mobility, quantum Hall effect and anomalous optical response in atomically thin InSe. Nat. Nanotechnol. 12, 223–227 (2016).

Geim, A. K. Graphene: status and prospects. Science 324, 1530–1534 (2009).

Liu, Y., Huang, Y. & Duan, X. F. Van der Waals integration before and beyond two-dimensional materials. Nature 567, 323–333 (2019).

Xie, L. et al. Graphene-contacted ultrashort channel monolayer MoS2 transistors. Adv. Mater. 29, 1702522 (2017).

Liu, Y., Duan, X., Huang, Y. & Duan, X. Two-dimensional transistors beyond graphene and TMDCs. Chem. Soc. Rev. 47, 6388–6409 (2018).

Qiu, C. et al. Scaling carbon nanotube complementary transistors to 5-nm gate lengths. Science 355, 271–276 (2017).

Ho, P. et al. High-mobility InSe transistors: the role of surface oxides. ACS Nano 11, 7362–7370 (2017).

Wells, S. A. et al. Suppressing ambient degradation of exfoliated InSe nanosheet devices via seeded atomic layer deposition encapsulation. Nano Lett. 18, 7876–7882 (2018).

Jiang, J. et al. Stable InSe transistors with high-field effect mobility for reliable nerve signal sensing. npj 2D Mater. Appl. 3, 29 (2019).

Kang, S., Movva, H. C. P., Sanne, A., Rai, A. & Banerjee, S. K. Influence of electron-beam lithography exposure current level on the transport characteristics of graphene field effect transistors. J. Appl. Phys. 119, 124502 (2016).

Arora, V. K. et al. High-field distribution and mobility in semiconductors. Jpn. J. Appl. Phys. 24, 537 (1985).

Chau, R. et al. Benchmarking nanotechnology for high-performance and low-power logic transistor applications. IEEE Trans. Nanotechnol. 4, 153–158 (2005).

Zhang, Z. Y. et al. High-performance n-type carbon nanotube field-effect transistors with estimated sub-10-ps gate delay. Appl. Phys. Lett. 92, 133117 (2008).

Khakifirooz, A., Nayfeh, O. M. & Antoniadis, D. A simple semiempirical short-channel MOSFET current–voltage model continuous across all regions of operation and employing only physical parameters. IEEE Trans. Electron Devices 56, 1674–1680 (2009).

Lundstrom, M. S. & Antoniadis, D. A. Compact models and the physics of nanoscale FETs. IEEE Trans. Electron Devices 61, 225–233 (2014).

Liu, Y., Luisier, M., Antoniadis, D., Majumdar, A. & Lundstron, M. S. On the interpretation of the ballistic injection velocity in deeply scaled MOSFETs. IEEE Trans. Electron Devices 59, 994–1001 (2012).

Rahman, A. & Lundstrom, M. S. A compact scattering model for the nanoscale double-gate MOSFET. IEEE Trans. Electron Devices 49, 481–489 (2002).

Knoch, J. & Appenzeller, J. Impact of the channel thickness on the performance of Schottky barrier metal–oxide–semiconductor field-effect transistors. Appl. Phys. Lett. 81, 3082 (2002).

Schulman, D. S., Arnold, A. J. & Das, S. Contact engineering for 2D materials and devices. Chem. Soc. Rev. 47, 3037–3058 (2018).

Sun, Z. et al. Statistical assessment of high-performance scaled double-gate transistors from monolayer WS2. ACS Nano 16, 14942–14950 (2022).

O’Brien, K. P. et al. Advancing 2D monolayer CMOS through contact, channel and interface engineering. IEDM Tech. Digest 7.1.1–7.1.4 (2021).

Chou, A.-S. et al. Antimony semimetal contact with enhanced thermal stability for high performance 2D electronics. IEDM Tech. Digest 7.2.1–7.2.4 (2021).

Sohn, A. et al. Precise layer control and electronic state modulation of a transition metal dichalcogenide via phase-transition-induced growth. Adv. Mater. 34, 2103286 (2022).

Asselberghs, I. et al. Wafer-scale integration of double gated WS2-transistors in 300mm Si CMOS fab. IEDM Tech. Digest 40.2.1–40.2.4 (2020).

Chang, H. et al. Synthesis of large-area InSe monolayers by chemical vapor deposition. Small 14, 1802351 (2018).

Arutchelvan, G. et al. Impact of device scaling on the electrical properties of MoS2 field-effect transistors. Sci. Rep. 11, 6610 (2021).

Su, S. K. et al. Layered semiconducting 2D materials for future transistor applications. Small Struct. 2, 2000103 (2021).

Smithe, K. H., English, C. D., Suryavanshi, S. V. & Pop, E. High-field transport and velocity saturation in synthetic monolayer MoS2. Nano Lett. 18, 4516–4522 (2018).

McClellan, C. J., Yalon, E., Smithe, K. K. H., Suryavanshi, S. V. & Pop, E. High current density in monolayer MoS2 doped by AlOx. ACS Nano 15, 1587–1596 (2021).

Chou, A. S. et al. High on-state current in chemical vapor deposited monolayer MoS2 nFETs with Sn ohmic contacts. IEEE Electron Device Lett. 42, 272–275 (2020).

Patel, K. A., Grady, R. W., Smithe, K. K. H., Pop, E. & Sordan, R. Ultra-scaled MoS2 transistors and circuits fabricated without nanolithography. 2D Mater. 7, 015018 (2020).

Datta, S. Electronic Transport in Mesoscopic Systems Ch. 2 (Cambridge Univ. Press, 1995).

Xia, F. et al. The origins and limits of metal–graphene junction resistance. Nat. Nanotechnol. 6, 179–184 (2011).

Agarwal, T. et al. Benchmarking of MoS2 FETs with multigate Si-FET options for 5 nm and beyond. IEEE Trans. Electron Devices 62, 4051–4056 (2015).

Acknowledgements

Funding for this work was provided by the National Key Research & Development Program of China (grant no. 2021YFA0717400) and the National Science Foundation of China (grant nos. 61888102, 61971009 and 62122006). We thank L.G. and F.M. (Institute of Physics, Chinese Academy of Sciences) for focused ion beam and STEM technique support.

Author information

Authors and Affiliations

Contributions

C.Q. and L.-M.P. proposed and supervised the project. J.J., C.Q. and L.-M.P. conceived the idea and designed the experiment. J.J. performed InSe material characterization, device fabrication and device characterization. L.X. provided the calculations and simulations based on DFT theory, TCAD models and compact models. J.J., C.Q., L.X. and L.-M.P. analysed the experimental and modelling results. J.J., C.Q., L.-M.P. and L.X. cowrote the manuscript. All authors commented on and discussed this work.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Nature thanks Peng Wu, Zhixian Zhou and the other, anonymous, reviewer(s) for their contribution to the peer review of this work. Peer reviewer reports are available.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Extended data figures and tables

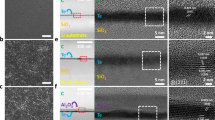

Extended Data Fig. 1 Structure characterization and schematic process flow of ballistic InSe FETs.

a, STEM image showing a top view of the atomic structure of few-layer InSe and corresponding selected electron diffraction pattern taken from the same InSe region. Scale bar, 2 nm. Inset, atomic structures of 2D InSe. Our InSe sample has an excellent crystal structure and an expected hexagonal lattice spacing of 3.4 Å without visible defects. b, Top-view SEM images of ballistic InSe FETs. Scale bar, 400 nm. c, Schematic process flow and structure of ballistic InSe FETs.

Extended Data Fig. 2 Benchmarking ID versus ns and TLM.

a, Benchmarking ID versus ns at VDS = 0.5 V (refs. 29,71,72,73,74,75). The numbers in parentheses is the channel length (nm). b, SEM image of a set of devices for TLM. c, Total resistance versus channel length, leading to a minimum value of 83 Ω μm. The fluctuation of resistances between different electrodes in the long channels leads to some inaccuracy in the extracted 2RC.

Extended Data Fig. 3 Comparison of transfer characteristics at various temperatures and Landauer formula.

a, Transfer characteristics of a ballistic non-optimal Schottky-barrier 2D InSe FET at various temperatures ranging from 300 to 100 K. b, Transfer characteristics of a ballistic ohmic-contact 2D InSe FET at various temperatures ranging from 300 to 100 K. c, Comparison of transfer characteristics of a ballistic ohmic-contact InSe FET and a ballistic non-optimal Schottky-barrier InSe FET at VDS = 0.3 V at 100 K. In a ballistic unoptimized Schottky-barrier InSe FET, the transfer curve exhibits two slopes below the threshold at low temperature. The lower part is exclusively thermionic emission (TE) current corresponding to carriers over the potential barrier, which is dominated by the channel. The upper part consists of thermionic emission and tunnelling current, also called thermal field emission (TFE). With an incremental change in VGS, the thermionic emission component changes only slightly owing to the Schottky-barrier effect. Also, the main increase in current is because of the tunnelling enhancement through squeezing the source Schottky barrier width and therefore exhibits a poor SS62,63. d, Experimental and theoretical total resistances in ballistic InSe transistors. The red stars are the experimental total resistance from typical output characteristics (Fig. 1j) and the black line is the calculated total resistance of the quantum limit by Landauer’s approach (related to the number of modes)76,77.

Extended Data Fig. 4 Capacitance–voltage characteristics and CQ simulation.

a,b, Optical and SEM images of our metal–insulator–metal (MIM) structure for capacitance–voltage (C–V) characteristics. c, Schematic diagram of the MIM structure. d, Typical as-measured back-gate multifrequency C–V curves; 19 frequency curves are measured between 10 kHz and 1 MHz. e, Typical back-gate C–V hysteresis curve at a frequency of 1 MHz. f, The back-gate capacitance versus f (10 kHz to 1 MHz) for VGS = 0.1, 0.3, 0.5 and 0.7 V. g, Thirty MIM curves of back-gate capacitance versus f (10 kHz to 1 MHz) at VGS = 0.5 V. h, Typical as-measured top-gate multifrequency C–V curves; 19 frequency curves are measured between 10 kHz and 1 MHz. i, Typical top-gate C–V hysteresis curve at a frequency of 1 MHz. j, The top-gate capacitance versus f (10 kHz to 1 MHz) for VGS = 0.1, 0.3, 0.5 and 0.7 V. k, Thirty MIM curves of top-gate capacitance versus f (10 kHz to 1 MHz) at VGS = 0.5 V. l, Simulated CQ versus VGS − VT, for a 10-nm InSe FET at VDS = 0 V and 0.5 V.

Extended Data Fig. 5 Transconductances of ballistic InSe FETs.

a, Transfer characteristics for ten typical ballistic InSe FETs at VDS = 0.5 V. The dashed line is the theoretically calculated transfer curve39. b, Corresponding transconductance of ten typical ballistic InSe FETs at VDS = 0.5 V. The best transconductance is 6 mS μm−1. Six FETs have transconductances exceeding 4 mS μm−1. The dashed line is the theoretically calculated transconductance39. c,d, Transfer curve and output of a typical ballistic InSe FET (with a transconductance of 6 mS μm−1). e, Transfer characteristics of a typical ballistic 2D InSe FET with 20-nm channel length at VDS = 0.1, 0.3, 0.5 and 0.7 V. f, Transfer characteristics comparison of ballistic 2D InSe FET at VDS = 0.5 and 0.7 V (coloured dots), 10-nm-node silicon FinFET (Intel, solid black line) and 20-nm-LG InGaAs FinFET normalized by state-of-the-art Fin Pitch = 34 nm (IBM, dashed black line). Note that all currents are normalized with the same rule. g, Transconductances comparison of typical ballistic 2D InSe FETs, a 10-nm-node silicon FinFET (Intel, solid black line) and an InGaAs FinFET (IBM, dashed black line). h, Transconductances comparison of ballistic 2D InSe FET at VDS = 0.5 and 0.7 V and other 2D FETs with sub-50-nm LG at VDD = 1 V. It shows that the transconductance of our InSe FETs at VDS = 0.7 V reaches 7 mS µm−1, which is larger than that of silicon FETs at the same bias voltage of VDS = 0.7 V but with slight degraded off-leakage current and subthreshold slope. The large transconductances of our 2D-InSe FETs benefit from several features of our FETs, including the ballistic channel with hardly any scatterings, higher thermal velocity, better source and drain contacts with negligible Schottky barriers and 2.6-nm-thick HfO2 double-gate structure.

Extended Data Fig. 6 Virtual Source Model fitting of output characteristics of InSe FETs.

Comparison of the Virtual Source Model fitting (hollow circles) and measured data (lines) for output characteristics of InSe FETs with LG = 10 nm (a) and LG = 20 nm (b). These results correspond to the red stars in Fig. 3e. To obtain an accurate Virtual Source Model fitting to extract the values of ballistic ratios, here a small gate voltage step of 0.1 V is used during output measurements.

Extended Data Fig. 7 Inner spacer structure and TCAD simulation.

a, Schematic diagram of a proposed process to achieve self-aligned (overlap-free) double-gate structure with low-k inner spacer and the process is compatible with the Y-doping ohmic contact. b,c, TCAD simulation of electron density distribution on the extension surfaces between the gate and the source/drain in ballistic InSe FETs with different k of the spacer. d, Schematic diagram of the ballistic InSe FETs with and without overlap from TCAD. e, The TCAD simulations of transfer curves of ballistic InSe FETs with (red) and without (black) overlap. f, On-state current density versus doping concentration of the ungated region below the spacer.

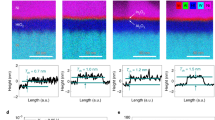

Extended Data Fig. 8 Transfer characteristics of typical ballistic InSe FETs and InSe thickness dependence of FET characteristics.

a, Transfer characteristics of five typical ballistic InSe FETs with LG = 10 nm, including SS and DIBL. b, Transfer characteristics of five typical ballistic InSe FETs with LG = 20 nm, including SS and DIBL. c, Typical AFM height profile of InSe samples, corresponding to 1, 3, 6, 13 and 22 layers. d, Dependence of the transfer characteristics of FETs on InSe channel thicknesses as in c. The reason for choosing the three-layer InSe channel material is that the monolayer InSe channel material has several basic limitations. (1) Monolayer InSe is more sensitive to the external environment and processing process than the three-layer InSe, so the on-state current and SS of the fabricated monolayer InSe FETs are degraded to some extent (Extended Data Fig. 8d). (2) The intrinsic electrical properties (thermal velocity etc.) of monolayer InSe are lower than those of the three-layer InSe channel (Fig. 1a) and, in addition, quantum-transport simulations also show that the transistors based on few-layer 2D semiconductors have higher on-state currents than those of monolayer 2D counterparts40,78.

Extended Data Fig. 9 Ballistic InSe FETs with single-top-gate, single-back-gate and dual-gate structures.

a,b, TCAD simulations of single-top-gate, single-back-gate and double-gate structures with 2.4-nm-thickness InSe channel and 10-nm gate length. The green transfer curve is the single-top-gate InSe FET, the blue transfer curve is the single-back-gate InSe FET and the red transfer curve is the dual-gate InSe FET. c, The experiment of the single-top-gate, the single-back-gate and the double-gate structures with 2.4-nm-thickness InSe channel and 20-nm channel length. The green transfer curve is the single-top-gate InSe FET, the blue transfer curve is the single-back-gate InSe FET and the red transfer curve is the dual-gate InSe FET. d, Top-view SEM images of ballistic InSe FETs with the single back gate (before top-gate fabrication) and the dual gate (after top-gate fabrication). e,f, The transfer characteristics of the typical ballistic 10-nm-channel-length InSe FETs with the single back gate (before top-gate fabrication, blue curves) and the dual gate (red curves). g,h, The transfer characteristics of the typical ballistic 20-nm-channel-length InSe FETs with the single back gate (before top-gate fabrication, blue curves) and the dual gate (red curves).

Extended Data Fig. 10 Electrical stability of ballistic 2D InSe FETs.

a, Transfer characteristics of a ballistic back-gate InSe FET without encapsulation in ambient conditions. b, Transfer characteristics of a ballistic double-gate InSe FET with top-gate encapsulation in ambient conditions. c, Transfer characteristics of a ballistic double-gate InSe FET before and after annealing at 250 °C for 1 h. LCH = 10 nm and VDS = 0.5 V. d, Output characteristics of the ballistic double-gate InSe FET before and after annealing at 250 °C for 1 h. LCH = 10 nm. Atomic thin InSe semiconductor is sensitive to moisture in the air and will suffer from a certain degree of degradation51,52,53. However, in previous reports, passivated InSe FETs encapsulated with hexagonal boron nitride45, a high-quality dry oxide51, high-k dielectric layer52 or PMMA53 show high stability and can be maintained for a long time. Here we adopt the double-gate structure, including HfO2/Ti/Au top-gate stacks. The high-k dielectric and top-gate metal covered on the InSe surface act as a passivation layer, which can effectively isolate moisture and oxygen in the air and improve the FETs’ stability.

Supplementary information

Supplementary Information

This file contains Supplementary Figures 1–13 and Supplementary References

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Jiang, J., Xu, L., Qiu, C. et al. Ballistic two-dimensional InSe transistors. Nature 616, 470–475 (2023). https://doi.org/10.1038/s41586-023-05819-w

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1038/s41586-023-05819-w

This article is cited by

-

Deciphering the ultra-high plasticity in metal monochalcogenides

Nature Materials (2024)

-

Robust multiferroic in interfacial modulation synthesized wafer-scale one-unit-cell of chromium sulfide

Nature Communications (2024)

-

Three-dimensional integration of two-dimensional field-effect transistors

Nature (2024)

-

Mechanism of plastic deformation in metal monochalcogenides

Nature Materials (2024)

-

2D materials for logic device scaling

Nature Materials (2024)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.