Abstract

The scaling of transistors with thinner channel thicknesses has led to a surge in research on two-dimensional (2D) and quasi-2D semiconductors. However, modulating the threshold voltage (VT) in ultrathin transistors is challenging, as traditional doping methods are not readily applicable. In this work, we introduce a optical-thermal method, combining ultraviolet (UV) illumination and oxygen annealing, to achieve broad-range VT tunability in ultrathin In2O3. This method can achieve both positive and negative VT tuning and is reversible. The modulation of sheet carrier density, which corresponds to VT shift, is comparable to that obtained using other doping and capacitive charging techniques in other ultrathin transistors, including 2D semiconductors. With the controllability of VT, we successfully demonstrate the realization of depletion-load inverter and multi-state logic devices, as well as wafer-scale VT modulation via an automated laser system, showcasing its potential for low-power circuit design and non-von Neumann computing applications.

Similar content being viewed by others

Introduction

The field-effect transistor (FET) is a fundamental component in modern electronics. The threshold voltage (VT) of a FET is a key parameter that determines its electronic functions, not only defining its switching modes but also scaling the supply voltage in the logic gates. In modern circuits, transistors are often tailored with different VT during the manufacturing process to enhance performance and lower power consumption. The ability to precisely control the VT of a transistor allows it to be used as a memory element, such as flash memory. In recent years, beyond-binary tunability between the “1” and “0” states has become particularly interesting in post–von Neumann applications, such as neuromorphic computation1,2, multi-state memory3,4 and multiplexed sensing5. The capacity to finely tune VT over a wide range is crucial for these applications, as it directly impacts the storage capacity and weight precision of associated devices. It enables the development of advanced technologies that can perform complex tasks and have a wide range of applications in fields such as artificial intelligence, machine learning, and the Internet of Things (IoT).

Atomically thin semiconductors, including two-dimensional and other quasi-2D materials, have shown great potential to develop beyond-silicon electronics. Indium oxide (In2O3) recently emerged as a promising channel material for FETs as it can be thinned down to 1 nm and maintains high electron mobility beyond 100 cm2 V–1 s–1, showing high on-state drain current density ID > 20 A mm−1 (refs. 6,7). This advancement allows for the scaling of In2O3 to align with modern technology nodes, and is expected to complement silicon-based systems for future back-end-of-line (BEOL) integration, expanding its range of applications beyond display technology. Moreover, In2O3 exhibits high potential to engineer the VT as a benefit generally granted to the oxide semiconductors (OS)8. In modern FETs, VT is tuned during fabrication by adjusting the implanted dopant concentration or by modifying the work function of the gate. To enable dynamic control over VT, additional charge-trapped layers are required, e.g., a floating gate9,10. In OS-based FETs, VT can be tuned by various approaches such as post-fabrication thermal annealing11,12, chemical doping13, passivation14, metal decorations15, and incorporating a gate electrode with selected work functions16, etc. It is known that vacancy-related surface effects play a crucial role in altering the charge carrier density of the OS, leading to the ease of VT tunability. Even though the vacancy-related surface effects can be easily controlled, scalable VT modulation with fine control over wide ranges is still challenging.

In this work, we report wide-range VT tunability in ultrathin In2O3 FETs achieved via a simple optical-thermal combined method. The method involves alternating ultraviolet (UV) illumination and oxygen annealing to achieve negative and positive VT tuning, respectively. The VT of a 2 nm-thick In2O3 transistor (30 nm-thick SiO2 as the dielectric) exhibits a tunable window of 20 V with a resolution of 0.05 V, equivalent to a maximum change of sheet carrier density (n2D) from 2\(\times\)1010 cm−2 to 2\(\times\)1012 cm−2 with a resolution of 109 cm−2. Importantly, this method is an entire post-fabrication process, and the VT modulation is reversible. We show that the VT of distributed transistors in a circuit can be selectively tuned, enhancing the gain of a depletion-load inverter by an order of magnitude. Exploiting the spatial VT tunability, we show that such local control of VT can be used to pattern the VT profile in a channel of a transistor to enable multi-step transfer characteristics, advocating potential for innovative logic design and neuromorphic applications. To further demonstrate the wafer-scale practicality, we fabricated In2O3 transistors on a 4-inch wafer and utilize the industry-level laser illumination system to achieve automatic large-area VT tuning for selected In2O3 transistors across the entire wafer.

Results and discussion

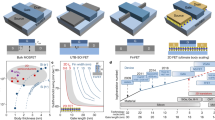

Indium has been utilized across a variety of applications (element scarcity is shown in Supplementary Table 1), including displays (e.g., IGZO), transparent electrodes (e.g., ITO), and solar cells (e.g., CIGS). In this study, ultrathin In2O3 is employed as the channel material of a transistor, as shown schematically in Fig. 1a. The transistor is fabricated using atomic layer deposition (ALD) to form a 2–4 nm In2O3 layer on p++Si substrates with a 30 nm-thick SiO2. Nickel is used as the source and drain contacts. It is important to note that the entire fabrication process is compatible with back-end-of-line (BEOL) CMOS processes, as it is carried out below the thermal budget of 300 °C (“Methods”)17. The high-resolution transmission electron microscopy (HRTEM; Supplementary Fig. 1) image reveals the amorphous nature and the atomic level uniformity of the In2O3 films is confirmed by AFM (Supplementary Fig. 2), which effectively accounts for the minimal device-to-device variation (Supplementary Fig. 3). It has been shown that In2O3 shows high electron mobilities even in an amorphous phase18. This is because the electronic property of OS is insensitive to crystallinity. Their transport is determined by the overlapping of s orbitals between neighboring metal atoms (e.g., indium) and is less affected by structural disorders8. The Tauc plot extracted from absorption spectra (Fig. 1b and Supplementary Fig. 4) shows that the bandgap of In2O3 increases with decreasing channel thickness (tch), from 2.7 eV (tch = 4 nm) to 3 eV (tch = 2 nm) due to the enhanced quantum confinement effect. This finding is similar to the layer-dependent bandgap changes observed in 2D materials, revealing the quasi-2D feature of the ultrathin In2O3 films19.

a Schematic of a 2 nm In2O3 transistor. The inset shows the HRTEM image of the ALD-deposited ultrathin In2O3 films. The scale bar is 5 nm. b Tauc plot of the In2O3 films as a function of film thickness. The fitting of the curve is done based on the Tauc model (α: absorption coefficient; h: Planck’s constant; ν: frequency of vibration). c Transfer curves of 2 nm In2O3 transistors with channel width/length of 10/2 µm and annealed under N2 and O2 for 30 min at 150 °C. Note that the amounts of threshold voltage (VT) shifts are saturated after 30 minutes (ID: drain current; VD: drain voltage; VG: gate voltage).

Figure 1c shows the transfer characteristics (ID–VG) of 2 nm In2O3 transistors annealed at 200 °C in O2 and N2 environments. The transfer characteristics (ID–VG) of In2O3 below 2 nm is shown in Supplementary Fig. 5 and saturation behavior (ID–VD) is shown in Supplementary Fig. 6. O2 and N2 annealing lead to VT shifts to +6 V and −20 V, respectively; both show effective tuning of VT after 30 min of annealing (the VT extraction method is described in the “Methods” section). While the traditional annealing method can effectively tune the VT of In2O3 transistors, precise control of VT over the tuning range is difficult. Figure 2a illustrates the proposed approach to achieve fine-tuning of VT in ultrathin In2O3 transistors. The device is first subjected to O2 annealing, which shifts the VT to +6 V. Subsequent UV irradiation (365 nm) on In2O3 transistors shifts the VT to the negative values (Fig. 2b), where the magnitude of VT shifts depends on the exposure time, incident power density and wavelength (Fig. 2c and Supplementary Figs. 7 and 8). Note that UV exposure causes an accumulation of VT shift, leading to a saturation point of −15 V with a tuning resolution of 0.05 V within a tunable window ΔVT of 21 V (Supplementary Fig. 9). To verify reproducibility of our approach, we tested devices with identical fabrication processes but different metal contacts (Pd, Pt) and substrates (10 nm HfO2 as the gate dielectric). All results exhibited consistent trends, regardless of substrate and metal contacts. (Supplementary Fig. 10). Importantly, the VT modulation using the proposed approach is reversible. UV-exposed In2O3 transistors with negative VT can be reset to have a value of 5 V after O2 annealing. Figure 3a shows repeated VT modulation achieved by multiple O2 annealing-UV exposure cycles. The field effect mobility (\({\mu }_{{FE}}\)) of the transistors is maintained at 49 ± 5 cm2 V–1 s–1, indicating that the properties of the In2O3 transistors are not significantly affected by the tuning VT processes (Fig. 3b). Additionally, we also conduct the bias stress experiment to investigate behavior and reliability of transistors under different bias conditions after the treatment of O2 annealing and UV exposure (Supplementary Fig. 11). A gate voltage was applied at ±15 V for 1000 s, with both source and drain grounded. The transfer characteristics of the device are immediately measured (<1 s) after bias stress. Furthermore, to evaluate the potential damage caused by laser exposure, we performed finite element simulations to analyze the temperature changes. The results indicate only a slight increase in temperature at the applied incident power densities (Supplementary Fig. 12).

a A schematic of VT tuning in ultrathin In2O3 transistors through UV exposure combined with thermal annealing; the inset is the microscopic image of the transistor with a scale bar of 5 µm. b Transfer curves of 2 nm In2O3 transistors with channel width/length of 10/2 µm after post treatments. The arrow represents the transition of transfer curves with UV light exposure (red lines) and O2 annealing (blue lines) (ID: drain current; VD: drain voltage; VG: gate voltage). c A contour plot of VT shifts as a function of UV exposure time and power density. Devices were annealed at 150 °C in O2 for 30 min to reset the VT before each UV exposure measurement. The absorbed power density increasing from 1\(\times\)106 mW cm−2 to 1\(\times\)108 mW cm−2 for exposure times from 30 s to 300 s under 365 nm laser illumination. The measurement time interval is 30 s and the transfer characteristics of the device are immediately measured (<5 s) after UV illumination. The plot consists of 7 different power densities and 10 different exposure times.

a VT of a 2 nm In2O3 transistor with channel width/length of 10/2 µm during multiple O2 annealing and UV exposure cycles. In2O3 transistors are thermally annealed under O2 for 30 min, followed by UV illumination under a power density of 1 mW cm−2. The blue triangles are the VT after O2 annealing. The red triangles are the VT after UV exposure. The dashed lines separate different switching cycle and the shaded areas represent the treatments (blue: O2 annealing; red: UV exposure). b The field effect mobility (\({\mu }_{{FE}}\)) of ultrathin In2O3 transistors as a function of VT tuned by the proposed method.

The size of the tunable window ΔVT is dependent on the thickness of the In2O3, as shown in Fig. 4a, b (VT shift as a function of channel length is shown in Supplementary Fig. 13). In2O3 with a thickness of 4 nm shows the largest tunable window, whereas In2O3 with a thickness of 2 nm is capable of being tuned between the enhancement mode (VT > 0 V) and the depletion mode (VT < 0 V). The offsets of tunable window for different thickness can be explained by the quantum confinement effect on the trap-neutral level model19. Fermi level is located deeply inside the conduction band for thicker In2O3 and aligns within the bandgap for thinner In2O3 as the bandgap is enlarged due to the enhanced quantum confinement effect.

a The range of the tunable window of In2O3 transistors with various In2O3 thicknesses, channel width/length of 10/2 µm. b The range of VT after treatment. c Benchmark of sheet carrier density (n2D) for different classes of ultrathin semiconductors with different thicknesses20,21,22,23,24,25,26,27,28,29,30, calculated using both the Drude model and the parallel-plate capacitor model. The shaded areas represent different classes of materials (red: In2O3; purple: monolayer 2D materials). d The Δn2D for different classes of ultrathin semiconductors based on capacitively charged structures. Shaded area represents different material categories (red: In2O3; green: ferroelectric memories; yellow: flash memories).

To further quantify the VT shift, we extract 2D carrier density (\({n}_{2D}\)) using the Drude model \({n}_{2D}={I}_{D}L/({qW}{V}_{D}{\mu }_{{FE}})\), where q is the electron charge, ID is the source-drain current at zero gate voltage, VD is the source-drain voltage, and μ is the field effect carrier mobility. Based on the Drude model, we benchmark our method against other VT tuning methods used in different classes of ultrathin semiconductors. Figure 4c shows the n2D of 2D semiconductors modulated by various chemical doping schemes20,21,22,23,24,25,26,27,28,29,30, which ranges from 1012 to 1013 cm−2 depending on the doping methods and materials (details in Supplementary Table 2). The tunable ranges of n2D achieved in In2O3 transistors vary from 1010 cm−2 to 1013 cm−2 depending on the thickness. 2 nm In2O3 exhibits the widest n2D tunable window (2\(\times\)1010 cm−2 to 2\(\times\)1012 cm−2), indicating the proposed method is competitive among various 2D doping techniques. The proposed methods offer a comparable effect to chemical doping, while providing the advantages of reversibility and area selectivity. In contrast to the substantial challenges associated with chemical doping in 2D materials, our method showcases the ease of achieving effective carrier concentration tuning in ultrathin In2O3. Moreover, our approach minimizes fabrication processes, thereby enhancing its potential for seamless integration in BEOL applications.

Another commonly used approach to control the VT of a transistor is through device design, usually done by inserting a layer that can be capacitively charged. For instance, flash memories store charge in a charge-trapping layer to modulate VT through the trapping and de-trapping process. Similarly, ferroelectrics modulate VT by controlling the polarization of a ferroelectric layer. The density of stored charge carriers n2D is around 1012 cm−2 to 1013 cm−2 for graphene and related 2D materials-based flash memories and ferroelectric memories. The Δn2D for In2O3 extracted by the parallel-plate capacitor model (1.5\(\times\)1013, 2.3\(\times\)1013 and 2.8\(\times\)1013 cm−2 for 2, 3 and 4 nm, respectively) is of the same order as flash memories and ferroelectric memories without extra gates (Fig. 4d)9,31,32,33,34,35. The details of 2D-based charge-storing schemes are summarized in Supplementary Table 3. Compared to other 2D doping and capacitively charged techniques, the proposed method demonstrates a more effective way to largely tune the carrier density in In2O3 transistors, enabling In2O3 transistors for innovative circuit and memory applications.

We conducted cyclically annealing between N2 and O2 environments to investigate the mechanism (Supplementary Fig. 14). The results demonstrate that the VT shift by N2 and O2 annealing is reversible, similar to the reversibility observed in UV exposure and O2 annealing processes. This result implies that the mechanisms underlying these two approaches may be identical. It is known that electronic properties of amorphous In2O3 can be altered by oxygen-related defects such as oxygen vacancies and oxygen adatoms on the surface36. Oxygen vacancies act as shallow donors and contribute to the spontaneous n-type conductivity of the In2O3 (the shallow donor level is observed in scanning tunneling microscopy (STS) shown in Supplementary Fig. 15). Oxygen adatoms, on the other hand, act as acceptor-like traps that counter-dope the n-type OS. Annealing in oxygen-rich or oxygen-scarce (N2 or vacuum) environments causes a rebalance of physically adsorbed oxygen adatoms, leading to positive and negative VT shifts, respectively. Furthermore, exposure to UV light generates holes that neutralize the negatively charged oxygen adatoms, resulting in their detachment and a decrease in the VT. This proposed mechanism is supported by the measurement of VT retention in different atmospheres, as shown in Supplementary Fig. 16. Additionally, the VT exhibits almost no change over time in an ultra-high vacuum environment (10−9 torr), which further highlights the crucial role of oxygen adatoms in this process. The results suggest that the stability could be improved by implementing effective isolation or passivation to minimize the exposure of In2O3 to the atmosphere.

Demonstration of depletion-load inverter and multi-step logic

The proposed method allows for precise control of VT, making it useful for advanced low-power circuits37. Here, we demonstrate a depletion-load inverter by adjusting the VT of the selected In2O3 transistors in a circuit, achieved by employing a micro-laser system that can focus UV exposure selectively on In2O3 transistors (details in “Methods”). Figure 5a illustrates the layout of an inverter circuit with two n-type In2O3 transistors connected by local bottom gates. Both transistors are set to enhancement mode via O2 annealing, resulting in a VT shift to +5 V. When VDD is applied, VOUT is limited as the channel resistance of the load transistor is large, resulting in a small gain of 2 for VDD = 3 V (Fig. 5b). After exposing the load transistor to UV light, tuning the selected transistor to depletion mode, the inverter becomes a depletion-load inverter with an enhanced gain of 18 (Fig. 5c). Note that the depletion load inverter serves as a proof of concept for our proposed technology. Integrating a complementary MOS configuration has the potential to further optimize the performance of inverters, resulting in reduced power consumption and improved spatial advantages. The functionality of the circuit is activated via the proposed method with local VT tunability, giving a higher degree of freedom to design and calibrate the circuit even after fabrication.

a A schematic and optical microscope image of In2O3 inverter (h: Planck’s constant; ν: frequency of vibration; VDD: drain voltage; VSS: source voltage; VIN: input voltage; VOUT: output voltage). b The voltage transfer characteristics of 2 nm In2O3 inverter with channel width/length of 10/2 µm before UV laser illumination. c The voltage transfer characteristics of In2O3 inverter of 2 nm In2O3 inverter with channel width/length of 10/2 µm after UV laser illumination. d A schematic of ultrathin In2O3 transistor with multi-state logic function (VG: gate voltage; ID: drain current; R1: resistance of first channel; R2: resistance of second channel; VT1: threshold voltage of first channel; VT2: threshold voltage of second channel). e, The transfer characteristics of In2O3 transistor with UV laser illumination on the specific area. f The transfer characteristics with the first-order derivative of log(ID) from e.

The ability to locally adjust the VT with high spatial resolution in In2O3 transistors allows for creating non-uniform VT patterns in the channel and enables new functions. We demonstrate that a reconfigurable In2O3 transistor can switch between binary and multi-state logic without the need for multiple gates38 or heterojunctions39. Figure 5d illustrates a transistor with uniform VT along the channel detailed in Supplementary Fig. 17. After UV exposure on the selected area, non-uniform VT pattern forms on the channel. The equivalent circuit configuration changes depending on the scanning pathways, consisting of parallel resistors and transistors with different VT depending on the exposure time. As a result, a single swing in transfer characteristics turns to double-swing characteristics (Fig. 5e, f), increasing the information capacity of a single transistor. The demonstration of an In2O3-based multi-state logic device introduces an alternative strategy to design reconfigurable multifunctional logic circuits and has the potential for neuromorphic applications (Supplementary Fig. 18)40,41.

Wafer-scale V T modulation

To further demonstrate the practicability of our technique, we fabricated In2O3 transistors on a 4-inch wafer (Fig. 6a) and employed an automated laser illumination system (Laser Lift-Off System; K-JET LASER TEK Inc.) for large-scale VT tuning (Fig. 6b). The system allows for precise alignment to direct focused flat-top illumination onto selected devices, enabling localized VT modulation (Fig. 6c, Supplementary Movie 1 and tool details in Methods). We demonstrate the scalability by tuning VT for 450 transistors in an 18 \(\times \) 25 array (Fig. 6d). The initial VT was set to ~7 V through O2 annealing for all transistors (Fig. 6e), and the VT of the laser-exposed transistors were tuned to negative values (Fig. 6f). The transfer curves after VT modulation were shown in Fig. 6g, demonstrating the consistency of the proposed approach. The VT of unexposed transistors remained the same after the large-area tuning, as shown in Fig. 6h. The \({\mu }_{{FE}}\) distribution shows that the mobility increases slightly after UV exposure (Fig. 6i), in agreement with previous results. Note that the device-to-device variation, induced by the variation in film quality across the wafer, may potentially be mitigated through the utilization of industrial-level ALD tools. Furthermore, the VT tuning precision could be improved by the incorporation of patterned photomasks. This demonstration not only shows capability of wafer-scale fabrication and VT tuning on multiple transistors, but also opens up possibilities for enhancing circuit functionality beyond VT adjustment.

a An image of ultrathin In2O3 transistor arrays on a 4-inch wafer. The scale bar is 1 cm. b Schematics of the automated laser illumination system used for VT modulation. c An optical microscope image of UV laser exposure on the designated channel area. The inset is the illustration of flat-top laser beams. The scale bar is 50 µm. d An optical microscope image of the basic array unit on 4-inch wafer consisted of an 18\(\,\times \,\)25 array (450 transistors). The scale bar is 200 µm. e A contour plot showing the VT of the transistors in the array before VT tuning. f A contour plot showing the VT of the transistors in the array after VT tuning. g The transfer curves of the devices with channel width/length of 10/2 µm in the array after VT tuning (red line: UV exposed areas; blue line: unexposed area). h The histogram of VT of the devices in the array after VT tuning. i The histogram of \({\mu }_{{FE}}\) of the devices in the array after VT tuning.

In summary, we demonstrate the wide-range VT tunability in ultrathin In2O3 using an optical–thermal method. This approach is comparable to doping and capacitively charged techniques used in other ultrathin semiconductors and avoids the need for external dopants and complex processes. Our demonstration of a depletion-load inverter suggests that this VT tuning method has the potential to enable new functionalities in combinational logic circuits. Additionally, we have demonstrated a single device with multi-state logic function, which opens up new possibilities for the design of multifunctional logic circuits and non-von Neumann computing. Moreover, we conducted large-scale VT modulation using an industry-level tool to highlight the practical applicability of this method alongside individual device testing.

Methods

Device fabrication

The device fabrication started with a standard wet and dry pre-clean of 300 mm Si substrate. The highly phosphorus-doped Si, which carrier density is over 1021 cm−3, was grown on Si substrate as a global back-gate. Then, 30 nm SiO2 was deposited by ALD at 260 °C with (H2Si[N(C2H5)2]2) as the precursor. Afterwards, In2O3 thin films with different thicknesses were deposited by ALD at 200 °C using (CH3)3In (TMIn) and O3 as indium (In) and oxygen (O) precursors. The active areas of In2O3 were defined by lithography with HCl etching with the channel width/length of 10/2 µm. Standard lithography patterning and lift-off procedures were performed to contact the In2O3 thin films with metal electrodes. 40 nm Ni was deposited by e-beam evaporation on In2O3 to serve as source/drain ohmic contacts.

Inverter fabrication

The inverter fabrication started with a standard wet and dry pre-clean of 250 mm Si with a 50 nm SiO2 substrate. Then, the local back gate of 40 nm Ni was deposited by e-beam evaporation. Afterwards, 6 nm HfO2 was deposited by ALD at 250 °C with TDMAHf as a precursor for 70 cycles. After the gate dielectric deposition, 2 nm In2O3 thin films were deposited by ALD at 200 °C using (CH3)3In (TMIn) and O3 as In and O precursors. The active areas of In2O3 were defined by lithography with HCl etching for 5 s. Then, the contact holes were patterned by standard lithography, followed by BOE etching for 5 min. Finally, a Ni (40 nm) film was deposited by e-beam evaporation to serve as source/drain ohmic contacts and metal line interconnections.

Device characterization

As-grown In2O3 was then measured for thickness using a transmission electron microscope (TEM). A focused ion beam (FIB) system (Auriga, Carl Zeiss) was used to fabricate the cross-sectional specimen, which was then examined by a TEM (none-Cs Metrios). The electronic characteristics were measured by an Agilent B2902B source. The \({\mu }_{{FE}}\) and VT of ultrathin In2O3 transistors were determined in linear regime using conventional MOSFET equation for \({V}_{D}\ll {V}_{G}-{V}_{T}\): \({I}_{D}=\frac{W}{L}{\mu }_{{FE}}{C}_{{OX}}({V}_{G}-{V}_{T}){V}_{D}\), where COX is the oxide capacitance. The result of \({\mu }_{{FE}}\) can be obtained from \({\mu }_{{FE}}=\frac{L{g}_{m}}{W{C}_{{OX}}{V}_{D}} \), where gm is maximum transconductance. The resulted VT was determined by linear extrapolation, which was conducted by plotting ID versus VG, extrapolating from maximum transconductance (gm) to ID = 0 and adding VD/2 to obtain the intercept at VG axis.

Laser exposure

The 365 and 532 nm laser beams were generated by diode lasers (RGB Laser systems, Lambda Beam). The laser light passes through a shutter (NM Laser Product, LST-5VDC) to control the laser exposure time. Following the shutter, an ND filter was used to control the laser incident power. After that, the laser beam (365, 532 nm) was focused on the device through a fixed optical path using a ×50 objective lens (OLYMPUS, LMPlanFL N ×50, NA = 0.5) with a laser spot diameter of ~10 μm. Meanwhile, the absorbed power was measured by a power meter which comprised a detector (Thorlab, S120VC) and a meter (Thorlab, PM100D).

Thermal annealing

The fabricated devices were placed in a customized chamber with two gas inlets. Then, the devices were annealed in O2 and N2 with 1 liter per minute gas flow for 30 min at 150 °C. The pressure was kept at about 1 atm.

Absorption spectra

The In2O3 films were deposited on a 200 μm-thick glass substrate following the same ALD process as mentioned before. An ellipsometer determined the thickness of In2O3 films for absorption measurement. A Hitachi U-4100 spectrophotometer was used to investigate the transmittance of samples between the 300 and 700 nm range with an integrating sphere. Absorptance of the films was calculated using the relation A = 100 − (T + R).

Wafer-scale V T modulation

Wafer-scale VT modulation was achieved using an automatic laser illumination tool (Laser Lift-Off System; K-JET LASER TEK Inc.). The laser spot size and shape can be customized by a mask based on our specific needs, allowing for arbitrary adjustments. The laser intensity is uniformly distributed across the entire exposure area (20 µm \(\times \) 1 µm for this study), commonly known as flat-top beams, achieved via applying a mask on the optical path to ensure consistent laser exposure within the targeted region. Laser pulses with energy of 0.0015 J/cm2, a wavelength of 365 nm, and a pulse width of 26 ns were directed onto the desired regions or devices. The scanning rate is ~1 ms/transistor.

Data availability

Relevant data supporting the key findings of this study are available within the article and the Supplementary Information file. All raw data generated during the current study are available from the corresponding authors upon request.

References

Seo, S. et al. Artificial optic-neural synapse for colored and color-mixed pattern recognition. Nat. Commun. 9, 1–8 (2018).

Lee, M. et al. Brain‐inspired photonic neuromorphic devices using photodynamic amorphous oxide semiconductors and their persistent photoconductivity. Adv. Mater. 29, 1700951 (2017).

Shen, H. et al. Multistate memory enabled by interface engineering based on multilayer tungsten diselenide. ACS Appl. Mater. Interfaces 12, 58428–58434 (2020).

Ríos, C. et al. Integrated all-photonic non-volatile multi-level memory. Nat. Photonics 9, 725–732 (2015).

Fahad, H. M. et al. Room temperature multiplexed gas sensing using chemical-sensitive 3.5-nm-thin silicon transistors. Sci. Adv. 3, e1602557 (2017).

Si, M., Lin, Z., Chen, Z. & Peide, D. Y. First demonstration of atomic-layer-deposited BEOL-compatible In2O3 3D Fin transistors and integrated circuits: high mobility of 113 cm2/V s, maximum drain current of 2.5 mA/μm and maximum voltage gain of 38 V/V in In2O3 inverter. In 2021 Symposium on VLSI Technology 1–2 (IEEE, 2021).

Zhang, Z. et al. A gate-all-around InO Nanoribbon FET with near 20 mA/m drain current. IEEE Electron. Device Lett. 43, 1905–1908 (2022).

Nomura, K. et al. Thin-film transistor fabricated in single-crystalline transparent oxide semiconductor. Science 300, 1269–1272 (2003).

Sup Choi, M. et al. Controlled charge trapping by molybdenum disulphide and graphene in ultrathin heterostructured memory devices. Nat. Commun. 4, 1–7 (2013).

Baeg, K. J., Noh, Y. Y., Sirringhaus, H. & Kim, D. Y. Controllable shifts in threshold voltage of top‐gate polymer field‐effect transistors for applications in organic nano floating gate memory. Adv. Funct. Mater. 20, 224–230 (2010).

Si, M., Charnas, A., Lin, Z. & Peide, D. Y. Enhancement-mode atomic-layer-deposited In2O3 transistors with maximum drain current of 2.2 A/mm at drain voltage of 0.7 V by low-temperature annealing and stability in hydrogen environment. IEEE Trans. Electron. Devices 68, 1075–1080 (2021).

Kikuchi, Y. et al. Device characteristics improvement of a-In–Ga–Zn–O TFTs by low-temperature annealing. Thin Solid Films 518, 3017–3021 (2010).

Chen, Y. et al. Polymer doping enables a two‐dimensional electron gas for high‐performance homojunction oxide thin‐film transistors. Adv. Mater. 31, 1805082 (2019).

Kim, T., Kim, M. J., Lee, J. & Jeong, J. K. Boosting carrier mobility in zinc oxynitride thin-film transistors via tantalum oxide encapsulation. ACS Appl. Mater. Interfaces 11, 22501–22509 (2019).

Lien, D.-H., Retamal, J. R. D., Ke, J.-J., Kang, C.-F. & He, J.-H. Surface effects in metal oxide-based nanodevices. Nanoscale 7, 19874–19884 (2015).

Zan, H.-W. et al. Dual gate indium-gallium-zinc-oxide thin film transistor with an unisolated floating metal gate for threshold voltage modulation and mobility enhancement. Appl. Phys. Lett. 98, 153506 (2011).

Sedky, S., Witvrouw, A., Bender, H. & Baert, K. Experimental determination of the maximum post-process annealing temperature for standard CMOS wafers. IEEE Trans. Electron. Devices 48, 377–385 (2001).

Kamiya, T., Nomura, K. & Hosono, H. Origins of high mobility and low operation voltage of amorphous oxide TFTs: electronic structure, electron transport, defects and doping. J. Disp. Technol. 5, 273–288 (2009).

Si, M. et al. Why In2O3 can make 0.7 nm atomic layer thin transistors. Nano Lett. 21, 500–506 (2020).

Fang, H. et al. High-performance single layered WSe2 p-FETs with chemically doped contacts. Nano Lett. 12, 3788–3792 (2012).

Fang, H. et al. Degenerate n-doping of few-layer transition metal dichalcogenides by potassium. Nano Lett. 13, 1991–1995 (2013).

Jo, S. H. et al. A high‐performance WSe2/h‐BN photodetector using a triphenylphosphine (PPh3)‐based n‐doping technique. Adv. Mater. 28, 4824–4831 (2016).

Kiriya, D., Tosun, M., Zhao, P., Kang, J. S. & Javey, A. Air-stable surface charge transfer doping of MoS2 by benzyl viologen. J. Am. Chem. Soc. 136, 7853–7856 (2014).

Li, X. et al. Isoelectronic tungsten doping in monolayer MoSe2 for carrier type modulation. Adv. Mater. 28, 8240–8247 (2016).

Li, Y., Xu, C.-Y., Hu, P. & Zhen, L. Carrier control of MoS2 nanoflakes by functional self-assembled monolayers. ACS Nano 7, 7795–7804 (2013).

Liu, X. et al. P‐type polar transition of chemically doped multilayer MoS2 transistor. Adv. Mater. 28, 2345–2351 (2016).

Tang, B. et al. Direct n-to p-type channel conversion in monolayer/few-layer WS2 field-effect transistors by atomic nitrogen treatment. ACS Nano 12, 2506–2513 (2018).

Yang, L. et al. Chloride molecular doping technique on 2D materials: WS2 and MoS2. Nano Lett. 14, 6275–6280 (2014).

Zhang, S. et al. Controllable, wide‐ranging n‐doping and p‐doping of monolayer group 6 transition‐metal disulfides and diselenides. Adv. Mater. 30, 1802991 (2018).

Du, Y., Yang, L., Zhou, H. & Peide, D. Y. Performance enhancement of black phosphorus field-effect transistors by chemical doping. IEEE Electron. Device Lett. 37, 429–432 (2016).

Jie, W. et al. Ferroelectric polarization effects on the transport properties of graphene/PMN-PT field effect transistors. J. Phys. Chem. C 117, 13747–13752 (2013).

Lee, H. S. et al. MoS2 nanosheets for top‐gate nonvolatile memory transistor channel. Small 8, 3111–3115 (2012).

Lee, Y. T. et al. Nonvolatile charge injection memory based on black phosphorous 2D nanosheets for charge trapping and active channel layers. Adv. Funct. Mater. 26, 5701–5707 (2016).

Li, D. et al. Nonvolatile floating‐gate memories based on stacked black phosphorus–boron nitride–MoS2 heterostructures. Adv. Funct. Mater. 25, 7360–7365 (2015).

Lu, Z. et al. Electrically induced, non-volatile, metal insulator transition in a ferroelectric-controlled MoS2 transistor. Appl. Phys. Lett. 112, 043107 (2018).

Conley, J. F. Instabilities in amorphous oxide semiconductor thin-film transistors. IEEE Trans. Device Mater. Reliab. 10, 460–475 (2010).

Mutoh, S. I., Douseki, T., Matsuya, Y., Aoki, T., Shigematsu, S. & Yamada, J. 1-V power supply high-speed digital circuit technology with multithreshold-voltage CMOS. IEEE J. Solid State Circuits 30, 847–854 (1995).

Yi, J. et al. Double‐gate MoS2 field‐effect transistors with full‐range tunable threshold voltage for multifunctional logic circuits. Adv. Mater. 33, 2101036 (2021).

Shim, J. et al. Phosphorene/rhenium disulfide heterojunction-based negative differential resistance device for multi-valued logic. Nat. Commun. 7, 1–8 (2016).

Mennel, L. et al. Ultrafast machine vision with 2D material neural network image sensors. Nature 579, 62–66 (2020).

Zhou, F. et al. Optoelectronic resistive random access memory for neuromorphic vision sensors. Nat. Nanotechnol. 14, 776–782 (2019).

Acknowledgements

This work was supported by the National Science and Technology Council, Taiwan, under Grant No. NSTC 110-2112-M-009-010-MY3. This work was in part supported by the “Advanced Semiconductor Technology Research Center” from The Featured Areas Research Center Program within the frame work of the Higher Education Sprout Project by the Ministry of Education (MOE) in Taiwan and in part under Grant No. NSTC 111-2634-F-A49-008. This work was in part supported by Semiconductor Research Corporation under Grant No. SRC 2022-PK-3801. The research was supported by Taiwan Semiconductor Manufacturing Company. D.-H.L. acknowledges the Yushan Scholar Program by the MOE in Taiwan. R.T. would like to thank Dr. Hsin-Fu Kuo from GoMore for scholarship financial support. The author also thanks Dr. Yu Ming Lin and Dr. Chung Te Lin for resource support in sample preparation.

Author information

Authors and Affiliations

Contributions

R.T. and D.-H.L. conceived the idea and designed the experiment. W.-Y.W. and D.-H.L. provided scientific guidance throughout. R.T., S.-T.W., Y.-Y.P., and S.-C.C. performed the device fabrication and the measurement. C.-C.K. and T.T.C. designed and developed the ALD tools. W.-Y.W. and S.S.L. provided engineering guidance for ALD growth. C.-C.S., W.-W.T. and H.-C.C. performed the ALD growth and TEM. Y.-H.K. and C.-L.L. performed the STS. W.-C.H. and J.-C.C. designed the laser illumination system and performed large-area VT tuning experiments. R.T., S.-T.W., W.-Y.W. and D.-H.L. analyzed the data. R.T., T.A., and D.-H.L. wrote the paper. All authors have read and approved the final version of the paper.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Nature Communications thanks Luisa Petti and the other, anonymous, reviewer(s) for their contribution to the peer review of this work. A peer review file is available.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Tseng, R., Wang, ST., Ahmed, T. et al. Wide-range and area-selective threshold voltage tunability in ultrathin indium oxide transistors. Nat Commun 14, 5243 (2023). https://doi.org/10.1038/s41467-023-41041-y

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41467-023-41041-y

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.