Abstract

Two-dimensional (2D) semiconductor-based vertical-transport field-effect transistors (VTFETs) – in which the current flows perpendicularly to the substrate surface direction – are in the drive to surmount the stringent downscaling constraints faced by the conventional planar FETs. However, low-power device operation with a sub-60 mV/dec subthreshold swing (SS) at room temperature along with an ultra-scaled channel length remains challenging for 2D semiconductor-based VTFETs. Here, we report steep-slope VTFETs that combine a gate-controllable van der Waals heterojunction and a metal-filamentary threshold switch (TS), featuring a vertical transport channel thinner than 5 nm and sub-thermionic turn-on characteristics. The integrated TS-VTFETs were realised with efficient current switching behaviours, exhibiting a current modulation ratio exceeding 1 × 108 and an average sub-60 mV/dec SS over 6 decades of drain current. The proposed TS-VTFETs with excellent area- and energy-efficiency could help to tackle the performance degradation-device downscaling dilemma faced by logic transistor technologies.

Similar content being viewed by others

Introduction

The continuous technology node shrinking and performance boost of complementary-metal-oxide-semiconductor (CMOS) field-effect transistor (FET) technology have offered significant impetus for the development of the semiconductor integrated circuit industry1,2,3,4,5,6. Despite the physical size downscaling-enabled performance improvement of these transistors, further scaling down along the conventional route has been predicted to be less cost-effective due to the fact that the constituent material and/or device concept are approaching their physics limitations at the nanometre regime2,4,5,6. Especially, the transistor size reduction that limits the device density along with the supply voltage scaling that determines the power consumption have constituted a daunting challenge for future transistor downscaling6. In fact, the device size scaling and the energy-effectiveness increase for future highly scaled nano-transistors have been largely thwarted by the fundamental limits on the device electrostatics and the subthreshold swing (SS) properties, respectively1. Therefore, investment in the “next option” for near-future logic transistor technology has urgently promoted the quest for alternative device concepts with innovative materials, structures and working physics1,2. Many efforts have been made to enhance the device electrostatics and thus tackle the short-channel effect in ultra-scaled transistors, including FinFETs7, gate-all-around (GAA) nanosheet FETs8, vertical-transport FETs (VTFETs)5, beyond-Si semiconductor channel-based transistors2, etc. Among them, the VTFET—a unique transistor structure in which its source, semiconductor channel and drain components stack vertically to the substrate surface and thus induce the drive current along the perpendicular direction – has been demonstrated as a suitable device architecture to break the device performance-size downscaling dilemma imposed by the conventional planar transistor technology, i.e., lateral-transport FET (LTFET) structure9,10,11. Such a device geometry offers a much-reduced transistor feature by utilizing the vertical construction capability and an ultra-scaled channel length depending on the thickness of the semiconductor layer, which is thus highly promising to achieve an aggressive boost of transistor area-efficiency as well as other desired area-performance device metrics9,10,11. Impressively, Si-based VTFETs have been made possible in commercially-available CMOS technology, which have been regarded as an elegant device strategy to extend the downscaling towards the sub-5 nm CMOS technology node11. Furthermore, to maintain the device performance improvement and enrich the device functionalities, various VTFETs device concepts with semiconductor materials beyond Si have been proposed, including but not limited to bulk III-V compound semiconductors12, organic semiconductors13, oxide semiconductors14, and two-dimensional (2D) van der Waals (vdW) materials6,15,16,17.

In particular, high-performance 2D vdW heterostructures—which can be created by rationally stacking multiple 2D layers without the lattice-mismatch issue as often experienced in the bulk semiconductor counterparts—have been recently identified as a viable solution for VTFETs18. Benefitting from their superior electrostatic control, ultra-scaled 2D semiconductor VTFETs have showcased a well-preserved gate-control ability even at the sub-1-nm transport length limit15. Despite the promising merits of 2D semiconductor VTFETs, the evolution of such a device concept towards the ultra-scaled channel length simultaneously with the power consumption cut-down is highly demanding13,15,18,19. Although 2D vdW heterostructure-based VTFETs have been identified to have the potential for greatly relaxing the size-reduction constraints of conventional transistor technology, the low-power current switching operation—as set by the fundamental limit on the SS—remains a daunting challenge for energy-efficient VTFETs20. Besides, 2D vdW heterostructure-based VTFETs with the channel length downscaling to sub-5 nm generally show moderate transistor performance19. Breaking the performance degradation-size downscaling dilemma has thus been identified as a critical obstacle for the development of 2D vdW heterostructure-based VTFETs19.

Reduction of the SS can efficiently modify the steepness of the conduction state transition slope in a transistor, thus presenting a significantly lowered power consumption through the scaling down of the supply voltage21. However, the fundamental thermionic limitation of the SS in a conventional MOSFET is 60 mV/dec at room temperature, and further lowering of the SS beyond thermionic limitation would require alternative device working principles. Meanwhile, a suitable device concept for steep-slope VTFETs featuring both an SS lower than 60 mV/dec and transport channel length less than 5 nm has yet to be explored. Therefore, designing a device architecture with new physical principles becomes the key point to constructing steep-slope VTFETs with ultra-scaled channel length, which would offer a viable approach to tackle the performance enhancement-channel downscaling dilemma for future low-power and area-efficient vertical transistor technology.

In this work, we propose an efficient steep-slope VTFET device architecture formed from the integration of an Ag/TaOx/Ag-based metal filamentary resistance threshold switching (TS) cell and an ultra-scaled MoS2/MoTe2 vdW heterostructure, which is denoted as TS-VTFET. Taking advantage of the abrupt resistance switching of the TS cell along with the gate voltage-modulated conduction transition of the MoS2/MoTe2 heterojunction, unique features such as a sub-5 nm transport channel and a sub-60 mV/dec SS current transition characteristics can be retained in the proposed vdW heterostructure-based TS-VTFET. Specifically, our devices exhibit an average sub-60 mV/dec SS over 6 decades of drain current with a minimum SS (SSmin) down to ~2.7 mV/dec as well as an excellent current modulation ratio exceeding 1 × 108 at room temperature. The reliability performance of the TS-VTFETs has been systematically investigated, showing strong voltage-cycling and DC-voltage stressing characteristics that are required for practical transistor applications. Our results provide a promising device concept which could help to address the key downscaling challenges faced by mainstream conventional planar MOSFET technology, forming the basis for the development of future energy- and area-efficient vertical logic transistors.

Results

Design strategy and device architecture

For 2D semiconductor-based LTFETs (Fig. 1a), the efficiency of the channel conductance modulation process is limited by the SS (minimum value of 60 mV/dec at room temperature) due to the thermionic injection of carriers over an energy barrier22. In recent years, notable innovative steep-slope device concepts have been established which exhibit reduced supply voltage and power consumption by improving the SS beyond the 60 mV/dec limit at room temperature, including but not limited to negative-capacitance FET (NC-FET)21, tunnelling-FET6, Dirac-source FET23, impact ionization FET24, and phase-FET25,26. Especially, unlike other steep-slope transistor architectures, phase-FETs normally comprise disruptive components with different functionalities (that is, the two-terminal phase-transition component integrated in-series with the transistor), where the gate-voltage controlled transistor current transition along with the abrupt resistance switching of the phase-transition component would together lead to an overall sub-60 mV/dec steep-slope switching behaviours25,26,27,28. Such a heterogeneous integration strategy of disruptive components can be feasibly extended to conventional 2D semiconductor-based VTFETs (Fig. 1b). Therefore, integrating the two-terminal phase-transition device vertically with the 2D vdW heterostructure-based VTFET would naturally maximize the 3D construction capability of the device and result in a compact device architecture to further increase the transistor density on the chip, see Fig. 1c.

a Device architecture of a conventional lateral-transport field-effect transistor (LTFET) where the channel length is denoted as Lc. The operation mechanism involving the gate voltage (Vg) controllable energy band diagrams at ON and OFF states is depicted along with the typical transfer characteristics. For the energy band diagram, the arrows indicate the electron transport direction. EC, EF, and EV: conduction band energy, Fermi level, and valence band energy, respectively. The drain-source current (Id) switching curves of conventional LTFETs are normally with a subthreshold swing (SS) larger than 60 mV/dec at room temperature. For LTFETs, steep-slope device concepts such as negative-capacitance FET (NC-FET) and phase-FET have been proposed before. b Structure of a vdW junction-based vertical-transport field-effect transistor (VTFET). The gate voltage controlled current switching is enabled by the electrostatic modulation of the barrier formed at the junction interface. c Threshold switch (TS)-VTFET consists of a VTFET and a TS cell. The abrupt threshold current switching of the TS cell along with the junction current modulation in the VTFET leads to the steep-slope transistor current transition. Moreover, the high resistance performance of the TS cell in series with the VTFET would lead to efficient reduction of the device off-current. TE and BE represents top- and bottom-electrode of the TS cell, respectively.

Leveraging the electronic phase transition behaviour, such a hybrid architecture combining VTFET and phase-transition component could provide a potential sub-thermionic device concept with both advantages of the excellent area- and energy-efficiency. As shown in Fig. 1c, the proposed VTFET exploits a vdW heterojunction by vertically stacking the unipolar n-type (MoS2) and the p-terminal dominated ambipolar (MoTe2) semiconductors. Harnessing the merits including minimal interface trap states and large bandgap offset in high-quality MoTe2/MoS2 vdW vertical heterostructures29, voltage-reconfigurable band alignment can be efficiently realised in such a heterojunction, giving rise to electric field-effect mediated transport behaviours. To further enable the steep-slope current switching in this device architecture, a metal filament formation/rupture-based volatile TS cell (phase-transition component) is proposed to be integrated on the drain terminal of a VTFET without extra area cost, resulting in a small-footprint TS-VTFET structure (Fig. 1c). As the VTFET channel resistance determines the effective drain voltage (Vd) drop on the TS and the FET channel, the metal filament formation and rupture behaviours can thus be controlled by the gate voltage (Vg), which could consequently give rise to the steep-slope current switch in the proposed TS-VTFETs. Furthermore, benefiting from the high resistance of the off-state TS cell, reduction of the overall off-current would be possible for the TS-VTFET in comparison with the VTFET alone. The working principles of the TS-VTFET will be discussed in detail in the next sections.

Electrical properties of the vdW heterojunction VTFET

Using the standard dry-transfer method with mechanically exfoliated 2D semiconductor flakes (see Supplementary Note 1), we fabricated MoS2 and MoTe2 LTFETs as well as the MoS2/MoTe2 vdW heterostructure-based VTFET on a Al2O3/HfO2 (3 nm/12 nm) dielectric layer, as schematically shown in Fig. 2a. Note that the ultrathin Al2O3 layer is deposited on the HfO2 for two purposes: (1) suppress the interface defects when in contact with the 2D layers;30 (2) prevent the leakage favoured crystalline states formed in HfO231. Both MoS2 and MoTe2 layers along with their vertically-stacked heterostructure are investigated by Raman spectroscopy, showing excellent single crystalline quality (Fig. 2a). Among the library of 2D semiconductor-based vdW p-n heterojunctions, such a MoS2/MoTe2 combination would be more practical to be fabricated from scalable production perspectives since only the alternation of S and Te source is needed with the same Mo source (unlike other 2D heterojunctions like MoS2/WSe2)32. The top-view layout of the devices is shown in the optical image (Fig. 2b), where three different devices including a MoS2 LTFET, a MoTe2 LTFET and a MoS2/MoTe2 VTFET (formed at the overlapping area of the MoS2 and MoTe2 flakes) are demonstrated. The cross-section high-angle annular dark field scanning transmission electron microscopy (HAADF STEM) and high-resolution TEM (HR-TEM) images in Fig. 2c present the layered structure of a typical MoS2/MoTe2 VTFET created on the Al2O3/HfO2 dielectric substrate. Here, an atomically-sharp and ultra-flat interface can be observed between the adjacent MoS2 and MoTe2 layers, which ensures the good performance of the vdW heterostructure-based electronic devices33. The uniform distribution of Mo, S, Te, Al and Hf in the MoTe2/MoS2/Al2O3/HfO2/Si (bottom electrode) has been further confirmed using energy-dispersive X-ray spectroscopy (EDS) mapping, as shown in Fig. 2c. The MoS2/MoTe2 vdW heterostructure-based VTFET device was also investigated using atomic force microscopy (AFM), showing a thickness of 1.7 nm and 3.2 nm for MoS2 (2 atomic layers) and MoTe2 (4 atomic layers) layer, respectively (see Supplementary Note 2). These results indicate that the transport channel of the fabricated VTFET only has a sub-5 nm channel length, which is highly promising for future ultra-scaled transistor technology15.

a Schematic diagram showing the MoS2 and MoTe2 LTFETs as well as the MoS2/MoTe2 vdW heterostructure-based VTFET. Raman spectra of 2D semiconductors are also given. b Optical image of the fabricated devices. A vdW hexagonal boron nitride (hBN) layer was placed on top of the devices as a protective layer. c Cross-section high-angle annular dark field scanning transmission electron microscopy (HAADF-STEM) and high-resolution TEM (HR-TEM) images of the vertically stacked MoS2/MoTe2 vdW heterostructure. The distribution of Al, Mo, S and Te is detected using the corresponding energy-dispersive X-ray spectroscopy (EDS) elemental mapping. The red dashed lines indicate the region of the MoS2/MoTe2 vdW heterostructure. d Output curves at different gate voltage values for MoS2 and MoTe2 LTFETs, respectively. Vd: drain-source voltage. Output curves (f) and rectification ratio (e) under different applied gate voltages of the same device as in (f). g Calculated band profiles of the MoS2/MoTe2 vdW heterostructure-based VTFET under various Vd and Vg. Black dashed line indicates the Fermi energy level, blue and red filled circles represent electrons for different band energy profile cases. The arrows indicate the electron transport direction. h Transfer curves of the MoS2/MoTe2 VTFET measured with different Vd.

Electrical transport characterizations of all the fabricated MoS2 LTFETs, MoTe2 LTFETs and MoS2/MoTe2 VTFETs were performed at room temperature. By sweeping the drain-source voltage (Vd) under gate voltage with opposite polarities (Vg = 1 V and −1 V), different output characteristics of MoS2 and MoTe2 LTFETs can be obtained, see Fig. 2d. As a unipolar n-type semiconductor, the LTFET with MoS2 channel exhibits high and low conductance state at Vg = 1 V and −1 V, respectively. In contrast, the LTFET with a MoTe2 channel exhibits almost equally high drain-source current (Id) at Vg = 1 V and −1 V, indicating the ambipolar nature of the channel semiconductor. Distinct output curves have been observed in the MoS2/MoTe2 VTFETs, where the metal contact to the bottom MoS2 layer was kept grounded as the source electrode, see Fig. 2e, f. Clear rectification behaviour with asymmetric Id - Vd output curves can be observed for the MoS2/MoTe2 heterojunction, which could evolve as a function of the applied gate voltage. Changing the gate voltage from Vg = −1 V to Vg = 1 V, the rectification ratio drops from nearly 1×105 to almost 0. This behaviour can be attributed to the gate voltage-induced operation mode switching in the proposed VTFETs.

To gain insight into the working mechanism responsible for the VTFET, we simulated the band profiles along the vertical direction of the MoS2/MoTe2 heterojunction under different gate voltages, see Supplementary Note 3 for details. The simulated results show that the gate voltage can efficiently modulate the band profile of the bottom MoS2 layer and control the band alignment of the MoS2/MoTe2 heterojunction as well. Comprehensive band profile of the MoS2/MoTe2 heterojunction-based VTFET under different Vd and Vg are depicted in Fig. 2g. Briefly, corresponding to different polarities of the Vd, the proposed VTFET can be operated between a p-n junction and a tunnel diode with efficient gate voltage modulation. At Vd > 0 V, the MoS2/MoTe2 heterojunction-based VTFET works as a conventional forward biased p-n diode, where the current increases with increasing the Vd and the Vg due to the exponential growth of majority carriers in the n-type MoS2. The device turns to the high resistance state under negative Vg due to the reason that the MoS2 layer is modulated to the electron depletion state by gate control. On the other hand, the MoS2/MoTe2 heterojunction can work as a reverse biased tunnel diode at Vd < 0 V, in which the band-to-band tunnelling (BTBT) current increases with the growth of the applied Vd and the tunnelling onset voltage decreases with higher gate voltage. With decreasing applied Vg, the band tilting of the tunnel diode could be weakened, thus resulting in a larger barrier impeding the overall tunnelling current. The abovementioned working mechanism has been verified with low-temperature Id-Vd characteristics in the VTFETs, where the tunnelling current at negative drain voltage region barely changes but the forward bias current under positive Vd diminishes at 80 K, see Supplementary Note 4. Consistent with the proposed working principles, the MoS2/MoTe2 heterojunction-based VTFET shows distinct transfer characteristics when varying the Vd, as shown in Fig. 2h. Similar to a conventional MOSFET, an excellent current switching behaviour with ON-OFF ratio (Ion/Ioff) beyond 1×106 can be achieved, indicating that the MoS2/MoTe2 heterojunction-based VTFET with a sub-5 nm channel transport length could be a promising option for future transistor technology with ultra-scaled channel length. To show the unique gate voltage controllable behaviours of the proposed VTFETs, we have also presented the transfer properties of the MoS2 and MoTe2 LTFETs, see Supplementary Note 5. It is noteworthy that the carrier transport path in the VTFETs consists of the lateral and the vertical directions as discussed in Supplementary Note 6. An ideal VTFET would have a minimal lateral transport channel length to offer the ultra-scaled footprint in the 2D plane, albeit that the lateral conducting line at the bottom linking the vertical channel to the source electrode is unavoidable in VTFET device structure. The lateral transport in the VTFET proceeds by drift-diffusion with the intralayer carrier recombination within each material, while the vertical transport is dominated by the diffusion of majority carriers or the band-to-band tunnelling depending on the applied voltage. As discussed in Supplementary Note 6, the charge transport in VTFET is dominated by the vertical MoS2/MoTe2 p-n diode and has no appreciable contribution from the lateral semiconductor channel. This conclusion has been further verified by analysing the electric properties of a MoS2/MoTe2 VTFET with the gate electrode confined within the heterojunction area, see Supplementary Note 7.

vdW heterostructure-based steep-slope TS-VTFET

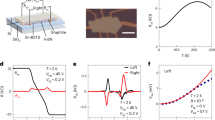

Having demonstrated the basic electrical properties of the MoS2/MoTe2 heterojunction-based VTFETs, we now focus on the steep-slope switching behaviour in the proposed TS-VTFETs (Fig. 3a). Following a previously reported high-performance TS cell design strategy34, we fabricated high-quality TS cells using magnetron sputtering, which consist of alternating TaOx/TaOy/TaOx (x < y) layers with Ag as both top and bottom electrodes (see TEM analysis shown in Supplementary Note 8). With such symmetric Ag electrodes, the Ag conductive filament can be triggered to grow at both sides of the TS cell, leading to an excellent volatile bidirectional resistive threshold switching with a very small current switching slope (Fig. 3b). The fabricated TS cell presents reliable threshold switching under pre-set compliance current (ICC), showing excellent stability of threshold voltage (Vth) up to 100 consecutive switching cycles, see Supplementary Note 9. Moreover, the device maintains a high on-off ratio over a wide range of cell areas (see Supplementary Note 9), indicating great uniformity and scalability of the resistive switching medium. We have also discussed the asymmetric electrode configuration effect on the electrical properties of the TS cell, see Supplementary Note 10 for details. As schematically depicted in Fig. 3c, the resistive switching behaviour in the TS cell could be attributed to the formation and rupture of the Ag filament at a proper driving voltage34. The Ag filament after the high voltage electroforming process (V > Vth) could grow from both top- and bottom-Ag electrodes and extend to the TaOx/TaOy/TaOx dielectric medium, which serves as the conducting channel and make the TS cell less insulating. When the applied voltage drops below a certain voltage holding the metal filament formation (Vhold), the Ag filament becomes unstable and eventually ruptures, thus the conducting channels in the TS cell disappear and the device turns into a highly insulating.

a Schematic of the MoS2/MoTe2 TS-VTFET, where the source contact is connected to the MoS2 layer. b Typical threshold resistive switching of the TaOx/TaOy/TaOx TS cell with ultra-low leakage current and very steep current switching slope. Vhold, Icc, and Vth: metal filament holding voltage, compliance current, and threshold voltage triggering the filament formation, respectively. The arrows indicate the current sweeping directions. c Schematic drawing of the Ag filament formation and rupture process in the TS cell. d Output curves of the VTFET and the TS-VTFET at Vg = 1 V. e Transfer characteristics of the VTFET and the TS-VTFET during the forward sweeping process at room temperature. The dashed black line indicates the “cross points” below which the instrument limit induced noisy current contaminates the measured Id. In our case, the instrument limit current cross points occur at or below 30 fA for all the transfer curves measured. f Point SS calculation for both VTFET and TS-VTFET as a function of the Id during forward gate voltage sweeping. The dashed black line indicates the SS = 60 mV/dec limit.

We now demonstrate the TS-VTFET with steep-slope switching properties. As presented in Figs 2b, 3a, the TS cell was directly deposited on the drain terminal of the MoS2/MoTe2 heterojunction-based VTFET. In this way, we can accurately compare the electrical properties of the VTFET and the TS-VTFET since they share the same MoS2/MoTe2 heterojunction as the transistor channel. Note that, the TaOx/TaOy/TaOx and Ag layers were deposited at room temperature while the high-quality Al2O3/HfO2 dielectric layer were fabricated at 200 °C (see Supplementary Note 11), indicating that the proposed TS-VTFET can be fabricated at low temperature and is thus compatible with the back-end-of-line (BEOL) process. The output curves for both VTFET and TS-VTFET at Vg = 1 V are presented in Fig. 3d. As expected, the MoS2/MoTe2 heterojunction-based TS-VTFET shows a similar Id - Vd curve with the TS cell, indicating that the transport properties of the TS-VTFET are jointly controlled by the TS phase-transition component as well as the VTFET. For a fixed drain voltage higher than the Vth of TS cell (Vd > Vth), the proposed TS-VTFET can be operated as a transistor with steep switching characteristics, showing a high ON-OFF current switching ratio exceeding 1 × 108 (Fig. 3e). Compared to the VTFET, an abrupt channel current switching slope can be obtained in the TS-VTFET along with a much-reduced gate voltage modulation range and off-current, see Fig. 3e. Remarkably, in the forward gate bias sweep, the transfer curve of the TS-VTFET at Vd = 0.3 V shows excellent sub-threshold characteristics with an average SS of 1.52 mV/dec over 6 orders of magnitude change in the drain current within the ~10−14 A to ~10−7 A range. The dashed black line in Fig. 3e indicates the “cross points” below which the drain current of the measured device become similar with the noisy current due to the instrument limit. In our case, the instrument limit current cross points occur at or below 30 fA for all the transfer curves measured on TS-VTFET. The measured off-current from the TS-VTFET exceeds the lower limit of our equipment’s capabilities, consequently leading to the generation of random and negative current values. Given such facility limitation, we utilized the lower limit of current detection (30 fA) for the calculation of device performance metrics including SS, ON-OFF ratio, etc., irrespective of the recorded current values. Such a steep-slope switching performance strongly satisfies the Internal Roadmap for Devices and Systems (IRDS) standard for a low-power FET, that is, the average SS is below 60 mV/dec for four decades of channel current. Note, the minimal current level of our device is determined by the measurement facility limit, which could be even lower than the as-measured value for the actual device and may thus contribute to a steeper current switching with smaller SS27,34. Moreover, benefiting from the volatile switching and a low hold voltage of the TS cell, the TS-VTFET can operate with a low hysteresis voltage down to ~60 mV (at Vd = 1 V) during gate bias sweeping (Supplementary Note 12), which is important for practical transistor application requiring small hysteresis35. Next, statistical data for SS as a function of the output drain current for both VTFET and TS-VTFET is plotted in Fig. 3f. In stark contrast, while the VTFET shows an SS higher than the 60 mV/dec limit at room temperature, the MoS2/MoTe2 heterojunction-based TS-VTFET presents SS values much below 60 mV/dec over a wide current modulation range and thereby demonstrates better steep-slope switching performance combating the power consumption for transistor operation. The I60, a device figure-of-merit that determines the point where the current exhibits a transition from sub-60 mV/dec to super-60 mV/dec, is found to be as high as ~1 × 10−7 A in the presented TS-VTFET. Given the excellent steep-slope device properties, we further compare our device on three important figure-of-merits, i.e., SSmin, I60 and I60/Ioff36, with previously reported steep-slope transistors. The comparison results clearly indicate excellent performance metrics of the presented TS-VTFET, see detailed discussion in the next section. This underscores its potential as a promising solution for future high-performance steep-slope logic transistors, which is advantageous in terms of miniaturization, device performance, low power consumption, etc.

We now analyse the channel current switching dynamics in the TS-VTFET. At a certain gate voltage, the TS-VTFET can be regarded as a resistor in series with the resistance-variable TS cell (Fig. 4a). As shown in Fig. 4a, the ramped current mode I-V characteristics of the TS cell in series with a load resistor show a clear negative differential resistance (NDR) behaviour with the snapback current switching, indicating the volatile and abrupt formation process of the Ag filament37. Correspondingly, by replacing the resistor with the VTFET, it can be predicted that three stages of the current switching process would be identified in the TS-VTFET according to the voltage distribution across the TS cell during gate voltage sweeping, as shown in Fig. 4a, b. Figure 4c schematically illustrates the internal effective voltage distribution and band diagrams of the proposed TS-VTFET at different operation states during forward gate voltage sweeping, indicating that the abrupt current switching mechanism in the TS-VTFET is associated with the gate-voltage controlled TS cell behaviour. At state 1, the VTFET channel is highly insulating with the applied Vg smaller than the threshold gate voltage (Vg, th), thus the effective drain-source voltage drop on the TS (VTS) is much lower than the applied Vd owing to the voltage distribution of the VTFET part (Vd’). With increasing the gate voltage, partial voltage falling on the TS becomes larger as the resistance of the VTFET reduces. Note, despite the channel resistance of the VTFET decreasing at this stage, the TS-VTFET is still in an insulating condition since the high-resistance TS cell could block the current. With the gate voltage approaching a certain Vg (state 2), the effective drain-source voltage drop on the TS would reach its threshold voltage (Vd, th) and trigger the formation of Ag filament, thus resulting in the overall drain current surge of the TS-VTFET. Such a process is associated with the NDR behaviour as observed in the TS cell, which could lead to an abruptly increased drain-source voltage drop across the VTFET channel and thereby the steep-slope channel conductance transition. Finally, as shown in stage 3, the TS cell becomes fully conducting and the applied Vd almost totally drops on the VTFET, which gives rise to a normal transfer behaviour similar with that of the VTFET. The above analysis can be further verified by measuring the transfer characteristics of the TS-VTFET with varying the applied drain voltage, as illustrated in Fig. 4b. Obviously, the threshold gate voltage to trigger the channel current switching is dependent on the applied drain voltage of the TS-VTFET, which is due to the balance between the overall drain voltage and the effective potential drop on the VTFET channel during gate sweeping. When applying a Vd less than the Vth of the TS cell, the channel conduction state remains insulating during the gate voltage sweeping, since the effective voltage drop on the TS cell constantly remains below its threshold voltage, see the case of Vd = 0.1 V shown in Fig. 4b. With increasing the Vd beyond the Vd, th, the TS cell would be more inclined to be turned into the conducting state as the potential drop on the TS cell gets higher, leading to various transfer properties. Apparently, the change of applied drain voltage can significantly influence the device performance metrics including hysteresis, I60 and Vth, see Supplementary Note 12 for detailed discussions. Overall, this picture clearly indicates that the sub-thermionic switching behaviour of the TS-VTFET is strongly correlated with the TS NDR effect.

a Snapback type current switching of the TS cell in series with a 100 kΩ load resistor (RL). By sweeping the current, the TS cell undergoes 3 states: the TS medium is insulating (state 1), Ag metal filament triggered to formation (state 2), and the TS medium enters conducting phase with the formed metal filament (state 3). b Transfer curves of the TS-VTFET under different applied drain voltage values. c Schematic illustration of operation principles for the TS-VTFET associated with the filament formation process in the TS cell. Vg, th, Vd, th, VTS, Vd, and Vd’: threshold gate voltage to trigger the TS switching, threshold drain-source voltage to enable the metal filament formation in the TS cell, effective drain voltage on the TS, overall applied drain voltage, and the voltage distribution with the FET channel, respectively. For the band diagrams, the arrows indicate the electron transport direction, horizontal dashed lines represent Fermi level of the 2D semiconductors, horizontal solid lines represent Fermi level of the metals, filled circles denote electrons, and empty circles indicate the broken metal filament conducting path, respectively.

Reliability and performance benchmark of the TS-VTFET

Having discussed the device physics of TS-VTFETs, we now examine the reliability of the proposed device. For a filamentary switching dielectric medium, the high voltage DC stressing would cause a permanent conductive filament formation and thus threshold switching breakdown37. As shown in Fig. 5a, the MoS2/MoTe2 heterojunction-based TS-VTFET can function properly after a 10 s-long high voltage pulse biasing, proving that the demonstrated device is of high capability of long-term service. For the time-dependent DC stressing below the Vth, the device could work stably without any low voltage accumulation-induced filament formation, as shown in Fig. 5b. Moreover, the TS-VTFET shows great drain-source and gate voltage cycling endurance without any performance degradation after 1000 cycles of ON-OFF switching, see Supplementary Note 13. Overall, these results unambiguously demonstrate that the MoS2/MoTe2 heterojunction-based TS-VTFETs have excellent reliability.

a DC pulse stressing test of the TS-VTFET. b DC stressing of the TS-VTFET under the threshold voltage of the TS cell. c Comparison of SS and Ion/Ioff ratio at room temperature between the demonstrated TS-VTFET and previously reported VTFETs, including the organic semiconductor (OSC)-based vertical organic FET (VOFET)13, Si VTFET9, graphene/MoS2 VTFET38, IGZO/graphene VTFET14, VTFET with MXene Ti3C2Tx/Organic semiconductor PDVT-1020, MoS2/graphene VTFET39, WS2/graphene vertical tunnelling transistors16, black phosphorous (BP)/MoS2 VTFET29, MoS2/MoTe2 VTFET40 and MoS2/graphene VTFET15. Here, the Ion/Ioff refers to the drain current modulation ratio between the maximum (ON) and minimum (OFF) current level during gate voltage sweeping. Device parameters of the TS-VTFET are taken from the transfer characteristics measured at Vd = 0.3 V.

Finally, we illustrate the performance metrics benchmark of the demonstrated TS-VTFET with state-of-the-art VTFETs, as presented in Fig. 5c and Supplementary Note 14. The SSmin in combination with the ON-OFF current ratio at room temperature are highlighted and discussed here as two essential performance metrics for a VTFET. Note that the ON- and OFF-current discussed here refer to the drain current obtained at maximum and minimum gate voltage, respectively. A more detailed comparison of other important device figure-of-merits including current density, I60, average SS, etc. can be found in Supplementary Note 15. As can be seen from Fig. 5c, minimum SS value together with the ON-OFF current ratio of our device are compared with representative VTFETs in the literature, including organic semiconductor (OSC)-based vertical organic FET (VOFET) with ionic liquid gate13, standard Si VTFET9, graphene/MoS2 VTFET with ionic liquid gate38, IGZO/graphene VTFET with Al2O3 gate14, VTFET with MXene Ti3C2Tx/Organic semiconductor PDVT-1020, MoS2/graphene VTFET39, WS2/graphene vertical tunnelling transistors16, black phosphorous (BP)/MoS2 VTFET29, MoS2/MoTe2 VTFET on hBN40 and MoS2/graphene on 300 nm-thick SiO2 dielectric gate15. With the capability of steep-slope current switching and an excellent ON-OFF current ratio exceeding 1 × 108, the demonstrated MoS2/MoTe2 heterojunction-based TS-VTFET could thus outperform the reported VTFETs in terms of the sub-thermionic switching and low-power operation. Moreover, the vdW heterostructure-based TS-VTFET can be integrated seamlessly using the dry transfer method and TS medium deposition compatible with the BEOL process, which is beneficial for future low-energy electronic device manufacture2.

Discussion

In conclusion, we have reported vdW heterostructure-based VTFETs with a sub-5 nm transport channel length and steep-slope switching capability by exploiting the atomic thickness of 2D semiconductors and the abrupt current switching effect in TS cells. The demonstrated device features outstanding sub-thermionic SS down to ~2.7 mV/dec at room temperature, a competitive sub-60 mV/dec region over 6 decades of drain current, a high on-off current ratio and a low leakage current. These key performance metrics of the proposed TS-VTFETs have been shown to outperform previous vertical transistors. Furthermore, the demonstrated TS-VTFETs illustrate excellent reliability properties, which is critical for future practical applications. Our results provide a proof-of-concept steep-slope VTFET which could potentially be a front runner for next-generation ultra-scaled and low-power digital logic device technology.

Methods

Device fabrication

Flakes of MoS2 and MoTe2 (both purchased from HQ Graphene@) were mechanically exfoliated onto polydimethylsiloxane (PDMS, Gel-Pak@) supports using a low-residue blue type (Nitto, Japan). The 2D MoS2 and MoTe2 flakes of interest were then transferred onto the substrates. The MoS2/MoTe2 vdW heterostructures were vertically stacked using a location-precise transfer platform (Shanghai Onway Technology, China). Metal contacts to the 2D layers were formed through dry-transfer of the Au metal stripes. vdW material-based samples were annealed at 300 °C in vacuum for 2 h. The TS components were fabricated on the VTFETs using standard photolithography, metal sputtering and dielectric layer deposition methods. The Al2O3/HfO2 dielectric gate stack was deposited on heavily doped n-type Si using atomic layer deposition (ALD). HfO2 thin films were deposited through ALD at 200 °C with [(CH3)2N]4Hf (TDMAHf) and H2O as the Hf precursor and the oxygen source, respectively. To encapsulate the HfO2 film, an Al2O3 layer was in situ deposited using Al(CH3)3 (TMA) and H2O at 200 °C. Prior to the vdW heterostructure transfer, oxygen plasma was conducted to passivation the Al2O3 layer. TS dielectric layer deposition was conducted by a radio frequency magnetron sputtering with a Ta2O5 ceramic target at room temperature. The oxygen-deficient TaOx and oxygen-rich TaOy layers were sputtered with a pure Ar of ~0.1 Pa and a mixture of Ar: O2 (1: 2) at ~0.5 Pa, respectively. Ag electrodes were deposited in the same chamber by switching to the DC magnetron sputtering mode. A detailed vdW heterostructure preparation flow is schematically shown in Supplementary Note 1.

Characterizations

For the Raman spectra, all the vdW heterostructures were measured using a WITec Alpha 300 R with a 532 nm laser under 1 mW light intensity. TEM-related measurements were carried out using a probe aberration-corrected JEOL JEM-ARM200F with an Oxford X-MaxN 100TLE spectrometer, which was operated at 200 kV. Specimens of the vdW heterostructures for the TEM tests were prepared by Focused Ion Beam (FIB) milling (FEI Helios NanoLab 600i). A FS-Pro semiconductor parameter analyzer with a minimum current accuracy of 30 fA equipped with a Lakeshore cryogenic probe station (set at 25 °C and ~10−6 mbar) was adopted to perform all the electrical measurements. Thickness characterisation of 2D flakes was performed using a commercial atomic force microscopy (AFM) system (AIST-NT Smart SPM 1000) under an ambient atmosphere. Conductive platinum-coated tips (Mikromasch HQ: NSC35/Pt) with a force constant of ~5 N/m and a tip radius of less than 30 nm have been used for all imaging modes. To elucidate the operation mechanism of the VTFET, the band profiles were calculated by using the finite difference (FD) method to solve the 2-D Poisson’s equation.

Data availability

All data supporting this study and findings are presented in the article and the Supplementary Information file in graphic form. Source data are available from the corresponding authors upon request.

References

Salahuddin, S., Ni, K. & Datta, S. The era of hyper-scaling in electronics. Nat. Electron. 1, 442–450 (2018).

Akinwande, D. et al. Graphene and two-dimensional materials for silicon technology. Nature 573, 507–518 (2019).

Luo, Z. D., Yang, M. M., Liu, Y. & Alexe, M. Emerging opportunities for 2D semiconductor/ferroelectric transistor-structure devices. Adv. Mater. 33, 2005620 (2021).

Chen, Z. Gate-all-around nanosheet transistors go 2D. Nat. Electron. 5, 830–831 (2022).

Yakimets, D. et al. Vertical GAAFETs for the ultimate CMOS scaling. IEEE Trans. Electron Devices 62, 1433–1439 (2015).

Sarkar, D. et al. A subthermionic tunnel field-effect transistor with an atomically thin channel. Nature 526, 91–95 (2015).

Yang-Kyu, C., Tsu-Jae, K. & Chenming, H. Nanoscale CMOS spacer FinFET for the Terabit era. IEEE Electron Device Lett. 23, 25–27 (2002).

Veloso, A. et al. Nanowire & nanosheet FETs for ultra-scaled, high-density logic and memory applications. Solid State Electron 168, 107736 (2020).

Jagannathan, H. et al. Vertical-Transport Nanosheet Technology for CMOS Scaling beyond Lateral-Transport Devices. In IEEE International Electron Devices Meeting (IEDM) 26.21.21-26.21.24 (2021).

Tsutsui, G. et al. Hardware Based Performance Assessment of Vertical-Transport Nanosheet Technology. In IEEE International Electron Devices Meeting (IEDM) 34.34.31-34.34.34 (2022).

Song, T. Opportunities and challenges in designing and utilizing vertical nanowire FET (V-NWFET) standard cells for beyond 5 nm. IEEE Trans. Nanotechnol. 18, 240–251 (2019).

Ram, M. S. et al. High-density logic-in-memory devices using vertical indium arsenide nanowires on silicon. Nat. Electron. 4, 914–920 (2021).

Lenz, J. et al. High-performance vertical organic transistors of sub-5 nm channel length. Nano Lett. 21, 4430–4436 (2021).

Heo, J. et al. Graphene and thin-film semiconductor heterojunction transistors integrated on wafer scale for low-power electronics. Nano Lett. 13, 5967–5971 (2013).

Liu, L. et al. Transferred van der Waals metal electrodes for sub-1-nm MoS2 vertical transistors. Nat. Electron. 4, 342–347 (2021).

Georgiou, T. et al. Vertical field-effect transistor based on graphene-WS2 heterostructures for flexible and transparent electronics. Nat. Nanotechnol. 8, 100–103 (2013).

Miao, J. et al. Heterojunction tunnel triodes based on two-dimensional metal selenide and three-dimensional silicon. Nat. Electron. 5, 744 (2022).

Zhang, J., Gao, F. & Hu, P. A vertical transistor with a sub-1-nm channel. Nat. Electron. 4, 325–325 (2021).

Ma, L. et al. Realizing on/off ratios over 104 for sub-2 nm vertical transistors. Nano Lett. 23, 8303–8309 (2023).

Li, E. et al. MXene based saturation organic vertical photoelectric transistors with low subthreshold swing. Nat. Commun. 13, 2898 (2022).

Salahuddin, S. & Datta, S. Use of negative capacitance to provide voltage amplification for low power nanoscale devices. Nano Lett. 8, 405–410 (2008).

Ionescu, A. M. & Riel, H. Tunnel field-effect transistors as energy-efficient electronic switches. Nature 479, 329–337 (2011).

Tang, Z. et al. A steep-slope MoS2/graphene Dirac-source field-effect transistor with a large drive current. Nano Lett. 21, 1758–1764 (2021).

Choi, H. et al. A steep switching WSe2 impact ionization field-effect transistor. Nat. Commun. 13, 6076 (2022).

Shukla, N. et al. A steep-slope transistor based on abrupt electronic phase transition. Nat. Commun. 6, 7812 (2015).

Wang, X. F. et al. Two-mode MoS2 filament transistor with extremely low subthreshold swing and record high on/off ratio. ACS Nano 13, 2205–2212 (2019).

Hua, Q. et al. Atomic threshold-switching enabled MoS2 transistors towards ultralow-power electronics. Nat. Commun. 11, 6207 (2020).

Kim, S. G. et al. Steep-slope gate-connected atomic threshold switching field-effect transistor with MoS2 channel and its application to infrared detectable phototransistors. Adv. Sci. 8, 2100208 (2021).

Huang, M. et al. Multifunctional high-performance van der Waals heterostructures. Nat. Nanotechnol. 12, 1148–1154 (2017).

Cui, Y. et al. High-performance monolayer WS2 field-effect transistors on high-κ dielectrics. Adv. Mater. 27, 5230–5234 (2015).

Xu, Y. et al. Physical properties of an ultrathin Al2O3/HfO2 composite film by atomic layer deposition and the application in thin-film transistors. ACS Appl. Mater. Interfaces 15, 16874–16881 (2023).

Pezeshki, A., Shokouh, S. H., Nazari, T., Oh, K. & Im, S. Electric and photovoltaic behavior of a few-layer α-MoTe2 /MoS2 dichalcogenide heterojunction. Adv. Mater. 28, 3216–3222 (2016).

Wu, L. et al. Atomically sharp interface enabled ultrahigh-speed non-volatile memory devices. Nat. Nanotechnol. 16, 882–887 (2021).

Sun, Y. et al. Performance‐enhancing selector via symmetrical multilayer design. Adv. Funct. Mater. 29, 1808376 (2019).

Si, M. et al. Steep-slope hysteresis-free negative capacitance MoS2 transistors. Nat. Nanotechnol. 13, 24–28 (2018).

Vandenberghe, W. G. et al. Figure of merit for and identification of sub-60 mV/decade devices. Appl. Phy. Lett. 102, 013510 (2013).

del Valle, J., Ramírez, J. G., Rozenberg, M. J. & Schuller, I. K. Challenges in materials and devices for resistive-switching-based neuromorphic computing. J. Appl. Phys. 124, 211101 (2018).

Choi, Y. et al. Low-voltage complementary electronics from ion-gel-gated vertical van der Waals heterostructures. Adv. Mater. 28, 3742–3748 (2016).

Yu, W. J. et al. Vertically stacked multi-heterostructures of layered materials for logic transistors and complementary inverters. Nat. Mater. 12, 246–252 (2013).

Cheng, R. et al. High-performance, multifunctional devices based on asymmetric van der Waals heterostructures. Nat. Electron. 1, 356–361 (2018).

Acknowledgements

We acknowledge support from the National Key R&D Program of China under Grant No. 2023YFB4402303 (Z.-D. L.), the National Natural Science Foundation of China under Grant No. 62025402 (G.H.), 62274128 (Z.-D.L.), 92264202 (Z.-D.L.), 62090033 (Y. Liu), 62293522 (G.H.), 92364204 (Y. Liu), 61971375 (W.C.), the Zhejiang Provincial Natural Science Foundation of China under Grant No. LDT23F04023F04 (Z.-D. L.), LDT23F04024F04 (G. H.), LR21F010003 (W. C.), the Fundamental Research Funds for the Central Universities under Grant No. QTZX23079 (Z.-D. L.), and the Key Research and Development Program of Ningbo City under No. 2023Z071 (Z.-D. L.). Z.-D.L. would like to thank Dr. C. Zhao with Analytic & Testing centre of NPU for the assistance of device fabrication. Z.-D.L. would like to thank Dr. S. Cheng of School of Microelectronics, Xi’an Jiaotong University for the assistance of TEM characterization. J.S. and D.Z. acknowledges support by the Australian Research Council through Discovery Grants and the ARC Centre of Excellence in Future Low Energy Electronics Technologies (FLEET).

Author information

Authors and Affiliations

Contributions

Z.-D. L. conceived the concept, designed the experiments, analysed the data and wrote the manuscript. Q. Y., Z.-D. L., Y. Li and D. T. fabricated the samples. Z.-D. L. and Q. Y. carried out the electrical measurement. H. D., W. C. and Z.-D. L. discussed and performed the model simulation of devices. D. Z. and J. S. conducted the AFM measurement. Z.-D. L., X. G., Y. Liu, Y. H. and G. H. supervised the project, and revised the manuscript with comments from all authors. All authors participated in the discussion and editing of the manuscript.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Nature Communications thanks Woo Jong Yu, and the other, anonymous, reviewers for their contribution to the peer review of this work. A peer review file is available.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Yang, Q., Luo, ZD., Duan, H. et al. Steep-slope vertical-transport transistors built from sub-5 nm Thin van der Waals heterostructures. Nat Commun 15, 1138 (2024). https://doi.org/10.1038/s41467-024-45482-x

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41467-024-45482-x

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.