Abstract

Top gate a-InGaZnO (IGZO) thin-film transistors (TFTs) annealed at high temperature show excellent initial current–voltage (I–V) characteristics. However, when they are exposed to positive gate bias for a long time, hump can occur in the subthreshold region. This abnormal hump is accelerated at a higher positive gate voltage and mitigate by a negative gate voltage. While the strength of the hump is irrelevant to a change in channel width, it relies significantly on channel length. This phenomenon might be due to mobile Na ions diffused from a glass substrate migrating toward the back and edge side of the IGZO semiconductor by a vertical gate electric field. When a layer of Al2O3 is formed between the IGZO semiconductor and the glass substrate, the hump phenomenon could be successfully solved by serving as a barrier for Na ions moving into the IGZO.

Similar content being viewed by others

Introduction

Amorphous InGaZnO (a-IGZO) thin-film transistors (TFTs) have attracted much attention as switching or driving devices of TFT backplanes for applications of flexible, transparent, and large-area displays1,2,3. Due to their advantages such as large-current driving capability, low leakage current, low-temperature process, and superior large area manufacturing uniformity, a-IGZO TFTs are promising candidates that can meet high-performance requirements of advanced active-matrix organic light-emitting diodes (AMOLEDs) such as high resolution, high frame rate driving, and low power consumption4,5,6. However, various types of defects in the bulk or channel interface of an a-IGZO semiconductor can cause problems with long-term electrical stability of the TFT device. Many studies have determined effects of defect states in a-IGZO on electrical properties and reliability of a-IGZO TFT according to external stresses such as voltage, temperature, illumination, and mechanical force7,8,9,10. When observing changes in threshold voltage (Vth) of a-IGZO TFTs against various electrical stresses such as positive gate voltage bias, negative gate voltage bias, and gate bias stress with illumination, a hump might occur in the subthreshold region of current–voltage (I–V) characteristics11,12,13. These bias stress-induced hump phenomena can occur due to formation of a parasitic current path by creating unintentional parallel transistors in local active regions of a-IGZO TFTs14,15,16,17,18. They can eventually cause changes of subthreshold slope or on-set voltage in I–V characteristics of TFTs, resulting in high-pixel defects and bad pixel-uniformity on OLED display panels. Hump phenomena reported in a-IGZO TFTs can be caused by several factors such as back-channel conduction due to migration of various ionized defects inside IGZO semiconductors, charge trapping in the edge region of IGZO active islands, and impact ionization due to a high drain current15,16,17,18,19,20. Therefore, when a hump occurs in a TFT device, it is important to analyze the cause and present a solution for this phenomenon known to deteriorate display images.

In this paper, we investigated a time-delayed hump phenomenon that occurred under a positive gate bias condition of high voltage for a long time in top gate a-IGZO TFTs with excellent I–V characteristics. Changes in the hump for stress time were observed according to different channel widths (W) and lengths (L) of TFTs. In addition, the cause and mechanism of hump generation were identified through various electrical stress measurements and spectrometry analyses of ions in a-IGZO films. It was found that some Na ions diffused into the a-IGZO film from the glass substrate could cause a hump in I–V characteristics. An improvement method was proposed to remove the hump from the a-IGZO TFT.

Methods

A borosilicate glass (Schott, Borofloat®, 0.7 mm, UK) was used as a substrate to fabricate a IGZO TFT device. Indium Tin Oxide (ITO; 20 nm) was deposited and patterned to form source and drain (S/D) electrodes on top of the glass substrate. IGZO (In: Ga: Zn = 1: 1: 1 atomic%, 30 nm) was then deposited with a radio frequency (RF)-magnetron sputtering system. An RF power source (13.56 MHz, 100 W) was employed for depositing IGZO layers. During deposition, the chamber working pressure was set to be 0.67 Pa with argon (Ar): oxygen gas (O2) flow rate ratio of 35: 5 standard cubic centimeters per minute at room temperature. IGZO films were photo-patterned and wet etched with a buffered oxide etchant (200:1, Mattech Resource). Al2O3 as a gate insulator layer was deposited by plasma enhanced atomic layer deposition (PEALD) using trimethyl aluminum (TMA) as a metal source and O2 as a reactant. Plasma power was set to be 100 W at 250 °C. One cycle of atomic layer deposition (ALD) was performed with the following sequence: TMA source injection (0.5 s)–argon (Ar) purge (3.0 s)–O2 injection (1.0 s)–RF-plasma (0.5 s)–Ar purge (5 s). The thickness of Al2O3 layers was set to be 150 nm. After S/D contact holes were formed on the Al2O3 dielectric layer by photolithography, Mo (50 nm) gate electrode was sputter-deposited and patterned to afford IGZO TFTs with a top-gate staggered configuration. These IGZO TFTs were post-annealed at 350 °C for 1 h. Meanwhile, an IGZO TFT with a barrier layer on the glass substrate was fabricated as a comparative TFT device. Before depositing ITO S/D, an Al2O3 barrier layer (50 nm) was formed on the substrate using PEALD under the same deposition conditions (250 °C, 100 W) as a gate insulator. All other TFT processes except for the barrier layer were carried out in the same way. I–V characteristics of a-IGZO TFTs were then measured with gate voltage (Vg) sweep of − 20 V to + 20 V at a constant drain voltage (Vd) of + 10 V using a semiconductor device analyzer (B1500A, Agilent) at room temperature under dark air ambient condition. Time of flight-secondary ion mass spectrometry (TOF–SIMS; M6, IONTOF GmbH) was conducted to determine the amount of each component such as In, Ga, Zn, H, OH, and Cl ions in IGZO films. A cesium (Cs+) primary ion beam was used at a current of 120 nA and a raster size of 200 × 200 mm2. Chemical states of oxygen atoms in Al2O3/IGZO/glass stack and Al2O3/IGZO/Al2O3/glass stack were examined by X-ray photoelectron spectroscopy (K-Alpha+, Thermo Fisher Scientific).

Results and discussion

Electrical characteristics and bias stress stability of top gate a-IGZO TFTs

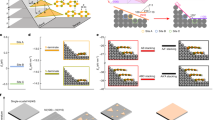

Figure 1a,b show I–V characteristics of top gate a-IGZO TFTs with different channel widths (W = 20, 40, 80, 160 μm with a fixed L of 20 μm) and different channel lengths (L = 5, 10, 20, 40, 80, 160 μm with a fixed W of 160 μm) after annealing at 350 °C for 1 h, respectively. These a-IGZO TFTs exhibited excellent electrical performances and uniformity with field effect mobility of 7.3 ± 0.92 cm2V−1 s−1, Vth of 0.25 ± 0.33 V, subthreshold slope (SS), and 112 ± 44 mVdec−1 in the above-described range of channel width by length (W/L). To examine electrical reliabilities of these a-IGZO TFTs, changes in their I–V curves were observed after they were stressed under positive gate bias condition applying gate voltages of + 10 V, + 20 V, and + 30 V at a fixed drain voltage of + 0.1 V for 10,000 s, respectively. As the gate voltage of TFTs increased, the Vth of transfer curves shifted more to the positive direction as shown in Fig. 2. This could be attributed to an increase in charge trapping at the channel interface of the IGZO semiconductor by a prolonged positive gate bias21,22. Meanwhile, when the stress time reached 10,000 s under positive gate bias stress (PBS), a weak hump appeared in subthreshold region of the I–V curve (Fig. 2a). As shown in Fig. 2b,c, considering that the hump was significantly increased with increasing gate voltage to + 20 V and + 30 V, it was found that this hump phenomenon was generated obviously by a gate bias stress. We noted the occurrence of this abnormal hump at long-term direct current (DC) gate bias stress. To determine whether the same hump would appear in negative gate field, a sustained negative gate bias stress (NBS) to the a-IGZO TFT was applied under the condition of a gate voltage of − 20 V and a drain voltage of + 10 V for 10,000 s. As shown in Fig. 3a, there was little change in the I–V curve up to 3,000 s at NBS. Although the Vth shifted slightly negatively (ΔVth = – 0.98 V) after 10,000 s, no hump occurred. As shown in Fig. 3b, we applied NBS again to the TFT device where the hump was generated by PBS to observe how the hump changed. The hump gradually decreased as NBS continued. It completely disappeared after 10,000 s. Therefore, it was clearly found that the hump phenomenon in the a-IGZO TFTs occurred only by positive gate bias. Meanwhile, according to previous studies on reliabilities of a-IGZO TFTs, impact ionization by strong lateral electric field in drain region of a-IGZO semiconductors can cause hump20,23,24. The electrical reliability in terms of hump against high drain field stress in the a-IGZO TFT was then investigated by applying continuous DC stress under a drain voltage of + 25 V and a gate voltage of + 5 V (Vdg = + 20 V) for 10,000 s. As shown in Fig. 4, there was only a slight increase in drain current after drain current stress. No hump phenomenon appeared. Therefore, the hump phenomenon in our a-IGZO TFTs was not related to the lateral electrical field induced by the high drain voltage. Instead, it was caused by the vertical electrical field formed by gate voltage.

Characterization and analysis for hump generation in top gate a-IGZO TFTs

Several studies have been conducted on hump due to a gate bias stress of a-IGZO TFTs15,16,17,18,19,20. Hump phenomena are known to occur when shallow donor species such as ionized vacancies, metal interstitials, and hydrogen interstitials in a-IGZO semiconductors are trapped in the channel interface or a-IGZO edge region, or when they are trapped in the back channel. We observed changes in I–V curves after applying PBS by 10,000 s to respective TFT devices with various channel widths and channel lengths to understand the generation mechanism of hump caused by gate bias applied to a-IGZO TFTs. Figure 5a shows initial I–V curves of a-IGZO TFTs with a channel length fixed at 20 μm and different channel widths of 20, 40, 80, and 160 μm and I–V curves of those after PBS of 10,000 s. Figure 5b shows I–V curves of IGZO TFTs with a channel width fixed at 160 μm and different channel lengths of 5, 10, 20, 40, 80, and 160 μm before and after PBS. Dashed lines are initial I–V characteristics of a-IGZO TFTs and solid lines are I–V characteristics of those after PBS 10,000 s. As shown in Fig. 5a, the size of the hump was irrelevant to the change in channel width of TFTs. On the other hand, as shown in Fig. 5b, the channel length had an obvious effect. The current level of the hump increased as the channel length was shortened. Considering that the hump phenomenon depended only on channel length, it suggested that a parallel type of parasitic transistor was created in the edge region of a-IGZO active island by continuous PBS, resulting in a hump. We thought that it would not be favorable to explain the gradual hump generation using a shallow donor model related to charged defects such as ionized vacancies, metal interstitials, or hydrogen interstitials created in a-IGZO by PBS. This is because shallow donors in the a-IGZO semiconductor can have more stable formation energy when the Fermi level (EF) is moved away from the conduction band edge by negative gate bias25,26. In other words, it is difficult to suggest that these shallow donors could directly affect the hump because they must be reduced within the IGZO bulk in PBS. In addition, the device characteristics were compared by varying barrier thicknesses such as 2 nm, 5 nm, and 50 nm to compare whether SiO2 serves as a diffusion blocking layer or is more effective than Al2O3 layer. Figure S1a–c show IGZO TFTs with Al2O3 barrier of 50 nm, 5 nm, and 2 nm, respectively. In Al2O3 barrier, hump occurred at 2 nm, but hump did not occur at 5 nm. On the other hand, Fig. S2a–c show IGZO TFTs with SiO2 barrier of 50 nm, 5 nm, and 2 nm, respectively. In SiO2 barrier, the size of hump decreased as the thickness increased, but hump still occurred even at 50 nm. Therefore, it was confirmed that Al2O3 ALD thin film acts as an excellent barrier for Na, but the SiO2 ALD thin film is difficult to use as a good barrier.

On the other hand, this hump phenomenon might be caused by ionic chemical species that have moved from the glass substrate. To prevent ionic chemical species that could affect electrical properties of the TFT coming across from the glass substrate, an Al2O3 barrier layer (50 nm) was formed on top of the glass substrate using PEALD. All other processes were done under the same conditions to fabricate the a-IGZO TFT. Figure 6 shows I–V curves a-IGZO TFTs with Al2O3 barrier under PBS with gate voltage of + 10 V, + 20 V, and + 30 V, respectively. Interestingly, there was no hump in these TFTs at all. From the fact that Al2O3 barrier can solve this problem, the cause of the hump could be diffusion of some cation species to the a-IGZO layer from the glass substrate during a high temperature post-annealing of a-IGZO TFT.

TOF–SIMS analysis was conducted to determine which ionic impurity diffused into the a-IGZO layer affected the hump. With respect to analysis targets, proton, hydroxyl ions, Na ions, and Al ions were considered as candidates of ion species that might affect electrical properties of TFTs by diffusion into IGZO from a glass substrate. Figure 7a shows TOF–SIMS data for a-IGZO thin film without Al2O3 barrier and Fig. 7b shows data for a-IGZO thin film with Al2O3 barrier. Comparing these two SIMS data, it was found that numbers of proton and hydroxyl ions were as small as being negligible (only a few counts for H and OH). Thus, their changes in IGZO according to the presence or absence of Al2O3 barrier might be insignificant, making it difficult to affect the hump in the a-IGZO TFT. It was also found that Na ions diffused a lot inside a-IGZO film when there was no Al2O3 barrier and that Al ions diffused a lot inside IGZO film when there was an Al2O3 barrier. Since the hump phenomenon was only found in a-IGZO TFTs without barrier layer, Al diffusion was not the cause of the hump. Thus, it could be concluded that Na ions should be the chemical species that caused the hump. In addition, XPS analysis was conducted to investigate the basic film quality of a-IGZO on a glass, a-IGZO on Al2O3, and Al2O3. Figure 8 shows O1s spectra of Al2O3/a-IGZO/glass stack and Al2O3/a-IGZO/Al2O3/glass stack. The binding energy of O1s peak of Al2O3 bulk layer was 531.7 eV in both stacks. a-IGZO (531.1 eV) on glass and a-IGZO (531.0 eV) on Al2O3 showed similar O1s spectra in the IGZO bulk film layers. However, the O1s spectrum was quite different in the region close to the rear interface of a-IGZO. a-IGZO (531.0 eV)/glass interface showed relatively higher binding energy than IGZO (530.7 eV)/Al2O3 interface. This showed that the chemical bonding environment of the IGZO rear interfaces might vary considerably due to the difference of inorganic layers such as SiO2 and Al2O3 despite the same binding energy in the a-IGZO bulk regions of the two stacks. Meanwhile, we fabricated a-IGZO TFTs using a Si wafer including SiO2 as an alkali-free substrate. Figure S3 shows the I–V characteristics of a-IGZOTFT on the Si wafer substrate according to the PBS time, but hump did not occur at all. Therefore, by using a Si wafer as an alkali-free substrate, it was possible to reconfirm that Na+ in the substrate was the cause of time-delayed hump in the I–V curve.

Interpretation of hump generation mechanism in top gate a-IGZO TFTs

We examined how Na ions diffused into IGZO could cause a hump. Figure 9 shows 3D-device structures and cross-sectional views of the cross-section passing through the center of the gate in the plan view of the IGZO TFTs. Figure 9a,b show the TFTs without Al2O3 barrier and with Al2O3 barrier, respectively. Especially, Fig. 9a illustrated the process of creating parasitic transistors on edge regions of a-IGZO active island that could cause a hump. To understand the origin of the hump characteristics, TOF–SIMS analysis data before and after post-annealing of 350 °C were compared as shown in Fig. S4. Although post-annealing obviously increased the diffusion of Na ions, Na ions were identified within a-IGZO on glass even before post-annealing. It is believed that the diffused Na ions were detected in a-IGZO even before annealing due to a heat treatment effect by the high temperature deposition process (250 °C) of the Al2O3 gate insulator. Therefore, rather than Na + diffusion being the direct cause of hump, Na + migration (drift) due to an electric field by gate bias might be the cause of hump. Na+ could be migrated to the interface of glass and a-IGZO due to a vertical electrical field formed under PBS. Figure 10 shows an energy band diagram to explain the mechanism of hump generation due to Na+ diffused in the IGZO film by the gate electric field. Figure 10a shows an initial flat-band state of a-IGZO TFT during high-temperature annealing. Due to diffused Na ions from the glass substrate, the energy band would be slightly bent behind the a-IGZO layer. Figure 10b,c show a-IGZO band bending by Na+ migration into the back of the IGZO by the electric field under long-term PBS, presenting the mechanism of hump generation accordingly. Regarding edge regions, both sidewalls of the IGZO are thin. The electric field on the IGZO edge regions would be stronger than that on the a-IGZO bulk layer. Na ions would be quickly trapped, and conduction band lowering might occur first at the edge region. Eventually, the channel of parallel transistors created in the edge regions might open early, causing a hump. In other words, even if the same gate voltage was applied, a-IGZO on the edge region might reach an accumulation state first. IGZO channel on the edge region could be formed earlier than that on the bulk region, leading to the occurrence of a hump. On the other hand, as shown in Fig. 10d,e, when NBS was applied, the trapped Na ions would be de-trapped from the IGZO interface and migrated in the direction of the front channel. Therefore, electrons accumulated at the edge would be depleted and the hump disappeared.

Energy band diagrams of a-IGZO TFTs (a) at initial state after high-temperature annealed, (b) at bulk region under long-term PBS condition, (c) for generation of parasitic transistors causing a hump on the edge region under long-term PBS condition (Na ions would be quickly trapped, and conduction band lowering might occur first at the edge region.), (d) at bulk region under long-term NBS condition, and (e) on the edge region under long-term NBS condition (The trapped Na ions would be de-trapped from the IGZO interface and migrated in the direction of the front channel.).

Conclusion

Top gate a-IGZO TFTs post-annealed at high temperature of 350 °C showed good field effect mobility with uniform Vth and SS at their I–V characteristics according to different channel widths and lengths. However, hump occurred in the subthreshold region when they were exposed to positive gate DC bias stress for a long time (more than 3600 s). This stress-induced hump accelerated at higher positive gate voltage but disappeared by negative gate voltage. In particular, the current level of the hump increased as the channel length was shortened, while it was independent on channel width. It was thought that parallel parasitic transistors might have been created in the edge region of a-IGZO active island during sustained PBS. This could be caused by ionic chemical species moving from the glass substrate. TOF-SIMS analysis confirmed that Na ions were significantly diffused into a-IGZO from glass substrate where there was no Al2O3 barrier layer. To prevent ionic chemical species that could affect electrical properties of the TFT from coming across from the glass substrate, an Al2O3 barrier layer was formed between a-IGZO TFT and glass substrate, leading to no hump in the resultant TFT at all. Mobile Na ions might have migrated to the edge and back side of a-IGZO active island by a vertical gate electric field. Parasitic transistors created at the edge regions might have been turned on earlier to generate hump. Therefore, when Al2O3 layer was formed under a-IGZO TFT, this hump phenomenon could certainly be solved by working as a barrier against Na ions coming cross into a-IGZO.

Data availability

The data that support the findings of this study are available within the article.

References

Hsu, H.-H., Chang, C.-Y. & Cheng, C.-H. A flexible IGZO thin-film transistor with stacked TiO2-based dielectrics fabricated at room temperature. IEEE Electron. Device Lett. 34, 768–770. https://doi.org/10.1109/LED.2013.2258455 (2013).

Kamiya, T. & Hosono, H. Material characteristics and applications of transparent amorphous oxide semiconductors. NPG Asia Mater. 2, 15–22. https://doi.org/10.1038/asiamat.2010.5 (2010).

Kamiya, T., Nomura, K. & Hosono, H. Origins of high mobility and low operation voltage of amorphous oxide TFTs: Electronic structure, electron transport, defects and doping. J. Disp. Technol. 5, 273–288. https://doi.org/10.1109/JDT.2009.2021582 (2009).

Kwon, J. Y. et al. Bottom-gate gallium indium zinc oxide thin-film transistor array for high-resolution AMOLED display. IEEE Electron Device Lett. 29, 1309–1311. https://doi.org/10.1109/LED.2008.2006637 (2008).

Lin, C. L., Chang, W. Y. & Hung, C. C. Compensating pixel circuit driving AMOLED display with a-IGZO TFTs. IEEE Electron. Device Lett. 34, 1166–1168. https://doi.org/10.1109/LED.2013.2271783 (2013).

Wager, J. F., Yeh, B., Hoffman, R. L. & Keszler, D. A. An amorphous oxide semiconductor thin-film transistor route to oxide electronics. Curr. Opin. Solid State Mater. Sci. 18, 53–61. https://doi.org/10.1016/j.cossms.2013.07.002 (2014).

Görrn, P. et al. Stability of transparent zinc tin oxide transistors under bias stress. Appl. Phys. Lett. 90, 063502. https://doi.org/10.1063/1.2458457 (2007).

Jiang, J., Toda, T., Hung, M. P., Wang, D. & Furuta, M. Highly stable fluorine-passivated In–Ga–Zn–O thin-film transistors under positive gate bias and temperature stress. Appl. Phys. Express 7, 114103. https://doi.org/10.7567/APEX.7.114103 (2014).

Yao, J. et al. Electrical and photosensitive characteristics of a-IGZO TFTs related to oxygen vacancy. IEEE Trans. Electron. Devices 58, 1121–1126. https://doi.org/10.1109/TED.2011.2105879 (2011).

Hasan, M. M., Billah, M. M., Naik, M. N., Um, J. G. & Jang, J. Bending stress induced performance change in plastic oxide thin-film transistor and recovery by annealing at 300 °C. IEEE Electron. Device Lett. 38, 1035–1038. https://doi.org/10.1109/LED.2017.2718565 (2017).

Tsai, C. T. et al. Influence of positive bias stress on N2O plasma improved InGaZnO thin film transistor. Appl. Phys. Lett. 96, 242105. https://doi.org/10.1063/1.3453870 (2010).

Yang, J. et al. Investigation of a hump phenomenon in back-channel-etched amorphous In–Ga–Zn–O thin-film transistors under negative bias stress. IEEE Electron. Device Lett. 38, 592–595. https://doi.org/10.1109/LED.2017.2686898 (2017).

Mativenga, M., Haque, F., Billah, M. M. & Um, J. G. Origin of light instability in amorphous IGZO thin-film transistors and its suppression. Sci. Rep. 11, 1–12. https://doi.org/10.1038/s41598-021-94078-8 (2021).

Huzaibi, H. U., Lu, N., Billah, M. M., Geng, D. & Li, L. Investigation of hump behavior of amorphous indium–gallium–zinc–oxide thin-film transistor under positive bias stress. IEEE Trans. Electron. Devices 69, 549–554. https://doi.org/10.1109/TED.2021.3135249 (2022).

Shi, X. et al. Study of positive-gate-bias-induced hump phenomenon in amorphous indium–gallium–zinc oxide thin-film transistors. IEEE Trans. Electron. Devices 67, 1606–1612. https://doi.org/10.1109/TED.2020.2972978 (2020).

Yang, J. et al. Investigation of an anomalous hump phenomenon in via-type amorphous In–Ga–Zn–O thin-film transistors under positive bias temperature stress. Appl. Phys. Lett. 110, 143508. https://doi.org/10.1063/1.4979870 (2017).

Kim, Y. M. et al. Investigation of zinc interstitial ions as the origin of anomalous stress-induced hump in amorphous indium gallium zinc oxide thin film transistors. Appl. Phys. Lett. 102, 173502. https://doi.org/10.1063/1.4803536 (2013).

Kim, W. S. et al. Abnormal behavior with hump characteristics in current stressed a-InGaZnO thin film transistors. Solid State Electron. 137, 22–28. https://doi.org/10.1016/j.sse.2017.08.001 (2017).

Mativenga, M., Seok, M. & Jang, J. Gate bias-stress induced hump-effect in transfer characteristics of amorphous–indium–gallium–zinc–oxide thin-film transistors with various channel widths. Appl. Phys. Lett. 99, 122107. https://doi.org/10.1063/1.3641473 (2011).

Yang, T. J. et al. Physical model of a local threshold voltage shift in InGaZnO thin-film transistors under current stress for instability-aware circuit design. Curr. Appl Phys. 46, 55–60. https://doi.org/10.1016/j.cap.2022.11.011 (2023).

Chen, T. C. et al. Investigating the degradation behavior caused by charge trapping effect under DC and AC gate-bias stress for InGaZnO thin film transistor. Appl. Phys. Lett. 99, 022104. https://doi.org/10.1063/1.3609873 (2011).

Chen, T. C. et al. Behaviors of InGaZnO thin film transistor under illuminated positive gate-bias stress. Appl. Phys. Lett. 97, 112104. https://doi.org/10.1063/1.3481676 (2010).

Choi, S. H. & Han, M. K. Effect of channel widths on negative shift of threshold voltage, including stress-induced hump phenomenon in InGaZnO thin-film transistors under high-gate and drain bias stress. Appl. Phys. Lett. 100, 043503. https://doi.org/10.1063/1.3679109 (2012).

Wang, D., Zhao, W., Li, H. & Furuta, M. Drain current stress-induced instability in amorphous InGaZnO thin-film transistors with different active layer thicknesses. Materials 11, 559. https://doi.org/10.3390/ma11040559 (2018).

de Jamblinne de Meux, A., Bhoolokam, A., Pourtois, G., Genoe, J. & Heremans, P. Oxygen vacancies effects in a-IGZO: Formation mechanisms, hysteresis, and negative bias stress effects. Phys. Status Solidi A 214, 1600889. https://doi.org/10.1002/pssa.201600889 (2017).

Li, H., Guo, Y. & Robertson, J. Hydrogen and the light-induced bias instability mechanism in amorphous oxide semiconductors. Sci. Rep. 7, 1–9. https://doi.org/10.1038/s41598-017-17290-5 (2017).

Acknowledgements

This work was supported by the Technology Innovation Program (20010804) funded by the Ministry of Trade, Industry and Energy (MOTIE), Republic of Korea. It was also supported by the National Research Foundation of Korea (NRF) funded by the Ministry of Science and ICT (RS-2022-00143178), Republic of Korea.

Author information

Authors and Affiliations

Contributions

B.S.K. designed and supervised the research. S.H.P, M.Y.K, H.W.K, C.O., H.K.L. performed the experiments and analyzed the data. All authors discussed the results and reviewed the manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher's note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary Information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Park, S.H., Kim, M.Y., Kim, H.W. et al. Investigating an abnormal hump phenomenon in top gate a-InGaZnO thin-film transistors due to mobile sodium diffusion. Sci Rep 13, 13714 (2023). https://doi.org/10.1038/s41598-023-40664-x

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-023-40664-x

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.