Abstract

Josephson superconducting qubits and parametric amplifiers are prominent examples of superconducting quantum circuits that have shown rapid progress in recent years. As such devices become more complex, the requirements for reproducibility of their electrical properties across a chip are being tightened. Critical current of the Josephson junction Ic is the essential electrical parameter in a chip. So, its variation is to be minimized. According to the Ambegaokar–Baratoff formula, critical current is related to normal-state resistance, which can be measured at room temperature. In this study, we focused on the dominant source of non-uniformity for the Josephson junction critical current–junction area variation. We optimized Josephson junction fabrication process and demonstrated resistance variation of 9.8–4.4% and 4.8–2.3% across 22 × 22 mm2 and 5 × 10 mm2 chip areas, respectively. For a wide range of junction areas from 0.008 to 0.12 μm2, we ensure a small linewidth standard deviation of 4 nm measured over 4500 junctions with linear dimensions from 80 to 680 nm. We found that the dominate source of junction area variation limiting \({\mathrm{I}}_{\mathrm{c}}\) reproducibility is the imperfection of the evaporation system. The developed fabrication process was tested on superconducting highly coherent transmon qubits (T1 > 100 μs) and a nonlinear asymmetric inductive element parametric amplifier.

Similar content being viewed by others

Introduction

As the complexity of superconducting quantum circuits grows with an increase of number of qubits, the tolerances for its frequency allocations are tightened to avoid frequency crowding1 or to obtain the exact interaction frequencies depending on the circuit architecture. Recent quantum processors and simulators already contain dozens and even hundreds of transmon qubits2,3,4,5,6,7,8,9 making qubit frequency reproducibility one of the crucial challenges. Transmon transition frequency follows \(\mathrm{\hslash }{\mathrm{f}}_{01}\approx \sqrt{8{\mathrm{E}}_{\mathrm{c}}{\mathrm{E}}_{\mathrm{j}}}-{\mathrm{E}}_{\mathrm{c}}\), where \({\mathrm{E}}_{\rm{c}}=\frac{{\mathrm{e}}^{2}}{2\mathrm{C}}\) is charging energy and \({\mathrm{E}}_{\rm{j}}= \frac{\mathrm{\hslash }{\mathrm{I}}_{\rm{c}}}{2\mathrm{e}}\) is Josephson energy10. Qubit charging energy is accurately controlled, since capacitance \(\mathrm{C}\) depends on the dimensions of a planar electrode which can be reproducibly fabricated with modern microtechnology. Critical current \({\mathrm{I}}_{\rm{c}}\) at zero temperature is related to the normal-state resistance \({\mathrm{R}}_{\mathrm{n}}\) by the Ambegaokar–Baratoff formula \({\mathrm{I}}_{c}=\frac{\pi \Delta }{2{\mathrm{eR}}_{\mathrm{n}}}\), where \(\Delta\) is the superconducting energy gap11. The resistance can be measured at room temperature. \({\mathrm{I}}_{\mathrm{c}}\) of the tunnel junction, in turn, is defined by linear dimensions, tunnel barrier thickness, its microscopic structure and the material of the superconductor used. Typical nanoscale linewidth of Josephson junctions is challenging to reproduce with low variation using Niemeyer-Dolan technology12,13. Any deviation of the linear dimensions of the tunnel barrier directly affects qubit frequency. Moreover, some qubit architectures, for example, fluxoniums or \(0-\uppi\) qubits require frequency tunability14,15. In this case, parallel tunnel-junctions with significant asymmetry (50:1–70:1) are introduced in order to obtain the desired Hamiltonian parameters and to reduce the sensitivity to flux-noise16,17.

On the other hand, parametric amplifiers based on superconducting nonlinear asymmetric inductive elements (SNAIL)18 and travelling wave parametric amplifiers (TWPA)19 require long arrays of multiple high asymmetry nonlinear elements, which determine their amplification range and saturation power. The above-described high asymmetry features require reliable design and fabrication of Josephson junction arrays with a wide range of areas (spanning from 0.01 to 1 μm2) on a single chip with the precise control of the small junction area. One could increase the area of the junctions with increased oxide thickness for better critical current control, but it leads to additional noisy two-level defects20.

In previous works dealing with Al-AlOx-Al junctions suitable for superconducting qubit fabrication, 2.5–6.3% normal resistance variation was reported for 0.01–0.16 μm2 junction area on a 76-mm wafer21. In another study22, the variation of 1.8% and 3.5% for \({\mathrm{R}}_{\mathrm{n}}\) of 0.042 μm2 was demonstrated for the junctions across 10 × 10 mm2 chip and 49 cm2 area, respectively. Although impressive results were obtained, the authors did not control linear dimensions. The assessment of junction fabrication reproducibility was carried out solely by measuring the resistance of the SQUID without tight control of the smaller junction. So, the asymmetry value was not controlled. It is worth noting, that fabrication of josephson junctions for superconducting qubit is rarely described in detail.

In this work, we report on improving fabrication reproducibility for small Josephson junctions (down to 80 nm) and investigate the origins of junction area non-uniformity. First, we strived to reduce the variation of linear dimensions of small junctions by optimizing e-beam lithography and get the standard deviation of linewidth less than 4 nm for resist Dolan bridge features width from 80 to 680 nm. Secondly, we minimized junction resistance variation and line edge roughness (LER) by optimizing the evaporation angle. As the result, we obtained 9.8–4.4% and 4.8–2.3% resistance variation for 22 × 22 mm2 and 5 × 10 mm2 chips respectively in a wide range of junction areas from 0.008 μm2 up to 0.12 μm2 using the standard Niemeyer-Dolan technique. Furthermore, our research shows a strong correlation of 0.82 between the junction area and the resistance, especially for small junctions of about 100 nm. We also show, that reproducibility is limited by the imperfection of the evaporation system.

Materials and methods

The Josephson junctions (JJ), described in this work, were fabricated using the Niemeyer–Dolan technique. This method does not require large evaporation angles, unlike Manhattan junctions23,24, which leads to worse line edge roughness. Another advantage is a better suitability for fabrication of large arrays of junction, e.g., for fluxonium or parametric amplifiers, where junctions have to be placed directly one after another. However, this method has a poor Dolan bridge stability and narrow process window and, therefore, precise control of the fabrication operations is required. The recently developed subtractive methods for junction fabrication have shown promising results25,26,27,28. However, these methods require additional process steps with an extremely careful control of interfaces, which makes fabrication significantly more complicated. Nonetheless, the recommendations given in this paper apply for all the three methods.

For this study, 1 × 1 inch2 high high-resistivity silicon substrates (> 10,000 \(\Omega \cdot \mathrm{cm}\)) were used. Next, a 100 nm thick Single-crystalline Continuous Ultra-Smooth Low-loss Low-cost (SCULL) 29 Al base layer is deposited with ultra high vacuum (UHV) e-beam evaporation system. Probe pads were defined using a direct-laser lithography and then dry-etched in BCl3/Cl2 inductively coupled plasma. Resist bilayer for junction itself is composed of MMA(8.5)MMA copolymer (500 nm) and chemically amplified resist CSAR 62 (100 nm).

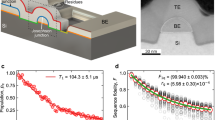

Resist thicknesses were precisely controlled to minimize junction area variation. Resist thickness range \(3\upsigma\) is typically less than 5 nm. The Josephson junctions are then defined using a 50 kV electron-beam lithography tool. The development was performed manually in a bath of amilacetat at room temperature followed by a 60 s IPA dip and addittional 240 s in a IPA:DIW solution to get 200 nm undercut. We use oxygen descum followed by buffered oxide etchant (BOE) dip in order to remove e-beam resist residues and native oxide. Aluminum junction electrodes were e-beam shadow-evaporated in a UHV system. The first electrode was evaporated at \({\mathrm{\alpha }}_{1}\) angle, which we varied in our experiments. Then the electrode was statically oxidized at 5.2 mBar during 10 min. The second electrode was evaporated at \({\mathrm{\alpha }}_{2}=0\) angle, (see Fig. 1) for the cartoon of the process. Thicknesses of bottom and top electrodes are 25 nm and 45 nm, respectively. Resist lift-off was performed in a bath of N-methyl-2-pyrrolidone at 80 °C for 3 h and rinsed in a bath of IPA with sonication. Junction normal resistance was measured with an automatic probe station.

Niemeyer–Dolan bridge technique used in this paper. (a) Scheme of the used shadow evaporation process. The first metal layer was deposited at an angle (dark grey color) through two-layer resist mask MMA-CSAR, and the second layer at 0 angle (light grey color). Angular deposition was performed first, in order to avoid shading from the junction wall at the second deposition, causing electrode discontinuity. (b) Top view SEM image of the fabricated junction after the removal of the resist mask.

Experimental overview

The dominant source of junction resistance non-uniformity is junction area variation22. The deviation of the mask feature size could be minimized by optimizing e-beam lithography (EBL) process30,31. There is typically a large junction wiring area (1–25 μm2) leading to significant backscattering exposure of Dolan bridge during EBL. We simulated proximity effect using Monte Carlo method for the two different mask stacks: MMA-PMMA A4 and MMA-CSAR 62. The simulations indicate that the dose on the junction area increases by ~ 30% due to backscattering exposure, that corresponds to widening of the feature size by 50 nm in case of PMMA A4 top layer. The backscattering for the highly sensitive AR-P 6200.04 was three times lower. In the experiments, we used a high-sensitivity resist to minimize backscattering and fixed wiring design to keep linewidth (LW) biases constant.

First, we optimized e-beam lithography: writing field size (FS) and step size (SS) to study LW variations by measuring more than 1200 junctions. Direct scanning electron microscopy (SEM) measurement of the resist mask LW is challenging, since the electron beam damages the resist mask and distorts the results. To overcome this problem, we instead measured the width of sputtered at 0° “shadows” of the mask features using an automatic SEM tool. Our test chip contained 98 junctions for each of the the patterning parameter: field size (50, 100, 200, 500 μm), scanning direction (longitudinal and transverse), step size (2, 3, 5 nm) and linewidths: (100, 103, 105, 150, 300, 500 nm). The exposed area of the topology is divided into square write fields—maximum area that can be written at fixed stage position with the size FS. We minimized writing field size (FS) in order to lower beam deflection and therefore lower aberrations, which increase LW variations and edge roughness. A cartoon of the layout exposure process is shown on (Fig. 2a). With the smaller FS of 100 μm instead of 500 μm the linewidth 3σ variation decreases from 17.4 to 7.1 nm. For FS less than 100 μm the LW variation does not change (see Fig. 2b). We noticed the lowering of maximum positioning deviation from 41 to 33 nm for 500 μm and 200 μm field size, respectively, that may be explained by reduction of spherical aberrations.

(a) Electron beam lithography process. From bottom to top: test chip, enlarged image of a single cell with a junction in the center, hidden image of the Josephson junction in the resist. (b) Measured linewidth (LW) variation of the nominal 100 nm feature size grouped by field size. Inlet shows 3σ of linewidth variation. Dot color corresponds to the bars in the main picture. (c) Histograms of measured linewidths for 100 nm (blue), 103 nm (red) and 105 nm (yellow) nominal dimensions. When lines are scanned longitudinally (left picture), close nominal linewidth are undistinguishable, since their LW histograms overlap completely and average values are the same. The lines scanned transversely (right) have LW average values difference corresponding to the beam step size.

Within the field size the pattern is scanned with a step size, which is limited by pattern generator frequency. The calculated step size equals to 2 nm for our 50 MHz tool with 180 μC/cm2 and 200 pA beam current. We tried to obtain the highest accuracy corresponding to our step size. We did not observe any differences between exposed nominal feature sizes of 100 nm and 103 nm, when e-beam scanned parallel to the longest edge of a feature (longitudinally). We used another scanning algorithm that scanned the junctions transversely and then the difference of 2 nm between feature sizes reproduced (Fig. 2c). The measurement results for the other nominal linewidths are listed in the supplementary materials.

Next, we experimentally investigated the influence of deposition angle on the mask LER. We automatically measured LER of the resist mask and the bottom electrode. We used Matlab and ImageJ for image recognition and LER quantification. Line edge roughness of the electrodes grows slowly from 2 nm for the deposition angles from 0° to 45° up to 4 nm, and dramatically increases starting from 45° (Fig. 3a). Such a big LER values can affect the \({\mathrm{I}}_{\mathrm{c}}\) variation of comparably small junctions (sub 100 nm), which are common for many devices.

(a) Line edge roughness of resist mask after evaporation (purple) and bottom electrode (yellow) as a function of deposition angle (b) SEM image of resist mask after evaporation at \({\mathrm{\alpha }}_{1}=\) 62°. (c) SEM image of measured bottom electrode evaporated at \({\mathrm{\alpha }}_{1}=\) 62°. (d) Measured normal resistances grouped by nominal junction area. Blue color corresponds to junctions evaporated at 40° angle with electrodes fully overlayed. Yellow-junctions evaporated at 35° with incomplete electrodes overlay. (e,f) SEM images of 0.01 μm2 junctions used in the experiment with and without full overlay respectively.

After the first junction electrode deposition at an angle, there is a rough metal layer deposited on the resist mask walls (Fig. 3b), which increases LER of the resist mask. This increased resist mask roughness transfers into the first (Fig. 3c) and second deposited electrodes. However, smaller evaporation angle could lead to unstable overlay of the electrodes which results in additional resistance variation (Fig. 3d). We experimentally compared two different evaporation angles \({\mathrm{\alpha }}_{1}\) of 40° with full overlay (Fig. 3e) and 35° with partial overlay (Fig. 3f) by measuring 5000 Josephson junctions with areas from 0.008 to 0.12 μm2. There is the factor of two improvements in resistance spread for the electrodes with full overlay. Out theory is that there are slightly different evaporation angles across the substrate due to evaporation system imperfectness. This imperfection lies in the fact that the source of evaporation is a point, therefore the flow of the evaporated metal has a conical shape. Because of such shape of the metal flow, the deposition angles across the wafer are distorted32. The margin for junction electrodes overlap compensates this angle variation. The overlay margin can be increased by reducing the width of the bridge, but minimal bridge width is limited by its stability. We used 150 nm wide bridge in our experiments, as it provides robustness for the whole range of junction areas.

Results and discussion

For a quantitative investigation of JJ reproducibility across the substrate, we fabricated 22 × 22 mm2 chip with a statistically significant number of Josephson junctions (> 5000) and measured their normal resistance at room temperature. The substrate contained six 5 × 10 mm2 chips with different junction areas: 0.008, 0.010, 0.012, 0.025 and 0.120 μm2. (Fig. 4a) shows heat maps of measured resistances and LWs across the sample, fabricated with the following parameters: 100 nm field size, 2 nm step size, 40° evaporation angle. Resistance spread across the substrate is 4.4–9.8% for JJ areas 0.120–0.008 μm2, the average inter-chip variation is 3.1–6.3%. Furthermore, the average variation is 2.3–4.8% across single 5 × 10 mm2 chip. Substrate-scale chip LW standard deviation σ for 150 × 170 nm2 junctions is about 4 nm. (The heat maps of the other junction areas can be found in supplementary materials) (Fig. 4b) shows normal resistance for the directly measured JJ areas.

(a) Heat maps of measured top electrode LW and resistance RN for 150 × 170 nm2 junctions. For both the LW map and the resistance map, there is a visible gradient stemming from evaporation source imperfection. (b) Measured resistance vs. measured junction area. Junctions were fabricated in three area groups: 0.008, 0.025 and 0.12 μm2. Solid line is a linear fit. SEM images of the junction in the corresponding junction area groups. SEM-images show fabricated Josephson junctions with corresponding 0.008, 0.025 and 0.12 μm2 areas.

The slope of the linear fit is −1, since \(\mathrm{R }= 1/\mathrm{A}\), where A is the area of the junction. The correlation coefficient between the normal resistance and the JJ area is 0.82, thus the main contributor in \({\mathrm{R}}_{\mathrm{n}}\) fluctuation is LW variation. We speculate that the other source of resistance spread is oxidation inhomogeneity. The oxidation inhomogeneity depends both on the microstructure of the electrode surface22,33,34,35, which depends on the deposition parameters, and on the oxidation parameters of the tunnel barrier, such as the process time, oxygen pressure, and the oxidation method32,36. We observe a linearly dependent gradient of resistance on the heat map, which is also reproduced on LW heat map. We assume that the gradient of \({\mathrm{R}}_{\mathrm{n}}\) originates from the imperfection of the evaporation source. To test this hypothesis, we fabricated another substrate, with the both electrodes evaporated at 0° angle to eliminate any significant angle variations. LW variation gradient became less visible. The LW standard deviation σ at 0° angle was lower than at 45°: 3.3 nm against 4 nm (the heat map is presented in the supplementary materials). A possible practical solution to eliminate the gradient could be to use a bias of the resist mask linewidth features to compensate the junction area variation. To summarize, our Junctions resistance variation is mostly limited by junction area fluctuations, which, in turn, are limited by evaporation system imperfectness and resolution of our 50 keV e-beam lithography tool.

To test the developed process, we fabricated and measured two similar chips with 6 single transmon qubits each using the optimized lithography and evaporation parameters for junctions described in this work.

We also deposited bandages to shortcut the parasitic junctions37 and placed free-standing airbridges across microwave lines in order to supress the parasitic modes. Two qubits on the chip were frequency-fixed, the other had various SQUID asymmetries α (0.25, 0.35, 0.45, 0.55). The areas of 250 × 260 nm2 for single junction and 200 × 220 nm2 for the larger junction of the asymmetrical SQUIDs were used. The chips were wire-bonded in the Cu boxes and measured in dilution refrigerator at 20 mK. Coherence and frequency masurements are presented in Table 1. Next, we fabricated and tested a SNAIL parametric amplifier with 25 SNAIL cells and large asymmetry38. The areas of 0.63 μm2 and 0.055 μm2 for large and small junctions respectively were used (α = 0.087) to obtain the frequency of 6 GHz.

Summary and conclusions

To improve Josephson junction reproducibility, we performed a systematic study of fabrication process origins of critical current non-uniformity, focusing on junction area fluctuations. To that end, we fabricated a significant number of junctions and directly measured their dimensions and normal resistance. A high-sensitivity resist stack was picked to lower the backscattering exposure. We minimized the e-beam lithographer field size to improve junction linewidth variation and used a proper scanning algorithm to increase accuracy. Evaporation angle showed a direct effect on the junction line edge roughness. LER of the resist mask transfers to the deposited junction and grows with increasing evaporation angle. We provided a complete junction electrode overlay and improved resistance variation compared to the incomplete overlay. The developed fabrication process demonstrated 9.8–4.4% and 4.8–2.3% resistance variation for 22 × 22 mm2 and 5 × 10 mm2 chips respectively in a wide range of junction areas from 0.008 μm2 up to 0.12 μm2. We found a strong correlation of 0.82 between the normal resistivity and the junction area. Junction reproducibility is dominantly limited by the fluctuations of the resist mask linewidth and could be further improved by using a lithography tool with a higher resolution. We have also noticed that the evaporation system imperfectness distorts junction area and therefore increases \({\mathrm{I}}_{\mathrm{c}}\) variation.

Data availability

The datasets used and/or analysed during the current study available from the corresponding author on reasonable request.

References

Hertzberg, J. B. et al. Laser-annealing Josephson junctions for yielding scaled-up superconducting quantum processors. npj Quantum Inf. 7, 129. https://doi.org/10.1038/s41534-021-00464-5 (2021).

Arute, F. et al. Quantum supremacy using a programmable superconducting processor. Nature 574, 505–510. https://doi.org/10.1038/s41586-019-1666-5 (2019).

Jurcevic, P. et al. Demonstration of quantum volume 64 on a superconducting quantum computing system. Quantum Sci. Technol. 6, 025020. https://doi.org/10.1088/2058-9565/abe519 (2021).

Chow, J., Dial, O. & Gambetta, J. IBM Quantum Breaks the 100-Qubit Processor Barrier. https://research.ibm.com/blog/127-qubit-quantum-processor-eagle (IBM Research, 2021).

Krinner, S. et al. Realizing repeated quantum error correction in a distance-three surface code. Nature 605, 669–674. https://doi.org/10.1038/s41586-022-04566-8 (2022).

Zhu, Q. et al. Quantum computational advantage via 60-qubit 24-cycle random circuit sampling. Sci. Bull. 67(3), 240–245. https://doi.org/10.1016/j.scib.2021.10.017 (2022).

Acharya, R. et al. Suppressing quantum errors by scaling a surface code logical qubit. arXiv preprint arXiv:2207.06431. https://doi.org/10.48550/arXiv.2207.06431 (2022).

Besedin, I. S. et al. Topological excitations and bound photon pairs in a superconducting quantum metamaterial. Phys. Rev. B 103, 224520. https://doi.org/10.1103/PhysRevB.103.224520 (2021).

Fedorov, G. P. et al. Photon transport in a Bose-Hubbard chain of superconducting artificial atoms. Phys. Rev. Lett. 126, 180503. https://doi.org/10.1103/PhysRevLett.126.180503 (2021).

Koch, J. et al. Charge-insensitive qubit design derived from the Cooper pair box. Phys. Rev. A 76, 042319. https://doi.org/10.1103/PhysRevA.76.042319 (2007).

Ambegaokar, V. & Baratoff, A. Tunneling between superconductors. Phys. Rev. Lett. 10, 486. https://doi.org/10.1103/PhysRevLett.10.486 (1963).

Niemeyer, J. & Kose, V. Observation of large dc supercurrents at nonzero voltages in Josephson tunnel junctions. Appl. Phys. Lett. 29, 380–382. https://doi.org/10.1063/1.89094 (1976).

Dolan, G. J. Offset masks for lift-off photoprocessing. Appl. Phys. Lett. 31, 337–339. https://doi.org/10.1063/1.89690 (1977).

Manucharyan, V. E. et al. Fluxonium: Single cooper-pair circuit free of charge offsets. Science 326(5949), 113–116. https://doi.org/10.1126/science.1175552 (2009).

Gyenis, A. et al. Experimental realization of a protected superconducting circuit derived from the 0–π qubit. PRX Quantum 2, 010339. https://doi.org/10.1103/PRXQuantum.2.010339 (2021).

Moskalenko, I. N. et al. High fidelity two-qubit gates on fluxoniums using a tunable coupler. npj Quantum Inf. 8, 130. https://doi.org/10.1038/s41534-022-00644-x (2022).

Moskalenko, I. N. et al. Tunable coupling scheme for implementing two-qubit gates on fluxonium qubits. Appl. Phys. Lett. 119, 194001. https://doi.org/10.1063/5.0064800 (2021).

Frattini, N. E. et al. Optimizing the nonlinearity and dissipation of a snail parametric amplifier for dynamic range. Phys. Rev. Appl. 10, 054020. https://doi.org/10.1103/PhysRevApplied.10.054020 (2018).

Ranadive, A. et al. Kerr reversal in Josephson meta-material and traveling wave parametric amplification. Nat. Commun. 13, 1737. https://doi.org/10.1038/s41467-022-29375-5 (2022).

Nugroho, C. D., Orlyanchik, V. & Van Harlingen, D. J. Low frequency resistance and critical current fluctuations in Al-based Josephson junctions. Appl. Phys. Lett. 102, 142602. https://doi.org/10.1063/1.4801521 (2013).

Osman, A. et al. Simplified Josephson-junction fabrication process for reproducibly high-performance superconducting qubits. Appl. Phys. Lett. 118, 064002. https://doi.org/10.1063/5.0037093 (2021).

Kreikebaum, J. M. et al. Improving wafer-scale Josephson junction resistance variation in superconducting quantum coherent circuits. Supercond. Sci. Technol. 33, 06LT02. https://doi.org/10.1088/1361-6668/ab8617 (2020).

Potts, A. et al. CMOS compatible fabrication methods for submicron Josephson junction qubits. IEE Proc.-Sci. Meas. Technol. 148, 225–228. https://doi.org/10.1049/ip-smt:20010395 (2001).

Lecocq, F. et al. Junction fabrication by shadow evaporation without a suspended bridge. Nanotechnology 22, 315302. https://doi.org/10.1088/0957-4484/22/31/315302 (2011).

Stehli, A. et al. Coherent superconducting qubits from a subtractive junction fabrication process. Appl. Phys. Lett. 117, 124005. https://doi.org/10.1063/5.0023533 (2020).

Winkel, P. et al. Nondegenerate parametric amplifiers based on dispersion-engineered Josephson-junction arrays. Phys. Rev. Appl. 13, 024015. https://doi.org/10.1103/PhysRevApplied.13.024015 (2020).

Bal, M. et al. Overlap junctions for superconducting quantum electronics and amplifiers. Appl. Phys. Lett. 118, 112601. https://doi.org/10.1063/5.0048621 (2021).

Verjauw, J. et al. Path toward manufacturable superconducting qubits with relaxation times exceeding 0.1 ms. npj Quantum Inf. 8, 93. https://doi.org/10.1038/s41534-022-00600-9 (2022).

Rodionov, I. A. et al. Quantum engineering of atomically smooth single-crystalline silver films. Sci. Rep. 9, 12232. https://doi.org/10.1038/s41598-019-48508-3 (2019).

Astrand, M. et al. Understanding dose correction for high-resolution 50 kV electron-beam lithography on thick resist layers. MNE 16, 100141. https://doi.org/10.1016/j.mne.2022.100141 (2022).

Guo, S. et al. Fabrication of superconducting niobium nitride nanowire with high aspect ratio for X-ray photon detection. Sci. Rep. 10, 9057. https://doi.org/10.1038/s41598-020-65901-5 (2020).

Moskalev, D. O. et al. Optimization of shadow evaporation and oxidation for reproducible quantum Josephson junction circuits. Sci. Rep. 13, 4174. https://doi.org/10.1038/s41598-023-31003-1 (2023).

Zeng, L. J. et al. Direct observation of the thickness distribution of ultra thin AlOx barriers in Al/AlOx/Al Josephson junctions. J. Phys. D Appl. Phys. 48, 395308. https://doi.org/10.1088/0022-3727/48/39/395308 (2015).

Nik, S. et al. Correlation between Al grain size, grain boundary grooves and local variations in oxide barrier thickness of Al/AlOx/Al tunnel junctions by transmission electron microscopy. Springerplus 5, 1067. https://doi.org/10.1186/s40064-016-2418-8 (2016).

Fritz, S. et al. Correlating the nanostructure of Al-oxide with deposition conditions and dielectric contributions of two-level systems in perspective of superconducting quantum circuits. Sci. Rep. 8, 7956. https://doi.org/10.1038/s41598-018-26066-4 (2018).

Tolpygo, S. K. et al. Properties of unshunted and resistively shunted Nb/AlOx-Al/Nb Josephson junctions with critical current densities from 0.1 to 1 mA/μm2. IEEE Trans. Appl. Supercond. 27(4), 1–15. https://doi.org/10.1109/TASC.2017.2667403 (2017).

Dunsworth, A. et al. Characterization and reduction of capacitive loss induced by sub-micron Josephson junction fabrication in superconducting qubits. Appl. Phys. Lett. 111, 022601. https://doi.org/10.1063/1.4993577 (2017).

Ezenkova, D. et al. Broadband SNAIL parametric amplifier with microstrip impedance transformer. Appl. Phys. Lett. 121(23), 232601. https://doi.org/10.1063/5.0129862 (2022).

Acknowledgements

Technology was developed and samples were made at the BMSTU Nanofabrication Facility (FMN Laboratory, FMNS REC, ID 74300).

Author information

Authors and Affiliations

Contributions

A.A.P., N.S.S. and I.A.R. conceptualized the ideas of the project. A.A.P. and N.S.S. prepared writing-original draft. A.A.P., D.A.E. and D.O.M. fabricated experimental samples and discussed results. D.A.E. and E.A.K. performed morphology characterization. E.V.Z. and N.D.K. performed shadow evaporation process. A.I.I. and N.S.S. conducted the electrical characterization of the experimental samples. A.A.P., N.S.S. and I.A.R. reviewed and edited the manuscript. I.A.R. supervised the project. All authors analyzed the data and contributed to writing the manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher's note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary Information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Pishchimova, A.A., Smirnov, N.S., Ezenkova, D.A. et al. Improving Josephson junction reproducibility for superconducting quantum circuits: junction area fluctuation. Sci Rep 13, 6772 (2023). https://doi.org/10.1038/s41598-023-34051-9

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-023-34051-9

This article is cited by

-

Wiring surface loss of a superconducting transmon qubit

Scientific Reports (2024)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.