Abstract

Multilevel nonvolatile transistor memories were fabricated using star-shaped poly((4-diphenylamino)benzyl methacrylate) (star-PTPMA) electret dielectric for charge storage and N,N′-bis(2-phenylethyl)perylene-3,4,9,10-bis(dicarboximide) (BPE-PTCDI) as an n-type semiconductor. Charges were controllably stored by applying a negative voltage bias, detected by shifting the threshold voltage, and this device retained the digital states even when the supplied voltage was removed. The multilevel data storage characteristics obtained by applying different gate voltages suggested that the device possessed nonvolatile write-many-read-many (WMRM) memory behaviors. The electronic charges were transferred and permanently accumulated in the gate electret from the restricting region of the star-PTPMA with well-defined charge trapping elements, but not in the case of linear-PTPMA. P-type pentacene was also used as a semiconductor layer to clarify the operating mechanism under a gate electric field. Our results demonstrated the significance of the architecture effect of the polymer electrets for nonvolatile organic transistor memory devices and their potentials in high-density data storage.

Similar content being viewed by others

Introduction

Electrical memory devices based on organic polymeric materials generally offer the advantages of low cost, easy processability and structural flexibility in comparison with inorganic silicone-based devices.1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12 Resistor- and transistor-based memory devices are popular architectural approaches for operating the memories. Data storage with resistor memories employs the changes in resistance in response to an applied voltage bias.3, 4, 5, 6, 7 In contrast, transistor memories use the direct integration of the memory elements with a transistor, and an additional electric field introduced at the gate electrode modulates the charge distribution and channel current of the device.1, 2, 3, 4, 5 Furthermore, the configuration of transistor memories minimizes the effects of metal filaments induced by the migration of metal atoms between the electrodes and the sneak current problem that frequently occurs in cross-point memory device cells.

The key parameter in the operation of transistor memories is the reproducibility of the current–voltage characteristics, which may be affected by the hysteresis sweep or shift of the threshold voltage, thereby creating bistable and multistable transistor transfer curves.1, 2, 3, 4, 5, 10 The storage of charge in a transistor dielectric can be achieved using chargeable polymer electrets,13, 14, 15, 16, 17, 18, 19, 20 organic ferroelectric oriented-dipole dielectric materials,21, 22, 23 and nanoparticles embedded or nanostructured gate dielectrics.24, 25, 26, 27, 28 An electret is a dielectric material that has a quasi-permanent electric charge. Therefore, charges can be locally trapped in a layer of chargeable dielectrics in polymer electret memories. Katz et al.13 first proposed a quasi-stable threshold voltage shift in 1−2-μm-thick poly(4-methylstyrene) or cyclic olefin copolymers. The polarity effects of electrets on nonvolatile transistor memories were investigated by Kim et al.14, 15 by comparing various styrenic polymer gate electrets. The magnitude of available memory was inversely proportional to both the hydrophilicity and polarity of the dielectric. Nonpolar and hydrophobic polymers were favorable for producing efficient chargeable dielectrics. Our group has also reported on the nonvolatile flash memory characteristics of a pentacene-based transistor that employed polystyrene that was para-substituted with a π-conjugated oligofluorene as an electret.18 The memory-switching behaviors were related to the length of the fluorene pendent, and a longer conjugation length significantly enhanced the information storage ability.

However, the above efforts have focused on linear polymeric systems with aromatic π-conjugated pendent moieties as the electret materials for transistor memory devices.13, 14, 15, 16, 17, 18, 19, 20 In addition, the majority of the aforementioned transistor memories that employed the polymer electret dielectric were limited to possess two-level memory characteristics.13, 14, 15, 16, 18 Advanced nonvolatile memory technology can have more than 1 bit in each of the cells by increasing the levels of the channel current.5, 17, 29, 30, 31 The multilevel memory cell is a demonstrated technology, and it has become attractive owing to the scaling limitations of lithography technology.5 The development of multilevel data storage is still in progress, especially in the use of organic-based memories,15, 29, 30 which can further enhance the memory capacity per unit cell area without reducing the cell size.

Star-shaped polymers consist of arms of macromolecule chain segments that are linked to a central core, and their electronic properties can be considerably different than their linear analogs owing to the close proximity of the arms within a single molecule. Here, we first employ the three-armed star-shaped poly[(4-diphenylamino)benzyl methacrylate] (star-PTPMA) as the polymer electret for multilevel data storage in transistor memories. The star-shaped polymer electret with pendent hole-transporting triphenylamine moieties could be charged and retain the digital states even when the supplied voltage was removed. For comparison, a linear-shaped PTPMA electret was also used; therefore, the effects of the architecture on the memory characteristics could be elucidated.

An n-channel organic semiconducting material, N,N'-bis(2-phenylethyl)perylene-3,4,9,10-bis(dicarboximide) (BPE-PTCDI), was employed as an active layer deposited on the top of the charge storage electret-modified SiO2/Si substrate for exploring the multilevel data accesses of nonvolatile write-many-read-many (WMRM) transistor memory devices. In addition, the p-channel semiconductor pentacene was also used for comparison to explore the charge-transporting mechanism, which revealed the significance of the polymer architecture effect on the electrets for nonvolatile organic transistor memory devices.

Materials and methods

Materials

Three-armed star-shaped star-PTPMA and linear-PTPMA were synthesized through group transfer polymerization, as previously reported by our group.32 BPE-PTCDI was purchased from the Luminescence Technology Corp. (Hsinchu, Taiwan) and used as received. All the commercially obtained reagents and anhydrous solvents were used without further purification.

Device fabrication and measurement

Devices were fabricated on highly doped n-type Si(100) wafers that had a 300-nm-thick SiO2 layer. Following a solvent cleaning procedure and drying under a stream of nitrogen, a solution of star-PTPMA (10 mg ml−1) in toluene was stirred overnight, filtered, spin-coated onto the wafer substrate at 1000 r.p.m. for 60 s and cured at 80 °C for 2 h under vacuum (10−6 torr). The semiconducting BPE-PTCDI was vacuum-deposited with a growth rate of 0.5 nm s−1 at 10−7 torr while the substrate temperature was maintained at 90 °C. A top-contact electrode (80 nm) was subsequently deposited by evaporating gold through a shadow mask with a channel length and width of 50 and 1000 μm, respectively.

All the measurements of the transistor memories were conducted using a Keithley 4200-SCS semiconductor parameter analyzer (Keithley Instruments Inc., Cleveland, OH, USA), with a Remote PreAmp (4200-PA) in a N2-filled glove box at room temperature. Triaxial cables were connected to the probe station to minimize the background noise. The capacitance of the bilayer dielectrics was measured using a Keithley 4200-SCS analyzer equipped with a 4210-CVU capacitance voltage measurement unit. The carrier mobility (μ) and threshold voltage (Vth) can be estimated from the slope and intercept of the linear plot of the square root of the drain-to-source current (Ids1/2) versus the gate voltage (Vg) using the following equation in the saturation regime:

where Ctot is the capacitance per unit area of the total dielectric layer and Vth is the threshold voltage.

Results and discussion

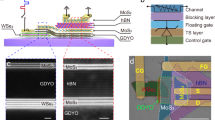

Figure 1 presents a schematic diagram of prototype BPE-PTCDI transistor memories based on a bottom-gate−top-contact configuration, in which star-PTPMA is used as the chargeable polymer electret. The film thicknesses of each layer were determined to be approximately 45 nm of star-PTPMA, 50 nm of BPE-PTCDI and 80 nm of Au source/drain electrode based on the cross-sectional scanning electron microscopy image (Supplementary Figure S1). The representative AFM micrograph of the SiO2/star-PTPMA bilayer film in Figure 1 reveals a smooth surface with a RMS roughness of 0.2–0.3 nm. This surface can promote the growth of the organic semiconductor, as shown in Figure 1. In addition, the hydrophobic characteristic of the star-PTPMA with a water contact angle of 93.2° (Supplementary Figure S2) ensures good wetting and the well-formed growth of BPE-PTCDI on the smooth electret surface.

A nanorod-like BPE-PTCDI thin film with a diameter of 60±8 nm was formed on the star-PTPMA surface (Supplementary Figure S3), and it had better molecular packing than that on the bare SiO2 surface with aggregated spheres (Supplementary Figure S4). Out-of-plane X-ray diffraction profiles of the BPE-PTCDI thin film deposited on the star-PTPMA with a lattice spacing of 1.5 nm exhibit stronger diffraction intensity and a narrower full width at half maximum than those on the bare SiO2 surface (Figure 1).33 This evidence supports the premise that an additional smooth star-PTPMA layer will improve the intermolecular transfer integral and the crystalline structures of the organic semiconductors, which could simultaneously reduce the silanol-type traps from the SiO2 interface.

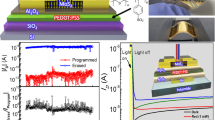

The electrical transfer and output characteristics of the investigated transistor memories are shown in Figure 2a and Supplementary Figure S5, respectively. All the measurements were conducted under dark conditions to prevent light-induced charge transfer34 or excitons.17 The transfer curves exhibit a typical n-type accumulation mode with a good current modulation, whereas the output curves exhibit well-defined linear and saturation regions. The same operational polarity was observed without any ambipolar behavior induced by the dielectric.35 The electron mobility was 0.02 cm2 V−1 s−1 with an ON/OFF current ratio of 105 and a threshold voltage of 8.5 V, which represents a significant effect on the star-PTPMA dielectric relative to 1.8 × 10-3 cm2 V−1 s−1 on the bare SiO2 wafer. This result is attributed to the highly crystalline structure of BPE-PTCDI on the top of the star-PTPMA surface.

The transistor memories are extended from the regular transistor and operated by a combination of applied appropriate gate pulses based on the shifts of the transfer curves, which caused different resistance modulations at a zero gate bias. Figure 2a presents the negative shift of the transfer curve (at a fixed drain voltage of 100 V) for the BPE-PTCDI-based transistor memory device prepared on the star-PTPMA electrets according to the negative gate voltage with a duration of 1 s. The programmed operation (−100 V) of the stored charges depletes the electrons from the transistor channel and consequently results in a substantial threshold voltage shift in the negative direction, which serves as a ‘writing’ process.

Intriguingly, an opposite polarity bias (gate bias of 100 V, 1 s) or power-off condition still maintains a similar trace. This device structure and its operation present essential functionalities for the characteristics of nonvolatile memory. In general, the transistor memories exhibit reversible cyclic transfer characteristics with an obvious hysteresis upon their dual sweeps because the trapped charges could be de-trapped or recombined by the charges injected from the organic semiconductors.13, 14, 15, 16, 17, 18, 19, 20 However, our BPE-PTCDI transistor memory device that contains a star-PTPMA electret exhibits an irreversible switching behavior that originates from the electron-donating nature of the pendent triphenylamine moieties and the coexisting energy level alignment at the interfaces. In addition, there are no obvious changes in the mobility and the ON/OFF current ratio of the transistor device, which implies that no additional traps are created in the interface except for the stored charges. The threshold voltage of the transistor with an additional star-PTPMA electret layer can be systematically controlled by applying the gate bias, even on a short time scale (approximately several ms).

Another important parameter, the memory window, increases the difference in the transfer curves between the initial scan and after applying a writing gate bias. The large memory window (∼36.5 V) suggests that a significant number of holes are trapped by the star-PTPMA electret layer. The memory ratio that describes the difference in current without the applied gate voltage is as high as 105, which leads to a low misreading rate of the memory device. It is possible to define the programmed state from the microscopic point of view as positive charges stored in the electret and a large reading current state. In contrast, the original OFF state is defined by neutral charges in the electret and a low reading current. Figure 2b presents the ability to retain data as a function of the retention time before (pristine) and after contact charging with a writing voltage, which was monitored by testing the same cell without applying the gate voltage. Notably, the current obtained in both the ON and OFF states are well separated without severe degradation for at least 1.5 × 105 s. The stored data are reliably maintained, and a distinguishable ON/OFF ratio is expected to be a promising feature for nonvolatile drives where information cannot be modified once written. These transistor memories are truly permanent after being charged with a high voltage.

The electrical transfer characteristics under various sweep ranges and electrical pulses were measured in an inert atmosphere at room temperature. Figure 3a illustrates the variations in the memory window at various gate voltage sweep ranges and a fixed drain voltage of 100 V. The transfer curves of the transistor memories were obtained by applying maximum gate voltages ranging from −20, −40, −60, −80 or −100 V to 100 V. As shown in this figure, the threshold voltage shifts towards a more negative position as the initial sweep gate voltage moves towards a more negative value. Figure 3b displays a unique transfer characteristic by the combination of electrical programmed voltages with the duration of each voltage pulse of 1 s. The investigated device exhibits an increasing negative shift of the curve with a more negative threshold voltage when the different negative gate voltages are programmed from −60 to −200 V (lines with open circles). Meanwhile, the device follows similar curves (lines with solid squares) after each programming action, which represents a reading procedure without any applied gate voltage pulse.

(a) Electrical transfer characteristics of devices with gate voltage scanned from various negative gate voltages to 100 V. (b) Electrical transfer characteristics of devices with the various programmed voltages (lines with solid squares) and the corresponding reading curves (lines with open circles). (c) The corresponding current levels at various applied gate voltage biases.

This result confirms that the data storage of the device may be maintained for a long time after applying a specific pulse and allows data to be recorded but not erased. This behavior would be called a WMRM storage as compared with the write-once-read-many nomenclature. The threshold voltage changes and the shifting of the transfer curve indicate that the negative pulse generates a certain number of charges in the dielectric. The negative direction of the threshold voltage shift in the n-channel transistor device indicates that the effective charges have a positive polarity. In addition, weak (or no) hysteresis is observed in these dual (forward and backward) scans (Supplementary Figure S6). This result suggests that the interface trapped charge (defects or impurities) can be excluded36 and possible electron injection or hole de-trapping effects on the characteristics of BPE-PTCDI-based transistor memories would not occur.

These transistor memories are nonvolatile, and they retain a given conductance state without any applied bias. Furthermore, a large memory ratio and controllable threshold voltage levels are critical factors for fulfilling the multilevel implementation. The multilevel transistor memories can be utilized to increase the memory capacity without decreasing the size of the device to the nanoscale. Figure 3c presents the multilevel data storage characteristics in the transistor memories using star-PTPMA as a polymer electret, and the device is reading under a small voltage of −20 V for 6 points within each voltage level. The current response as a function of time was plotted and varies after applying different writing biases. Therefore, six well-defined data levels are distinguishable with one OFF state (at a threshold voltage of 8.5 V) in conjunction with another five distinct intermediate and ON states (at threshold voltages of −9.3, −19.4, −29.4, −40.2 and −52.1 V, respectively) by different programmed voltages of −60, −100, −140, −180 and −200 V, respectively. Each state can be read separately to resemble six levels in a single device. In fact, the extent of storage can be clearly selected depending on the demand of the writing access.

The retention of performance on the BPE-PTCDI transistor memories was tested under four different states and estimated to be greater than 2 × 104 s (Supplementary Figure S7). Here, multilevel data storage is approached and the large sensing margin of our device is readily applicable for real memory devices without the use of a current amplifier. The multilevel conduction state may be due to various degrees of traps captured in the electret at different set biases.

The present results for transistor memories using an n-channel organic semiconductor fabricated on the SiO2/star-PTPMA dielectrics bilayer could provide the relationships between the semiconductor morphologies, dielectric surface characteristics and transistor performance parameters. The possible mechanism for clarifying the multilevel memory behaviors in the transistor device is elucidated as follows: The chemical structure and electronic properties of the star-PTPMA dielectric are directly related to the memory behaviors via interface energetics. The smooth morphology (low roughness) without nanoscopic pinholes from the star-PTPMA dielectric surface can significantly reduce the interface trap (for example, chemical defect). The molecular frontier orbital of the star-PTPMA dielectric derived from the cyclic voltammograms and the optical band gap are correlated with the carriers of the semiconductors. The HOMO and LUMO of the star-PTPMA are on the order of −5.48 and −1.84 eV,32 respectively, and the reported values for the HOMO and LUMO of BPE-PTCDI are −6.02 and −4.21 V,33 respectively (Supplementary Figure S8). Under a negative gate bias (writing process), a considerable number of positive charges are induced through the BPE-PTCDI from the source/drain electrode and subsequently trapped on the star-PTPMA electrets via a charge transfer process, as illustrated in Figure 4a. The high electric field at the dielectric results in the efficient transfer of holes from the BPE-PTCDI semiconductor to the polymer electret.

It is clear that the inserted star-PTPMA can promote charge injection or transport in the device. A significant amount of electrons form in the n-channel BPE-PTCDI and easily accumulate at the interface between BPE-PTCDI and the polymer electret, owing to an identical internal electric field that is induced from the trapped positive charges, even though the external gate voltages are removed. Therefore, the transfer curve shifts to the more negative bias direction compared with the initial state, which leads to a high-conductance ON state at the zero gate bias. This result indicates that the star-PTPMA electret acts as a hole-trapping site in the n-channel transistor memories. The stabilization of positive charge carriers could be due to the good hole-transporting ability of the pendant triphenylamine moieties. The charges remain even under the power-off condition owing to the tunneling barrier of the electret layer.

Also note that the LUMO level of the star-PTPMA is too high to act as an electron trap. The irreversible shifts can be explained by the large electron-injection barrier (2.37 eV; defined as the mismatch between the LUMOs of BPE-PTCDI and star-PTPMA). The transfer curves do not return to the initial position owing to the lack of recombination with the holes trapped in star-PTPMA from insufficient countercharge injection (Figure 4a). In addition, the trapped holes in the star-PTPMA polymer electret are not released even through the application of a reverse scan voltage, which suggests that there are no electrical hysteresis loops (Supplementary Figure S6).

Even in the light illumination-assisted program,17 the devices cannot reach the positive threshold voltage shift after a high-negative gate voltage bias. The amounts of the trapped holes stored in the star-PTPMA depend on the applied gate voltage bias. It was hypothesized that the threshold voltage could not shift back to a more positive direction (in other words, erasing action cannot be processed) owing to the absence of hole de-trapping or trapped opposite polarity charge carriers.2 All the contributions reasonably explain the nonvolatile WMRM memory behavior of our transistor memories.

To better interpret the charge injection/trapping mechanism, p-type pentacene-based transistor memories using star-PTPMA as chargeable polymer electrets were fabricated for comparison because they provided higher HOMO and LUMO levels than those of BPE-PTCDI associated with the interface alignments. As estimated from Supplementary Figure S9, the pentacene transistor exhibited a hole mobility of 0.27 cm2 V−1 s−1 with an ON/OFF ratio of 2.3 × 106 and an initial threshold voltage of −18 V. The threshold voltage and the amount of memory windows can be changed by applying a gate voltage bias or a subsequent sweep range. The pentacene-based transistor memories with star-PTPMA polymer electrets exhibit a memory hysteresis window of ca. 54 V at a drain voltage of −100 V with a gate voltage dual sweep range of 60 to −100 V, as shown in the transfer curves (black line with a solid square) of Supplementary Figure S9. The forward and backward transfer curves exhibit a similar trace relative to the initial ones after the first gate bias of 100 V (red line with solid circle). After applying a negative and positive gate bias for 1 s to program and erase the device, the dual sweep curves were shifted in the negative (blue line with solid triangle) and positive (green line with open circle) directions, respectively.

This hysteresis in the above schematic transfer characteristics can be interpreted as follows. The lower back sweep (anticlockwise) hysteresis and the negative shift of the threshold voltage under a negative gate bias in the p-type transistor indicate that a number of positive charges induced from the p-channel pentacene are trapped by the star-PTPMA electret. However, the electron injection to the star-PTPMA electret is not efficient, owing to the relatively high barrier from the LUMO energy level between pentacene and star-PTPMA (1.06 eV; see Supplementary Figure S8). This result indicates that electrons cannot be trapped in the electret layer and that the stored holes are compensated by countercharges (electrons). Note that the transfer curves can be shifted back to the initial ones (green line with open circle), which reveals an erasing operation and nonvolatile flash memory behavior from overall electrical characteristics. The reversible process verifies that the trapped holes can be released back to the channel through a reverse positive gate voltage because the HOMO level of pentacene is close to that of star-PTPMA. Trapping of opposite polarity charge carriers cannot act upon our transistor memories, which is perhaps due to the considerable difference in the LUMO energy levels or unipolar behavior of the organic semiconductor.2 On the basis of the results from the pentacene p-type semiconductors, we confirm that the memory capability primarily arises from the trapping of holes in the star-PTPMA electret and the charging mechanism in polymer electret based transistor memories.

For transistor memories based on organic polymers, the chargeable dielectric layer indeed has an important role and the threshold voltage shift may be related to the amounts of captured carriers. Note that the threshold voltage shift of 36.5 V was quite large after applying a gate bias of 100 V with a charge trapping density of 2.18 × 1012 cm−2 (see details in Supplementary Information). The carrier density in the reported transistor memory was in the range of 1011–5 × 1012 cm−2 with a threshold voltage of 14–35 V.14, 18, 20 In the case of ferroelectric polyvinylidene fluoride copolymer memory, it had a charge trapping density of 9.33 × 1011 cm−2.23 The nanoparticles/polymer hybrids used as floating gate nonvolatile flash memories exhibited carrier densities on the order of 1011–1012 cm−2 with hysteresis windows of 10–41 V.25, 26, 27 In our study, the transistor memories using star-PTPMA as an electret provided a reasonable charge trapping density (approximately 1012 cm−2) for competing with other memories based on organic transistors.

If the linear-PTPMA was used as the polymer electret, the device also exhibited the nonvolatile WMRM-type memory characteristics but with fewer well-defined data levels, as shown in Supplementary Figure S10. The charges could also be stored by applying a negative voltage bias (−100 V); however, in this case, only two or three well-defined data levels can be obtained, owing to the considerably smaller threshold voltage shift (17 V) compared with the star-PTPMA electret. This result reflects the importance of the shape architecture of the electret materials on the memory characteristics. Star-shaped polymers result in a more compact structure than linear polymers owing to the segment density.

The chain rigidity of star-PTPMA is restricted by the central nitrogen core, which forms a high triphenylamine trapping density. The star-PTPMA thin film related to linear-PTPMA exhibits stronger excimer emission (Supplementary Figure S11), which is attributed to the excimer formation of the aggregated triphenylamine moieties.32, 37 Such star-shaped pendent polymers with attached aromatic fluorescent probes may lead to strong molecular aggregation induced emission38, 39 and a well-packed triphenylamine conformation. Therefore, transistor memories based on the star-PTPMA electret have more trapped charges to produce an obvious threshold shift and contribute to more well-defined conductance levels for data storage. Furthermore, significant threshold voltage shifts as a function of the programmed gate bias were also observed (Figure 4b). A low critical gate voltage of −20 V starts to be programmed owing to the small difference of relative HOMO energy levels between BPE-PTCDI and PTPMA electret (0.54 V) for efficient charge transfer processes.

In regard to the relatively high operation voltage of the fabricated device, a solution to reduce the operation voltage is to enhance the gate dielectric capacitance and therefore, to employ a reduced thickness of SiO2 gate dielectric (approximately 100 nm) needed to achieve useful transistor currents when conventional gate insulators are utilized. The programmed voltages are reduced to −20, −40 or −60 V and a memory ratio of 102–104 can be obtained if the readout is performed with a gate voltage of ±10 V (Supplementary Figure S12). In addition, the transistor memory behavior of the output characteristics was similarly repeated at a programmed voltage of −50 V, as shown in Supplementary Figure S13, where the drain currents appear to be greater than those of initial curves. Although the memory windows become reduced to 9.5 V, the smaller thickness of the gate dielectric allows low programmed voltages to produce a researched multilevel nonvolatile WMRM memory behavior for application.

In conclusion, multilevel nonvolatile WMRM transistor memories with an additional charge trapping electret based on star-PTPMA have been presented. The large and irreversible negative threshold voltage shift in the transfer curves suggests that the electronic charges are transferred and permanently accumulate in the star-PTPMA gate electret owing to the restricting region of star-shaped polymers with well-defined charge trapping elements. Stable multilevel data storage is achieved through utilizing the appropriate programmed voltage pulse. This study reveals a promising future for key memory device elements, and this technology can be readily integrated into high-density, flexible, nonvolatile memory devices.

References

Guo, Y., Yu, G. & Liu, Y. Functional organic field-effect transistors. Adv. Mater. 22, 4427–4447 (2010).

Leong, W. L., Mathews, N., Tan, B., Vaidyanathan, S., Dotz, F. & Mhaisalkar, S. Towards printable organic thin film transistor based flash memory devices. J. Mater. Chem. 21, 5203–5214 (2011).

Ling, Q.-D., Liaw, D.-J., Zhu, C., Chan, D. S.-H., Kang, E.-T. & Neoh, K.-G. Polymer electronic memories: materials, devices and mechanisms. Prog. Polym. Sci. 33, 917–978 (2008).

Heremans, P., Gelinck, G. H., Muller, R. M., Baeg, K.-J., Kim, D.-Y. & Noh, Y.-Y. Polymer and organic nonvolatile memory devices. Chem. Mater. 23, 341–358 (2011).

Lee, S.-J. Progress in non-volatile memory devices based on nanostructured materials and nanofabrication. J. Mater. Chem. 21, 14097–14112 (2011).

Yang, Y., Ouyang, J., Ma, L., Tseng, R. J. H. & Chu, C. W. Electrical switching and bistability in organic/polymeric thin films and memory devices. Adv. Funct. Mater. 16, 1001–1014 (2006).

Liu, C.-L. & Chen, W.-C. Donor–acceptor polymers for advanced memory device applications. Polym. Chem. 2, 2169–2174 (2011).

Fang, Y.-K., Liu, C.-L., Li, C., Lin, C. J., Mezzenga, R. & Chen, W.-C. Synthesis, morphology, and properties of poly(3-hexylthiophene)-block-poly(vinylphenyl oxadiazole) donor–acceptor rod–coil block copolymers and their memory device applications. Adv. Funct. Mater. 20, 3012–3024 (2010).

Chen, J.-C., Liu, C.-L., Sun, Y.-S., Tung, S.-H. & Chen, W.-C. Tunable electrical memory characteristics by the morphology of self-assembled block copolymers:PCBM nanocomposite films. Soft Matter 8, 526–535 (2012).

Egginger, M., Bauer, S., Schwodiauer, R., Neugebauer, H. & Sariciftci, N. S. Current versus gate voltage hysteresis in organic field effect transistors. Monatsh. Chem. 140, 735–750 (2009).

Kang, N.-G., Cho, B., Kang, B.-G., Song, S., Lee, T. & Lee, J.-S. Structural and electrical characterization of a block copolymer-based unipolar nonvolatile memory device. Adv. Mater. 24, 385–390 (2012).

Hahm, S. G., Kang, N.-G., Kwon, W., Kim, K., Ko, Y.-K., Ahn, S., Kang, B.-G., Chang, T., Lee, J.-S. & Ree, M. Programmable bipolar and unipolar nonvolatile memory devices based on poly(2-(N-carbazolyl)ethyl methacrylate) end-capped with fullerene. Adv. Mater. 24, 1062–1066 (2012).

Katz, H. E., Hong, X. M., Dodabalapur, A. & Sarpreshkar, R. Organic field-effect transistors with polarizable gate insulators. J. Appl. Phys. 91, 1572–1576 (2002).

Baeg, K.-J., Noh, Y.-Y., Ghim, J., Kang, S.-J., Lee, H. & Kim, D.-Y. Organic non-volatile memory based on pentacene field-effect transistors using a polymeric gate electret. Adv. Mater. 18, 3179–3183 (2006).

Hung, C., West, J. M. & Katz, H. E. Organic field-effect transistors and unipolar logic gates on charged electrets from spin-on organosilsesquioxane resins. Adv. Funct. Mater. 17, 142–153 (2007).

Baeg, K.-J., Noh, Y.-Y., Ghim, J., Lim, B. & Kim, D.-Y. Polarity effects of polymer gate electrets on non-volatile organic field-effect transistor memory. Adv. Funct. Mater. 18, 3678–3685 (2008).

Guo, Y., Di, C.-A., Ye, S., Sun, X., Zheng, J., Wen, Y., Wu, W., Yu, G. & Liu, Y. Multibit storage of organic thin-film field-effect transistors. Adv. Mater. 21, 1954–1959 (2009).

Hsu, J.-C., Lee, W.-Y., Wu, H.-C., Sugiyama, K., Hirao, A. & Chen, W.-C. Nonvolatile memory based on pentacene organic field-effect transistors with polystyrene para-substituted oligofluorene pendent moieties as polymer electrets. J. Mater. Chem. 22, 5820–5827 (2012).

Chou, Y.-H., You, N.-H., Kurosawa, T., Lee, W.-Y., Higashihara, T., Ueda, M. & Chen, W.-C. Thiophene and selenophene donor-acceptor polyimides as polymer electrets for nonvolatile transistor memory devices. Macromolecules 45, 6946–6956 (2012).

Singh, Th. B., Marjanovic, N., Matt, G. J., Sariciftci, N. S., Schwodiauer, R. & Bauer, S. Nonvolatile organic field-effect transistor memory element with a polyemric gate electret. Appl. Phys. Lett. 85, 5409–5411 (2004).

Schroeder, R., Majewski, L. A. & Grell, M. All-organic permanent memory transistor using an amorphous, spin-cast ferroelectric-like gate insulator. Adv. Mater. 16, 633–636 (2004).

Naber, R. C. G., Tanase, C., Blom, P. W. M., Gelinck, G. H., Marsman, A. W., Touwslager, F. J., Setayesh, S. & Leeuw, D. M. de High-performance solution-processed polymer ferroelectric field-effect transistors. Nat. Mater. 4, 243–248 (2005).

Lim, S. H., Rastogi, A. C. & Desu, S. B. Electrical properties of metal-ferroelectric-insulator-semiconductor structures based on ferroelectric polyvinylidene fluoride copolymer film gate for nonvolatile random access memory application. J. Appl. Phys. 96, 5673–5682 (2004).

Sekitani, T., Yokota, T., Zschieschang, U., Klauk, H., Bauer, S., Takeuchi, K., Takamiya, M., Sakurai, T. & Someya, T. Organic nonvolatile memory transistors for flexible sensor arrays. Science 326, 1516–1518 (2009).

Leong, W. L., Mathews, N., Mhaisalkar, S., Lam, Y. M., Chen, T. & Lee, P. S. Micellar poly(styrene-b-4-vinylpyridine)-nanoparticle hybrid system for non-volatile organic transistor memory. J. Mater. Chem. 19, 7354–7361 (2009).

Baeg, K.-J., Noh, Y.-Y., Sirringhaus, H. & Kim, D.-Y. Controllable shifts in threshold voltage of top-gate polymer field-effect transistors for applications in organic nano floating gate memory. Adv. Funct. Mater. 20, 224–230 (2010).

Wei, Q., Lin, Y., Anderson, E. R., Briseno, A. L., Gido, S. P. & Watkins, J. J. Additive-driven assembly of block copolymer-nanoparticle hyrid materials for solution processable flaoting gate memory. ACS Nano 6, 1118–1194 (2012).

Burkhardt, M., Jedaa, A., Novak, M., Ebel, A., Voitchovsky, K., Stellacci, F., Hirsch, A. & Halik, M. Concept of a molecular charge storage dielectric layer for organic thin-film memory transistors. Adv. Mater. 22, 2525–2528 (2010).

Lee, J.-S., Kim, Y.-M., Kwon, J.-H., Sim, J. S., Shin, H., Sohn, B.-H. & Jia, Q. Multilevel data storage memory devices based on the controlled capacitive coupling of trapped electrons. Adv. Mater. 23, 2064–2068 (2011).

Li, H., Xu, Q., Li, N., Sun, R., Ge, J., Lu, J., Gu, H. & Yan, F. A small-molecule-based ternary data-storage device. J. Am. Chem. Soc. 132, 5542–5543 (2010).

Pellegrino, L., Manca, N., Kani, T., Tanaka, H., Biasotti, M., Bellingeri, E., Siri, A. S. & Marre, D. Multistate memory devices based on free-standing VO2/TiO2 microstructures driven by joule self-heating. Adv. Mater. 24, 2929–2934 (2012).

Hsu, J.-C., Chen, Y., Kakuchi, T. & Chen, W.-C. Synthesis of linear and star-shaped poly[4-(diphenylamino)benzyl methacrylate]s by group transfer polymerization and their electrical memory device applications. Macromolecules 44, 5168–5177 (2011).

Ling, M. M., Erk, P., Gomez, M., Koenemann, M., Locklin, J. & Bao, Z. Air-stable n-channel organic semiconductors based on perylene diimide derivatives without strong electron withdrawing groups. Adv. Mater. 19, 1127–1123 (2007).

Park, B., Paoprasert, P., In, I., Zwickey, J., Colavita, P. E., Hamers, R. J., Gopalan, P. & Evans, P. G. Functional self-assembled monolayers for optimized photoinduced charge transfer in organic field effect transistors. Adv. Mater. 19, 4353–4357 (2007).

Singh, T. B., Meghdadi, F., Gunes, S., Marjanovic, N., Horowitz, G., Lang, P., Bauer, S. & Sariciftci, N. S. High-performance ambipolar pentacene organic field-effect transistors on poly(vinyl alcohol) organic gate dielectric. Adv. Mater. 17, 2315–2320 (2005).

Goldman, C., Krellner, C., Pernstich, K. P., Hass, S., Gundlach, D. J. & Batlogg, B. Determination of the interface trap density of rubrene single-crystal field-effect transistors and comparison to the bulk trap density. J. Appl. Phys. 99, 034507 (2006).

Park, M. H., Huh, J. O., Do, Y. & Lee, M. H. Synthesis and properties of polyethylene with side-chain triphenylamines as hole-transporting materials. J. Polym. Sci. Polym. Chem. 46, 5816–5825 (2008).

You, J., Yoon, J. A., Kim, J., Huang, C.-F., Matyjaszewski, K. & Kim, E. Excimer emission from self-assembly of fluorescent diblock copolymer prepared by atom transfer radical polymerization. Chem. Mater. 22, 4426–4434 (2010).

Huang, Y., Lam, J. W. Y. & Tang, B. Z. Aggregation-induced emission. Chem. Soc. Rev. 40, 5361–5388 (2011).

Acknowledgements

The authors acknowledge the financial support from the National Science Council of Taiwan.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Competing interests

The authors declare no conflict of interest.

Additional information

Supplementary Information accompanies the paper on the NPG Asia Materials website

Supplementary information

Rights and permissions

This work is licensed under a Creative Commons Attribution-NonCommercial-NoDerivs 3.0 Unported License. To view a copy of this license, visit http://creativecommons.org/licenses/by-nc-nd/3.0/

About this article

Cite this article

Chiu, YC., Liu, CL., Lee, WY. et al. Multilevel nonvolatile transistor memories using a star-shaped poly((4-diphenylamino)benzyl methacrylate) gate electret. NPG Asia Mater 5, e35 (2013). https://doi.org/10.1038/am.2012.64

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1038/am.2012.64

Keywords

This article is cited by

-

Flexible non-volatile optical memory thin-film transistor device with over 256 distinct levels based on an organic bicomponent blend

Nature Nanotechnology (2016)

-

High-performance stretchable resistive memories using donor–acceptor block copolymers with fluorene rods and pendent isoindigo coils

NPG Asia Materials (2016)