Abstract

The fabrication of electronic circuits on unconventional substrates largely broadens their application areas. For example, green electronics achieved through utilization of biodegradable or recyclable substrates, can mitigate the solid waste problems that arise at the end of their lifespan. Here, we combine screen-printing, high precision laser drilling and thermal evaporation, to fabricate organic field effect transistor (OFET) active-matrix (AM) arrays onto standard printer paper. The devices show a mobility and on/off ratio as high as 0.56 cm2V−1s−1 and 109 respectively. Small electrode overlap gives rise to a cut-off frequency of 39 kHz, which supports that our AM array is suitable for novel practical applications. We demonstrate an 8 × 8 AM light emitting diode (LED) driver with programmable scanning and information display functions. The AM array structure has excellent potential for scaling up.

Similar content being viewed by others

Introduction

The development of new electronic devices has been made successful by integrating them onto unconventional substrates or objects, which enhances their functionalities and thus broadens their potential applications. For example, pressure and temperature sensors integrated with the clothing of athletes or medical patients, allow for real-time health monitoring and data recording1,2,3. For anti-counterfeiting and security purposes, flexible circuits and programmable non-volatile memory are deposited onto banknotes, enabling users to easily write, erase and read the stored information by applying different gate bias levels4,5,6,7,8. As these novel devices utilize the flexible or bendable properties of organic materials, they are relatively difficult to achieve using typical rigid inorganic semiconductors. Among the different electronic components, the transistor, one of the cornerstones of the modern electronics industry, plays a crucial role in the further development of the flexible electronics. In particular, the ability of fabricating high performance flexible transistors on unconventional substrates, will enable innovative applications9,10,11. However, conventional microfabrication approaches such as spin coating or thermal evaporation may not be suitable for high roughness substrates. As a result, there is an imminent need to develop alternative microfabrication methods that can be applied suitably on rough substrates and can scale up for large-area applications. Moreover, it is also important to investigate the growth mechanisms of organic semiconductors on rough surfaces, in order to achieve performance that is comparable to devices on smooth substrates.

Although some organic field effect transistors (OFETs) have shown comparable mobility with amorphous silicon transistors, they are usually limited to substrates with smooth surfaces such as silicon, glass and plastic films. To reduce leakage current and enhance field effect mobility, different approaches such as the substrate buffering process8,11,12, self-assembled monolayers5,13,14,15,16,17,18,19,20 and charge injection layers17,21,22,23 have been developed to fabricate high performance OFETs on these conventional substrates. However, these approaches are usually designed for specific bulk substrate or thin-film dielectric materials with smooth surfaces, making them unsuitable for substrates with a high roughness of several micrometers (μm). Previously, in pentacene OFETs, it has been found that the carrier mobility decreases significantly from 0.31 cm2V−1s−1 to 0.02 cm2V−1s−1 when the silicon dioxide dielectric surface roughness increases from 0.2 nm to 1.5 nm24,25. A similar effect has also been reported in polymer dielectric devices where the pentacene grain size is largely influenced by the roughness variation induced by dielectric polymer chain movement25,26. In fact, aside from dielectric surfaces, the substrate itself can also cause the roughness effect. This is especially true for unconventional substrate materials where the substrates dominates the overall roughness. The rough surface will interrupt the lateral diffusion of the deposited organic molecules, resulting in the poor stacking of molecules and a smaller grain size, thus leading to lower carrier mobility27.

When selecting the substrates for flexible OFETs, polymeric materials are usually used due to their mechanical flexibility, ductility and no lattice matching requirements1,2,12,15,28,29,30,31. When compared with commonly used flexible substrates such as poly(ethylene naphthalate) (PEN) or poly(ethylene terephthalate) (PET), paper substrates based on cellulose fiber are widely used in our daily life. They also have a number of advantages including a promising low cost, foldablility and biodegradable properties. These unique assets open up new research directions for fabricating electronic devices on paper directly and thus enable the further development of novel paper-based electronics applications. Devices like digital micro-fluidic chips32,33,34, solar cells35,36,37, batteries38 and memory transistors8,39 have been previously demonstrated. Nevertheless, the major drawback of paper substrates is the surface morphology. In typical commercial-grade printer paper made from plant fibers with diameters larger than 10 μm, the surface roughness can be up to a few micrometers (around 1,000 to 10,000 times larger than that of Si/SiO2). As a result, obtaining high performance OFETs, let alone more complicated organic circuits, could be very challenging on such a rough surface.

Here we combine screen-printing, high resolution via-hole laser drilling and thermal evaporation to fabricate an OFET active-matrix (AM) array (8 × 8) onto standard 80 g m−2 printer paper (Fuji-Xerox) without any substrate pretreatment. A statistical study of the transistor array shows uniform performance across the substrate and that device-to-device variation is insignificant. The maximum mobility and on/off ratio of the devices are 0.56 cm2V−1s−1 and 109, respectively. By measuring the variation of the source-drain current under different gate bias frequency conditions, we evaluated the average cut-off frequency of the current OFETs on paper substrate to be around 39 kHz. This suggests that simple portable circuits are ready to be developed on paper substrates using the process. The 8 × 8 transistor array is further applied as an active-matrix LED driver by integrating with white color LEDs for point scanning, line scanning and direct image display on the printer paper. Further, the presented fabrication method is suitable for scaling up to large-area devices and mass production. Our findings also shed light on new research areas of biodegradable green electronics that would have extremely low cost. The conventional printer paper can be electrically functionalized for advanced applications such as smart chips, bio-sensors, or anti-counterfeiting devices.

Results

Large-area screen-printed electrodes

To address the substrate roughness effects, we employed a screen-printing method to deposit the bottom silver (Ag) gate electrodes (Fig. 1a). The specially designed paste contains a silver nanoparticles (diameter ~300 nm) content of ~85% in carrier solvent, resulting a high viscosity of 200 Pa·s (Toyo Ink Asia, Supplementary Fig. S1a). Such a high viscosity helps prevent the paste from spreading or being absorbed into the cellulose fiber. It is also worth noting that the paste used in the current work does not require a post-deposition sintering process and was used directly after simply drying it in an ambient air environment for 2 hours. To print the desired silver electrode patterns, a stainless steel mesh (wire diameter 18 μm) is first selectively covered by an emulsion, which fills the mesh in unused regions to create the desired gate electrode patterns. Both optical and scanning electron microscopy (SEM) images of a mesh are shown in Fig. 1a. The silver paste and different mesh patterns are then used to screen-print the source/drain electrodes and electrical interconnects using a homemade screen-printer. By optimizing both the screen printer settings and the mesh parameters, the printed electrodes can define a highly repeatable 60 μm channel length with nine source/drain fingers on each device. From the SEM images of the paper substrate (Fig. 1c) and subsequent screen-printed silver electrodes (Fig. 1f), a single layer of screen-printed silver (~6 μm thick, Fig. 1e) is observed to significantly planarize the paper substrate and reduce the surface roughness from several micrometers down to around 150 nm (Fig. 1b). The electrical conductivity of the single layer screen-printed silver electrode on the paper substrate is measured to be 104 S cm−1, which is comparable to other commonly used metal or indium tin oxide (ITO) electrodes. Such a large conductivity on high roughness surface is difficult to achieve by conventional thermal evaporation or magnetron sputtering of a metal thin film. Furthermore, the screen-printed gate electrode can eliminate the need for thick underlying dielectric buffer layers such as PDMS and Cytop on the paper surface8,11. Next, the screen-printed silver gate electrode layer is coated with a parylene-C dielectric layer via chemical vapor deposition (CVD) to a thickness of 2-μm-thick (areal capacitance Ci ≈ 1.4 nF cm−2, Supplementary Fig. S2). This process further reduces the surface roughness to 50 nm (Fig. 1b and Supplementary Fig. S3) and renders it ready for semiconductor deposition.

Transistor structures on printer paper.

(a) Schematic process of the screen-printing approach. Top middle inset shows an optical image of the enlarged source/drain pattern, where the light blue part is covered by emulsion. Top right inset is an SEM image of channel area defined between two fingers. (b) Surface roughness (root mean square) after different fabrication processes. (c) SEM surface image of the paper substrate. (d) Schematic cross sectional structure of the transistor. (e) SEM cross sectional image of the transistor under the drain electrode area. (f) SEM surface image of the screen-printed gate electrode on paper.

Semiconductor performance on a rough dielectric surface

Here we employ two different small molecular organic semiconductors, dinaphtho[2,3-b:2',3'-f] thieno[3,2-b] thiophene (DNTT) and pentacene, deposited by thermal evaporation as the device active layer and compare their performance on the paper substrate. Control samples are fabricated on ITO coated glass substrates for comparison. The schematic cross sectional structure of a single transistor device is shown in Fig. 1d. The channel width (W) and length (L) of all these single devices are 4 mm and 100 μm, respectively. In order to provide a fair comparison, a constant parylene-C layer thickness (2 μm) was used for all devices including the control samples and the semiconductor active layers on both substrates are deposited together. The 2 μm thick parylene-C deposited onto ITO glass and screen-printed silver on printer paper had a resulting root-mean-square roughness (Rq) of 5 nm and 50 nm respectively (Supplementary Fig. S3). The device performance of all four device structures (2 substrates, 2 semiconductors) is summarized in Table 1. The DNTT and pentacene on ITO glass/parylene-C (Structures I and II) show average mobilities of 0.36 cm2V−1s−1 and 0.074 cm2V−1s−1. While equivalent devices on a paper substrate (Structure III and IV), exhibited carrier mobilities which decreased to 0.33 cm2V−1s−1 and 0.038 cm2V−1s−1, respectively. These findings suggest that the DNTT semiconductor has a higher tolerance towards substrate roughness than pentacene. From the atomic force microscope (AFM) imagery of the 50 nm thick DNTT and pentacene thin films deposited on ITO glass/parylene-C, shown in Fig. 2a and 2b, it can be observed that the pentacene grain size is smaller and more grain boundaries are apparent, while the DNTT thin film exhibits a stronger layer stacking structure with fewer grain boundaries. The large roughness of the underlying screen-printed silver nanoparticles on the paper substrate makes measuring the exact surface morphology of the organic active layer difficult (Fig. 2c and 2d). To characterize the active layer growth for the first few monolayers, we performed AFM measurements on the first 5 nm of both DNTT and pentacene (Fig. 2e and 2f). From the insets of Fig. 2e and 2f, it can be clearly noted that the first 5 nm of DNTT prefers to form taller island structures rather than covering a larger area of parylene-C. On the other hand, no significant individual islands are observed for the first few monolayers of pentacene and they tend to cover a larger area of parylene-C dielectric (Frank-van der Merwe mode)40. It is believed that the observed distinct behavior of DNTT and pentacene on the high-roughness substrate is correlated to different growth modes of the organic semiconductors. Our findings provide direct evidence that although the surface roughness is commonly believed to be one of the key limiting factors on the performance of OFETs, it can still be counterbalanced by the growth mode of the organic semiconductor materials.

AFM investigation on semiconductors growth on different surfaces.

(a–d) AFM images of semiconductor surface morphology (50-nm-thick) of structures I, II, III and IV of Table 1. AFM images of the semiconductor surface morphology of 5-nm-thick (e) DNTT and (f) pentacene grown on a parylene-C surface on screen-printed Ag electrodes and paper substrate. Scale bar is 500 nm. Inset of (e) and (f) are the height profiles of the sample grains (white dotted lines).

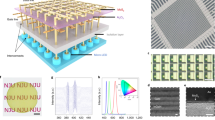

Active-matrix transistor array on paper

Based on these highly reproducible OFETs, we further develop a more complex active-matrix OFET array onto the paper substrate (see Supplementary Fig. S4 for the schematic fabrication steps). The active-matrix (AM) transistor array is widely used as the driver in displays41,42,43,44,45 and is dominated by silicon-based technology. Unlike discrete devices, where each transistor has its own three terminals (source, drain and gate), an AM array uses the crossing points of orthogonal row and column electrodes to locate each pixel, resulting in far fewer control electrodes. This configuration greatly reduces the space occupied by electrode lines to allow a much higher device density. However, the performance requirement for each transistor in the AM array is also higher, as one short or open circuited transistor may result in the breakdown of an entire row or column of the array. The challenge of realizing an AM array with a large device density, good large-area uniformity and a high yield rate is further heightened when fabricating on high-roughness paper substrates. Here we realize an 8 × 8 AM OFET array with a pixel size of 3 mm × 3 mm corresponding to a resolution of 8.4 dots per inch (DPI). The completed array on a printer paper substrate, with laser pre-printed information, is shown in Fig. 3a. Unlike the single device geometry, the gate lines of the array are placed on the backside of the paper substrate to eliminate an extra crossing between electrodes to help suppress the leakage current. The backside gate lines are connected to the gate electrodes through two via-holes drilled through the substrate via a CO2 laser. The through-paper via-holes are filled with Ag paste using the doctor blading technique and a laser-cut mask. Setting the via-hole diameter to 60 μm results in a 100% yield of electrical connections between the gate lines and gate electrodes (see Methods for experimental details). Fig. 3b shows the transfer curves of all 64 OFETs in a single 8 × 8 array. It should be noted that all the transistors exhibit uniform transfer characteristics, on/off ratios larger than 107 and leakage currents lower than 100 pA. The mobility, threshold voltage and on/off ratio of the 64 devices are plotted as colormaps in Fig. 3c, 3d and 3e. The average mobility, threshold voltage and on/off ratio are 0.45 cm2V−1s−1, −4.7 V and 1.5 × 108, respectively. The standard deviations of the mobility and the threshold voltage are as small as 0.05 cm2V−1s−1 and 1.5 V. The slight mobility increase from the discrete transistor (Table 1) to the AM array structure (from 0.33 cm2V−1s−1 to 0.45 cm2V−1s−1) is attributed to the decrease of channel length from 100 μm to 60 μm, resulting in a decrease of the total grain boundary effects that dominate the overall mobility. It is also worth mentioning that the measured threshold voltages have a higher magnitude for the transistors with gate electrodes at the array edge. As the currents in the on state of edge devices are similar to other devices located elsewhere, the measured mobilities of these devices at the edge are relatively higher.

Uniformity test of 8 × 8 active matrix (AM) transistor array.

(a) AM transistor array on printer paper with pre-printed information. (b) 64 transfer curves of one AM array automatically acquired using LabVIEW™. (c–e) Mobility, threshold voltage (VTH) and on/off ratio (log value) colormaps of the 64 transistors in the AM. Mobility mean value is 0.45 cm2V−1s−1 with a standard deviation of 0.05 cm2V−1s−1; VTH mean value is −4.7 V with a standard deviation of 1.5 V; On/off ratio has a mean value of 1.5 × 108 and standard deviation of 3.7 × 108.

LED integration to AM array

To further demonstrate the application potential of the current OFET AM array on paper, we integrate light emitting diodes (LEDs) onto the individual source contacts of the array and use the array as the driver for a graphical display. A cross sectional schematic diagram of a single array pixel is shown in Fig. 4a and optical image of the fabricated array is shown in Fig. 4c. It should be noted from Fig. 4a that on top of the AM array we deposit an additional parylene-C layer to prevent the overlap between drain lines and source lines at their intersection (red dotted box in the inset of Fig. 4c). After deposition of the top parylene-C layer, an additional laser drilling process is applied to create two via-holes to expose source electrodes through the parylene-C and allow screen-printing of the source lines directly. Contact pads for the discrete LEDs are co-fabricated with source lines in a single printing step and are followed by LED mounting. From the inset of Fig. 4c detailing a single array pixel, the 60 μm channel gap can be clearly observed between the source and the drain electrodes. The 60 μm channel length with nine source/drain fingers can provide sufficient current for the LEDs and, at the same time, maintain the high device yield rate. The terminations of the source, drain and gate lines are designed to mate with commercial flexible flat cables (FFCs) for a direct plug-in connection. Three multiplexers are connected to the gate, source and drain lines respectively to control array via device bias. These bias signals from the sourcemeters and the three multiplexers, are synchronized by a custom LabVIEW™ (National Instruments) program on a control computer as shown in the driving circuit diagram in Fig. 4b. In order to visualize individual device currents and demonstrate the array capabilities, we control the switching methods of the different multiplexers to achieve both single point scanning (Fig. 4d) and line scanning (Fig. 4e). Figure 4f further demonstrates the image display application of the paper-based AM LED array by using the programmable scanning process and to pattern and clearly display the letters “HKU.”

OFET AM driver scanning and information display.

(a) Schematic of OFET AM driver. (b) Array driving circuit, red lines correspond to digital signals and black lines to analog signals. (c) Optical image of OFET AM LED driver, standard connector interfaces to FFCs (flat flexible cables) are formed by screen-printing. Inset is an enlarged single pixel of the array, where the red dotted box indicates the insulation layer (2nd parylene-C) between drain (vertical) and source (horizontal) electrodes. VGS = −40 V and VDS = −15 V are used to operate the OFET AM LED driver. Different operating conditions of the driver are shown. (d) Single scan, one by one operation of each pixel. (e) Line scan, row by row operation of pixels. (f) Image display using programmed fast scanning to display “HKU” in capital letters.

Cut-off frequency

The short channel length and little overlap between the source/drain and gate electrodes can enable a high operating frequency of the realized AM array17. A high operating frequency of the transistor array structure is extremely important for large-scale applications where a large number of devices are interconnected. To test the cut-off frequency of the fabricated structures, we measured the peak-to-peak source/drain current (IDS, peak-peak) and gate current (IGS, peak-peak) variations induced by a modulated gate bias under different frequencies. The cut-off frequency is defined as the operating frequency when IDS, peak-peak equals, IGS, peak-peak. The measured values of the IDS, pk-pk and IGS, pk-pk of a typical device under different frequencies are shown in Fig. 5a and the cut-off frequency can be obtained through a linear fitting of the log-log plot. The average cut-off frequency is of all 64 devices in an 8 × 8 array is around 39 kHz. This value compares favorably to a value of 41.3 kHz calculated using transistor parameters in the equation below:17

where L is the channel length and ΔL is the overlapping length between the gate and source/drain electrodes which induce parasitic capacitance. A cut-off frequency colormap of all transistors in an array is shown in Fig. 5b, where the lowest frequency and highest frequency are ca. 30 kHz and 50 kHz, respectively. It suggests the number of devices in the array can be higher than the current demonstration of 64 devices.

Discussion

In summary, we developed a methodology combining screen-printing, laser drilling and thermal evaporation to fabricate OFET active-matrix arrays on standard printer paper without pre-treatment. All electrode patterning is performed by a high-resolution screen-printing method with a fast speed and high potential for large-area production. Fine patterning of the electrodes allow for a remarkable channel length (60 μm) on the standard printer paper with an extremely high yield rate. Although rough surfaces are generally believed to be unsuitable for organic electronics, especially small molecule semiconductors, the realized DNTT OFETs on printer paper show comparable performance to those on conventional flat substrates. An 8 × 8 active-matrix array with 8.4 DPI resolution is successfully demonstrated and employed as an AM LED driver. Fully programmable scanning and information display functionality of the OFET AM LED array demonstrated the great potential of realizing new functionalities to standard printer paper. The presented technique can also be applied to memory, sensor and/or photovoltaic fabrication onto paper substrates, which can greatly broaden the application areas of paper-based green electronics.

Methods

AM array fabrication

The fabrication process started using 99.99% nitrogen to blow the surfaces of the paper substrate to dislodge particulates. Through-substrate via-holes were created with a CO2 laser system (Universal, VLS 2.30) with 1.8% power, 1% speed and 1000 DPI. Due to the flammability of paper, no thermal expansion and local surface roughness changes were caused at laser focal points. The via-hole diameter was fixed to be around 60 μm with sharp well-defined edges. Relatively low viscosity Ag paste (diluted paste, Supplementary Fig. S1b) was filled into the via-holes to serve as the electrical conductor. The backside gate bus lines were then formed by screen-printing on a homemade printing stage. The optimized distance between the screen frame and substrate was set to be 0.9 mm. The printing speed was controlled to lower than 10 cm/s to ensure well-defined metal patterns. For all printing processes, if not specified, the printer paper was held by a vacuum suction stage to guarantee a uniformly printed pattern. Gate electrodes were next formed by screen-printing on the top side of the via-holes. The thickness of a single layer screen-printed electrode was 6 μm. Parylene-C was adopted as the gate dielectric layer because of its large-area capability, uniformity and cost-efficiency. In order to ensure a uniform coating over all the gate electrodes and prevent leakage, the parylene-C layer thickness was set to be 2 μm at a deposition pressure of 25 mTorr (PDS 2010, SCS). After gate dielectric formation, 50-nm-thick DNTT or pentacene film was deposited by thermal evaporation at a base pressure lower than 1 × 10−6 Torr (Moorfield). Silver source and drain electrodes were also printed by the screen-printing process. The entire AM array was then held in a glove box for 2 hours to allow all solvents to dry. This corresponds to steps 1–6 of Supplementary Fig. S4.

OFET AM LED driver fabrication

After AM array fabrication, 5-μm-thick parylene-C layer was then deposited to act as the cross point insulator. To expose the source electrodes underneath the second parylene-C layer, another CO2 laser drilling process was performed (0.3% power, 1% speed). Contact pads for the discrete micro-LEDs and the source bus lines were screen-printed together. For the final fabrication step, 64 micro-LEDs were mounted manually under an optical microscope. The completed OFET AM LED array was then plugged into a standard flexible flat cable (FFC) interface (1 mm pitch) to connect it to the electrical testing system. This corresponds to steps 7–9 of Supplementary Fig. S4.

Measurements

Transfer curves were obtained by a Keithley 2636B dual-channel source-meter under darkness in a glove box (water and oxygen content lower than 1 ppm). Cut-off frequency data was measured using a signal generator (Agilent 33210A), voltage amplifier (Thorlabs HVA200) and lock-in amplifier (Stanford SR 850). AC voltage signals were generated by the signal generator and linearly amplified. This amplified AC signal was then used as the gate-source voltage (Supplementary Fig. S6). A constant DC drain-source voltage of −80 V was applied to ensure transistor operation in the saturation regime. Peak to peak values of the drain-source and gate-source currents were acquired using a resistor (12 kΩ) combined with the lock-in amplifier.

The OFET AM driver was demonstrated by applying a VGS = −40 V and VDS = −15 V. A custom LabVIEW™ (National Instruments) program was employed to control the AM drivers by selectively opening or closing specific channels through a Keithley 7011 multiplexer. For point scanning, row scanning and information display, each step of the device scanning was pre-defined in the LabVIEW™ program to complete an entire image frame. Each from was then frame looped and changed over multiple refresh cycles to display the desired scanning functions. The electromechanical switching mechanism of the multiplexer limited the frame refresh rate of information display mode to 3 Hz. However, from the cut-off frequency measurements, the AM driver is capable of frame refresh rates of several hundred Hertz.

AFM characterization was completed via a Bruker Multimode 8 scanning probe microscope and SEM imaging was performed with a Hitachi S-4800 field emission scanning electron microscope. XRD measurements made use of a Rigaku SmartLab X-ray Diffractometer. An Agilent 4294A Precision Impedance Analyzer was utilized for capacitance measurements.

References

Ramuz, M., Tee, B. C. K., Tok, J. B. H. & Bao, Z. N. Transparent, Optical, Pressure-Sensitive Artificial Skin for Large-Area Stretchable Electronics. Adv. Mater. 24, 3223–3227 (2012).

Schwartz, G. et al. Flexible polymer transistors with high pressure sensitivity for application in electronic skin and health monitoring. Nat. Commun. 4, 1859 (2013).

Mannsfeld, S. C. B. et al. Highly sensitive flexible pressure sensors with microstructured rubber dielectric layers. Nat. Mater. 9, 859–864 (2010).

Naber, R. C. G., Asadi, K., Blom, P. W. M., de Leeuw, D. M. & de Boer, B. Organic Nonvolatile Memory Devices Based on Ferroelectricity. Adv. Mater. 22, 933–945 (2010).

Zschieschang, U. et al. Organic Electronics on Banknotes. Adv. Mater. 23, 654–658 (2011).

Eder, F. et al. Organic electronics on paper. Appl. Phys. Lett. 84, 2673–2675 (2004).

Martins, R. et al. Selective floating gate non-volatile paper memory transistor. Phys Status Solidi-R 3, 308–310 (2009).

Khan, M. A., Bhansali, U. S. & Alshareef, H. N. High-Performance Non-Volatile Organic Ferroelectric Memory on Banknotes. Adv. Mater. 24, 2165–2170 (2012).

Martins, R. et al. Complementary Metal Oxide Semiconductor Technology With and On Paper. Adv. Mater. 23, 4491–4496 (2011).

Tobjork, D. & Osterbacka, R. Paper Electronics. Adv. Mater. 23, 1935–1961 (2011).

Li, Y. et al. Solution-processed organic crystals for field-effect transistor arrays with smooth semiconductor/dielectric interface on paper substrates. Org. Electron. 13, 815–819 (2012).

Sekitani, T., Zschieschang, U., Klauk, H. & Someya, T. Flexible organic transistors and circuits with extreme bending stability. Nat. Mater. 9, 1015–1022 (2010).

Zschieschang, U. et al. Flexible low-voltage organic thin-film transistors and circuits based on C-10-DNTT. J. Mater. Chem. 22, 4273–4277 (2012).

Yokota, T. et al. Sheet-Type Flexible Organic Active Matrix Amplifier System Using Pseudo-CMOS Circuits With Floating-Gate Structure. IEEE Trans. Electron. Devices 59, 3434–3441 (2012).

Kuribara, K. et al. Organic transistors with high thermal stability for medical applications. Nat. Commun. 3, 723 (2012).

Kaltenbrunner, M. et al. Ultrathin and lightweight organic solar cells with high flexibility. Nat. Commun. 3, 770 (2012).

Ante, F. et al. Contact Resistance and Megahertz Operation of Aggressively Scaled Organic Transistors. Small 8, 73–79 (2012).

Sekitani, T. & Someya, T. Stretchable organic integrated circuits for large-area electronic skin surfaces. MRS Bull. 37, 236–245 (2012).

Yokota, T. et al. Low-voltage organic transistor with subfemtoliter inkjet source-drain contacts. Mrs Communications 1, 3–6 (2011).

Sekitani, T. & Someya, T. Human-friendly organic integrated circuits. Mater. Today 14, 398–407 (2011).

Alam, M. W., Wang, Z. K., Naka, S. & Okada, H. Mobility enhancement of top contact pentacene based organic thin film transistor with bi-layer GeO/Au electrodes. Appl. Phys. Lett. 102 (2013).

Dell'Erba, G. et al. Organic integrated circuits for information storage based on ambipolar polymers and charge injection engineering. Appl. Phys. Lett. 104, 153303 (2014).

Abdur, R., Jeong, K., Lee, M. J. & Lee, J. High performance of pentacene organic thin film transistors by doping of iodine on source/drain regions. Org. Electron. 14, 1142–1148 (2013).

Steudel, S. et al. Influence of the dielectric roughness on the performance of pentacene transistors. Appl. Phys. Lett. 85, 4400 (2004).

Kim, C., Facchetti, A. & Marks, T. J. Polymer gate dielectric surface viscoelasticity modulates pentacene transistor performance. Science 318, 76–80 (2007).

Fritz, S. E., Kelley, T. W. & Frisbie, C. D. Effect of dielectric roughness on performance of pentacene TFTs and restoration of performance with a polymeric smoothing layer. J. Phys. Chem. B 109, 10574–10577 (2005).

Yang, H. C. et al. Conducting AFM and 2D GIXD studies on pentacene thin films. J Am Chem Soc 127, 11542–11543 (2005).

Cosseddu, P., Lai, S., Barbaro, M. & Bonfiglio, A. Ultra-low voltage, organic thin film transistors fabricated on plastic substrates by a highly reproducible process. Appl. Phys. Lett. 100, 093305 (2012).

Graz, I. M. & Lacour, S. P. Flexible pentacene organic thin film transistor circuits fabricated directly onto elastic silicone membranes. Appl. Phys. Lett. 95, 243305 (2009).

Jedaa, A. & Halik, M. Toward strain resistant flexible organic thin film transistors. Appl. Phys. Lett. 95, 103309 (2009).

Klauk, H., Zschieschang, U., Pflaum, J. & Halik, M. Ultralow-power organic complementary circuits. Nature 445, 745–748 (2007).

Ko, H. et al. Active digital microfluidic paper chips with inkjet-printed patterned electrodes. Adv. Mater. 26, 2335–2340 (2014).

Abadian, A. & Jafarabadi-Ashtiani, S. Paper-based digital microfluidics. Microfluid & Nanofluid 16, 989–995 (2014).

Fobel, R., Kirby, A. E., Ng, A. H., Farnood, R. R. & Wheeler, A. R. Paper microfluidics goes digital. Adv. Mater. 26, 2838–2843 (2014).

Fan, K., Peng, T. Y., Chen, J. N., Zhang, X. H. & Li, R. J. Low-cost, quasi-solid-state and TCO-free highly bendable dye-sensitized cells on paper substrate. J. Mater. Chem. 22, 16121–16126 (2012).

Hubler, A. et al. Printed Paper Photovoltaic Cells. Adv. Energy Mater. 1, 1018–1022 (2011).

Barr, M. C. et al. Direct Monolithic Integration of Organic Photovoltaic Circuits on Unmodified Paper. Adv. Mater. 23, 3500–3505 (2011).

Hilder, M., Winther-Jensen, B. & Clark, N. B. Paper-based, printed zinc-air battery. J Power Sources 194, 1135–1141 (2009).

Peng, B. Y. & Chan, P. K. L. Flexible organic transistors on standard printing paper and memory properties induced by floated gate electrode. Org. Electron. 15, 203–210 (2014).

Kwak, S. Y., Choi, C. G. & Bae, B. S. Effect of Surface Energy on Pentacene Growth and Characteristics of Organic Thin-Film Transistors. Electrochem. Solid St. 12, G37–G39 (2009).

Chida, A. et al. Flexible high-resolution full-color top-emitting active-matrix organic light-emitting diode display. J. Soc. Inf. Display 21, 422–432 (2013).

Fujisaki, Y. et al. Flexible Active-Matrix Organic Light-Emitting Diode Display Using Air-Stable Organic Semiconductor of Dinaphtho[2, 3-b: 2 ', 3 '-f]thieno[3, 2-b]-thiophene. IEEE Trans. Electron. Devices 59, 3442–3449 (2012).

Sekitani, T. et al. Stretchable active-matrix organic light-emitting diode display using printable elastic conductors. Nat. Mater. 8, 494–499 (2009).

Park, S. H. K. et al. Transparent and Photo-stable ZnO Thin-film Transistors to Drive an Active Matrix Organic-Light-Emitting-Diode Display Panel. Adv. Mater. 21, 678–682 (2009).

Zhou, L. S. et al. All-organic active matrix flexible display. Appl. Phys. Lett. 88, 083502 (2006).

Acknowledgements

The work is supported by the General Research Funding Scheme of the Research Grant Council of Hong Kong (HKU 710313E) and the Seed Funding Scheme of The University of Hong Kong (201210159031 and 201209160033). The authors thank the Electron Microscope Unit (EMU) of The University of Hong Kong for the use of their scanning electron microscopy tools.

Author information

Authors and Affiliations

Contributions

P.K.L.C conceptualized the work. B.P. carried out most of the experimental work including device fabrication and characterization. P.K.L.C and B.P. wrote the manuscript. X.R. offered ideas and helped in electrical circuit design. Z.W. carried out capacitance measurements and SEM. X.W. helped with thermal evaporation of the materials. R. C. R. offered ideas and helped in editing the manuscript. All authors discussed the results and commented on the manuscript.

Ethics declarations

Competing interests

The authors declare no competing financial interests.

Electronic supplementary material

Supplementary Information

Supplementary information

Rights and permissions

This work is licensed under a Creative Commons Attribution-NonCommercial-NoDerivs 4.0 International License. The images or other third party material in this article are included in the article's Creative Commons license, unless indicated otherwise in the credit line; if the material is not included under the Creative Commons license, users will need to obtain permission from the license holder in order to reproduce the material. To view a copy of this license, visit http://creativecommons.org/licenses/by-nc-nd/4.0/

About this article

Cite this article

Peng, B., Ren, X., Wang, Z. et al. High performance organic transistor active-matrix driver developed on paper substrate. Sci Rep 4, 6430 (2014). https://doi.org/10.1038/srep06430

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/srep06430

This article is cited by

-

Vertically Integrated Electronics: New Opportunities from Emerging Materials and Devices

Nano-Micro Letters (2022)

-

Fabrication of screen-printed electrodes: opportunities and challenges

Journal of Materials Science (2021)

-

Printable, Highly Sensitive Flexible Temperature Sensors for Human Body Temperature Monitoring: A Review

Nanoscale Research Letters (2020)

-

Study of enhancement in the dielectric and electrical properties of WO3-doped LiF nano-composite

Journal of Materials Science (2018)

-

Charge-integrating organic heterojunction phototransistors for wide-dynamic-range image sensors

Nature Photonics (2017)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.