Abstract

Complementary electronics has represented the corner stone of the digital era, and silicon technology has enabled this accomplishment. At the dawn of the flexible and wearable electronics age, the seek for new materials enabling the integration of complementary metal-oxide semiconductor (CMOS) technology on flexible substrates, finds in low-dimensional materials (either 1D or 2D) extraordinary candidates. Here, we show that the main building blocks for digital electronics can be obtained by exploiting 2D materials like molybdenum disulfide, hexagonal boron nitride and 1D materials such as carbon nanotubes through the inkjet-printing technique. In particular, we show that the proposed approach enables the fabrication of logic gates and a basic sequential network on a flexible substrate such as paper, with a performance already comparable with mainstream organic technology.

Similar content being viewed by others

Introduction

Complementary metal-oxide semiconductor (CMOS) is the most widespread technology for the design and production of electronic circuits. Since the beginning of the 1970s, this technology has been employed for both digital and analogue design and has been the driving force of the digital revolution1,2. CMOS technology uses complementary n-type and p-type field-effect transistors (FETs) and presents several advantages with respect to the unipolar counterpart, i.e., the low power dissipation, the full output logic swing, and the large noise immunity2.

Within the new scenario of ubiquitous, flexible, and wearable electronics, CMOS still represents the technology at choice for the development of the Internet of Things1 as well as smart packaging, human-health monitoring, cyber-physical systems etc.3 However, in order to fully exploit its advantages and potential applications, it has to be declined and adapted to the new requirements in terms of physical flexibility and stretchability of the circuits3,4,5,6. This translates into finding suitable materials for both the devices and the substrates. Towards this direction, CMOS logic gates and circuits based on organic semiconductors like P3HT, TIPS-pentacene, N1100 etc., have been fabricated on flexible substrates, with reduced power consumption, and mobility in the range from 0.1 to ~5 cm2/Vs7,8,9,10. High mobility and low power supply are key performance indicators of the quality of technology, especially for portable applications. Despite the fact that organic electronics has certainly reached a high level of maturity, it is uncertain how much this technology can be pushed to further improve in terms of stability, and electrical behavior. Low-dimensional materials, including 1D carbon nanotubes (CNTs)11 and 2D materials (2DMs)12 such as transition metal dichalcogenides (TMDs)13 have entered the research scenario only recently, but have already demonstrated a huge potential in this context. Thanks to their outstanding mechanical and electrical properties, comparable to long-term studied organic materials, they represent one of the most promising classes of materials for the next generations of wearable and flexible electronics applications14,15,16,17,18,19. CNTs have been previously employed to develop CMOS inverters on flexible substrate showing interesting performance20,21. For example, Xiao et al.22 recently reported a CNTs-based high-gain inverter fabricated on polyethylene terephthalate by means of aerosol printing, but with poor performance in terms of noise immunity and power consumption. Several attempts to obtain 2DM-based CMOS inverters have been demonstrated on rigid substrates23,24, while remarkable results have not yet been obtained so far on flexible substrates25,26,27.

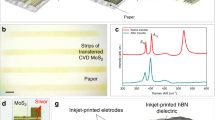

Here, we demonstrate a flexible CMOS technology on paper, combining n-type MoS2-based FETs and p-type CNTs-based FETs. We have chosen paper as a substrate to fulfil the need for environmentally friendly and recyclable substrates, necessary for the sustainable development of ubiquitous electronics. Indeed, from this point of view, thanks to its low cost, intrinsic flexibility, and full recyclability, paper represents an extremely promising substrate28. Despite these indisputable advantages, this substrate is still challenging for the fabrication of electronic devices, mainly because its large roughness, high hygroscopicity, and low thermal resistance28. Its use thus poses additional fabrication constraints, even compared to other flexible substrates such as plastics, and therefore compatible fabrication techniques must be adopted. To overcome the current lack of high-performing inkjet-printed 2D semiconductors, i.e., with mobility higher than 1 cm2/Vs, we have opted for a CVD-grown MoS2 channel, patterned in strips and then transferred on paper in a “channel array” configuration29. CVD growth allows for large-area fabrication and is compatible with the employed substrate. The rest of the device, as well as the whole p-type FET, is entirely inkjet-printed, using 2D hBN as a gate dielectric. Inkjet printing has been chosen as the main fabrication technique because it is a cost-effective, mask-less process, which offers advantages in terms of versatility, resolution, and material wastage. These features, combined with the possibility of working at room temperature, make this technique ideal for the fabrication of devices on paper. Thanks to the high capacitance per unit area of the printed insulating films used in the FET gate stack, both types of FETs work with low supply voltage (≤ 3 V), and are therefore suitable to be integrated into low-voltage circuits. This is a fundamental requirement for portable electronic systems, where the supply voltage can be provided using solar cells30, near-field radio-frequency coupling31, or thin-film batteries32,33, and can enable the design of low power circuits. To demonstrate the potential of the proposed approach, we have designed, fabricated, and characterized CMOS circuits on paper, such as inverters, NOR gates, and a D-Latch, which are some of the main building blocks needed to develop complex, low-power integrated electronics on paper.

Results and discussion

Fabrication and characterization of CNTs and MoS2 FETs

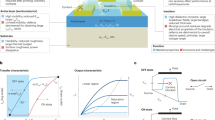

The transistors are fabricated in a top-gate/top-contact configuration, as shown in Fig. 1a, where a CMOS inverter with a n-type MoS2-based FET and p-type CNTs-based FET are illustrated.

a Sketch showing a CMOS inverter made of an inkjet-printed CNTs p-type FET and an inkjet-printed MoS2 n-type FET. Inset, optical micrograph of both types of FET fabricated on paper, the scale bars correspond to 500 µm. b Output characteristics of p-type FET, obtained decreasing VGSp from +3 to −3 V with a step of 0.5 V (blue curves), and output characteristics of n-type FET, obtained increasing VGSn from −3 to +3 V with a step of 0.5 (red curves). c Transfer characteristics of a CNTs FET (blue curve) and a MoS2 FET (red curve) measured as a function of the gate voltage for a drain voltage of −2.0 and 2.0 V, respectively, in semi-logarithmic scale. d Transfer characteristic curves of a CNTs FET (blue curve) and a MoS2 FET (red curve) measured as a function of the gate voltage for a drain voltage of −2.0 and 2.0 V, respectively in linear scale.

The p-type FET is inkjet-printed on paper exploiting a CNTs ink purchased from NanoIntegris (see “Methods” and Supplementary Notes3); then, the source and drain electrodes are printed on top, using a nanoparticle-based silver ink (purchased from Sigma Aldrich, see “Methods”). A hexagonal boron nitride (hBN) film is then inkjet-printed on the channel as the gate insulator. The ink synthesis and characterization, previously developed in34, have been reported in Supplementary Notes1. Finally, the top-gate is printed on top of the dielectric, employing the same silver ink used for the source and drain electrodes. Two different channel lengths Lp have been considered, i.e., Lp = 40 µm and Lp = 350 µm, with a fixed channel width of Wp = 500 µm. It should be noted that, for all the fabricated FETs, Lp is larger than the length of an individual CNT (which is in the range 0.3–5 µm). Therefore, transport in the channel occurs through a percolative CNTs network and can be influenced by the CNT-CNT interface35. The channel has been printed with a single layer, which is found to be enough to ensure percolation of the CNTs network. This allows to minimize the density of the printed CNTs, and, thus, to increase the FET ION/IOFF current ratio, as demonstrated in previous papers36,37.

The top-gate/top-contacts n-type FETs are obtained by printing the source and drain silver electrodes over a CVD-grown MoS2 stripe transferred on paper (see Supplementary Notes2). After that, the same water-based hBN ink employed for the p-type FETs is printed as the dielectric; finally, a silver gate is printed on top of the channel/dielectric stack. The detailed fabrication method and the complete electrical characterization of the n-type FETs are reported in29. The channel length (Ln) and width (Wn) of the n-type transistor are 40 and 500 µm, respectively.

Mirror symmetric electrical characteristics with respect to the reference voltage (i.e., ground) for the two types of devices is a key requirement for a high-performance complementary technology38,39. Indeed, in a complementary-based logic circuit, the p-type FETs must act as a pull-up network (which provides the high logic level), while the n-type FETs as a pull-down network (which provides the low logic level): in this context, large current mismatch between the two types of FETs lead to asymmetrical behavior, which can be due to the mismatch of several parameters. The channel current for a FET in saturation regime can be generalized using the following formula40:

which is valid for both p-type (x = p) and n-type (x = n) FETs. IDSx, µx, CG, VGSx, and VTHx are the channel current, the field-effect mobility, the gate dielectric capacitance per unit area, the gate voltage, and the threshold voltage, respectively. Since in both cases the hBN dielectric is printed using the same process, it can be assumed that CG is the same for both the n- and p-type FETs. Therefore, from Eq. 1, the IDSx mismatches can arise from three parameters: µx, VTHx, and Wx/Lx. Exploiting the flexibility of the inkjet-printing technique, which allows the individual control of the lateral device’s dimensions down to ~20 µm41, we have used the channel length (Lp and Ln) as a design degree of freedom to obtain better-matched CMOS characteristics, while keeping the channel width constant (Wp = Wn = 500 µm). In the inset of Fig. 1a, we show the optical micrograph of a representative p-type (blue box) and n-type (red box) FET with Lp = 350 and Ln= 40 µm respectively. The output characteristics, i.e., IDS as a function of the drain voltage VDS, of the p-type FET are obtained decreasing VGSp from +3 to −3 V, while the output characteristic of the n-type FET is obtained increasing VGSn from −3 to +3 V (Fig. 1b). The two devices exhibit similar characteristics, with comparable saturation currents for sufficiently high |VGSx|. In addition, the curves have a linear behavior for low VDS, indicating good ohmic contacts between the inkjet-printed silver and both the CNTs and the MoS2 channels.

Figure 1c, d shows the transfer characteristics (in linear and semi-logarithmic scale) of both devices measured for VDSp = −2.0 V and VDSn = 2.0 V. The threshold voltages (VTHx) are similar for both devices (|VTHx| ≈ 0). Considering the same |VTH|, from Eq. 1, it can be observed that the Lp/Ln ratio allows to compensate the mismatch between µp and µn.

The µx has been calculated for both transistors using the formula in the saturation regime40:

We extracted an average µp ≈ 25 cm2 V−1 s−1 for the CNTs FET and µn ≈ 3 cm2 V−1 s−1 for the MoS2 FET. The achieved µp is in line with42,43 or even better44,45 as compared to the previously reported mobility for CNTs FETs on flexible substrates.

The versatility of the exploited fabrication technology allows us to integrate several FETs in a flexible, cost-effective way, onto the same paper substrate. In the following, we propose some digital circuits to demonstrate the potential of the technology. All circuits are designed to work with a voltage supply VDD ≤ 3 V.

Flexible complementary inverter on paper

Inverters represent the fundamental building blocks of digital electronics. Figure 2a shows the schematic and the optical image of a complementary inverter printed on paper, while integrating both a CNTs and a MoS2 FET. In Fig. 2a, VIN is the input voltage, VOUT is the output voltage, VDD is the supply voltage (VDD = 2), and GND is the ground of the circuit. The voltage transfer characteristic (VTC), i.e., VOUT as a function of VIN, is shown in Fig. 2b (black line). The VTC shows almost an ideal behavior for the output logic levels: a high logic level (high VOUT, obtained for low VIN values) equal to VDD, and a low logic level (low VOUT, obtained for high VIN values) almost 0 V. These characteristics allow to achieve low static power consumtion. Overall, the inverter demonstrates a good rail-to-rail output voltage swing of 98.25% VDD and a logic threshold voltage (VM, i.e., the VIN value at which the switching occurs VIN = VOUT) of 0.9, close to the ideal value VDD/2. The voltage gain, defined as G = dVOUT/dVIN, is reported in the inset of Fig. 2b, and it is calculated to be ~8. The obtained G behavior is of primary importance for an inverter, since it guarantees the regeneration of logic levels: all signals VIN < VM (VIN > VM), can be properly regenerated through a chain of inverters in order to obtain a good logic value ‘1’ (‘0’).

a Electrical schematic and optical image of a complementary inverter made of a CNTs FET and a MoS2 FET. b Voltage transfer characteristic (VTC, black line), and noise margin (red line) of the flexible complementary inverter for VDD = 2 V. Inset, the voltage gain of the same CMOS inverter. c Power consumption of the complementary inverter for VDD = 2.0 V.

These performances open up the possibility to design circuits with multiple stages, in which each stage is able to drive the subsequent ones38 (as we will show later on, in the case of the D-LATCH).

Two of the most important parameters to enable a robust design of large-scale integrated circuits are the low and high Noise Margins (NMlow and NMhigh, respectively), which quantifies the immunity of the logic circuit against noise. The overall Noise Margin of the circuit (NM) is equal to the minimum between NMlow and NMhigh, which are defined as46:

where VILmax is the maximum input voltage that can be considered as logic ‘0’ and VOLmax is the maximum output voltage that can be considered as logic ‘0’, and

where VOHmin is the minimum output voltage can be considered as ‘1’ logic and VIHmin is the minimum input voltage that can be considered as ‘1’ logic.

Ideally, the two noise margins should both be equal to VDD/2. In our case, NMlow is 47% VDD/2, while NMhigh is 85% VDD/2, as shown in Fig. 2b. Therefore, the flexible printed inverter fabricated on paper is immune to noise level up to ~0.47 V. The obtained NM value ensures a good tolerance of the circuit against noise, and is in line10,47 or even better22,27 as compared to those previously reported for inverters fabricated on a flexible substrate.

Figure 2c shows the power consumption of the inverter, calculated as PS = VDD·IS, (where IS the current that flows between the supply rails), as a function of VIN. As expected, the maximum power is dissipated during the switching, while it is minimum at the steady state. The figure of merit that takes into account the average static power consumption (PSa) is defined as:

where ISCH and ISCL are the currents flowing between the supply rails, when the output voltage is high and low, respectively. The inverter in Fig. 2 is characterized by a PSa of 29 nW, which is comparable with those previously reported for low-power consumption circuits20,47,48, or even lower21,22. As can be seen from Fig. 2c, PSa is increased by the power dissipated at the low logic state (PSaL = ISCL · VDD/2), while the one dissipated at the high logic state (PSaH = ISCH ⋅ VDD/2) is about one order of magnitude lower. This may be due to slight asymmetry in transistor behavior, and in particular to the higher IOFF of the p-type FET, probably a consequence of residual metallic CNTs49,50,51.

A comparison between the properties of the proposed inverter on paper and the state of art of the complementary inverters based on low-dimensional and organic materials is reported in Supplementary Table 1.

Characteristics of other inverters fabricated on paper using the same approach are reported in Supplementary Fig. 4.

Flexible complementary NOR on paper

To further demonstrate the potential of the proposed complementary technology, we developed a NOR gate on paper. This is a universal logic gate, that allows the design of any Boolean function without the need for other logic gates52.

Figure 3a, b shows the digital symbol and the schematic of a NOR, respectively. The steady output voltage, VOUT, is reported in Fig. 3c as a function of the combination of the input signals, IN1 and IN2, which can only assume the logic value ‘1’ (corresponding to 3 V), or the logic value ‘0’ (corresponding to 0 V). The measured output voltage follows the expected Boolean function, with logic levels close to the ideal ones. Indeed, the output voltage swing is, in the worst case (i.e., considering the worst ‘0’, for IN1 = 1, IN2 = 0), 2.8 V. This value approaches the ideal rail-to-rail voltage swing (3 V). The dynamic response of the NOR gate is reported in Supplementary Figs. 5 and 6.

Flexible hybrid complementary-PTL D-Latch on paper

An interesting technological solution is represented by the hybrid CMOS and Pass Transistor Logic (PTL), which allows the reduction of circuit complexity53,54. In PTL, the input signal is allowed or inhibited depending on the level of a control signal, which drives the transistor gate.

We exploit this hybrid approach to develop a D latch, which is an important building block of sequential logic units, since it can be used as a memory element in the finite state machines. A latch, characterized by two stable states, is a circuit able to store or retain a bit of information depending on the control signal. As a proof of concept, a printed hybrid complementary-PTL D-Latch on paper has been designed and fabricated. Figure 4a shows the digital symbol of a D-Latch and its truth table, while Fig. 4b depicts its electrical schematic. Two CNTs FETs were chosen as pass transistors because they present better performance with respect to the n-type FETs (see Supplementary Fig. 7). The implemented circuit uses only six transistors, a smaller number with respect to those required to obtain the same function with a static conventional CMOS circuit38. Fig. 4c shows the time evolution of the output signal, Q, and the inverse output signal, \(\bar Q\), as a function of the input signal voltage, D, and the clock CLK, which controls the switching ON/OFF of the pass transistors. It should be noticed that the output Q follows the input D only when CLK is in the logic state ‘0’, whilst the output Q keeps the value of the input D when CLK is in the logic state ‘1’. As evident from the figure, sources of non-idealities as intrinsic defects (most likely in the printed dielectric), are limiting the switching performance of the system, which deserves further investigation, though out of the scope of the current work. A complete characterization of the circuit, including the time evolution of Q as a function of the other combinations of D and CLK, is reported in Supplementary Fig. 8.

a Symbol of the complementary-PTL D-Latch, and its truth table. b Schematic of the complementary-PTL D-Latch. c Time evolution of the output, Q, and the inverse output, \(\bar Q\), as a function of the input signal, D, and clock, CLK. The blue zones show the hold phases of the Latch, while the dash-dot lines highlight the output voltage changes.

In summary, we have demonstrated an inkjet-printed, complementary technology on paper based on p-type CNTs and n-type MoS2 FETs. We have designed, fabricated, and characterized CMOS inverters with a gain of up to 8, noise margin of about 50%, a full rail-to-rail output swing, and a static power consumption of about 30 nW. Starting from this fundamental building block, we have developed more complex circuits such as CMOS NOR gates and a PTL CMOS D-Latch. The obtained results demonstrate that this technology could lead to the implementation of a new generation of low-cost, complementary electronics on paper.

Methods

Materials

PEL P60 (purchased from Printed Electronics Limited) is used as paper a substrate. A commercial nanoparticle silver ink (purchased from Sigma-Aldrich) is used to print the metallic contacts. The single-walled CNTs ink is diluted from IsoSol-S100 commercial ink (99.9%, purchased from NanoIntegris) using toluene (final concentration ~0.053 mg mL−1). More details are available in Supplementary Table 2, Supplementary Fig. 3, and Supplementary Notes3. Bulk boron nitride (purchased from Sigma-Aldrich, >1 μm, 98% grade) powders were used to prepare the hBN ink. A complete description of the preparation and characterization of the employed custom-made hBN ink is available in Supplementary Notes1 and Supplementary Fig. 1. CVD MoS2 was grown on sapphire, patterned in stripes, and transferred on paper. Details on growth, pattern and transfer are provided in Supplementary Notes2 and Supplementary Fig. 2.

Devices fabrication

The n-type transistor is fabricated in a top-gate/top-contact configuration using the MoS2 stripes as active channels. A Fujifilm Dimatix Materials Printer 2850 is used to define the contacts and the insulator layers under ambient conditions. No annealing or post-treatment process is performed after any printing step. The silver ink is deposited with a single printing pass using one nozzle, a drop spacing of 20 μm, and keeping the printer platen at room temperature. A cartridge with a typical droplet volume of 1 pL is used for the definition of the contacts (source, drain, and gate). A 2 mg mL−1 hBN ink is printed on top using a drop spacing of 20 μm and 100 printing passes. A cartridge with a droplet volume of 10 pL is used for the definition of the insulating layer.29

The p-type transistor is fabricated in a top-gate/top-contact configuration using the semiconducting single-walled CNTs ink. The same printer used for the fabrication of the n-type transistor is employed to define the contacts, the channel, and the insulator layers under ambient conditions. Also in this case, no annealing or post-treatment process is performed after any printing step. The CNTs is deposited with a single printing pass using one nozzle, a drop spacing of 20 μm, and keeping the printer platen at room temperature. Contacts and insulating layers are printed using the same parameter employed for the fabrication of the n-type transistor.

Data availability

The data that support the findings of this work are available from the corresponding author upon reasonable request.

References

Hussain, A. M. & Hussain, M. M. CMOS-technology-enabled flexible and stretchable electronics for internet of everything applications. Adv. Mater. 28, 4219–4249 (2016).

Chung, S. & Lee, T. Towards flexible CMOS circuits. Nat. Nanotechnol. 15, 11–12 (2020).

Huang, S., Liu, Y., Zhao, Y., Ren, Z. & Guo, C. F. Flexible electronics: stretchable electrodes and their future. Adv. Funct. Mater. 29, 1805924 (2019).

Gupta, S., Navaraj, W. T., Lorenzelli, L. & Dahiya, R. Ultra-thin chips for high-performanceflexible electronics. npj Flex. Electron. 2, 8 (2018).

Park, H. et al. Investigation of electrical characteristics of flexible CMOS devices fabricated with thickness-controlled spalling process. Solid. State Electron. 173, 107901 (2020).

Lin, Z., Huang, Y. & Duan, X. Van der Waals thin-film electronics. Nat. Electron. 2, 378–388 (2019).

Klauk, H., Zschieschang, U., Pflaum, J. & Halik, M. Ultralow-power organic complementary circuits. Nature 445, 745–748 (2007).

Kraft, U. et al. Flexible low-voltage organic complementary circuits: Finding the optimum combination of semiconductors and monolayer gate dielectrics. Adv. Mater. 27, 207–214 (2015).

Cho, K. G. et al. Sub-2 V, transfer-stamped organic/inorganic complementary inverters based on electrolyte-gated transistors. ACS Appl. Mater. Interfaces 10, 40672–40680 (2018).

Casula, G. et al. Printed, low‐voltage, all‐organic transistors and complementary circuits on paper substrate. Adv. Electron. Mater. 6, 1901027 (2020).

Toan, D. et al. Environment-friendly carbon nanotube based flexible electronics for noninvasive and wearable healthcare. J. Mater. Chem. C 4, 10061–10068 (2016).

Gao, L. Flexible device applications of 2D semiconductors. Small 13, 1603994 (2017).

Chen, H., Cao, Y., Zhang, J. & Zhou, C. Large-scale complementary macroelectronics using hybrid integration of carbon nanotubes and IGZO thin-film transistors. Nat. Commun. 5, 4097 (2014).

Kelly, A. G. et al. All-printed thin-film transistors from networks of liquid-exfoliated nanosheets. Science 356, 69–73 (2017).

Akinwande, D., Petrone, N. & Hone, J. Two-dimensional flexible nanoelectronics. Nat. Commun. 5, 5678 (2014).

Robinson, J. A. Perspective: 2D for beyond CMOS. APL Mater. 6, 058202 (2018).

Kim, Y. D. & Hone, J. Screen printing of 2D semiconductors. Nature 544, 167–168 (2017).

Wang, C., Takei, K., Takahashi, T. & Javey, A. Carbon nanotube electronics – moving forward. Chem. Soc. Rev. 42, 2592–2609 (2013).

Schneider, D. S. et al. Highly responsive flexible photodetectors based on MOVPE grown uniform few-layer MoS2. ACS Photonics 7, 1388–1395 (2020).

Honda, W., Arie, T., Akita, S. & Takei, K. Mechanically flexible and high-performance CMOS logic circuits. Sci. Rep. 5, 15099 (2015).

Zhang, X. et al. Flexible CMOS-like circuits based on printed P-type and N-type carbon nanotube thin-film transistors. Small 12, 5066–5073 (2016).

Xiao, H. et al. Polarity tuning of carbon nanotube transistors by chemical doping for printed flexible complementary metal-oxide semiconductor (CMOS)-like inverters. Carbon N. Y. 147, 566–573 (2019).

Jeon, P. J. et al. Low power consumption complementary inverters with n-MoS2 and p-WSe2 dichalcogenide nanosheets on glass for logic and light-emitting diode circuits. ACS Appl. Mater. Interfaces 7, 22333–22340 (2015).

Wan, D. et al. High voltage gain WSe2 complementary compact inverter with buried gate for local doping. IEEE Electron Device Lett. 41, 944–947 (2020).

Das, T. et al. Highly flexible hybrid CMOS inverter based on Si nanomembrane and molybdenum disulfide. Small 12, 5720–5727 (2016).

Zhang, X. et al. Substitutional fluorine doping of large-area molybdenum disulfide monolayer films for flexible inverter device arrays. ACS Appl. Mater. Interfaces 12, 5720–5727 (2020).

Liu, Y. & Ang, K. W. Monolithically integrated flexible black phosphorus complementary inverter circuits. ACS Nano 11, 7416–7423 (2017).

Zhang, Y. et al. Flexible electronics based on micro/nanostructured paper. Adv. Mater. 30, 1801588 (2018).

Conti, S. et al. Low-voltage 2D materials-based printed field-effect transistors for integrated digital and analog electronics on paper. Nat. Commun. 11, 3566 (2020).

Elumalai, N. K. & Uddin, A. Open circuit voltage of organic solar cells: an in-depth review. Energy Environ. Sci. 9, 391–410 (2016).

Chasin, A. et al. An integrated a-IGZO UHF energy harvester for passive RFID tags. IEEE Trans. Electron Devices 61, 3289–3295 (2014).

Moitzheim, S., Put, B. & Vereecken, P. M. Advances in 3D thin-film Li-ion batteries. Adv. Mater. Interfaces 6, 1–17 (2019).

Chen, J. et al. Narrowband internet of things: implementations and applications. IEEE Internet Things J. 4, 2309–2314 (2017).

Worsley, R. et al. All-2D material inkjet-printed capacitors: toward fully printed integrated circuits. ACS Nano 13, 56–60 (2019).

Tang, J. et al. Flexible CMOS integrated circuits based on carbon nanotubes with sub-10 ns stage delays. Nat. Electron. 1, 191–196 (2018).

Snow, E. S., Novak, J. P., Campbell, P. M. & Park, D. Random networks of carbon nanotubes as an electronic material. Appl. Phys. Lett. 82, 2145–2147 (2003).

Tanaka, T. & Sano, E. Low-frequency noise in carbon nanotube network thin-film transistors. Jpn. J. Appl. Phys. 53, 090302 (2014).

Rabaey, J. M., Chandrakasan, A. & Nikolic, B. Digital Integrated Circuits: A Design Perspective. (Prentice Hall Electronics and VLSI Series, Upper Saddle River, NJ, 2003).

Myny, K. The development of flexible integrated circuits based on thin-film transistors. Nat. Electron. 1, 30–39 (2018).

Sze, S. M. & Ng, K. K. Physics of Semiconductor Devices. (John Wiley & Sons, Inc., Hoboken, NJ, 2007).

Lessing, J. et al. Inkjet printing of conductive inks with high lateral resolution on omniphobic ‘rF paper’ for paper-based electronics and MEMS. Adv. Mater. 26, 4677–4682 (2014).

Lu, S. et al. Flexible, print-in-place 1D–2D thin-film transistors using aerosol jet printing. ACS Nano 13, 11263–11272 (2019).

Lau, P. H. et al. Fully printed, high performance carbon nanotube thin-film transistors on flexible substrates. Nano Lett. 13, 3864–3869 (2013).

Cao, X. et al. Fully screen-printed, large-area, and flexible active-matrix electrochromic displays using carbon nanotube thin-film transistors. ACS Nano 10, 9816–9822 (2016).

Cai, L., Zhang, S., Miao, J., Yu, Z. & Wang, C. Fully printed stretchable thin-film transistors and integrated logic circuits. ACS Nano 10, 11459–11468 (2016).

Zschieschang, U. et al. Mixed self-assembled monolayer gate dielectrics for continuous threshold voltage control in organic transistors and circuits. Adv. Mater. 22, 4489–4493 (2010).

Honda, W. et al. High-performance, mechanically flexible, and vertically integrated 3D carbon nanotube and InGaZnO complementary circuits with a temperature sensor. Adv. Mater. 27, 4674–4680 (2015).

Huang, T. C. et al. Pseudo-CMOS: a design style for low-cost and robust flexible electronics. IEEE Trans. Electron Devices 58, 141–150 (2011).

Kocabas, C. et al. Experimental and theoretical studies of transport through large scale, partially aligned arrays of single-walled carbon nanotubes in thin film type transistors. Nano Lett. 7, 1195–1202 (2007).

Ha, M. et al. Printed, sub-3V digital circuits on plastic from aqueous carbon nanotube inks. ACS Nano 4, 4388–4395 (2010).

Schießl, S. P. et al. Polymer-sorted semiconducting carbon nanotube networks for high-performance ambipolar field-effect transistors. ACS Appl. Mater. Interfaces 7, 682–689 (2015).

Zhou, J., Arugula, M. A., Halámek, J., Pita, M. & Katz, E. Enzyme-based NAND and NOR logic gates with modular design. J. Phys. Chem. B 113, 16065–16070 (2009).

Zimmermann, R. & Fichtner, W. Low-power logic styles: CMOS versus pass-transistor logic. IEEE J. Solid-State Circuits 32, 1079–1090 (1997).

Ding, L. et al. CMOS-based carbon nanotube pass-transistor logic integrated circuits. Nat. Commun. 3, 677 (2012).

Acknowledgements

The authors acknowledge the ERC PEP2D (Contract No. 770047), H2020 WASP (Contract No. 50 825213), the Graphene Flagship Core3 (Contract No. 881603), and the project Origenal (Contract No. 863258).

Author information

Authors and Affiliations

Contributions

I.B., L.P., and S.C. designed and fabricated the electronic devices, performed the electrical measurements, analyzed the results, and wrote the original draft under the supervision of G.F.; R.W. and S.M. developed the inks under the supervision of C.C.; D.K.P. and M.P. carried out the MoS2 growth and transfer under the supervision of T.M; E.D and G.P. contributed to the characterization of the materials; G.F, G.I., F.P., and M.M. supervised the research. All authors discussed the results.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Brunetti, I., Pimpolari, L., Conti, S. et al. Inkjet-printed low-dimensional materials-based complementary electronic circuits on paper. npj 2D Mater Appl 5, 85 (2021). https://doi.org/10.1038/s41699-021-00266-5

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41699-021-00266-5

This article is cited by

-

Synthesis of nanoSiO2/graphene oxide nanocomposite as a novel engine oil additive for reducing friction and wear

Journal of Materials Science (2024)

-

Printed transistors made of 2D material-based inks

Nature Reviews Materials (2023)