Abstract

Tin halide perovskites have the general chemical formula ASnX3, where A is a monovalent cation and X is a monovalent halide anion. These semiconducting materials can be used to fabricate p-type transistors at low cost and temperature and could be potentially integrated with n-type oxide-based transistors to create complementary circuits. However, the materials suffer from low crystallization controllability and high film defect density, resulting in uncompetitive device performance. Here we show that pure-tin perovskite thin-film transistors can be created using triple A cations of caesium–formamidinium–phenethylammonium. The approach leads to high-quality cascaded tin perovskite channel films with low-defect, phase-pure perovskite/dielectric interfaces. The optimized thin-film transistors exhibit hole mobilities of over 70 cm2 V−1 s−1 and on/off current ratios of over 108, which are comparable with commercial low-temperature polysilicon transistors. The transistors are fabricated using solution-processing methods at temperatures no higher than 100 °C. We also integrate the devices with n-type metal oxide transistors to create complementary inverters with voltage gains of 370, and NOR and NAND logic gates with rail-to-rail switching performance.

Similar content being viewed by others

Main

The development and commercialization of high-performance n-type metal oxide field-effect transistors have outpaced their p-type counterparts1,2. Tin (Sn2+) halide perovskites, such as caesium tin triiodide (CsSnI3) and methylammonium tin triiodide (MASnI3), are p-type semiconductors with high hole mobilities (several hundreds of square centimetres per volt per second) and excellent processability via cost-effective, scalable and low-temperature film deposition methods3,4,5,6,7,8. Their dispersive valence band maximum and small hole carrier effective mass (comparable with that of silicon) provide good intrinsic hole transport properties. As a result, tin perovskites are promising semiconductors for the development of high-performance p-channel transistors, which could be used with n-channel metal oxide transistors to create noise-immune and low-power-consumption complementary-metal–oxide–semiconductor-like electronics9,10,11.

The development of high-performance tin perovskite thin-film transistors (TFTs) requires the fabrication of high-quality tin perovskite semiconductor films. However, tin perovskites typically show fast film crystallization, which leads to defective films and uncompetitive device performance12,13. B- and X-site engineering (Pb and Br/Cl alloying) can slow down Sn–I perovskite crystallization, yielding uniform films with dense grains and low defects14,15. Perovskite TFTs fabricated with this approach can deliver encouraging electrical performance with high field-effect mobility (μFE) of up to around 50 cm2 V−1 s−1. However, the involvement of heavy Pb and strong ionic Br/Cl raises concerns about Pb toxicity and enhances Fröhlich interactions between the charge carriers and electric fields produced by phonons, limiting charge-carrier mobilities at room temperature3.

Intrinsically, Sn/I as B-/X-site components can benefit high hole mobilities due to the strong Sn5s–I5p coupling near the valence band maximum and weak Fröhlich interaction3. In contrast, the A-site cation has a less direct influence on the band edge but can assist crystallization, adjust the tolerance factor, contribute to entropic/structural stabilization and indirectly optimize the perovskite properties16,17. Previous efforts, including using mixed A cations for core–shell structures and designing more conducting bulky organic spacers, have improved TFT performance, but the maximum μFE value is less than 25 cm2 V−1 s−1 (refs. 6,7,11). In this Article, we show that the A cations of caesium–formamidinium–phenethylammonium (CsFAPEA) can be used to create high-quality cascaded pure-Sn-channel films and a low-defect phase-pure perovskite/dielectric interface. The optimized TFTs exhibit a hole mobility of over 70 cm2 V−1 s−1 and a current ratio (Ion/Ioff) exceeding 108, which is similar to commercial low-temperature polysilicon (LTPS) device performance.

A-cation-engineered Sn TFTs

The Sn perovskite thin films (~30 nm thickness) with different A-cation compositions were deposited onto dielectric silicon oxide (SiO2; 100 nm thickness) substrates from different precursors using spin coating, followed by gold source and drain electrode evaporation, creating the bottom-gate top-contact TFTs (Fig. 1a). The different precursors, which mainly contain desired A-cation compositions and tin(ii) iodide (SnI2) were prepared in a glove box and all the preparation details are given in Methods. We use the nomenclature of FA, FAPEA and CsFAPEA to denote all the perovskite compounds, which act as the semiconducting layers in the TFTs with optimized performance per type. Pristine FA devices show conductor behaviours with a negligible field effect and Ion/Ioff (Supplementary Fig. 1a). Such phenomena result from the high background hole density of three-dimensional (3D) Sn perovskites, due to the lowest formation energy of Sn-vacancy defects18,19. We then involved PEA cations, which can tune the crystallization process of FASnI3 perovskite, reducing the defect densities20,21. The FAPEA TFTs (made from the optimal molar ratio of FA:PEA = 7:2) show clear field-effect modulation with an average μFE value of 14 cm2 V−1 s−1 and Ion/Ioff of 2.5 × 107 (Supplementary Fig. 1a). To explore the feasibility for higher and competitive TFT performance, we further involved the third Cs cation to substitute the partial FA cations.

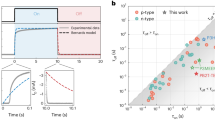

a, Structural scheme of the Sn perovskite TFT. The arrow depicts the charge-carrier transport path. b, μFE and Ion/Ioff of TFTs based on channels fabricated from mixed precursors with different Cs molar ratios, the x in (CsxFA1–x)7PEA2. The error bars are calculated from ten devices per type, and data are presented as mean ± standard deviation. c,d, Transfer (c) and output (d) characteristics of the optimized TFTs (Cs ratio = 10 mol%). Ig in c indicates the gate leakage current. The |IDS|1/2 versus VGS data of the forward scan are shown in the blue linear line, corresponding to the right y axis. VDS = −40 V. Channel width/length = 1,000 μm/200 μm. Supplementary Fig. 4 shows the electrode geometry. e, Transfer characteristics of 50 individual CsFAPEA TFTs fabricated from ten different batches. The inset shows the μFE statistics. f, Representative μFE values of reported perovskite TFTs based on different channel films. LTPS, low-temperature polysilicon level (μFE ≈ 70 cm2 V−1 s−1, Ion/Ioff ≈ 107).

Surprisingly, the triple-cation-engineered TFTs show notably boosted performance, and 10 mol% Cs substitution delivers the optimal improvement, including a fivefold higher μFE and tenfold higher Ion/Ioff compared with those of pristine FAPEA TFTs (Fig. 1b). Either a lower or higher Cs ratio decreases μFE and Ion/Ioff and results in noticeable dual-sweep hysteresis (Supplementary Fig. 1b). The typical p-channel transfer characteristics of an optimized CsFAPEA TFT (denoting (CsxFA1–x)PEA2Sn8I25, x = 10%) are shown in Fig. 1c, exhibiting a high μFE value of 72 cm2 V−1 s−1 and Ion/Ioff of 2.6 × 108 with small dual-sweep hysteresis and a subthreshold swing (SS) of 0.5 V dec−1 (discussed later). Supplementary Fig. 2 shows the plot of μFE versus gate voltage. The corresponding output characteristics of the CsFAPEA TFT show good linearity at low drain–source voltages (VDS) and current saturation at high VDS (Fig. 1d), suggesting low charge-carrier injection barriers and ohmic contact between the perovskite channel and gold electrodes. A reasonably low contact resistance of around 1 kΩ cm was calculated by the transmission-line method22 (Supplementary Fig. 3). The TFTs are also highly reproducible and an average μFE value of 67.6 ± 3.6 cm2 V−1 s−1 was obtained from 50 devices in ten different batches (Fig. 1e) with an average Ion/Ioff value of (1.8 ± 0.3) × 108, SS of 0.8 ± 0.2 V dec−1 and threshold voltage (VTH) of 20.4 ± 2.9 V (statistics defined as mean ± standard deviation). Such electrical parameters are superior to those of the devices based on other perovskite semiconductors6,7,9,11,14,15,19,23,24,25,26,27, and comparable with the commercial LTPS level (Fig. 1f).

Film morphology and structure

We then sought to understand the reasons behind the outstanding TFT performance. The morphologies of the different pure-Sn perovskite films are shown in Fig. 2a. The pristine 3D FA film shows poor film coverage with considerable voids and distinct grain boundaries, which is typical due to the extremely fast crystallization process, that is, rapid crystal growth occurs before nucleation is complete28. The grain boundaries are defect-rich regions, resulting in the highly p-doped character of the pristine FA films with poor charge transport property. PEA substitution greatly improved the film morphology, with much better coverage with only a few voids. It is also noticed that the grains tended to merge, forming a molten film with no discernible boundaries, similar to previous observations on optimized Sn perovskite films12,15. Generally, the crystallization control is essential to high-quality pure-Sn perovskite films12. The improved FAPEA film morphology can be attributed to the slower crystallization because the large PEA cations in the precursor retard the fast reactions between the perovskite building components29. However, the FAPEA film still appears bumpy with relatively high roughness and voids, indicating the regulation of fast crystallization is not yet sufficient20. With further Cs substitution, the optimized CsFAPEA film shows smooth morphology with full coverage. The roughness (Rq) for the CsFAPEA film is only 1.37 nm (Fig. 2b), around half that of the FAPEA film. The obtained smooth and pinhole-free morphology of the triple-cation CsFAPEA semiconducting film can benefit the charge-carrier transport in devices as well as the TFT uniformity and yield.

a–e, SEM (a), AFM (b), XRD (c), ultraviolet–visible (d) and photoluminescence (e) data of the perovskite films. Diffraction intensities in c are multiplied by five for the FA film and divided by three for the PEA film, for clearer display, and the diffraction patterns of the (PEA)2SnI4 film (denoted as PEA) are provided for reference. All the films were controlled with a similar thickness (~30 nm) produced under the same deposition conditions for the TFT semiconducting layers.

Figure 2c shows the X-ray diffraction (XRD) patterns of different perovskite thin films. The diffraction patterns of the pristine FA thin films are mostly indexed to 3D orthorhombic (Amm2) FASnI3 perovskite structure21. The FA film shows poor crystallinity and/or random texture, reflected by the weak diffraction peaks. Both FAPEA and CsFAPEA thin films show enhanced peak intensities of the 3D main body structure. Besides, we observed diffraction peaks from the two-dimensional small-n structures (n represents the number of octahedral inorganic sheets). The FAPEA film shows heterogeneous small-n phases for both n = 1 and 2, whereas the optimized CsFAPEA film displays a pure small-n phase of n = 2 (phase distribution will be discussed later). In the ultraviolet–visible absorption and photoluminescence spectra (Fig. 2d,e), the shoulder peaks of the n = 2 phase are detected30, whereas the n = 1 signal is not detectable possibly due to the very thin film thickness and the energy transfer between phases31.

Phase distribution and crystallization kinetics

To analyse the phase distribution, grazing-incidence wide-angle X-ray scattering (GIWAXS) measurements were conducted. Incident angles of 0.2° and 2.0° were used to characterize the thin-film surface and bulk (bottom) structures, respectively. Note that the 0.2° incident angle can typically reach ~10 nm below the surface, whereas the 2.0° can detect the bottom of our thin perovskite films. Such a method has been well established and utilized previously19,20. The pristine FA film shows random and disordered orientations, as evidenced by the blurry diffraction rings, rather than discrete Bragg diffraction spots (Supplementary Fig. 5). After introducing PEA cations, the patterns obtained from the surface of the FAPEA film are mostly indexed to the 3D FASnI3 structure (Fig. 3a). The bottom patterns are indexed to quasi-two-dimensional small-n phases due to their higher formation energy (Fig. 3b)32. We noticed that the bottom structure of FAPEA is composed of heterogeneous phases, n = 1 and n = 2, consistent with the XRD data. The more ring-like instead of spot-like diffraction patterns also reveal that the FAPEA thin film is highly defective with a random orientation/texture. Contrastingly, the optimized CsFAPEA thin film shows more discrete Bragg spots in the diffraction patterns (Fig. 3c), indicating that Cs substitution effectively improves the cascaded perovskite structure by reducing structural imperfections and regulating the ordered crystallinity/texture. Interestingly, we observed a pure small-n phase (n = 2) at the bottom of the CsFAPEA thin film (Fig. 3d). We also noticed that the small-n phases align parallel to the substrates. Previous studies reported two factors that increased the likelihood of mixed-dimensional perovskites to align parallel to the substrate: small film thickness (for example, <50 nm) and small n values (for example, ≤3)29, which rationalize the parallel orientation. This orientation is beneficial to a TFT device, where horizontal charge-carrier transport between the source and drain electrodes at the semiconductor/dielectric interface under gate voltage control is dominant (Fig. 1a).

a–d, GIWAXS for surface structure (incident angle of 0.2°) (a and c) and bottom structure (incident angle of 2.0°) (b and d) of FAPEA and CsFAPEA films. e, Dynamic light scattering data showing the particle size distribution in the precursor solutions of FAPEA and CsFAPEA. f, Illustration of the free reaction enthalpy versus the reaction coordinates, adapted from another work36.

We then sought to clarify the role of Cs substitution in the formation of high-quality cascaded perovskite films. We speculate that the differences between the crystallization kinetics of FAPEA and CsFAPEA lie in the pre- and middle-crystallization processes. Crystallization typically includes nucleation and crystal growth. It has been well recognized that fast nucleation and slow crystal growth are essential to form pinhole-free high-quality perovskite films13,33. Dynamic light scattering was used to characterize the particle size distribution in the FAPEA and CsFAPEA precursor solutions. The colloidal distribution of the FAPEA solution is mainly concentrated at ~1 nm (Fig. 3e), corresponding to a common colloidal dispersion28. The minor bump at several 103 nm is related to traces of dry material powder or impurities34. Besides the typical colloidal dispersion centred at ~1 nm, the CsFAPEA precursor solution shows another particle size distribution concentrated at ~500 nm, indicating that large stable clusters with a radius of 500 nm are already formed in the precursor solution before nucleation occurs, denoted as pre-nucleation clusters35. This pre-nucleation cluster model is different from the classical crystallization scenario but similar to the precursor-to-crystalline kinetics established for calcium carbonate36. In the classical scenario, nucleation occurs when the critical nucleation enthalpy ∆G is overcome (Fig. 3f). In the pre-nucleation cluster model, clusters are formed with a much lower activation energy barrier ∆g, which can be overcome even by room-temperature thermal energy. Therefore, we were able to detect the clusters in the CsFAPEA precursor at room temperature and they greatly reduced the free energy barrier from precursor to crystalline. As a result, nucleation happens much easier with the subsequent more uniform crystal growth and structural stabilization in CsFAPEA (Supplementary Fig. 6). In addition, the formation of the n = 2 phase at the bottom with Cs substitution is consistent with recent experimental and theoretical studies where similar n = 2 perovskite structures were observed involving different organic A-cation combinations17,21, which have been attributed to the entropic/structural stabilization, originating from self-adjustable strain balancing37. As such, triple A-cation engineering regulates the crystallization kinetics of a pure-Sn perovskite, producing high-quality thin films with fewer structural disorders, particularly creating a low-defect phase-pure perovskite/dielectric interface, which is crucial to the achievement of high-performance perovskite TFTs.

Defect–property relationship

To better understand the defect–property relationships in Sn perovskites, we conducted X-ray photoelectron spectroscopy (XPS) and Hall-effect measurements. The XPS data were used to analyse the Sn status. Sn defects are the major defects in Sn perovskites, especially Sn vacancies (VSn), which can be generated (1) during the perovskite structure formation due to their low formation energy and (2) from the oxidation of Sn2+ to Sn4+. As shown in Fig. 4a, the CsFAPEA film has a much lower ratio for the undercoordinated Sn with an oxidation state of δ < 2+ (Snδ<2+) (ref. 38), reflecting more well-coordinated Sn sublattices and a lower density of structural imperfections15. The CsFAPEA film also shows a much higher Sn2+ ratio and lower Sn4+ ratio than the other two (Supplementary Fig. 7 shows the XPS spectra). Since the VSn defects play a dominant role in deciding the hole carrier concentration of Sn perovskites4, Hall-effect measurements were then used to investigate the hole concentrations and Hall mobilities (μHall) of the different perovskite thin films (Supplementary Fig. 8). The FA film shows an average hole carrier concentration of 6.5 × 1016 cm−3, which decreases to 2.2 × 1016 cm−3 (FAPEA) and 2.4 × 1015 cm−3 for CsFAPEA films (Fig. 4b). This trend is a result of the decreasing density of hole generators, VSn, agreeing well with the XPS analyses. Correspondingly, the μHall value of the perovskite films increases from the average μHall = 45 cm2 V−1 s−1 (FA; resistivity ρ = 2.1 Ω cm) to 111 cm2 V−1 s−1 (FAPEA; ρ = 2.5 Ω cm) and up to 362 cm2 V−1 s−1 for CsFAPEA films (ρ = 6.9 Ω cm). The μHall value is mainly determined by the scattering time interval during charge-carrier transport, which is dominated by scattering centres, such as crystal structure disorders and ionized/charged defects3,15. Thus, the triple A-cation engineering effectively improves the perovskite film quality and reduces the density of charged defects, suppressing charge-carrier scattering and providing a rationale for the much enhanced μHall value.

a,b, XPS analyses on Sn status (a) and hole concentrations and Hall mobilities (μHall) of the FA, FAPEA and CsFAPEA films (b). The error bars in b were calculated from five devices per type and the data are presented as mean ± standard deviation. c, VTH shift in FAPEA and CsFAPEA TFTs under bias stress measurement (VGS = VDS = −40 V). The error bars in c were calculated from five devices per time and the data are presented as mean ± standard deviation. d, Inverter diagram and optical image. e, Butterfly voltage transfer characteristics with another plotted in a mirror; VDD = 12.5 V. The inset shows the noise margin (NM), determined by the maximum size of the square that fits the voltage transfer characteristics. f, Gain = (dVout)/(dVin). g–i, NAND and NOR optical images (g) and their output characteristics (h and i).

A TFT can also be used as a sensitive electronic characterization platform, providing more information about defects and properties. Besides high μFE and Ion/Ioff, the transfer characteristics of the CsFAPEA perovskite TFT also show minor dual-sweep hysteresis and SS of 0.5 V dec−1 (Fig. 1c). The small hysteresis mainly benefits from the reduced iodide interstitials/vacancies of iodine Frenkel defects (Supplementary Fig. 9)39, which are the main cause of hysteresis in p-channel Sn perovskite TFTs15. These iodide-related defects are preferentially formed under VSn-rich conditions39. Based on the Hall results, the cation-engineered CsFAPEA thin films show notably reduced hole concentration (VSn defects), greatly benefiting the small hysteresis. Moreover, using the SS value of 0.5 V dec−1 from the optimized CsFAPEA TFT, the trap state density (NTrap) at the dielectric/perovskite interface was calculated as 1.3 × 1012 cm−2 eV−1, which is approximately half that of FAPEA (2.5 × 1012 cm−2 eV−1, SS = 0.9 V dec−1; Methods provides the calculation details). This indicates that triple A-cation engineering not only enhances the film quality of Sn perovskites but also constructs a low-trap dielectric/perovskite interface for high-performance transistor applications.

The operation stability of perovskite TFTs was also assessed using bias stress testing to evaluate the practical applications. Constant negative bias voltages (VGS = VDS = −40 V) cause a continuous negative threshold voltage (VTH) shift over 10 V (25% of the operation voltage) for FAPEA TFTs after 4,000 s, whereas the optimized CsFAPEA TFTs only show an average VTH shift of 3.5 V (less than 10% of the operation voltage) during the first 2,000 s and remain saturated until biased for 4,000 s (Fig. 4c and Supplementary Fig. 10a,b). The smaller VTH shift in the CsFAPEA TFTs is attributed to the lower carrier trapping in the perovskite film and at the perovskite/dielectric interface14,40. This mainly benefits from the reduced trap densities through triple A-cation engineering, as demonstrated above. Interestingly, the SS of the FAPEA TFT keeps decreasing as the biasing time increases, suggesting the passivation of interface traps. A possible reason is that the charged iodide interstitials/vacancies of iodine Frenkel defects migrate, driven by the constantly applied bias voltage, resulting in the passivation of interface traps. Contrastingly, the SS of the optimized CsFAPEA TFT remains stable during the bias stress, indicating (1) that ion migration in the optimal low-defect CsFAPEA TFT is negligible and (2) that no extra trap sites are generated in the TFT under a constant bias stress41. Therefore, the triple A-cation engineering effectively reduces the trap densities, which are created by crystal defects, structure disorders and impurities, rationalizing the excellent performance and stable operation of the CsFAPEA TFTs.

Moreover, we evaluated the long-term air, thermal and light stabilities of pure-Sn perovskite TFTs. We noticed that the TFTs show fast degradation after air exposure because of Sn2+ oxidization (Supplementary Fig. 10c)4. Encouragingly, the device exhibited constant transfer characteristics after a test period of 30 days in a vacuum (~10−6 torr; Supplementary Fig. 10d), which indicates the good intrinsic phase stability of the perovskite. We anticipate that effective encapsulations, such as those used in commercial organic light-emitting diodes, and anti-oxidation additives and stabilization strategies for Sn-based perovskites would be helpful to improve the air stability42. Additionally, the TFTs showed good thermal stability at 60 °C, that is, the typical testing temperature of TFTs1 (Supplementary Fig. 10e). This would benefit from the fact that Cs, FA and PEA cations in the triple A-cation system possess higher thermal stability (>150 °C) compared with the volatile MA cation (~80 °C)43. Although we found that the device was light sensitive (Supplementary Fig. 10f), the light instability of high-performance TFTs can be readily overcome by adopting light-shielding layers used in commercial Si and metal oxide devices1. This light-sensitive property can also enable the study of multifunctional transistors and other emerging devices, for example, phototransistors, optical–electrical dual-modulation neuromorphic devices and non-volatile photomemories44,45,46,47,48.

Going a step further, we demonstrated the processability and compatibility of the p-channel perovskite TFTs with the well-developed n-channel metal oxide ones for monolithic complementary circuit integration. We fabricated the complementary metal–oxide–semiconductor inverters by integrating the perovskite TFTs on one chip with In2O3 TFTs. The inverter diagram and optical image are shown in Fig. 4d. Figure 4e shows the standard rail-to-rail voltage transfer characteristics, where Vout was either the supplied VDD or 0 (GND) with an abrupt switch at around VDD/2, indicating an ideal logic transfer from ‘1’ to ‘0’. More importantly, the inverter shows a noise margin of 5.16 V, reaching as high as 82% of the ideal value (VDD/2), which means that even if the noise causes a Vin shift up to 82% of VDD/2, the inverter would still give a correct Vout signal, showing the high noise-immune character. The integrated inverter also shows a high gain of 370 at VDD = 12.5 V (Fig. 4f), markedly superior to the wire-linked complementary inverter or complementary-metal–oxide–semiconductor-like inverters involving perovskite TFTs9,49. Furthermore, we integrated the complementary logic gates, namely, NAND and NOR (Fig. 4g), demonstrating the good technological adaptation of perovskite TFTs. Figure 4g shows the optical images and Fig. 4h,i plots the output characteristics of NAND and NOR, respectively, showing full rail-to-rail Boolean functionalities. The input signals are the voltage inputs for Vin1 and Vin2, where logic ‘1’ and ‘0’ represent voltages of VDD = 10 V and 0 V, respectively.

Conclusions

We have reported high-performance pure-Sn perovskite TFTs by incorporating a triple A-cation combination (CsFAPEA) to construct low-defect cascaded channel films. This simple A-cation engineering creates a low-trap perovskite/dielectric interface, which is crucial for efficient charge-carrier transport and high-performance TFTs. The resulting transistors exhibit a high hole μFE value of over 70 cm2 V−1 s−1, which is comparable with commercial LTPS-based devices. The perovskite TFTs also show good compatibility with commercial n-channel metal oxide technologies, highlighting their potential in the development of functional complementary circuits50.

Methods

Chemicals

We used the following as received without further purification: N,N-dimethylformamide (anhydrous, 99.80%, Sigma-Aldrich), dimethyl sulfoxide (anhydrous, ≥99.90%, Sigma-Aldrich), formamidinium iodide (FAI, ≥99.50%, Xi’an Polymer Light Technology), phenethylammonium iodide (≥99.50%, Xi’an Polymer Light Technology), caesium iodide (CsI, >99.90%, Xi’an Polymer Light Technology), SnI2 (anhydrous, beads, 99.99% trace-metal basis, Sigma-Aldrich), tin(ii) fluoride (99.00%, Sigma-Aldrich) and chlorobenzene (anhydrous, 99.80%, Sigma-Aldrich).

Precursor and device preparation

The precursor solutions were prepared by mixing FAI, phenethylammonium iodide, CsI and SnI2 in N,N-dimethylformamide/dimethyl sulfoxide mixed solvents at a volume ratio of 3:1. First, FAI (0.2 M), phenethylammonium iodide (0.4 M) and SnI2 (0.2 M, with 10 mol% tin(ii) fluoride) were dissolved in the solvents. Then, they were mixed at a volume ratio of 7:1:8 to get the FA7PEA2 (denoted to FAPEA) precursors (0.1 M). To make the (CsxFA1–x)7PEA2 precursor, CsI (0.2 M) was prepared before being mixed at a volume ratio of FAI:CsI = (1−x):x, x = ~0–15% into the FAPEA precursors. The optimized samples made from x = 10% were denoted as CsFAPEA. Each precursor was stir heated at 60 °C for 2 h before use. Dielectric layers were the purchased 100 nm SiO2 on Si substrates with a capacitance of ~30 nF cm−2. For the perovskite film deposition, the SiO2/Si substrates (1.5 × 1.5 cm2) were first treated with ultraviolet ozone for 30 min, then the precursor solutions were dropped on the substrates and spin coated at a speed of 4,000 r.p.m. for 60 s (acc 5 s) with 70 µl of chlorobenzene dripping after ~15 s from the beginning. Afterwards, the films were annealed at 100 °C for 10 min, constructing thin films with a similar thickness of ~30 nm. All the precursor solutions and films were prepared in a N2-filled glove box (O2 and H2O levels of 1–2 ppm). Then, thermal evaporation and a shadow mask were used for the Au source/drain electrode deposition. The channel width and length of the TFTs are 1,000 and 200 μm, respectively. Supplementary Fig. 4 provides the electrode geometry. Each TFT was tip scratched before measurement to reduce the gate leakage and the influence of fringe effect. Smaller channel lengths would cause the maximum drain current beyond the equipment test limit (10−2 A). For the complementary inverter and logic gates integration, we first evaporated patterned nickel (20 nm) as the bottom gate through a designed shadow mask, then used hafnium oxide (100 nm) by atomic layer deposition as the dielectric layer, solution-processed In2O3 TFTs patterned by photolithography as n-channel and self-patterned perovskite TFTs as the p-channel and eventually evaporated gold through another designed shadow mask as source and drain electrodes.

Characterizations

The XRD patterns of the film were recorded using a Rigaku D/MAX 2600V with Cu Kα (λ = 1.5406 Å) radiation. The SEM images were obtained using a field-emission scanning electron microscope (Hitachi S4800). AFM data were collected using atomic force microscopy (Nanoscope V Multimode 8, Bruker). XPS characterizations were conducted using a VersaProbe Scanning Microprobe under a vacuum (10−8 torr). The Hall measurements were performed using the van der Pauw method, using a 0.51 T magnet and a bespoke sample holder in a N2-filled glove box at room temperature. The electrical signal during the Hall measurement was obtained using a Keithley 4200-SCS and probe station (MST 4000A, MS TECH). Dynamic light scattering measurements were conducted using a Zetasizer Nano (Malvern Instruments). For the GIWAXS analysis, the X-ray beam energy was 9.84 eV, corresponding to a wavelength of 1.26 Å, and the sample–detector distance was 208.76 mm. Transistor transfer characteristics were measured using a semiconductor parameter analyser (Keithley 4200-SCS) in a N2-filled glove box at room temperature in the continuous mode. The saturation TFT mobility was calculated as

where L, W, Ci, IDS and VGS are the channel length, channel width, dielectric areal capacitance, source–drain current and gate–source voltage, respectively. The SS value was extracted from the reciprocal of a subthreshold slope, in V dec–1. The VTH value was extracted by linear fitting |IDS|1/2 versus VGS. The perovskite/dielectric interface trap density can be estimated from \({N}_{{{\rm{trap}}}}=\left[\frac{{{\rm{SS}}q}{{\log }}(e)}{{kT}}-1\right]\frac{{C}_{{\rm{i}}}}{q}\), where q is the electron charge, k is the Boltzmann constant and e is the base of the natural logarithm.

Data availability

All data needed to evaluate the conclusions in the paper are present in the paper and/or its Supplementary Information. Additional data related to this paper are available from the corresponding authors A.L. (ao.liu@northwestern.edu) or Y.-Y.N. (yynoh@postech.ac.kr) upon reasonable request.

References

Shiah, Y.-S. et al. Mobility–stability trade-off in oxide thin-film transistors. Nat. Electron. 4, 800–807 (2021).

Liu, A., Zhu, H. & Noh, Y.-Y. Solution-processed inorganic p-channel transistors: recent advances and perspectives. Mater. Sci. Eng.: R Rep. 135, 85–100 (2019).

Herz, L. M. Charge-carrier mobilities in metal halide perovskites: fundamental mechanisms and limits. ACS Energy Lett. 2, 1539–1548 (2017).

Zhou, Y. et al. Defect activity in metal halide perovskites with wide and narrow bandgap. Nat. Rev. Mater. 6, 986–1002 (2021).

Chung, I. et al. CsSnI3: semiconductor or metal? High electrical conductivity and strong near-infrared photoluminescence from a single material. High hole mobility and phase-transitions. J. Am. Chem. Soc. 134, 8579–8587 (2012).

Liang, A. et al. Ligand-driven grain engineering of high mobility two-dimensional perovskite thin-film transistors. J. Am. Chem. Soc. 143, 15215–15223 (2021).

Gao, Y. et al. Highly stable lead-free perovskite field-effect transistors incorporating linear π-conjugated organic ligands. J. Am. Chem. Soc. 141, 15577–15585 (2019).

Liu, A. et al. Antimony fluoride (SbF3): a potent hole suppressor for tin(ii)-halide perovskite devices. InfoMat 5, e12386 (2023).

Zhu, H. et al. High-performance and reliable lead-free layered-perovskite transistors. Adv. Mater. 32, 2002717 (2020).

Lin, Y. H., Pattanasattayavong, P. & Anthopoulos, T. D. Metal-halide perovskite transistors for printed electronics: challenges and opportunities. Adv. Mater. 29, 1702838 (2017).

Kim, J. et al. High-performance p-channel tin halide perovskite thin film transistor utilizing a 2D–3D core–shell structure. Adv. Sci. 9, 2104993 (2022).

Zhu, Z. et al. Smooth and compact FASnI3 films for lead-free perovskite solar cells with over 14% efficiency. ACS Energy Lett. 7, 2079–2083 (2022).

Dong, H. et al. Crystallization dynamics of Sn-based perovskite thin films: toward efficient and stable photovoltaic devices. Adv. Energy Mater. 12, 2102213 (2022).

Liu, A. et al. High-performance inorganic metal halide perovskite transistors. Nat. Electron. 5, 78–83 (2022).

Zhu, H. et al. High-performance hysteresis-free perovskite transistors through anion engineering. Nat. Commun. 13, 1741 (2022).

Lee, J. W. et al. Rethinking the A cation in halide perovskites. Science 375, eabj1186 (2022).

Tong, J. et al. Carrier control in Sn-Pb perovskites via 2D cation engineering for all-perovskite tandem solar cells with improved efficiency and stability. Nat. Energy 7, 642–651 (2022).

Xiao, Z., Song, Z. & Yan, Y. From lead halide perovskites to lead-free metal halide perovskites and perovskite derivatives. Adv. Mater. 31, 1803792 (2019).

Shao, S. et al. Field-effect transistors based on formamidinium tin triiodide perovskite. Adv. Funct. Mater. 31, 2008478 (2021).

Wang, F. et al. 2D-quasi-2D-3D hierarchy structure for tin perovskite solar cells with enhanced efficiency and stability. Joule 2, 2732–2743 (2018).

Shao, S. et al. Highly reproducible Sn-based hybrid perovskite solar cells with 9% efficiency. Adv. Energy Mater. 8, 1702019 (2018).

Liu, C., Xu, Y. & Noh, Y.-Y. Contact engineering in organic field-effect transistors. Mater. Today 18, 79–96 (2015).

Kagan, C., Mitzi, D. & Dimitrakopoulos, C. Organic-inorganic hybrid materials as semiconducting channels in thin-film field-effect transistors. Science 286, 945–947 (1999).

Matsushima, T. et al. Solution-processed organic–inorganic perovskite field-effect transistors with high hole mobilities. Adv. Mater. 28, 10275–10281 (2016).

Liu, A. et al. Modulation of vacancy-ordered double perovskite Cs2SnI6 for air-stable thin-film transistors. Cell Rep. Phys. Sci. 3, 100812 (2022).

Senanayak, S. P. et al. A general approach for hysteresis-free, operationally stable metal halide perovskite field-effect transistors. Sci. Adv. 6, eaaz4948 (2020).

She, X. J. et al. A solvent-based surface cleaning and passivation technique for suppressing ionic defects in high-mobility perovskite field-effect transistors. Nat. Electron. 3, 694–703 (2020).

Meng, X. et al. Crystallization kinetics modulation of FASnI3 films with pre-nucleation clusters for efficient lead-free perovskite solar cells. Angew. Chem. Int. Ed. 60, 3693–3698 (2021).

Quintero-Bermudez, R. et al. Compositional and orientational control in metal halide perovskites of reduced dimensionality. Nat. Mater. 17, 900–907 (2018).

Liu, J. et al. Observation of internal photoinduced electron and hole separation in hybrid two-dimentional perovskite films. J. Am. Chem. Soc. 139, 1432–1435 (2017).

Wang, N. et al. Perovskite light-emitting diodes based on solution-processed self-organized multiple quantum wells. Nat. Photon. 10, 699–704 (2016).

Chen, S. et al. Crystallization in one-step solution deposition of perovskite films: upward or downward? Sci. Adv. 7, eabb2412 (2021).

Liu, C., Cheng, Y.-B. & Ge, Z. Understanding of perovskite crystal growth and film formation in scalable deposition processes. Chem. Soc. Rev. 49, 1653–1687 (2020).

O’Kane, M. E. et al. Exploring nanoscale structure in perovskite precursor solutions using neutron and light scattering. Chem. Mater. 34, 7232–7241 (2022).

Gebauer, D. et al. Pre-nucleation clusters as solute precursors in crystallisation. Chem. Soc. Rev. 43, 2348–2371 (2014).

Gebauer, D., Völkel, A. & Cölfen, H. Stable prenucleation calcium carbonate clusters. Science 322, 1819–1822 (2008).

Fu, Y. et al. Incorporating large a cations into lead iodide perovskite cages: relaxed Goldschmidt tolerance factor and impact on exciton–phonon interaction. ACS Cent. Sci. 5, 1377–1386 (2019).

Mundt, L. E. et al. Surface-activated corrosion in tin–lead halide perovskite solar cells. ACS Energy Lett. 5, 3344–3351 (2020).

Ambrosio, F., Meggiolaro, D., Almutairi, T. M. & De Angelis, F. Composition-dependent struggle between iodine and tin chemistry at the surface of mixed tin/lead perovskites. ACS Energy Lett. 6, 969–976 (2021).

Lin, Y.-H. et al. Hybrid organic–metal oxide multilayer channel transistors with high operational stability. Nat. Electron. 2, 587–595 (2019).

Liu, A. et al. High-performance p-channel transistors with transparent Zn doped-CuI. Nat. Commun. 11, 4309 (2020).

Ye, T. et al. Ambient-air-stable lead-free CsSnI3 solar cells with greater than 7.5% efficiency. J. Am. Chem. Soc. 143, 4319–4328 (2021).

Kim, J. Y. et al. High-efficiency perovskite solar cells. Chem. Rev. 120, 7867–7918 (2020).

Zhu, H. et al. Perovskite and conjugated polymer wrapped semiconducting carbon nanotube hybrid films for high-performance transistors and phototransistors. ACS Nano 13, 3971–3981 (2019).

Zhu, H. et al. High-performance layered perovskite transistors and phototransistors by binary solvent engineering. Chem. Mater. 33, 1174–1181 (2021).

Li, F. et al. Ambipolar solution-processed hybrid perovskite phototransistors. Nat. Commun. 6, 8238 (2015).

Beom, K., Fan, Z., Li, D. & Newman, N. Halide perovskite based synaptic devices for neuromorphic systems. Mater. Today Phys. 24, 100667 (2022).

Chen, J.-Y. et al. Nonvolatile perovskite-based photomemory with a multilevel memory behavior. Adv. Mater. 29, 1702217 (2017).

Yusoff, A. Rb. M. et al. Ambipolar triple cation perovskite field effect transistors and inverters. Adv. Mater. 29, 1602940 (2017).

Park, W.-T. & Noh, Y.-Y. A self-aligned high resolution patterning process for large area printed electronics. J. Mater. Chem. C 5, 6467–6470 (2017).

Acknowledgements

This study was supported by the Ministry of Science and ICT through the National Research Foundation, funded by the Korean government (2021R1A2C3005401, RS-2023-00216352 and RS-2023-00260608; to Y.-Y.N.). This work was supported by the BK21 FOUR Program for Education Program for Innovative Chemical Engineering Leaders of the National Research Foundation of Korea (NRF) grant funded by the Korean government (MSIT to A.L. and H. Z.). This research was also supported by the Samsung Display Corporation (to Y.-Y.N.). H.Z. thanks J. Kim and J.-Y. Go for help with the GIWAXS measurements and analyses, and also to G.-S. Ryu for help with the shadow mask design.

Author information

Authors and Affiliations

Contributions

H.Z. and Y.-Y.N. conceived the study. H.Z. performed the experiments. A.L. and W.Y. helped with the experiment. A.L., Y.R. and G.Z. assisted with the characterizations and analyses. A.L. and S.B. helped with the analyses and discussion. H.Z., A.L. and Y.-Y.N. wrote the manuscript. All the authors contributed to the discussion and approved the final version of the manuscript.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Nature Electronics thanks Mallory Mativenga, Anita Ho-Baillie and Kamal Asadifor for their contribution to the peer review of this work.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Supplementary Information

Supplementary Figs. 1–10.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Zhu, H., Yang, W., Reo, Y. et al. Tin perovskite transistors and complementary circuits based on A-site cation engineering. Nat Electron 6, 650–657 (2023). https://doi.org/10.1038/s41928-023-01019-6

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1038/s41928-023-01019-6