Abstract

Two-dimensional semiconductors can be used to build next-generation electronic devices with ultrascaled channel lengths. However, semiconductors need to be integrated with high-quality dielectrics—which are challenging to deposit. Here we show that single-crystal strontium titanate—a high-κ perovskite oxide—can be integrated with two-dimensional semiconductors using van der Waals forces. Strontium titanate thin films are grown on a sacrificial layer, lifted off and then transferred onto molybdenum disulfide and tungsten diselenide to make n-type and p-type transistors, respectively. The molybdenum disulfide transistors exhibit an on/off current ratio of 108 at a supply voltage of 1 V and a minimum subthreshold swing of 66 mV dec−1. We also show that the devices can be used to create low-power complementary metal–oxide–semiconductor inverter circuits.

Similar content being viewed by others

Main

Dielectric layers with a high dielectric constant (κ), minimal leakage current and reduced thickness are essential for creating low-power electronic devices and circuits. High-κ dielectrics such as hafnium oxide (HfO2) have, for instance, been used in silicon electronics for over a decade1,2,3,4. Similar approaches to grow high-κ dielectric layers have been attempted on two-dimensional (2D) layered materials including graphene, transition metal dichalcogenides and black phosphorus5,6,7,8,9,10,11. However, unlike conventional semiconductors, the surfaces of 2D materials are free of dangling bonds and thus a seeding layer or surface functionalization is typically required to provide nucleation sites before the growth of a high-κ dielectric12,13,14. These additional treatments increase the processing complexity and degrade the interface between the dielectric and 2D material15.

Surface oxidation of semiconducting Bi2O2Se into Bi2SeO5—a high-κ dielectric material—can avoid such pretreatment, but this method faces challenges to become more generally applicable16,17. Pretreatment can also be avoided if the dielectric can be integrated on the 2D material using only van der Waals forces, instead of chemical bonding during in situ growth. Various van der Waals heterostructures have been fabricated by creating layers on another substrate and then transferring them onto a 2D material as a freestanding thin film18,19, but using such methods with dielectrics is challenging due to the difficulties in preparing and handling freestanding high-κ dielectric thin films. Single-crystal strontium titanate, SrTiO3 (STO), is a complex oxide with a high dielectric constant of over 300 at room temperature20,21. These properties make it attractive for exploring the emergent transport properties of 2D materials in an ultrahigh-κ dielectric environment21,22, as well as for fabricating 2D-material-based electronic devices with scaled supply voltage. However, it is challenging to integrate STO on 2D materials, which is required for independent gate control in practical applications, due to structure mismatch and processing incompatibility common for oxide materials23,24,25.

In this Article, we report high-performance n-type molybdenum disulfide (MoS2) and p-type tungsten diselenide (WSe2) field-effect transistors (FETs) on silicon substrates with single-crystal STO as the top-gate dielectric. The STO is epitaxially grown on a sacrificial layer and subsequently transferred with the help of van der Waals forces. The MoS2 FETs exhibit an on/off current ratio (Ion/Ioff) of over 108 within the top-gate voltage (VTG) range of ±1.0 V and a minimum subthreshold swing (SS) of 66 mV dec−1. The WSe2 FETs exhibit an on/off ratio of 107 within a VTG value of ±1.0 V. The near-ideal SS and negligible residual doping illustrate the high quality of the STO–2D material interfaces. Double-gate and Hall-effect measurements on graphene devices yield an effective dielectric constant of 17–20, which is higher than that of HfO2 (κ ≈ 13–17)26,27, when grown by atomic layer deposition on 2D materials. We also create a low-power complementary metal–oxide–semiconductor (CMOS) inverter that has a static power consumption of only several picowatts by combining STO-gated n-type MoS2 and p-type WSe2 transistors.

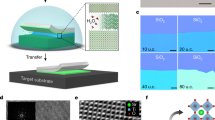

Fabrication of STO–2D material heterostructures

Our integration of STO on 2D layered materials begins with the sequential pulsed laser deposition (PLD) of Sr3Al2O6 (SAO) and STO layers on STO substrates28,29,30,31 (Methods provides details of growth) (Fig. 1a). Next, the surface of the as-grown STO thin film was covered with a thin polydimethylsiloxane (PDMS) sheet. The stack was then floated in a deionized (DI) water bath to etch the sacrificial SAO layer and produce an STO membrane adhering to the PDMS sheets due to van der Waals forces (Supplementary Fig. 1 shows the optical images of the STO membrane on PDMS). This membrane was then deliberately ruptured and transferred onto multiple PDMS sheets by repetitive laminating and peeling the PDMS sheets to produce scattered micrometre-sized STO flakes. In this way, we could choose STO flakes with lateral sizes similar to those of mechanically exfoliated 2D materials, facilitating subsequent device fabrication. The STO flakes on PDMS were accurately aligned and brought into contact with target 2D flakes on SiO2/Si substrates and being monitored under a microscope. Last, the PDMS was peeled off slowly, leaving the STO flakes on SiO2/Si substrates because of a stronger interaction between STO and SiO2 than that between STO and PDMS32. The freestanding STO film can be transferred, in principle, onto any 2D material, which is crucial for fabricating complex electronic circuits involving 2D materials with different electronic properties.

a, Schematic of the fabrication process: (i) sequential PLD growth of SAO and STO on a bulk STO substrate; (ii) the surface of the STO thin film is covered with a PDMS sheet and the stack is then floated in a DI water bath to dissolve the sacrificial SAO layer; (iii) the PDMS sheet supporting the STO membrane is laminated with another PDMS sheet and peeled off slowly, yielding micrometre-sized STO flakes on both PDMS sheets; (iv) a micrometre-sized STO flake is aligned and laminated, under a microscope, onto a 2D material on SiO2/Si. The PDMS sheet is then peeled off, leaving STO on SiO2/Si. b, Optical image of a representative STO–MoS2 heterostructure on SiO2/Si. The inset displays the optical image of the original MoS2 flake. Scale bars, 10 µm. c, AFM height image of the heterostructure shown in b. Scale bar, 5 µm. The inset shows the height profile along the marked line, from which the thicknesses of MoS2 (3.4 nm) and STO (45.9 nm) were extracted. d, Schematic of three-dimensional cubic and 2D layered crystal structures of STO and MoS2. e, Cross-sectional HAADF-STEM image of an STO–MoS2 heterointerface. Scale bar, 2 nm.

A representative STO–MoS2 heterostructure on SiO2/Si is shown in Fig. 1b. Transferring STO on MoS2 did not induce noticeable contamination. The morphology of this heterostructure was further examined by atomic force microscopy (AFM) imaging (Fig. 1c). Both STO and MoS2 flakes exhibited uniform thicknesses and clean surfaces. Conformal contact was formed at the heterointerface, although STO has a distinctively different crystal structure compared with MoS2 (Fig. 1d). Figure 1e shows the high-angle annular dark-field scanning transmission electron microscopy (HAADF-STEM) image of an STO–MoS2 interface. Individual atoms of STO arranged in a cubic lattice can be clearly identified in the STEM image and the X-ray diffraction peaks of STO film transferred on the SiO2/Si substrate can be clearly identified (Supplementary Fig. 1). Both these results confirm the excellent crystallinity of STO even after transfer. The intact layered structure of MoS2 demonstrates that the van der Waals integration process is non-invasive to the underlying 2D materials.

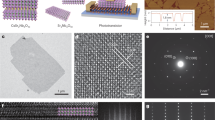

Dielectric properties of transferred STO

The quantitative evaluation of the effective dielectric constant of transferred STO flakes, which includes contributions from the van der Waals gap and interfacial impurities, is not currently available experimentally. Therefore, to ensure the accuracy of the extracted value, we employed two methods: double-gate33 and Hall-effect34 measurements. Figure 2a shows a graphene Hall bar device on a p-Si substrate with a 285 nm SiO2 capping layer. SiO2 and STO act as the bottom- and top-gate dielectric layers, respectively. The graphene sheet was patterned by electron-beam lithography and etched into a Hall bar using oxygen plasma before being covered with STO (Supplementary Fig. 2). The thicknesses of STO (44.2 nm) and graphene (double layer) were determined by AFM and Raman spectroscopy, respectively (Supplementary Fig. 3). The charge carrier concentration in graphene can be simultaneously modulated by the top and bottom gates. As a result, the top-gate transfer curves shift with a varying back-gate voltage (VBG) (Fig. 2b). The slope of the top-gate Dirac point voltage (VDIRAC,TG), which marks charge neutrality, versus VBG is equal to the ratio of the bottom-gate to top-gate capacitance (\(C_{{{{\mathrm{SiO}}}}_2}/C_{{{{\mathrm{STO}}}}}\)), if the parallel-plate capacitor model is assumed for both top and bottom gates27,33. Substituting the fitted value (0.03) in Fig. 2c into

where εSTO and \(\varepsilon _{{{{\mathrm{SiO}}}}_2}\) (3.9) are the dielectric constants of STO and SiO2, respectively, and tSTO and \(t_{{{{\mathrm{SiO}}}}_2}\) are the thicknesses of STO and SiO2, respectively, we derived εSTO of 20.2 from this device, which corresponds to a capacitance of 0.4 µF cm−2.

a, Optical image of a graphene Hall bar device with STO top-gate dielectrics. The boundary of the double-layer graphene is indicated by the dashed line. Scale bar, 10 µm. The inset illustrates the device geometry. b, Sheet resistance (RS) of graphene (Gr) as a function of top-gate voltages (VTG) at different back-gate voltages (VBG). c, VBG-dependent top-gate Dirac voltages (VDIRAC,TG). The linear fitting, represented by the solid line, yields a slope of −0.03. d, Hall resistance (Rxy) as a function of magnetic field (B) at different VTG values. e, Hole concentration (p2D) versus VTG, extracted from the linear fitting of Rxy–B relations in d. The solid line indicates the linear fitting of p2D–VTG. f, Leakage current density (JTG) versus VTG of three representative devices.

Carrier concentrations, from which the dielectric constant of STO can also be derived, were directly extracted by Hall-effect measurements. Figure 2d shows that the Hall resistance (Rxy) linearly depends on the magnetic field (B) at different VTG values. The Rxy–B slope is equal to 1/(en2D) or 1/(ep2D) depending on the carrier type, where e, n2D and p2D are the elementary charge, electron concentration and hole concentration, respectively. At VTG away from the Dirac point, one type of carrier dominates in graphene and their concentration changes linearly with VTG (ref. 35). From the linear fit of p2D–VTG (Fig. 2e), the top-gate capacitance CSTO is calculated to be 0.34 µF cm−2 according to dp2D/dVTG = CSTO/e. The accuracy of the Hall-effect measurements was further verified by its application in back gating. They yield \(\varepsilon _{{{{\mathrm{SiO}}}}_2}\) of 4.0 (Supplementary Fig. 4), which matches the theoretical value of SiO2 (3.9–4.0). It is worth noting that the extracted εSTO from double-gate (20.2) and Hall-effect (17.2) measurements includes contributions from polymethyl methacrylate (PMMA) residues between STO and graphene, which reduce the effective capacitance and dielectric constant. Nonetheless, these values are already greater than that of atomic-layer-deposited HfO2 on 2D materials, demonstrating the feasibility of using STO for practical devices27.

The dielectric strength of STO was also investigated. Leakage currents through Au–STO–graphene stacks (JTG) display similar attributes (Fig. 2f). The leakage current is very small and below the detection limit of our measurement setup (~10−13 A) when VTG is within the range of roughly −4 to 2 V. Beyond this range, JTG increases rapidly but no catastrophic failure is observed within ±10 V, which corresponds to a nominal electric field of around 2.5 MV cm−1. These results prove the electrical robustness of the transferred STO. In addition, the forward-biased JTG is substantially larger than the reverse-biased JTG, which can be explained by the band alignment of the heterostructures (Supplementary Fig. 5). STO is an insulator with a bandgap of 3.3 eV (ref. 36), and the Fermi level of graphene, which can be tuned by VTG, aligns closer to the conduction band edge of STO. As a result, electrons (holes) can be injected into STO at a large positive (negative) VTG, and electron injection starts at a smaller bias. Such leakage behaviour does not deter the operation of 2D transistors because the large dielectric constant of STO, compared with more commonly used dielectric materials for 2D electronics such as hexagonal boron nitride (hBN), Al2O3 and HfO2 (Supplementary Table 1), provides sufficient electrostatic modulation to 2D semiconductors at small gate voltages, as demonstrated in the following sections.

MoS2 transistors with STO top-gate dielectrics

As the most studied 2D semiconductor for field-effect transistors, few-layer (FL) MoS2 was selected to prove the feasibility of STO as the dielectric layer in high-performance transistors. To fully explore the potential of STO-gated MoS2 transistors, we employed FL graphene as the drain/source electrodes for the following reasons. First, its gate-tuneable Fermi level facilitates barrier-free injection of charge carriers into 2D semiconductors37,38. Second, its atomically flat and ultrathin nature allows the fabrication of multilayer van der Waals heterostructures with clean and flat interfaces39,40,41. Third, the mechanical flexibility and optical transparency of graphene are desirable for potential flexible and transparent electronics based on 2D semiconductors42. To fabricate graphene-contacted MoS2 transistors, we sequentially transferred graphene, MoS2 and STO on SiO2/Si substrates (Supplementary Fig. 6). The device structure is sketched in Fig. 3a. The channel length and width of the fabricated device based on an FL MoS2 flake and 38.1 nm STO (Fig. 3b, inset) are 5.4 µm and 4.8 µm, respectively. The graphene electrodes are beneath MoS2 and overlap with the top gate so that the whole MoS2 channel as well as the graphene–MoS2 contact regions are simultaneously modulated by the top gate. Thus, the transistor is effectively turned on and off by applying VTG within the range of ±1 V. As shown in Fig. 3c and Supplementary Fig. 7, the output curves are linear when VDS is small, indicating ohmic contacts. When VDS further increases, IDS gradually saturates, signalling pinch-off of the MoS2 channel at larger VDS. The transfer curves in Fig. 3b, measured with the back gate grounded (VBG = 0 V), display characteristics of a typical n-type transistor with a current on/off ratio (Ion/Ioff) of over 108 at a drain–source bias (VDS) of 0.5 V and an SS value as small as 66 mV dec−1, close to the thermionic limit at room temperature (60 mV dec−1). The SS remains low for IDS of several orders of magnitude (Fig. 3d). Little hysteresis in the IDS–VTG or SS–IDS curves is observed between the forward and reverse top-gate sweeping, indicating a low interfacial trap density. The reproducibility of these performance metrics was verified by the measurements of nine devices (Supplementary Table 2).

a, Schematic of the double-gated transistor together with the electrical measurement configuration. S, source; D, drain. b, Double-sweep IDS–VTG characteristics of the device with the back gate grounded. The gate sweeping directions are indicated by the arrows. The inset shows the optical image of the device. The boundaries of graphene and MoS2 are outlined by dashed lines. Scale bar, 10 µm. c, Output curves (IDS–VDS) with VTG varying from 0 to 1.0 V at steps of 0.1 V. d, Subthreshold swing (SS) as a function of IDS. e, Mobility (µ) of MoS2 measured by four-probe (device numbers 1–4) and two-probe (device numbers 5–7) method before and after the deposition of STO. f, A comparison of the current on/off ratio (Ion/Ioff) and SS of our transistor with state-of-the-art MoS2 transistors with hBN or high-κ dielectrics in the literature10,11,13,27,39,48,49,50,51. The required gate voltages for the corresponding Ion/Ioff and SS are also labelled.

The high Ion/Ioff at small operation voltages of our STO-gated MoS2 transistors can be attributed to the following three reasons. First, the top-gate electrode and high-κ STO covers both MoS2 channel and graphene–MoS2 contacts and simultaneously exerts strong electrostatic modulation to them. Thus, the on current is not limited by the access resistance (Supplementary Fig. 8), which exists in many locally top-gated MoS2 transistors10,27. Second, the near-ideal SS value permits turning the transistor on and off within a narrow gate-voltage span. It originates from a relatively small capacitance related to the interfacial traps compared with the dielectric capacitance of STO according to

where kB, T, q, CSTO and Cit are the Boltzmann constant, absolute temperature, elementary charge, areal capacitance of STO and areal capacitance related to interfacial traps, respectively13,43. Third, the deposition of STO has a trivial effect on the doping level and mobility of MoS2. In recent reports, it was shown that the atomic layer deposition of high-κ dielectrics tends to exert a considerable n-doping effect on MoS2 to the extent that a large negative top-gate voltage is required to turn off the transistors13,15,44. Such a doping effect has been frequently attributed to the unbalanced positive charges in the dielectric layer15,45. In contrast, the van der Waals integration of STO has a negligible doping effect on MoS2, indicating little net charges in STO. This phenomenon is proved by the very similar back-gate transfer characteristics of MoS2 transistors before and after the deposition of STO (Supplementary Fig. 9c). The IDS–VBG curves show little horizontal shift and the transistor without and with the STO coverage is switched off at almost the same VBG. The high-κ dielectric environment has been proposed as a booster for the mobility of MoS2 because it benefits the screening of charged impurity scattering34,46. However, the extra high-κ dielectrics also bring additional scattering sources, such as trapped charges in high-κ dielectrics and at the interfaces, which deteriorate the mobility44,46,47. The mobility of MoS2 before and after the deposition of STO was investigated by both two- and four-probe field-effect measurements (Supplementary Fig. 9 and Supplementary Table 3). As shown in Fig. 3e, the mobility exhibits varied behaviours for the seven devices, but the change after STO deposition is generally small. The relatively unchanged mobility compared with that before covering with STO is probably due to counteraction from the previously mentioned opposed effects. Nonetheless, the retained value of mobility allowed the STO-gated MoS2 transistors to exhibit sufficient on-state conductance leading to Ion/Ioff over 108 within the VTG range of ±1 V.

Figure 3f shows that the performance of our MoS2 transistors is competitive compared with the state-of-the-art MoS2 transistors employing hBN or high-κ dielectrics, such as HfO2 and Al2O3, in terms of Ion/Ioff and SS. A large Ion/Ioff is indispensable for the explicit recognition of the on and off states for practical digital electronics. A smaller SS means more abrupt switching of the transistor between the on and off states because SS represents the minimum required change in the gate voltage for a tenfold increase in IDS. In addition, the magnitude of the required gate voltage also depends on the initial doping level of MoS2, which shifts the IDS–VBG curves close to or away from the zero gate voltage (as explained above). The required gate voltages for the corresponding Ion/Ioff and SS are labelled in Fig. 3f for comparison. As can be seen, the magnitude of the required gate voltages of our STO-gated MoS2 transistors is also among the lowest.

Low-power CMOS inverter

The top-gate transfer characteristics of our MoS2 transistors can be tuned by VBG (Fig. 4a). As VBG decreases, the IDS–VTG curves shift monotonously in the positive direction. At a large negative VBG, the transistor transforms into the enhancement mode, which means the threshold voltage (VTH) becomes positive, and a positive VTG is required to switch on the transistor. In particular, with a back-gate biasing of −30 V, IDS is below 1 pA at VTG = 0 V. However, due to the preserved low SS, IDS reaches over 1 µA at VTG of only 1 V, displaying an Ion/Ioff of over 107 (Fig. 4b). These merits demonstrate that our top-gated transistor can operate with a very low standby power consumption. It is worth noting that both dynamic and static power consumed by back-gate biasing are negligible since VBG is fixed and the d.c. current through the relatively thick SiO2 is negligible. Tuning VTH by back-gate biasing in this work is analogous to the back-gate biasing strategy in advanced silicon-on-insulator and FinFET technologies52,53. Properly scaling the thickness of the bottom SiO2 may reduce the required VBG to a value comparable to VTG. The combination of near-ideal subthreshold slope, large Ion/Ioff and small operation voltage of our transistors is especially useful for low-power electronic applications.

a, Transfer curves (IDS–VTG) of the MoS2 transistor at different back-gate voltages. b, IDS–VTG of the WSe2 transistor (p-FET) and MoS2 transistor (n-FET) at VBG = −40 V. They were measured at VDS = 1 V (n-FET) and VDS = −1 V (p-FET). The inset shows the circuit diagram of the CMOS inverter. VDD, VIN and VOUT stand for the supply voltage, input voltage and output voltage, respectively. c, Voltage transfer curves of a CMOS inverter built on a WSe2 p-type and MoS2 n-type transistor. The inset shows the voltage gain (−dVOUT/dVIN) of the inverter. d, Instantaneous power consumed by the inverter against VIN.

Low-power digital circuits are critical to extend the service time of ubiquitous portable devices that rely on batteries, as well as to avoid overheating that leads to the malfunction of processors. As usually implemented for emerging materials and technologies54,55, the potential of our STO-gated transistors for low-power digital circuits was verified by fabricating and testing inverters (or ‘NOT’ logic gates), the basic functional unit in CMOS digital circuits. A CMOS inverter (circuit diagram shown in Fig. 4b, inset) consists of a p-type and n-type transistor in series and their conductance is simultaneously controlled by a single gate voltage (VIN). It outputs a logic state that opposes the input and these logic states are represented by the respective voltage levels. To fabricate the CMOS inverter, we realized p-type transistors with a local STO top gate through chemical doping and back-gate biasing of WSe2 (Supplementary Fig. 10). The transfer characteristic of the WSe2 transistor (Fig. 4b) reveals Ion/Ioff of ~107 within the VTG range of ±1 V. Connecting the WSe2 and MoS2 transistors in the inverter configuration, we obtained an excellent inversion action (voltage transfer characteristics are shown in Fig. 4c). When the input voltage (VIN) is zero (corresponding to logic ‘0’), the output voltage (VOUT) approaches the supply voltage (VDD), corresponding to logic ‘1’. On the contrary, when VIN is increased to a higher value (logic ‘1’), VOUT is close to zero (logic ‘0’). Benefitting from the gate-tuneable IDS–VTG characteristics of our MoS2 transistors, the inverter functions well at totally positive voltages, a requirement for practical applications. The peak values of voltage gain (10.5 at VDD = 0.5 V and 14.2 at VDD = 1.0 V), defined as −dVOUT/dVIN, are far greater than unity, demonstrating that our inverter is robust to errors and suitable for multistage logic circuits.

The total power consumed by an inverter in practical CMOS digital circuits include dynamic, static and short-circuit power56. The dynamic power results from the charging and discharging of the next-stage metal–oxide–semiconductor capacitor during switching and is proportional to the square of the operation voltages. Therefore, the minimized operation voltages of our transistors should be highly beneficial for a reduction in dynamic power. To analyse the static and short-circuit power consumed by our inverter, we plotted the instantaneous power against VIN (Fig. 4d). The instantaneous power is equal to VDD × IDD, where IDD is the current flowing from supply to ground. The static power, that is, the power consumed at idle ‘0’ or ‘1’ states, comes mainly from subthreshold conduction. The static power consumed by our inverter is shown to be at the picowatt level, which is difficult to achieve with typical 2D semiconductor-based CMOS inverters due to subthreshold current still consuming considerable power at VIN = 0 V. The short-circuit power, which is the instantaneous power at VIN other than the ‘0’ and ‘1’ states, has peak values of 21 nW at VDD = 0.5 V and 0.34 µW at VDD = 1.0 V. Although these values are not outstanding, the short-circuit power makes up a very small portion of the total power because the inverter stays at the ‘0’ and ‘1’ states for most of the time during each functioning cycle of digital circuits56. It is also worth mentioning that our locally gated WSe2 transistors operate in the depletion mode. This fact limits the voltage gain, increases the required VIN (higher than the respective VDD) to switch off the p-type WSe2 transistor of the inverter and deteriorates the short-circuit power. The realization of enhancement-mode p-type transistors, whose performance matches the MoS2 n-type transistors, should improve the gain and power consumption further.

Conclusions

We have shown that thin films of high-κ STO can be integrated with 2D materials using a van der Waals approach. Using stacked STO as the top dielectric material, we created a MoS2 n-type transistor that, due to the large dielectric constant of STO and excellent interfacial quality, exhibits an Ion/Ioff value of over 108 at a supply voltage of 1 V and minimum SS of 66 mV dec−1. We also created a CMOS inverter with picowatt standby power consumption by combining the n-type MoS2 transistors with p-type WSe2 transistors. Our van der Waals integration strategy circumvents many technical problems of established methods, which tend to deteriorate the interface quality or restrict material combinations during fabrication, and other complex oxides and 2D materials may be able to adopt this strategy to construct high-performance devices and circuits. Our approach provides a potential route to a wide range of hybrid oxide–oxide and oxide–2D material heterostructures, which could be used to create advanced forms of electronics such as hybrid spintronics and oxide-based twistronics.

Methods

Material preparation

STO/SAO bilayer films were sequentially grown by PLD on TiO2-terminated STO(001) substrates with sintered SAO and STO ceramic targets. Before the deposition, the STO substrates were buffered HF etched and then annealed at 950 °C to achieve a TiO2-terminated atomically flat surface57. During growth, the target materials were vapourized by irradiation of an excimer laser (wavelength λ = 248 nm) operated with a repetition rate of 2 Hz and a laser fluence of 1.8 J cm−2, whereas the STO substrates were kept at 760 °C. The partial pressures of oxygen (PO2) for the growth of SAO and STO were 1 × 10−6 and 1 × 10−2 torr, respectively. After deposition, all the samples were cooled down to room temperature at the rate of 10 °C min–1 under a PO2 value of 1 × 10−2 torr.

SiO2/Si substrates were treated with oxygen plasma (CUTE-1MPR dual-mode plasma processing system, Femto Science) for 5 min at a power of 50 W before mechanical exfoliation and transfer of graphene (Gr), MoS2 and WSe2. To transfer MoS2 on Gr, MoS2 flakes on SiO2/Si were lifted off by PDMS sheets using a wedging transfer method58. Briefly, the surface of the SiO2/Si substrate supporting the target MoS2 flake was covered with a PDMS sheet. Then, DI water was added to the surrounding of the PDMS sheet, and it slowly penetrated into the gap between PDMS and SiO2 because the SiO2 surface is hydrophilic after oxygen plasma treatment. The PDMS sheet with the target MoS2 flake finally floated up on the surface of DI water. The PDMS/MoS2 stack was then picked up, dried and transferred onto graphene on another SiO2/Si substrate using the method described earlier.

Material characterization

HAADF-STEM images were obtained at 300 kV using an aberration-corrected FEI Titan Themis G2 instrument. The AFM images were measured in the tapping mode using a Cypher ES Environmental AFM (Asylum Research). Raman spectra were measured on a WITec alpha300 confocal Raman system with an excitation wavelength of 532 nm.

Device fabrication

Drain, source and top-gate electrodes were defined by electron-beam lithography followed by thermal deposition of 5 nm Cr and 60–100 nm Au.

Electrical measurements

The transistors were bonded to chip carriers and measured using a Keithley 2635b sourcemeter and two Keithley 2450 sourcemeters in a shielded vacuum chamber (0.1 mbar) at room temperature. The CMOS inverters were measured with an additional Keithley 2230G power supply. Two-terminal I–V measurements were performed using the Keithley 2635b sourcemeter. Hall-effect measurements were carried out in a helium atmosphere (~0.1 torr) in an Oxford TeslatronPT cryostation equipped with a magnetic field of up to 8 T.

Data availability

The data that support the conclusions in this paper are available from the corresponding authors upon reasonable request.

References

Kingon, A. I., Maria, J.-P. & Streiffer, S. Alternative dielectrics to silicon dioxide for memory and logic devices. Nature 406, 1032–1038 (2000).

Gusev, E. et al. Ultrathin high-K gate stacks for advanced CMOS devices. In International Electron Devices Meeting. Technical Digest (Cat. No.01CH37224) 20.1.1–20.1.4 (IEEE, 2001).

Bohr, M. T., Chau, R. S., Ghani, T. & Mistry, K. The high-k solution. IEEE Spectr. 44, 29–35 (2007).

Packan, P. et al. High performance 32nm logic technology featuring 2nd generation high-k + metal gate transistors. In 2009 IEEE International Electron Devices Meeting (IEDM) 1–4 (IEEE, 2009).

Franklin, A. D. Nanomaterials in transistors: from high-performance to thin-film applications. Science 349, aab2750 (2015).

Chhowalla, M., Jena, D. & Zhang, H. Two-dimensional semiconductors for transistors. Nat. Rev. Mater. 1, 16052 (2016).

Liu, Y., Duan, X., Huang, Y. & Duan, X. Two-dimensional transistors beyond graphene and TMDCs. Chem. Soc. Rev. 47, 6388–6409 (2018).

Akinwande, D. et al. Graphene and two-dimensional materials for silicon technology. Nature 573, 507–518 (2019).

Resta, G. V. et al. Devices and circuits using novel 2-D materials: a perspective for future VLSI systems. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 27, 1486–1503 (2019).

Radisavljevic, B., Radenovic, A., Brivio, J., Giacometti, V. & Kis, A. Single-layer MoS2 transistors. Nat. Nanotechnol. 6, 147–150 (2011).

Wang, H. et al. Integrated circuits based on bilayer MoS2 transistors. Nano Lett. 12, 4674–4680 (2012).

McDonnell, S. et al. HfO2 on MoS2 by atomic layer deposition: adsorption mechanisms and thickness scalability. ACS Nano 7, 10354–10361 (2013).

Zou, X. et al. Interface engineering for high‐performance top‐gated MoS2 field‐effect transistors. Adv. Mater. 26, 6255–6261 (2014).

Kim, H. G. & Lee, H.-B.-R. Atomic layer deposition on 2D materials. Chem. Mater. 29, 3809–3826 (2017).

Sheng, Y. et al. Gate stack engineering in MoS2 field‐effect transistor for reduced channel doping and hysteresis effect. Adv. Electron. Mater. 7, 2000395 (2020).

Li, T. et al. A native oxide high-κ gate dielectric for two-dimensional electronics. Nat. Electron. 3, 473–478 (2020).

Tu, T. et al. Uniform high-k amorphous native oxide synthesized by oxygen plasma for top-gated transistors. Nano Lett. 20, 7469–7475 (2020).

Liang, S. J., Cheng, B., Cui, X. & Miao, F. Van der Waals heterostructures for high‐performance device applications: challenges and opportunities. Adv. Mater. 32, 1903800 (2019).

Liu, Y., Huang, Y. & Duan, X. Van der Waals integration before and beyond two-dimensional materials. Nature 567, 323–333 (2019).

Sakudo, T. & Unoki, H. Dielectric properties of SrTiO3 at low temperatures. Phys. Rev. Lett. 26, 851 (1971).

Couto, N. J., Sacépé, B. & Morpurgo, A. F. Transport through graphene on SrTiO3. Phys. Rev. Lett. 107, 225501 (2011).

Veyrat, L. et al. Helical quantum Hall phase in graphene on SrTiO3. Science 367, 781–786 (2020).

Liu, Y. et al. Thermal oxidation of WSe2 nanosheets adhered on SiO2/Si substrates. Nano Lett. 15, 4979–4984 (2015).

Liu, X., Wood, J. D., Chen, K.-S., Cho, E. & Hersam, M. C. In situ thermal decomposition of exfoliated two-dimensional black phosphorus. J. Phys. Chem. Lett. 6, 773–778 (2015).

Rao, R., Islam, A. E., Campbell, P. M., Vogel, E. M. & Maruyama, B. In situ thermal oxidation kinetics in few layer MoS2. 2D Mater. 4, 025058 (2017).

Sangwan, V. K. et al. Quantitatively enhanced reliability and uniformity of high-κ dielectrics on graphene enabled by self-assembled seeding layers. Nano Lett. 13, 1162–1167 (2013).

Li, W. et al. Uniform and ultrathin high-κ gate dielectrics for two-dimensional electronic devices. Nat. Electron. 2, 563–571 (2019).

Lu, D. et al. Synthesis of freestanding single-crystal perovskite films and heterostructures by etching of sacrificial water-soluble layers. Nat. Mater. 15, 1255–1260 (2016).

Ji, D. et al. Freestanding crystalline oxide perovskites down to the monolayer limit. Nature 570, 87–90 (2019).

Dong, G. et al. Super-elastic ferroelectric single-crystal membrane with continuous electric dipole rotation. Science 366, 475–479 (2019).

Hong, S. S. et al. Extreme tensile strain states in La0.7Ca0.3MnO3 membranes. Science 368, 71–76 (2020).

Castellanos-Gomez, A. et al. Deterministic transfer of two-dimensional materials by all-dry viscoelastic stamping. 2D Mater. 1, 011002 (2014).

Xu, H. et al. Quantum capacitance limited vertical scaling of graphene field-effect transistor. ACS Nano 5, 2340–2347 (2011).

Radisavljevic, B. & Kis, A. Mobility engineering and a metal–insulator transition in monolayer MoS2. Nat. Mater. 12, 815–820 (2013).

Xia, J., Chen, F., Wiktor, P., Ferry, D. & Tao, N. Effect of top dielectric medium on gate capacitance of graphene field effect transistors: implications in mobility measurements and sensor applications. Nano Lett. 10, 5060–5064 (2010).

Van Benthem, K., Elsässer, C. & French, R. Bulk electronic structure of SrTiO3: experiment and theory. J. Appl. Phys. 90, 6156–6164 (2001).

Yu, L. et al. Graphene/MoS2 hybrid technology for large-scale two-dimensional electronics. Nano Lett. 14, 3055–3063 (2014).

Liu, Y. et al. Toward barrier free contact to molybdenum disulfide using graphene electrodes. Nano Lett. 15, 3030–3034 (2015).

Lee, G.-H. et al. Highly stable, dual-gated MoS2 transistors encapsulated by hexagonal boron nitride with gate-controllable contact, resistance, and threshold voltage. ACS Nano 9, 7019–7026 (2015).

Cui, X. et al. Multi-terminal transport measurements of MoS2 using a van der Waals heterostructure device platform. Nat. Nanotechnol. 10, 534–540 (2015).

Avsar, A. et al. Air-stable transport in graphene-contacted, fully encapsulated ultrathin black phosphorus-based field-effect transistors. ACS Nano 9, 4138–4145 (2015).

Yoon, J. et al. Highly flexible and transparent multilayer MoS2 transistors with graphene electrodes. Small 9, 3295–3300 (2013).

Sze, S. M. & Ng, K. K. Physics of Semiconductor Devices (John Wiley & Sons, 2006).

Zou, X. et al. Dielectric engineering of a boron nitride/hafnium oxide heterostructure for high‐performance 2D field effect transistors. Adv. Mater. 28, 2062–2069 (2016).

Xu, J.-P. et al. Effects of trapped charges in gate dielectric and high-κ encapsulation on performance of MoS2 transistor. IEEE Trans. Electron Devices 66, 1107–1112 (2019).

Ma, N. & Jena, D. Charge scattering and mobility in atomically thin semiconductors. Phys. Rev. 4, 011043 (2014).

Konar, A., Fang, T. & Jena, D. Effect of high-κ gate dielectrics on charge transport in graphene-based field effect transistors. Phys. Rev. B 82, 115452 (2010).

Wang, J. et al. Integration of high‐k oxide on MoS2 by using ozone pretreatment for high‐performance MoS2 top‐gated transistor with thickness‐dependent carrier scattering investigation. Small 11, 5932–5938 (2015).

Zhu, Y. et al. Monolayer molybdenum disulfide transistors with single-atom-thick gates. Nano Lett. 18, 3807–3813 (2018).

Desai, S. B. et al. MoS2 transistors with 1-nanometer gate lengths. Science 354, 99–102 (2016).

Wang, X. et al. Improved integration of ultra-thin high-k dielectrics in few-layer MoS2 FET by remote forming gas plasma pretreatment. Appl. Phys. Lett. 110, 053110 (2017).

Liu, Q. et al. Impact of back bias on ultra-thin body and BOX (UTBB) devices. In 2011 Symposium on VLSI Technology—Digest of Technical Papers 160–161 (IEEE, 2011).

Jha, N. K. & Chen, D. Nanoelectronic Circuit Design (Springer Science & Business Media, 2010).

Qiu, C. et al. Scaling carbon nanotube complementary transistors to 5-nm gate lengths. Science 355, 271–276 (2017).

Kong, L. et al. Doping-free complementary WSe2 circuit via van der Waals metal integration. Nat. Commun. 11, 1866 (2020).

Henzler, S. Power Management of Digital Circuits in Deep Sub-Micron CMOS Technologies Vol. 25 (Springer Science & Business Media, 2006).

Kawasaki, M. et al. Atomic control of the SrTiO3 crystal surface. Science 266, 1540–1542 (1994).

Schneider, G. F., Calado, V. E., Zandbergen, H., Vandersypen, L. M. & Dekker, C. Wedging transfer of nanostructures. Nano Lett. 10, 1912–1916 (2010).

Acknowledgements

We are grateful to S. Zeng and D. Wan for fruitful discussion regarding the PLD growth, as well as G. Chen for her help regarding the device fabrication. X.R.W. acknowledges support from the Nanyang Assistant Professorship grant from Nanyang Technological University; Academic Research Fund Tier 2 (grant nos. MOE-T2EP50120-0006 and MOE-T2EP50220-0016) and Tier 3 (grant no. MOE2018-T3-1-002) from the Singapore Ministry of Education; the Singapore National Research Foundation (NRF) under the Competitive Research Programs (CRP grant no. NRF-CRP21-2018-0003); and Agency for Science, Technology and Research (A*STAR) under its AME IRG grant (project no. A20E5c0094). Q.X. gratefully acknowledges funding support from the State Key Laboratory of Low-Dimensional Quantum Physics and start-up grant from Tsinghua University. P.G. acknowledges the support from the National Natural Science Foundation of China (grant nos. 51672007 and 11974023), the National Key R&D Program of China (grant no. 2016YFA0300804), Key Area R&D Program of Guangdong Province (2018B010109009), the Key R&D Program of Guangdong Province (2018B030327001), the National Equipment Program of China (ZDYZ2015-1), the ‘2011 Program’ Peking-Tsinghua-IOP Collaborative Innovation Center for Quantum Matter and Electron Microscopy Laboratory in Peking University for the use of the Cs-corrected electron microscope.

Author information

Authors and Affiliations

Contributions

A.J.Y. and X.R.W. conceived the idea and designed the experiments. A.J.Y. fabricated the heterostructures and devices. A.J.Y., assisted by K. Huang and C.Y., performed the electrical measurements and analysis. K. Han grew the oxides. W.W. performed the Raman characterization. Rui Zhu, Ruixue Zhu, J.X. and P.G. performed the STEM characterization and analysis. A.J.Y. and X.R.W. wrote the manuscript. All the authors contributed to the scientific discussion and commented on the manuscript.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Nature Electronics thanks Jianping Shi and the other, anonymous, reviewer(s) for their contribution to the peer review of this work.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Supplementary Information

Supplementary Figs. 1–10 and Tables 1–3.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Yang, A.J., Han, K., Huang, K. et al. Van der Waals integration of high-κ perovskite oxides and two-dimensional semiconductors. Nat Electron 5, 233–240 (2022). https://doi.org/10.1038/s41928-022-00753-7

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1038/s41928-022-00753-7

This article is cited by

-

Two-dimensional perovskite oxide as a photoactive high-κ gate dielectric

Nature Electronics (2024)

-

Heterogeneous integration of high-k complex-oxide gate dielectrics on wide band-gap high-electron-mobility transistors

Communications Engineering (2024)

-

Van der Waals enabled formation and integration of ultrathin high-κ dielectrics on 2D semiconductors

npj 2D Materials and Applications (2024)

-

Exploring the high dielectric performance of Bi2SeO5: from bulk to bilayer and monolayer

Science China Materials (2024)

-

Understanding the 2D-material and substrate interaction during epitaxial growth towards successful remote epitaxy: a review

Nano Convergence (2023)