Abstract

Monolayer molybdenum disulfide (ML-MoS2) is an emergent two-dimensional (2D) semiconductor holding potential for flexible integrated circuits (ICs). The most important demands for the application of such ML-MoS2 ICs are low power consumption and high performance. However, these are currently challenging to satisfy due to limitations in the material quality and device fabrication technology. In this work, we develop an ultra-thin high-κ dielectric/metal gate fabrication technique for the realization of thin film transistors based on high-quality wafer scale ML-MoS2 on both rigid and flexible substrates. The rigid devices can be operated in the deep-subthreshold regime with low power consumption and show negligible hysteresis, sharp subthreshold slope, high current density, and ultra-low leakage currents. Moreover, we realize fully functional large-scale flexible ICs operating at voltages below 1 V. Our process could represent a key step towards using energy-efficient flexible ML-MoS2 ICs in portable, wearable, and implantable electronics.

Similar content being viewed by others

Introduction

Flexible electronics plays an integral role in a large spectrum of fields including information technology, energy generation and storage, bio-sensing, and diagnosis1,2,3,4,5. Among them, flexible integrated circuits (ICs) dealing with information processing are favorable in portable, wearable, and implantable electronics with technological demands towards flexibility and robustness of large-area devices6,7,8. Conventional flexible ICs are usually fabricated from organic semiconductors6, 8, silicon of either amorphous or polycrystalline forms9,10, oxide semiconductors11,12, and carbon nanotubes (CNTs)13,14,15,16,17 via the thin-film-transistor (TFT) technology. Recently, the 2D semiconductor of monolayer MoS2 (ML-MoS2) emerged as an advanced channel material in large-area flexible TFTs18,19,20,21,22,23,24,25,26. In principle, such TFTs have great potential in both high performance and low-power applications, if considering the following merits. First, ML-MoS2 is atomically thin (only ~0.7 nm) and smooth yet mechanically strong (in-plane) and flexible (out-of-plane)1,27. Such a thin channel also offers benefits in ultra-scale devices where short channel effects would be the main concern28,29,30. Second, its 2H phase has a moderate band gap of ~2 eV, between that of silicon (~1.1 eV) and indium gallium zinc oxide (~3.5 eV), hence can work with both low off-state and high on-state currents31,32. Third, it has high electrical quality and is available at wafer scale22,33,34,35,36.

It has been shown that, at room temperature, rigid ML-MoS2 TFTs can feature high electron mobility (μ) of >100 cm2·V−1·s−1, high on/off ratio of >108, low subthreshold swing (SS) approaching the thermionic limit of 60 mV·dec−1, and high on-current of ~1.1 mA·μm−1 at a supply voltage of 1.5 V37,38,39. Hence, one might ask if such TFT technologies developed on rigid substrates could be transferred onto flexible substrates and be superior to existing flexible TFT technologies. Up to now, large-scale flexible ML-MoS2 ICs with various fully functional units such as logic gates, inverters, and ring oscillators (ROs) have been demonstrated vividly23,24,25. However, limited by materials and fabrications, such large-area flexible ICs suffer from either low performances or high-power consumptions, and it is challenging to realize both in a synergic manner.

In this work, we demonstrate the realization of low-power flexible ICs based on ML-MoS2. The technological advances of this work lay on both the newly developed high-quality ML-MoS2 wafers and the ultra-thin high-κ dielectric/metal-gate technology. High-quality 4-inch wafer-scale ML-MoS2 films are epitaxially grown on sapphire via an oxygen-assisted chemical vapor deposition (CVD) approach we developed recently34. As-grown films are strictly monolayer, uniform across entire substrates, and have large domain sizes over 200 μm. Such high-quality materials offer a desirable choice for realizing large-scale flexible ICs. Here, the flexible ICs are fabricated via a gate-first technology in which ultra-thin high-κ dielectrics are deposited on gate electrodes to achieve a record-low equivalent oxide thickness (EOT). Due to the enhanced gating efficiency, our ML-MoS2 flexible TFTs can work under operation voltages below 1 V.

Results

Gate-first technology for ultra-thin high-κ dielectric deposition

In a power-efficient system, transistors and circuits should ideally have a low-driving voltage which can be created by using high-capacitance dielectric layers for efficient electrostatic gating. We thus employed ultra-thin high-κ dielectrics of HfO2, a technique widely used in the present silicon-based high-performance and low-power electronics. Since ultra-thin high-κ dielectrics are very difficult to deposit on MoS2 due to the lack of surface dangling bonds40,41, we hence developed the high-κ dielectric/metal-gate technology, i.e. a gate-first technology, for ML-MoS2 TFTs. Figure 1a illustrates the device geometry with buried Ti-Au-Ti as the local back-gate electrode, ultra-thin HfO2 as the dielectric layer, ML-MoS2 as the channel, and Au as the source/drain electrodes.

a Schematic illustration of a buried-gate MoS2 TFT. b, c Cross-sectional scanning transmission electron microscope (STEM) image (b) of 5-nm HfO2 on the buried Ti-Au-Ti (1-5-1 nm) gate electrode, and corresponding energy disperse spectroscopy (EDS) elemental mapping image (c) clearly shows the distribution of Au, Ti, Hf and Si elements. Scale bars, 10 nm. d Atomic-resolution cross-sectional STEM image of Au-MoS2 contact interface. Red, yellow, and blue spheres are Au, Mo, and S atoms, respectively. Scale bar, 1 nm. e The dielectric constant and equivalent oxide thickness (EOT) of HfO2 layers deposited at different temperatures. f Normalized transfer curves of MoS2 TFTs (L = 5 μm, W = 40 μm) at Vds = 1 V with 5 nm, 10 nm HfO2 and 30 nm Al2O3 as the dielectric layer, individually. g, h Typical electrical output and transfer curves of MoS2 TFTs with Lch ≈ 50 nm and 5-nm HfO2 as the dielectric layer. Inset to (g) is the scanning electron microscope (SEM) image of the Lch ≈ 50 nm device. The Ids/W-Vg curve features with the sharp subthreshold swing (ISS = 75 mV·dec−1, refer to the black dash line) and small hysteresis (∆Vg = 11.5 mV, inset to h). The leakage current (Ig) is represented in gray color in (h).

During the device gate-first fabrication process, buried-gate electrodes of Ti-Au-Ti (1-5-1 nm) were first deposited on a substrate (either rigid or flexible) by standard lithography and electron beam evaporation processes. Note that the top 1 nm-Ti layer after oxidation in O2 plasma serves as the seeding layer for following atomic layer deposition (ALD) of the high-κ dielectrics; while the bottom 1 nm-Ti layer acts as the adhesive layer between Au and substrate. Other than the deposition of the seeding layer for the subsequent HfO2 deposition on 2D materials like graphene42, our approach employs the seeding layer on metal gates which are more general and compatible with the semiconductor fabrication process. Before and after metal gate depositions, we performed oxygen plasma cleaning to remove the photoresist residues on side walls and top surface of patterns/metal-gates introduced from the lithography process, as illustrated in Supplementary Fig. 1. With the help of this cleaning process, we can produce flat metal gates with clean surfaces and sharp boundaries. After ALD, the deposited HfO2 layers on metal gates are very uniform, as characterized by the atomic force microscope (AFM). The measured surface roughness of 5-nm HfO2 deposited on Ti/Au/Ti metal gates is typically <0.5 nm. After high-κ dielectric deposition, a 4''-wafer-sized ML-MoS2 film (See Supplementary Fig. 2 and Table 1 for film quality characterizations and comparisons) was transferred onto the overall structure by a wet chemical etching, and the transferred ML-MoS2 films are almost intact and flat on target substrates process (see Methods and Supplementary Fig. 3). Finally, multistep lithography, reactive ion etching (RIE), and electron beam evaporation were performed to define the channel and source/drain (S/D) contact regions.

For a typical TFT on the SiO2 substrate, we characterized its interfaces between different layers by cross-sectional scanning transmission electron microscope (STEM). Figure 1b, c shows a typical STEM image and corresponding Au, Ti, Hf, Si elemental mapping from energy disperse spectroscopy (EDS) at the HfO2/metal-gate interface. We can see a uniform and conformal coating of HfO2 with a thickness of 5 nm on the metal gate. Figure 1d shows an atomic-resolution STEM image of the Au-MoS2 interface. The sharp interface between periodically arranged Au atoms and three-atom-thick MoS2 surface without any defects or cracks suggests the high quality of contacts.

To evaluate the dielectric properties of HfO2 layers deposited on metal gates by ALD, we performed capacitance measurements (Supplementary Fig. 4). In Fig. 1e, we plot the dielectric constants (εr) of 5-nm and 10-nm thick HfO2 layers deposited at 110, 150, and 200 °C. Obviously, higher deposition temperature and thicker thickness are beneficial to achieving a better dielectric property. Hence, the ALD temperature of 200 °C was applied for rigid devices; whereas it is 150 or 110 °C for flexible devices to reduce the temperature-induced substrate deformation. In our batch fabrication of devices, the minimum HfO2 thickness (tHfO2) is 5 nm on rigid substrates, e.g., SiO2, and 10 nm on flexible substrates, e.g., polyethylene terephthalate (PET, see Supplementary Fig. 5 for roughness characterizations), for a reliable device yield. Note that the 5-nm HfO2 layer has an effective oxide thickness (EOT) of only 1.1 nm. Such low EOT is beneficial to high device transconductance at low supply voltages and efficient gating of MoS2 channels.

ML-MoS2 TFTs on rigid substrates

Firstly, let’s evaluate ML-MoS2 TFTs on SiO2 substrates with normalized channel lengths (Lch) and widths (W). Figure 1f shows the normalized transfer curves (Ids·L/W-∆Vg) of devices with HfO2 layer thickness of 5 and 10 nm. As a comparison, 30 nm thick Al2O3 devices are also included. It can be clearly seen that with decreased tHfO2 and increased εr, the gate voltages (Vg) can be reduced from 15 V to 3 V and the SS can be reduced from 250 mV·dec−1 to 75 mV·dec−1, while preserving the on-state current (Ion) densities and on/off ratios.

Figure 1g, h demonstrate typical output (Ids/W-Vds) and transfer curves (Ids/W-Vg) of a short channel device with tHfO2 = 5 nm and Lch ≈ 50 nm. This device features ultra-high on/off ratio of ~109, sharp subthreshold slope (SS) of ISS = 75 mV·dec−1 over 5 orders of magnitude, and negligible hysteresis (∆Vg ~ 11.5 mV, inset to Fig. 1h) subjected to the high quality of MoS2/HfO2 interface. The ultra-high on/off ratio could guarantee an ultra-low static power dissipation. When devices work at a stand-by mode (off state), the leakage current (Ig/W) can reach below 1 pA·μm−1 (Fig. 1h) for a general W/Lch = 5 μm/50 nm device. Due to the high gating efficiency, the maximum field could approach ~1 V·nm−1 and the carrier density can approach ni = 5.15 × 1013 cm−2 at Vg = 5 V. Note that the effective carrier densities in MoS2 channel would be overestimated based on the metal-insulator-metal capacitance (MIMCAP) results, thus we carried out metal-oxide-semiconductor capacitance (MOSCAP) measurements based on the MoS2 FET (Supplementary Fig. 6). Such high carrier densities in ML-MoS2 channels are among the highest in previous reports. As a result, the maximum on-state current densities (Ion/W) could reach 936 μA·μm−1 at Vds = 1.5 V with Lch = 50 nm in Fig. 1g, which is comparable to the highest value (1135 μA·μm−1 at Vds = 1.5 V) previously achieved in Bi-contacted ML-MoS2 TFTs with Lch = 35 nm39. More data on MoS2 TFTs with Lch of 150 nm and 300 nm appears in Supplementary Fig. 7. Note that even Au-contacts show slightly higher contact resistances than Bi-contacts, our devices still show linear output characteristics at small bias and saturated output behaviors at high bias voltages, which is important for the output current capacity of short channel devices. Besides, Ion/W is ~720 μA·μm−1 at Vds = 1 V, meeting the low-power application metrics of the International Roadmap for Devices and Systems (IRDS, 2024)43.

ML-MoS2 TFTs on flexible substrates

Next, we implement the technique of ultra-thin high-κ dielectric/metal gate deposition on flexible PET substrate. Figure 2a shows 4” wafer-scale ML-MoS2 TFTs on PET substrate. Now let’s evaluate devices on flexible substrates based on 10 nm HfO2. These long-channel TFTs have a high device yield (>96%) and nice spatial uniformity. In Fig. 2b we show transfer curves of 500 randomly picked TFTs with Lch varying from 5 to 75 μm. Statistics on the device’s μFE, on/off ratio, threshold voltage (Vth), and SS are shown in Fig. 2c. According to Lorentz distribution fittings, μFE averages at ~70 cm2·V−1·s−1 (maximizes at >110 cm2·V−1·s−1); on/off ratio averages at 5 × 107 (maximizes at ~1 × 109); Vth is centered at 0.96 ± 0.4 V; and SS averages at 83 mV·dec−1. All these performances are comparable to those previously achieved in rigid ML-MoS2 TFTs (Supplementary Table 2) and greatly improved over the previous state-of-the-art flexible TFTs (Supplementary Table 3). It is worth noting here that both the positive Vth and small SS are critical for the low power consumption in our devices, as will be shown later. Note that we also realize the fabrications of flexible ML-MoS2 FETs based on 5 nm HfO2 as measured in Supplementary Figs. 8, 9. Considering the low device yield (~60%) and higher leakage current level of the 5 nm HfO2, we mainly adopt 10 nm HfO2 as dielectric layer for integrated logic gates in following experiments.

a Photograph of an as-fabricated 4-inch MoS2 TFTs on the polyethylene terephthalate (PET) substrate. Scale bar, 1 cm. b Transfer curves of 500 randomly picked TFTs with the 10 nm HfO2 dielectrics. Bias voltage (Vds) is 1 V, and the device yield is 96.2%. Inset to (b) shows the enlarged image of the device array. Scale bar, 200 μm. c Histogram and Lorentz distribution fits of the device mobility, on/off ratio, threshold voltage and subthreshold swing extracted from the transfer curves in (b). d Contact and sheet resistance measurements from transfer length method (TLM) at ni ≈ 2.8 × 1013 cm−2. e Statistics and comparisons of the on-state current density of the flexible and rigid TFTs at Vds = 1 V versus channel length. This work is highlighted in red and blue circles, while the reference data points are drawn in gray and green squares (please refer to Supplementary Tables 2, 3 for details). Error bars in (d) and (e) are taken from 10 transistors with the same channel length.

According to previous studies44, the Vth variability comes mainly from sources including material uniformity (defects, grain boundaries, and layer thicknesses), oxide roughness, surface (MoS2 surface), and interface (contact interface, oxide-MoS2 interface) cleanness. In this study, MoS2 is strictly monolayer without additional layers and of high quality. High defects (mainly S-vacancies) density could cause severe n-doping in the devices, shifting Vth to very negative values. In present devices, the positive Vth reflects the low density of vacancy defects in the MoS2 channel region. The domain sizes in our samples are over 200 µm, much larger than the channel sizes, suggesting that grain boundaries are also not likely the source of Vth variations. The thin HfO2 layers deposited on metal gates are smooth with a surface roughness of ~0.5 nm, measured by AFM. We thus conclude that the main source of Vth variability, although it is small, comes mainly from the surface and interface cleanness.

The high device performance is attributed to several aspects. First, our ML-MoS2 films are of high quality. The extracted sheet resistance R□ is ~5.2 kΩ at ni ≈ 2.8 × 1013 cm−2 fitted by the transfer length method (TLM), as shown in Fig. 2d. Second, the employment of HfO2 dielectrics allows us to tune carrier densities in MoS2 over than 5 × 1013 cm−2. Third, the contact resistance Rc between Au and MoS2 is as low as ~0.59 kΩ·μm (see Fig. 2d and Supplementary Fig. 10 for the Rc extraction based on long channel and short channel devices). Such low Rc is facilitated by the ultra-slow Au-deposition rates (see Methods) and the bottom gate structure in which the contact region of ML-MoS2 can be doped to be metallic properties. Based on our data from both rigid and flexible TFTs, here we highlight the on-state current densities (Ids/W) as a function of Lch in Fig. 2e. Clearly, our data points lay at the upper envelope boundary if compared with literature works from monolayer flexible or rigid MoS2 TFTs (all reference data points acquired from Supplementary Tables 2, 3).

Low-power and high-performance flexible ICs

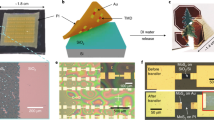

We further fabricated large-area flexible ICs based on ML-MoS2. Figure 3a shows a photograph of 4 × 4 cm2 electronic circuits fabricated on the PET substrate. As logic gates and inverters are essential building blocks of ICs, we included logic inverters, NAND, NOR, and AND gates in this batch (Fig. 3b, c).

a Photograph of 4 × 4 cm2 integrated monolayer MoS2 TFTs on the flexible PET substrate. Scale bar, 1 cm. b, c Optical image (b) and schematic circuits (c) of logic inverters, NAND, NOR, AND gates and 5-stage ring oscillators. Scale bar, 200 μm. Vdd, power supply voltage; Vin, VA, or VB, input voltages; Vout, output voltage. d Voltage transfer curves (VTCs) of a logic inverter with noise margin of 0.8(Vdd /2) at Vdd = 0.5 V. Inset shows corresponding voltage gain of 120. e Comparison of the inverter voltage gain as a function of Vdd among flexible inverters or rigid inverters based on 2D materials. The reference data points are listed in Supplementary Table 4. f Output characteristics of logic NAND, NOR, AND gates as a function of input voltage pulses with Vdd = 0.5 V.

The output characteristic of ML-MoS2 inverter shows abrupt switching behavior with power supply voltages Vdd = 0.5 V (Fig. 3d). The trip point of the inverter is when output voltage (Vout) equals input voltage (Vin) and of particular importance for low-power electronics as it determines the driving voltage of integrated logic circuits. The typical inverter also exhibits full swing output behavior with noise margin (NM) of 0.8×(Vdd /2) and voltage gain of 120. Note that the highest voltage gain is 192 at Vdd = 0.5 V and 397 at Vdd = 1 V, and it can approach 1000 (2670) at Vdd = 2 V (4 V), the highest ever achieved in MoS2 inverters (see Supplementary Fig. 11). Note that the rail-to-rail operations could be realized by further optimizing the circuit design of the FET units45, combing p-type FETs as building blocks46 or introducing doping techniques47. As can be seen in Fig. 3e, our MoS2 inverters have ultra-high gains and reliable outputs within the sub-1V supply voltage zone, as compared with other flexible inverters or rigid inverters based on 2D materials (the reference data points acquired from Supplementary Table 4). The ultra-high voltage gain is enabled by the strong gate controllability, while the trip point is mainly determined by the Vth distribution in our MoS2 TFTs. We also analyzed the individual TFT unit within an inverter (Supplementary Fig. 12) with intrinsic gains48 (defined as Ai = gm/gd) from 103 to 104, where gm and gd are the transconductance and output conductance of the TFT. Through monitoring the channel current of an inverter, the MoS2 TFT unit works mainly at the deep-subthreshold regime with ultra-low current densities. The calculated maximum output power of an inverter is 10.3 pW·μm−1, at the same level as an oxide semiconductor inverter32; and the quiescent power is below 0.1 pW·μm−1 at Vdd = 1 V (see Supplementary Table 5 for power consumption comparisons).

Typical output characteristics of ML-MoS2 logic NAND, NOR, AND gates are also shown in Fig. 3f. 0.5 V pulses of VA and VB with 1 s delay are used as input signals, where 0.5 V for the logic ‘1’ and 0 V for the logic ‘0’. All logic gates have correct Boolean output functionalities with a low supply voltage Vdd = 0.5 V.

In addition to logic gates and inverters, flexible ML-MoS2 ROs with various number of stages were also fabricated to demonstrate the reliability for low voltage operations. Figure 4a shows the optical microscope image of 11-stage ROs which integrate cascading eleven inverters and an additional inverter as the output buffer for measurements. The corresponding schematic circuit with three terminal electrodes of Vdd, Vss, and Vout is shown in Fig. 4b. Figure 4c shows the stable electrical output signals of an 11-stage RO at supply voltage Vdd from 0.3 V to 1 V (Vss terminal is grounded). Such low-driving voltages are facilitated from the small trip point of logic inverters. In contrast, if negative voltages are applied on the Vss terminal while the Vdd terminal is grounded, the RO could output negative signals starting from Vss = −0.4 V, as the swing threshold voltages of logic inverters shift negatively with the decreasing the operation voltages of Vss or Vdd terminal (Supplementary Fig. 11c, d).

a, b Optical image and schematic circuit diagram of 11-stage ROs. Scale bar, 200 μm. Vdd, or Vss, power supply voltages applied on drain or source electrodes. c Output signals of an 11-stage RO operated with sub-1 V supply voltages from 0.3 V to 1 V. d Output signals of 3-stage, 5-stage and 11-stage ROs operated at Vdd = 5 V. The output oscillation frequency increases by decreasing the stage number. e Summarized output frequencies of ROs as a function of Vdd from 0.3 V to 5 V. The output oscillation frequency increases with supply voltages. f Comparisons of propagation stage delay time as well as supply voltages with literature works. Detailed parameters are listed in Supplementary Table 6.

Generally, the output amplitude increases with the supply voltages and the oscillation frequency (f) decreases with the number of stages. Figure 4d shows the maximum output oscillation signals of 3-, 5- and 11-stage ROs operated at Vdd = 5 V. The ROs have reliable outputs with supply voltages varying from 0.3 V to 5 V (Fig. 4e). The maximum f is 24.8, 14.29, and 6.7 MHZ for 3-, 5- and 11-stage ROs, respectively. The corresponding propagation stage delay time (τpd = 1/2Nf, where N is RO stage number) at Vdd = 5 V is 6.7, 7.0, and 6.8 ns for 3-, 5-, and 11-stage ROs, respectively. Compared with previous flexible ROs fabricated from other 2D materials, organic, oxides or CNTs, our ROs locate at the preferred conner with the low driving voltages (sub-1 V) and fast propagation stage delay time (Fig. 4f). Note that, in this work, the parasitic capacitance from the overlapping region between the contact electrodes/additional outer MoS2 region with the gate is detrimental to high-frequency operation. The typical channel length/width of TFT unit is 1 μm/3 μm for ROs, and more device details and parasitic capacitance optimization is demonstrated in Supplementary Fig. 13. A typical real-time outputs of oscillating RO is included in the Supplementary Movie to show the stable operation.

Finally, we performed bending tests of the flexible ML-MoS2 ICs. As an example, here we show results from flexible MoS2 TFTs and 5-stage RO in Supplementary Figs. 14–17. On/off ratios as well as field-effect mobilities of individual TFTs could be well-preserved under a minimum bending radius (R = 2.4 mm). Under such bending, either along the X- or Y- direction, the 5-stage RO exhibits stable outputs without obvious degradations. The excellent mechanical flexibility and endurance, reliable electrical outputs of ROs, and high device yield indicate the good device performances and uniformity of our devices fabricated on flexible substrates; and the lowest operation supply voltage indicates the potential for low-power electronic applications.

Discussion

We developed an ultra-thin high-κ dielectric on metal gate technology for ML-MoS2 TFTs. Benefiting from the high-quality ML-MoS2 wafers as well as ohmic contacts, our ML-MoS2 TFTs could be tuned to high carrier density of 5.15 × 1013 cm−2 and allow a high current capacity of 936 μA·μm−1 at Vds = 1.5 V with sharp SS of 75 mV·dec−1, positive threshold voltages, negligible hysteresis, and ultra-low leakage currents. Large-area flexible TFTs and ICs show excellent spatial uniformity and a high device yield of >96% with fully functional inverters, logic gates, and ring oscillators working reliably under supply voltages below 1 V. The power consumption of an inverter can be as low as 10.3 pW·μm−1 at Vdd = 1 V. Besides, both the voltage gains of inverters and the propagation delay time of ROs we achieved are record-high values against previous flexible devices. Our results suggest that ML-MoS2 is a very competitive channel material in flexible ICs for both high performance and low power applications.

Methods

Growth of high-quality ML-MoS2 films

The growth was carried out in a CVD system using S (Alfa, 99.5%, 8 g) and MoO3 (Alfa, 99.9995%, 30 mg) powder as reaction sources. 4-inch c-plane sapphire wafers were used as substrates. In order to achieve large domain sizes, we intended to reduce the nucleation density during the growth process and elongate the growth time accordingly. The nucleation density of MoS2 was reduced by using higher oxygen flow rate for MoO3 source and reducing the Mo-source flux by lowering its evaporation temperature, increasing the distance between the Mo-source and sapphire substrate. During the growth, carrier gases of Ar (40 sccm) and Ar (240 sccm)/O2 (10 sccm) were fluxed for S power and MoO3 individually and the pressure in the chamber is ~1 Torr; temperatures were hold at 130 °C, 530 °C, and 930 °C for the S-, MoO3-source and substrate; and the growth process lasts usually about 50 min. Supplementary Fig. 2 demonstrates an optical image of high-quality 4-inch ML-MoS2 wafer with large domain sizes between 200 μm and 500 μm. These domains are well-stitched together to form a continuous film with 100% coverage.

Deposition of High-κ dielectric layers

ALD of HfO2 on Ti/Au/Ti (1 nm/5 nm/1 nm) local metal gates were carried out by Savannah-100 system (Cambridge NanoTech. Inc.) with H2O and tetrakis dimethylamino hafnium (TDMAH) as precursors. Prior to the deposition process, we used O2 plasma to treat the Ti/Au/Ti electrode surface by reactive ion etching (RIE) to oxidize the surface Ti layer. The oxidized layer (TiO2-x) acts as a buffer layer for dense high-κ dielectrics deposition. During the deposition, 20 sccm high-purity nitrogen was flowed as the carrier and purge gas; the reactor pressure was ~3 Torr; and the TDMAH precursor was heated to 75 °C. The deposition temperature is 110 °C or 150 °C for flexible samples, and 200 °C for rigid samples. The pulse and reaction time was 0.015/0.15 and 60/60 s for TDMAH/H2O precursors with deposition rate around 1 Å per cycle.

Device fabrications and measurements

TFTs and logic devices were fabricated via standard microfabrication processes such as e-beam lithography or UV lithography, oxygen RIE, e-beam evaporation and lifting-off. Transfer of ML-MoS2 films from sapphire to target substrates were assisted by wet etching in KOH solution (1 Mol/L, 110 °C). The process is illustrated in Supplementary Fig. 3. Au contact electrodes (10–15 nm) with clean interfaces were fabricated by e-beam evaporation with an ultra-low deposition rate of ~0.01 Å·s−1. All the electrical measurements were carried out in a Janis probe station at a base pressure of 10−6 Torr with an Agilent semiconductor parameter analyzer (B1500, high resolution modules) and Agilent digital oscilloscope (DSO-X 3054 A) at room temperature.

STEM characterizations

The cross-sectional STEM characterizations were carried out by an aberration corrected JEOL ARM 300 F transmission electron microscope operated at 300 kV.

Data availability

The Source Data underlying the figures of this study are available at https://doi.org/10.6084/m9.figshare.22776989. All raw data generated during the current study are available from the corresponding authors upon request.

References

Wu, W. et al. Piezoelectricity of single-atomic-layer MoS2 for energy conversion and piezotronics. Nature 514, 470–474 (2014).

Myny, K. The development of flexible integrated circuits based on thin-film transistors. Nat. Electron. 1, 30–39 (2018).

Park, Y. J. et al. All MoS2-based large area, skin-attachable active-matrix tactile sensor. ACS nano 13, 3023–3030 (2019).

Zhang, X. et al. Two-dimensional MoS2-enabled flexible rectenna for Wi-Fi-band wireless energy harvesting. Nature 566, 368–372 (2019).

Dai, Y. et al. Stretchable transistors and functional circuits for human-integrated electronics. Nat. Electron. 4, 17–29 (2021).

Kaltenbrunner, M. et al. An ultra-lightweight design for imperceptible plastic electronics. Nature 499, 458–463 (2013).

Gao, W. et al. Fully integrated wearable sensor arrays for multiplexed in situ perspiration analysis. Nature 529, 509–514 (2016).

Wang, S. et al. Skin electronics from scalable fabrication of an intrinsically stretchable transistor array. Nature 555, 83–88 (2018).

Kim, D. H. et al. Stretchable and foldable silicon integrated circuits. Science 320, 507–511 (2008).

Shahrjerdi, D. & Bedell, S. W. Extremely flexible nanoscale ultrathin body silicon integrated circuits on plastic. Nano Lett 13, 315–320 (2013).

Fortunato, E., Barquinha, P. & Martins, R. Oxide semiconductor thin-film transistors: a review of recent advances. Adv. Mater. 24, 2945–2986 (2012).

Papadopoulos, N. P. et al. Toward temperature tracking with unipolar metal-oxide thin-film SAR C-2C ADC on plastic. IEEE J Solid-State Circuits 53, 2263–2272 (2018).

Cao, Q. et al. Medium-scale carbon nanotube thin-film integrated circuits on flexible plastic substrates. Nature 454, 495–500 (2008).

Sun, D. M. et al. Flexible high-performance carbon nanotube integrated circuits. Nat. Nanotechnol. 6, 156–161 (2011).

Tang, J. et al. Flexible CMOS integrated circuits based on carbon nanotubes with sub-10 ns stage delays. Nat. Electron. 1, 191–196 (2018).

Xiang, L. et al. Low-power carbon nanotube-based integrated circuits that can be transferred to biological surfaces. Nat. Electron. 1, 237–245 (2018).

Long, G. et al. Carbon nanotube-based flexible high-speed circuits with sub-nanosecond stage delays. Nat. Commun. 13, 6734 (2022).

Radisavljevic, B. et al. Single-layer MoS2 transistors. Nat. Nanotechnol. 6, 147–150 (2011).

Yoon, Y., Ganapathi, K. & Salahuddin, S. How good can monolayer MoS2 transistors be? Nano Lett 11, 3768–3773 (2011).

Fiori, G. et al. Electronics based on two-dimensional materials. Nat. Nanotechnol. 9, 768–779 (2014).

Akinwande, D., Petrone, N. & Hone, J. Two-dimensional flexible nanoelectronics. Nat. Commun. 5, 5678 (2014).

Kang, K. et al. High-mobility three-atom-thick semiconducting films with wafer-scale homogeneity. Nature 520, 656–660 (2015).

Shinde, S. M. et al. Surface-functionalization-mediated direct transfer of molybdenum disulfide for large-area flexible devices. Adv. Funct. Mater. 28, 1706231 (2018).

Li, N. et al. Large-scale flexible and transparent electronics based on monolayer molybdenum disulfide field-effect transistors. Nat. Electron. 3, 711–717 (2020).

Conti, S. et al. Low-voltage 2D materials-based printed field-effect transistors for integrated digital and analog electronics on paper. Nat. Commun. 11, 3566 (2020).

Liu, Y. et al. Promises and prospects of two-dimensional transistors. Nature 591, 43–53 (2021).

Chang, H. Y. et al. High-performance, highly bendable MoS2 transistors with high-k dielectrics for flexible low-power systems. ACS Nano 7, 5446–5452 (2013).

Desai, S. B. et al. MoS2 transistors with 1-nanometer gate lengths. Science 354, 99–102 (2016).

Xie, L. et al. Graphene-contacted ultrashort channel monolayer MoS2 transistors. Adv. Mater. 929, 1702522 (2017).

Daus, A. et al. High-performance flexible nanoscale transistors based on transition metal dichalcogenides. Nat. Electron. 4, 495–501 (2021).

Wang, Q. H. et al. Electronics and optoelectronics of two-dimensional transition metal dichalcogenides. Nat. Nanotechnol. 7, 699–712 (2012).

Lee, S. & Nathan, A. Subthreshold Schottky-barrier thin-film transistors with ultralow power and high intrinsic gain. Science 354, 302–304 (2016).

Yu, H. et al. Wafer-scale growth and transfer of highly-oriented monolayer MoS2 continuous films. ACS nano 11, 12001–12007 (2017).

Wang, Q. et al. Wafer-scale highly oriented monolayer MoS2 with large domain sizes. Nano Lett 20, 7193–7199 (2020).

Li, T. et al. Epitaxial growth of wafer-scale molybdenum disulfide semiconductor single crystals on sapphire. Nat. Nanotechnol. 16, 1201–1207 (2021).

Kim, K. S. et al. Non-epitaxial single-crystal 2D material growth by geometric confinement. Nature 614, 88–94 (2023).

Si, M. et al. Steep-slope hysteresis-free negative capacitance MoS2 transistors. Nat. Nanotechnol. 13, 24–28 (2018).

Wang, Y. et al. Van der Waals contacts between three-dimensional metals and two-dimensional semiconductors. Nature 568, 70–74 (2019).

Shen, P. C. et al. Ultralow contact resistance between semimetal and monolayer semiconductors. Nature 593, 211–217 (2021).

Kim, H. G. & Lee, H. B. R. Atomic layer deposition on 2D materials. Chem. Mater. 29, 3809–3826 (2017).

Li, W. et al. Uniform and ultrathin high-κ gate dielectrics for two-dimensional electronic devices. Nat. Electron. 2, 563–571 (2019).

Zhu, Y. et al. Monolayer molybdenum disulfide transistors with single-atom-thick gates. Nano Lett 18, 3807–3813 (2018).

Moore, M. International Roadmap for Devices and Systems 2020 Edition. https://irds.ieee.org/images/files/pdf/2020/2020IRDS_MM.pdf (2020).

Smets, Q. et al. Sources of variability in scaled MoS2 FETs. In 2020 IEEE International Electron Devices Meeting (IEDM) 3.1.1–3.1.4 (IEEE, 2020).

Wachter, S. et al. A microprocessor based on a two-dimensional semiconductor. Nat. Commun. 8, 14948 (2017).

Guo, E. et al. Integrated complementary inverters and ring oscillators based on vertical-channel dual-base organic thin-film transistors. Nat. Electron. 4, 588–594 (2021).

Tian, J. et al. Rail-to-rail MoS2 inverters. ACS Appl. Electron. Mater 4, 2636–2640 (2022).

Li, S. et al. Nanometre-thin indium tin oxide for advanced high-performance electronics. Nat. Mater. 18, 1091–1097 (2019).

Acknowledgements

This work was supported by the National Key Research and Development Program (Grant No. 2021YFA1202900, 2021YFA1400502), the Strategic Priority Research Program of Chinese Academy of Sciences (CAS, grant No. XDB30000000), the National Science Foundation of China (NSFC, grant No. 61888102, 11834017, 61734001, and 62122084), and the Key-Area Research and Development Program of Guangdong Province (Grant No. 2020B0101340001). The authors also thank Prof. Aizi Jin, Prof. Tianzhong Yang and Dr. Xiao Guo in IOP-CAS for the assistance on short channel device fabrications and CS-STEM sample preparations.

Author information

Authors and Affiliations

Contributions

J.Ta. fabricated the devices and carried out the electrical measurements with the help of J.Ti., N.L., Y.P., Xiu.L., Y.Z., C.H., B.H., and Y.C. J.Ta., J.Ti., S.W., J.L., Y.G., and Da.S. performed the high-κ dielectric deposition. Q.W. performed the growth of ML-MoS2 films. Xia.L. J.Ta., Y.J. and X.B. prepared the TEM samples and performed the TEM characterizations. G.Z., Do.S., W.Y., R.Y., and L.D. supervised the project. J.Ta. and G.Z. analyzed data and wrote the manuscript. All authors discussed and commented on the manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Nature Communications thanks Alwin Daus for their contribution to the peer review of this work. A peer review file is available.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Tang, J., Wang, Q., Tian, J. et al. Low power flexible monolayer MoS2 integrated circuits. Nat Commun 14, 3633 (2023). https://doi.org/10.1038/s41467-023-39390-9

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41467-023-39390-9

This article is cited by

-

Room temperature photosensitive ferromagnetic semiconductor using MoS2

npj Spintronics (2024)

-

Epitaxy of wafer-scale single-crystal MoS2 monolayer via buffer layer control

Nature Communications (2024)

-

Silicon-processes-compatible contact engineering for two-dimensional materials integrated circuits

Nano Research (2023)

-

p-Type Two-Dimensional Semiconductors: From Materials Preparation to Electronic Applications

Nano-Micro Letters (2023)

-

Batch fabrication of MoS2 devices directly on growth substrates by step engineering

Nano Research (2023)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.