Abstract

Oxide semiconductors have been investigated as channel layers for thin film transistors (TFTs) which enable next-generation devices such as high-resolution liquid crystal displays (LCDs), organic light emitting diode (OLED) displays, flexible electronics, and innovative devices. Here, high-performance and stable Ga-Sn-O (GTO) TFTs were demonstrated for the first time without the use of rare metals such as In. The GTO thin films were deposited using radiofrequency (RF) magnetron sputtering. A high field effect mobility of 25.6 cm2/Vs was achieved, because the orbital structure of Sn was similar to that of In. The stability of the GTO TFTs was examined under bias, temperature, and light illumination conditions. The electrical behaviour of the GTO TFTs was more stable than that of In-Ga-Zn-O (IGZO) TFTs, which was attributed to the elimination of weak Zn-O bonds.

Similar content being viewed by others

Introduction

Oxide semiconductor materials such as In-Ga-Zn-O (IGZO)1,2,3,4, In-Sn-Zn-O (ITZO)5,6, In-Ga-O (IGO)7, and In-Sn-O (ITO)8 have several advantages as active layer of thin film transistors (TFTs) such as steep subthreshold swing (S factor), transparency, and extremely low leak current in off state when compared to conventional semiconductors such as hydrogenated amorphous silicon (a-Si:H)9 and polycrystalline silicon10. In addition, oxide TFTs have high field effect mobility (μFE) and can be easily fabricated on large-area substrates by deposition processes with low cost, low toxicity, and low risk of explosion, such as radiofrequency (RF) or direct current (DC) magnetron sputtering. These techniques are used in the TFT fabrication processes to deposit IGZO as semiconductor, ITO as the transparent electrodes for displays, and metallic materials (Cr, Mo, and Al) for electrodes. The fabrication processes for oxide semiconductors can be easily integrated into or replace conventional TFT processes, such as photolithography and etching. Hence, not only information displays but also novel devices have been proposed such as memories11, processors, and other electronic elements12. However, IGZO, ITZO, IGO, and ITO include In in the matrix which is associated with high fabrication costs as In is a rare metal with few mining sites13 and is hence expensive. On the other hand, the In-free oxide semiconductor materials such as ZnO14,15,16,17,18, Al-Zn-Sn-O (AZTO)19, Zn-Sn-O (ZTO)20, ZnON21 include Zn, which is thought to be the reason of the instability of devices with forming the weak Zn-O bond22. The electrical characteristics and those stability of In-free TFTs were not enough for application to the novel devices. In addition, multi-metallic materials (especially IGZO) are difficult to mass produce because the stoichiometry of the deposited films can be different to that of the sputtering target due to preferential sputtering of some elements2. Sputtering targets can be of poor quality due to low crystallinity or incomplete oxidation of compounds23, which may reduce device performance. Furthermore, there are many defects in the semiconductor films4,24,25,26,27,28,29,30,31, and it is difficult to control the density of oxygen vacancies induced during the deposition32,33,34. Therefore, new semiconductor materials that do not use rare metals and consist of fewer elements are being explored.

In this paper, we first report a stable TFT with a high μFE that incorporate Ga-Sn-O (GTO) as the amorphous and transparent oxide semiconductor. This material is a dual metallic oxide without rare metals such as In. The stability of the GTO TFT was evaluated under various stress conditions and compared to that of IGZO TFTs.

Results and Discussion

Abundance in the Earth’s upper continental crust

The abundance of Ga and Sn in the Earth’s upper continental crust is 18 ppm and 2.2 ppm, respectively, much higher than that of In (0.25 ppm)13, as shown in Fig. 1a. Therefore, substituting Sn for In is a reasonable countermeasure for avoiding the use of rare earth metals. Moreover, In and Sn have similar electronic structures and electrical properties. The high μFE observed for amorphous IGZO TFTs has been attributed to the electron path formed by the broad In 5 s orbital. In with atomic number 49 has an electronic structure in ground state; 1s22s22p63s23p63d104s24p64d105s25p. On the other hand, Sn with atomic number 50, the next element after In in the periodic table, has a similar electronic structure in ground state; 1s22s22p63s23p63d104s24p64d105s25p2 as shown in Fig. 1b35. As a result, In3+ ions in IGZO and Sn4+ ions in GTO have the same electronic structure of 1s22s22p63s23p63d104s24p64d10. Therefore, a high μFE is expected for GTO TFTs because the 5 s orbital of Sn serves as a path for current flow, similar to the 5 s orbital of In as shown in Fig. 1b1.

, and current path formed by metallic ions. (a) The relative abundance of the elements in the Earth’s upper continental crust is indicated by the green circles and the absolute values (ppm) are shown13. Ga and Sn as metallic elements of GTO are surrounded by red line, and In, Ga, Zn, elements of IGZO are surrounded by dashed blue line. (b) 5 s orbitals are indicated by red circles, 5p orbitals are indicated by orange ovals, electrons are indicated by yellow particles. In3+ ions and Sn4+ ions have the same electronic structure, and the path of electrons in IGZO and GTO can be formed by 5 s orbital without electrons described with red circles.

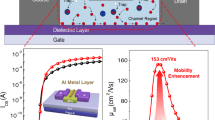

Electrical characteristic of the GTO TFT

Figure 2 shows the drain current (Ids) as a function of the gate voltage (Vgs) from −30 to 30 V with a 0.1 V step, and fixed drain voltage (Vds) of 0.1 V, from 5 to 30 V with a 5 V step. The ratio between the on current of the TFT (Ion) at Vgs = 30 V and the off current (Ioff) at Vgs = −10 V, (Ion/Ioff) was over 108. The threshold voltage, Vth = −1.49 V, subthreshold swing, S = 0.33 V/dec where S = dVgs/dlogIds, and the highest μFE of 25.6 cm2/V·s, were achieved for the GTO TFT in linear region at Vgs = 29.5 V and Vds = 0.1 V, which values were comparable to those observed for IGZO TFTs36 and ITZO TFTs5,6. In the saturation region, the value of μFE was slightly lower than that of linear region. High μFE of linear region would be due to the path of electron formed in the conduction band at high Vgs and low Vds, whereas lower μFE of saturation region would be because the route of electron was partially formed by percolation path in pinch off region at high Vds. In addition, the saturation characteristics of GTO TFTs were excellent, and the TFT characteristics did not deteriorate, even after measurement at high voltages of Vgs = 30 V and Vds = 30 V, as shown in Fig. 2b. The abovementioned excellent performances show that the GTO TFTs are suitable for use in next-generation displays such as 8 K ultra-high-definition televisions (UHDTV), LCD, and OLED37. The other GTO TFTs with different composition ratio from Ga: Sn = 1: 3 were fabricated, however, the best TFT performance was achieved with the current composition ratio.

(a), transfer characteristics (drain current vs. gate voltage for various drain voltages) with left axis in log scale and right axis in linear scale, respectively, and (b) output characteristics (drain current vs. drain voltage for various gate voltages) in linear scale. The electrical characteristics of GTO TFT was excellent with low off current in negative gate voltage region in transfer characteristics, and high on current in positive gate voltage. The saturation characteristics in high drain voltage were clearly observed in output characteristics.

Optical absorbance and XRD intensity of the GTO film

Figure 3a shows the optical absorbance of a GTO thin film deposited on a quartz substrate. The inset shows a photograph of the sample laid over printed text in red, green, and blue, showing the good transparency of the film in the visible wavelength range. The absorbance of the GTO thin film was lower than 20% at a wavelength of 300 nm and approximately zero above 380 nm. Figure 3b shows the XRD pattern of GTO thin film deposited on a quartz substrate. The structure of GTO thin film is amorphous, because the no diffraction peak was observed in the XRD pattern.

(a) optical absorbance as a function of wavelength. The inset is a photograph of a GTO thin film deposited on a quartz glass substrate put on the top of a printed paper, showing the transparency of the thin film. (b) XRD pattern showing amorphous structure of GTO thin film deposited on a quartz substrate.

Characteristic stability of the GTO TFT

A major drawback of conventional amorphous oxide semiconductors is the poor stability of TFTs under the driving conditions of devices38. In order to investigate the stability of the GTO TFTs, we performed accelerated operating tests such as the positive bias stress (PBS), positive bias temperature stress (PBTS), positive bias illumination stress (PBIS), negative bias stress (NBS), negative bias temperature stress (NBTS), and negative bias illumination stress (NBIS) tests.

Figure 4 shows the Ids-Vgs characteristics of a GTO TFT under the NBIS test conditions. Generally, amorphous oxide semiconductor TFTs have poor Ids-Vgs behaviour under NBIS testing36. However, only a negative shift of 4.3 V in Vgs was observed after applying NBIS conditions of a gate voltage of −20 V under light illumination for 3600 s. Excellent TFT characteristics were maintained even after the NBIS tests, such as low Ioff values in the negative Vgs region and high Ion values in the high Vgs region. In addition, no degradation in the S factor was observed in the subthreshold region of Vgs from around −10 V to 5 V after the NBIS test. Therefore, we can conclude that the no trap state was generated close to the conduction band and NBIS effects were due to the capturing of fixed charges in the insulator, similar to the reported effect for IGZO TFT38. This effect is different from the hypothesis such as elimination of dangling bonds with O2 annealing39, and defect formation in semiconductor layer or interface between the semiconductor and gate insulator40,41,42. The shift in the electrical characteristics is due to a similar mechanism to that known for IGZO TFTs; holes from electron-hole pairs excited by the light and heat are transported from the back channel of the semiconductor to the gate surface and are captured close to the interface between the gate insulator and the semiconductor38.

Figure 5 shows the stability of GTO TFT under the PBS, PBTS, PBIS, NBS, NBTS, and NBIS tests without passivation. The stress conditions are shown in the table in Fig. 5. The shifts of the turn-on voltage, which is defined as Vgs for Ids = 1 × 10−9 A, (ΔV) of all stress tests were less than that of NBIS tests. These results for NBTS and NBIS testing of GTO are better than those for IGZO TFTs, where the shift was over 10 V in the negative direction at 1000 s36. Therefore, it can be generally concluded that the stability of TFTs fabricated using GTO is better than that observed for IGZO. It was reported in the literature that weak bonds were formed between the Zn and O in IGZO22. As GTO does not include Zn in the matrix, we expect that the improved stability of the GTO TFT may be due to the absence of such weak bonds, because the enthalpy (heat) of formation of ZnO is smaller than Ga2O3 and SnO2, which means that the bonds in GTO is more stable than ZnO in IGZO. Therefore, the GTO lattice is expected to be stable during plasma processes, such as sputtering and CVD, for deposition of passivation films and dry etching process. In addition, the optical band gap of a GTO film obtained from a Tauc plot was 3.12 eV, which is larger than silicon-based semiconductors, and comparable to other oxide semiconductors, such as IGZO, ZnO, SnO2 and Ga2O3. This means that the generation of holes is limited. Hence, highly stable TFT characteristics are expected for GTO TFTs, because the large band gap means that the number of holes generated by light illumination is limited; the holes are the main reason for the NBIS instability of oxide semiconductor TFTs38. Moreover, the GTO is amorphous, and hence, large area uniformity is expected during the device fabrication process, because the amorphous oxide materials are thought to be more stable against grain boundaries formed in crystalline oxide semiconductors. The path of electrons in the GTO thin film is formed by the 5 s orbital of Sn ions, which is largely spreading in the matrix as shown in Fig. 1b. The uniform shape of the 5 s orbital maintains the current path in random direction of the bond between the elements in amorphous GTO matrix which was confirmed by XRD pattern. The role of Ga in GTO is similar to Ga and Zn in IGZO, which stabilize the amorphous structure with Coulomb potential. Zn stabilizes the amorphous structure in IGZO, however, Zn element is not needed in GTO for stabilizing the amorphous GTO TFT characteristics. In addition, improvement in the μFE and stability of GTO TFTs can be expected by appropriate passivation or treatment of the back channel and optimization of the fabrication process applied for IGZO TFTs25,43,44.

Shifts in the turn-on voltage, which is defined as Vgs for Ids = 1 × 10−9. A at the subthreshold region, (ΔV) at the subthreshold region are shown as a function of stress time under conditions of positive bias stress (PBS), positive bias temperature stress (PBTS), positive bias illumination stress (PBIS), negative bias stress (NBS), negative bias temperature stress (NBTS), and negative bias illumination stress (NBIS). The original state refers to the conditions before the stress test. The shift of the GTO TFT characteristics was largest for NBIS test.

Conclusion

High field effect mobility TFT with a low S factor was prepared using GTO, where the rare earth In was replaced by Sn. The stability of the GTO TFT without a passivation film under various accelerated operating conditions was significantly higher than that of equivalent IGZO TFTs. Although we compared the IGZO and GTO TFTs fabricated in our laboratory just for evaluation of the materials themselves, because TFT characteristics are influenced by the treatment of backchannel such as passivation materials and methods25,44,45 and surface treatment36,43, the effective treatments for IGZO TFT can also be effective for GTO TFT. We propose such GTO TFTs as key devices suitable for use in next-generation technologies such as displays, power devices, and artificial intelligence devices such as neural networks.

Methods

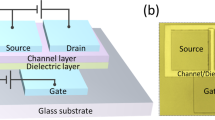

Samples

The fabricated GTO TFTs have a structure with a bottom gate and top contact. We used the same structure as that of previously reported IGZO TFTs36 in order to evaluate the compatibility of GTO with the other oxide semiconductor materials and compare their performance under the same conditions. The GTO active layers were deposited by RF magnetron sputtering using a sintered GTO ceramic target (99.99%, Ga:Sn = 1:3 in atomic ratio). The vacuum chamber was evacuated to 1 × 10−4 Pa and the sputtering gas pressure was controlled using a vacuum valve to introduce Ar and O2 gas into the chamber at a fixed flow rate of Ar:O2 = 20:1 sccm determined by a mass flow controller. The GTO was deposited on Si wafers (p-type; 0.01 Ω·cm; 50 mm in diameter) for use as gate electrodes in the TFT which had a 150 nm thermal oxide (SiO2) layer as the gate insulator. Source and drain (S/D) electrodes of Ti (20 nm in thickness) and Au (20 nm in thickness), respectively, were deposited using thermal evaporation on the GTO active layer. Both the semiconductor layer and S/D electrodes were patterned using stainless steel shadow masks set on top of the substrates. Post annealing was performed in air at 350 °C for 1 h using an annealing furnace. No passivation layer was deposited on the back channel of the TFTs36 to avoid undesired effects from plasma processes such as CVD for the fabrication of passivation films and dry etching processes43.

Characterisation

Electrical properties such as Ids-Vgs and Ids-Vds of GTO TFTs were measured in air at around 25 °C using a semiconductor parameter analyser (Agilent 4156 C). TFT parameters such as μFE, S factors, and Vth were calculated from TFT theory, such as Ids = μFE ci(W/L)(Vgs − Vth)Vds, where, ci is the capacitance of the TFT of unit area (F/cm2), W/L is the ratio of the channel width to the channel length defined between the S/D electrodes. The stability of the GTO TFTs was evaluated under accelerated operating conditions of devices, including voltage, temperature, and light illumination stresses using conditions of Vg = 20 V/ −20 V for positive or negative bias, respectively, 60 °C, and irradiation from an white LED lamp with wavelength from 450 nm to 780 nm. By combining these conditions, we evaluated the stability of the material under positive bias stress (PBS), positive bias temperature stress (PBTS), positive bias illumination stress (PBIS), negative bias stress (NBS), negative bias temperature stress (NBTS), and negative bias illumination stress (NBIS). The optical absorbance (A %) was obtained from the transmittance (T %) and reflectance (R %) using A = (100 − (R + T)), measured using a spectrometer from the ultraviolet to visible range (UV-VR) (300 nm to 800 nm). XRD pattern in 2θ/θ scan of GTO thin film deposited on a quartz substrate was measured with Rigaku SmartLab X-ray diffractometer (Cu Kα radiation).

Additional Information

How to cite this article: Matsuda, T. et al. Rare-metal-free high-performance Ga-Sn-O thin film transistor. Sci. Rep. 7, 44326; doi: 10.1038/srep44326 (2017).

Publisher's note: Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

References

Nomura, K. et al. Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors. Nature 432, 488–492 (2004).

Yabuta, H. et al. High-mobility thin-film transistor with amorphous InGaZnO4 channel fabricated by room temperature rf-magnetron sputtering. Appl. Phys. Lett. 89, 112123 (2006).

Hosono, H. Ionic amorphous oxide semiconductors: Material design, carrier transport, and device application. J. Non. Cryst. Solids 352, 851–858 (2006).

Kamiya, T., Nomura, K. & Hosono, H. Present status of amorphous In–Ga–Zn–O thin-film transistors. Sci. Technol. Adv. Mater 11, 044305 (2010).

Fukumoto, E. et al. High-mobility oxide TFT for circuit integration of AMOLEDs. J. Soc. Inf. Disp. 19, 867–872 (2011).

Tomai, S. et al. High-Performance Thin Film Transistor with Amorphous In2O3-SnO2-ZnO channel layer. Jpn. J. Appl. Phys. 51, 03CB01 (2012).

Ebata, K. et al. High-mobility thin-film transistors with polycrystalline In-Ga-O channel fabricated by DC magnetron sputtering. Appl. Phys. Express 5, 011102 (2012).

Miyasako, T., Senoo, M. & Tokumitsu, E. Ferroelectric-gate thin-film transistors using indium-tin-oxide channel with large charge controllability. Appl. Phys. Lett. 86, 1–3 (2005).

Street, R. A. Hydrogenated amorphous silicon. (Cambridge Univ. Press, 1991).

Kagan, C. R. & Andry, P. Thin-film transistors. (Marcel Dekker, 2003).

Suresh, A., Novak, S., Wellenius, P., Misra, V. & Muth, J. F. Transparent indium gallium zinc oxide transistor based floating gate memory with platinum nanoparticles in the gate dielectric. Appl. Phys. Lett. 94, 123501 (2009).

Kamiya, T. & Hosono, H. Material characteristics and applications of transparent amorphous oxide semiconductors. NPG Asia Mater. 2, 15–22 (2010).

Haxel, G. B., Hedrick, J. B. & Orris, G. J. Rare Earth Elements — Critical Resources for High Technology. United States Geol. Surv. Fact Sheet 87, 4 (2002).

Ohya, Y., Niwa, T., Ban, T. & Takahashi, Y. Thin film transistor of ZnO fabricated by chemical solution deposition. Jpn. J. Appl. Phys. 40, 297–298 (2001).

Masuda, S. et al. Transparent thin film transistors using ZnO as an active channel layer and their electrical properties. J. Appl. Phys. 93, 1624–1630 (2003).

Hoffman, R. L., Norris, B. J. & Wager, J. F. ZnO-based transparent thin-film transistors. Appl. Phys. Lett. 82, 733–735 (2003).

Hirao, T. et al. High Mobility Top-Gate Zinc Oxide Thin-Film Transistors (ZnO-TFTs) for Active-Matrix Liquid Crystal Displays Digest of SID'06, 18–20 (2006).

Hirao, T. et al. Novel top-gate zinc oxide thin-film transistors (ZnO TFTs) for AMLCDs. J. Soc. Inf. Disp. 15, 17–22 (2007).

Jeong, J. K. et al. Impact of device configuration on the temperature instability of Al-Zn-Sn-O thin film transistors. Appl. Phys. Lett. 95, 1–4 (2009).

Heo, J., Kim, S. B. & Gordon, R. G. Atomic layer deposited zinc tin oxide channel for amorphous oxide thin film transistors. Appl. Phys. Lett. 101, 113507 (2012).

Ok, K. C., Jeong, H. J., Kim, H. S. & Park, J. S. Highly stable ZnON thin-film transistors with high field-effect mobility exceeding 50 cm2/Vs. IEEE Electron Device Lett. 36, 38–40 (2015).

Kamiya, T., Nomura, K. & Hosono, H. Subgap states, doping and defect formation energies in amorphous oxide semiconductor a-InGaZnO4 studied by density functional theory. Phys. Status Solidi Appl. Mater. Sci. 207, 1698–1703 (2010).

Huh, J. Y. et al. Effects of the composition of sputtering target on the stability of InGaZnO thin film transistor. Thin Solid Films 519, 6868–6871 (2011).

Hoffmann, R. C. et al. Molecular precursor derived and solution processed indium-zinc oxide as a semiconductor in a field-effect transistor device. Towards an improved understanding of semiconductor film composition. J. Mater. Chem. C 1, 2577–2584 (2013).

Nomura, K., Kamiya, T. & Hosono, H. Highly stable amorphous In-Ga-Zn-O thin-film transistors produced by eliminating deep subgap defects. Appl. Phys. Lett. 99, 53505 (2011).

Chen, C., Cheng, K.-C., Chagarov, E. & Kanicki, J. Crystalline In–Ga–Zn–O Density of States and Energy Band Structure Calculation Using Density Function Theory. Jpn. J. Appl. Phys. 50, 91102 (2011).

Matsuda, T., Furuta, M., Hiramatsu, T., Furuta, H. & Hirao, T. Crystallinity and resistivity of ZnO thin films with indium implantation and postannealing. J. Vac. Sci. Technol. A Vacuum, Surfaces, Film. 28, 135–138 (2010).

Kimura, M., Nakanishi, T., Nomura, K., Kamiya, T. & Hosono, H. Trap densities in amorphous- InGaZnO4 thin-film transistors. Appl. Phys. Lett. 92, 2006–2009 (2008).

Kimura, M., Kamiya, T., Nakanishi, T., Nomura, K. & Hosono, H. Intrinsic carrier mobility in amorphous In-Ga-Zn-O thin-film transistors determined by combined field-effect technique. Appl. Phys. Lett. 96, 98–101 (2010).

Kimura, M. et al. Extraction of trap densities in ZnO thin-film transistors and dependence on oxygen partial pressure during sputtering of ZnO films. IEEE Trans. Electron Devices 58, 3018–3024 (2011).

Matsuda, T. & Kimura, M. Comparison of defects in crystalline oxide semiconductor materials by electron spin resonance. J. Vac. Sci. Technol. A 33, 20601 (2015).

Ryu, B., Noh, H. K., Choi, E. A. & Chang, K. J. O-vacancy as the origin of negative bias illumination stress instability in amorphous In-Ga-Zn-O thin film transistors. Appl. Phys. Lett. 97, 22108 (2010).

Matsuda, T., Nishimoto, D., Takahashi, K., Ueno, T. & Kimura, M. ESR Evaluation of Damages Induced in InGaZnO4 with Plasma. In Proceedings of International Display Workshops/Asia Display 2012 557–558 (2012).

Matsuda, T., Nishimoto, D., Takahashi, K. & Kimura, M. Evaluation of damage in InGaZnO4 induced by plasma using electron spin resonance measurement Matching. Jpn. J. Appl. Phys. 3, 03CB03 (2014).

Steven Dutch. Scale Drawings of Atoms and Orbitals: Cesium Through Radon. Available at: https://www.uwgb.edu/dutchs/Petrology/ScaleAtomsCsRn.HTM.

Kojiri, T., Matsuda, T. & Kimura, M. Thermally enhanced threshold voltage shifts in amorphous In-Ga-Zn-O thin-film transistor. Jpn. J. Appl. Phys. 53, 125802 (2014).

Matsueda,Y. Required Characteristics of TFTs for Next Generation Flat Panel Display Backplanes. In The Proceedings of the 6th International Thin-Film Transistor Conference 314–317 (2010).

Nomura, K., Kamiya, T. & Hosono, H. Stability and high-frequency operation of amorphous In-Ga-Zn-O thin-film transistors with various passivation layers. Thin Solid Films 520, 3778–3782 (2012).

Ji, K. H. et al. Effect of high-pressure oxygen annealing on negative bias illumination stress-induced instability of InGaZnO thin film transistors. Appl. Phys. Lett. 98, 103509 (2011).

Ueoka, Y. et al. Density of States in Amorphous In-Ga-Zn-O Thin-Film Transistor under Negative Bias Illumination Stress. ECS J. Solid State Sci. Technol. 3, Q3001–Q3004 (2014).

Oh, H. et al. Photon-accelerated negative bias instability involving subgap states creation in amorphous In-Ga-Zn-O thin film transistor. Appl. Phys. Lett. 97, 183502 (2010).

Lee, K. H. et al. The effect of moisture on the photon-enhanced negative bias thermal instability in Ga-In-Zn-O thin film transistors. Appl. Phys. Lett. 95, 232106 (2009).

Koretomo, D., Toda, T., Matsuda, T., Kimura, M. & Furuta, M. Anomalous Increase in Field-Effect Mobility in In-Ga-Zn-O Thin-Film Transistors Caused by Dry-Etching Damage Through Etch-Stop Layer. IEEE Trans. Electron Devices 63, 2785–2789 (2016).

Furuta, M., Jiang, J., Hung, P., Toda, T. & Wang, D. Suppression of Negative Gate Bias and Illumination Stress Degradation by Fluorine-Passivated In-Ga-Zn-O Thin-Film Glass substrate. ECS J. Solid State Sci. Technol. 5, Q88–Q91 (2016).

Bermundo, J. P., Ishikawa, Y., Yamazaki, H., Nonaka, T. & Uraoka, Y. Highly Reliable Polysilsesquioxane Passivation Layer for a-InGaZnO Thin-Film Transistors. ECS J. Solid State Sci. Technol. 3, Q16–Q19 (2013).

Acknowledgements

We would like to thank Dr. Shigekazu Tomai from Idemitsu Kosan Co. Ltd., for helpful discussions regarding target preparation and TFT measurements. This work was partially supported by the MEXT Supported Program for the Strategic Research Foundation at Private Universities (S1311040), a JSPS Grant-in-Aid for Young Scientists (B) (No. 26870717), and a Grant-in-Aid for Scientific Research (C) (No. 16K06733).

Author information

Authors and Affiliations

Contributions

Tokiyoshi Matsuda conducted the research, contributed to the choice of GTO material, development of the TFT fabrication process, evaluation of the GTO thin films and TFTs, and writing the paper. Kenta Umeda fabricated and characterised the TFTs. Yuta Kato developed the GTO TFT fabrication process. Daiki Nishimoto carried out the deposition and evaluation of the films. Mamoru Furuta conducted the film evaluation. Mutsumi Kimura managed the research and laboratory, contributed to discussions about the TFT characteristics, and revised the paper.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing financial interests.

Rights and permissions

This work is licensed under a Creative Commons Attribution 4.0 International License. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in the credit line; if the material is not included under the Creative Commons license, users will need to obtain permission from the license holder to reproduce the material. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/

About this article

Cite this article

Matsuda, T., Umeda, K., Kato, Y. et al. Rare-metal-free high-performance Ga-Sn-O thin film transistor. Sci Rep 7, 44326 (2017). https://doi.org/10.1038/srep44326

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/srep44326

This article is cited by

-

Amorphous metal oxide semiconductor thin film, analog memristor, and autonomous local learning for neuromorphic systems

Scientific Reports (2021)

-

A Review on the Recent Advancements in Tin Oxide-Based Thin-Film Transistors for Large-Area Electronics

Journal of Electronic Materials (2020)

-

Memristive characteristic of an amorphous Ga-Sn-O thin-film device

Scientific Reports (2019)

-

Solution-processed amorphous gallium-tin oxide thin film for low-voltage, high-performance transistors

Science China Materials (2019)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.