Abstract

Paraelectrical tuning of a charge carrier density as high as 1013 cm−2 in the presence of a high electronic carrier mobility on the delicate surfaces of correlated oxides, is a key to the technological breakthrough of a field effect transistor (FET) utilising the metal-nonmetal transition. Here we introduce the Parylene-C/Ta2O5 hybrid gate insulator and fabricate FET devices on single-crystalline SrTiO3, which has been regarded as a bedrock material for oxide electronics. The gate insulator accumulates up to ~1013cm−2 carriers, while the field-effect mobility is kept at 10 cm2/Vs even at room temperature. Further to the exceptional performance of our devices, the enhanced compatibility of high carrier density and high mobility revealed the mechanism for the long standing puzzle of the distribution of electrostatically doped carriers on the surface of SrTiO3. Namely, the formation and continuous evolution of field domains and current filaments.

Similar content being viewed by others

Introduction

Aprominent feature of phase transitions in correlated electron systems is the nanoscale dynamics leading to future electronics such as switching devices and novel nonvolatile resistance-change memory applications1,2,3,4,5,6,7,8,9. In spite of the long-standing research, device prototypes remain limited mainly due to the absence of a method for a continuous (i.e., paraelectrical) and precise electrostatic control (gating) of a two dimensional (2D) charge carrier density  . Furthermore, oxygen and cation stoichiometry are fairly unstable in perovskite-type (ABO3) transition-metal oxides (TMOs)10. Deposition of dielectric oxides on the surface of ABO3 channel for gating inevitably results in such kind of defects, introducing randomness and eventually smearing the critical features of metal-insulator transitions11. In the face of these challenges, we have chosen to fabricate FET adopting single-crystalline SrTiO3 for the channel. This compound is a band insulator with a crystal structure characteristic of many TMO Mott insulators and becomes metallic by electron doping. SrTiO3 is an n-type wide-gap semiconductor with a band gap of 3.2eV. It is considered as a matrix for spintronic devices due to the unique configuration of the spin-precession vector at the surface and the absence of the Dresselhaus term. The surface of the single crystal can be atomically flat and is widely used as a substrate for correlated TMO thin films, making it preferable candidate to test the suitability of the reported gate insulator for future electronics. Identifying the technical methods and physical mechanism for paraelectric tuning of electronic conduction in two dimensional electron gases (2DEG) created at the surface of SrTiO3 is a problem of bursting interdisciplinary interest12.

. Furthermore, oxygen and cation stoichiometry are fairly unstable in perovskite-type (ABO3) transition-metal oxides (TMOs)10. Deposition of dielectric oxides on the surface of ABO3 channel for gating inevitably results in such kind of defects, introducing randomness and eventually smearing the critical features of metal-insulator transitions11. In the face of these challenges, we have chosen to fabricate FET adopting single-crystalline SrTiO3 for the channel. This compound is a band insulator with a crystal structure characteristic of many TMO Mott insulators and becomes metallic by electron doping. SrTiO3 is an n-type wide-gap semiconductor with a band gap of 3.2eV. It is considered as a matrix for spintronic devices due to the unique configuration of the spin-precession vector at the surface and the absence of the Dresselhaus term. The surface of the single crystal can be atomically flat and is widely used as a substrate for correlated TMO thin films, making it preferable candidate to test the suitability of the reported gate insulator for future electronics. Identifying the technical methods and physical mechanism for paraelectric tuning of electronic conduction in two dimensional electron gases (2DEG) created at the surface of SrTiO3 is a problem of bursting interdisciplinary interest12.

High-density charge accumulation ~ 1015 cm−2 was recently realised13 through an electric double-layer (EDL) on the surface of electrolytes such as ionic liquids. Although the gating with EDL is a promising method for future correlated electron devices, its viability is hindered, because ionic liquids on the surface of TMOs may trigger redox reactions, causing vacancies at the interface especially in the presence of high electric fields14,15. In addition, the continuous control of the carrier density with EDL can be done only by using liquid electrolytes, which are unsuitable for integration to the present solid-state electronics.

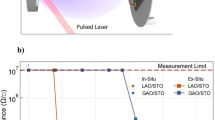

Here, we have engineered a bilayer of poly-monochloro-para-xylylene (known as Parylene-C)16 with Ta2O5, Fig. 1. Ta2O5 has a high dielectric constant ε = 25 and a relatively high dielectric strength ~4 MV/cm17. The combination of Ta2O5 and Parylene-C into a single gate insulator enabled a sheet carrier density of ~1013 cm−2 while keeping the field effect mobility of the SrTiO3 surface at ~10 cm2/Vs. Fabrication details can be found in the Methods Summary. The electronic transport measurements were performed using an Agilent 4155C semiconductor parameter analyser.1

(a) Photograph of a typical FET structure fabricated on the top of a (100) surface of a single-crystalline SrTiO3. Gate (G), source (S), drain (D) electrodes and four other potential probes such as V1 and V2 are indicated. A gold wire of 25 μm diameter is attached by conducting gold paint (Silvest 8560-1A, Tokuriki Chemicals). (b) Scanning electron microscopy images of the cross sections of the bilayer gate insulator. The sample was cleaved at room temperature (left) and at liquid N2 temperature (right). See Methods Summary for details. (c) Gate leak current plotted against the sheet carrier density for the bilayer gate insulator with 200 nm Ta2O5 deposited on the top of 48 nm Parylene-C (blue opaque square) and for the single layer gate insulator of 3 μm Parylene-C (red transparent square). (d) Field-effect (FE) mobility plotted against the sheet carrier density for samples A, B, C and D with different Parylene-C thickness as summarised in Table 1.

Results

Fig. 1(c) shows the gate leak currents plotted against the sheet carrier density for the bilayer gate insulator and for the single Parylene-C gate insulator. Although the total thickness of the bilayer gate insulator is 10 times thinner than the 3 μm-thick Parylene-C, the leak current of the bilayer is an order of magnitude lower, which is similar to the trend reported earlier18. Hence, the sputtering deposition of Ta2O5 does not damage the Parylene-C thin film. Fig. 1(d) depicts an upturn in the increase of the field effect mobility at sheet carrier densities 2 – 4 × 1012 cm−2. The field effect mobility is defined as  , where σsq ≡ (ISD/W)/(ΔV/Lo) is the sheet conductance and nsq ≡ Csq(VG − Vth)/e is the nominal sheet carrier density in the channel region. ISD is the channel current, Lo (and ΔV) is the distance (and voltage difference) between channel electrodes V2 and V1, W is the channel width, Csq is the measured total capacitance per unit area and e is the elementary charge. Although ISD increased almost exponentially with the application of VG, the ISD–VG behaviour is different from that in the conventional subthreshold regime. In fact, all our samples showed extremely large μFE, ~10 cm2/Vs at large carrier densities (i.e., large VG) without reaching saturation even at room temperature. Thus, we set the threshold voltage Vth = 0. Notably, μFE is an order of magnitude larger than earlier reports for a Parylene-C/SrTiO3 FET at room temperature (μFE = 0.3 cm2/Vs for nsq = 3 × 1012 cm−2)19 and comparable to the bulk Hall mobility of SrTiO320.

, where σsq ≡ (ISD/W)/(ΔV/Lo) is the sheet conductance and nsq ≡ Csq(VG − Vth)/e is the nominal sheet carrier density in the channel region. ISD is the channel current, Lo (and ΔV) is the distance (and voltage difference) between channel electrodes V2 and V1, W is the channel width, Csq is the measured total capacitance per unit area and e is the elementary charge. Although ISD increased almost exponentially with the application of VG, the ISD–VG behaviour is different from that in the conventional subthreshold regime. In fact, all our samples showed extremely large μFE, ~10 cm2/Vs at large carrier densities (i.e., large VG) without reaching saturation even at room temperature. Thus, we set the threshold voltage Vth = 0. Notably, μFE is an order of magnitude larger than earlier reports for a Parylene-C/SrTiO3 FET at room temperature (μFE = 0.3 cm2/Vs for nsq = 3 × 1012 cm−2)19 and comparable to the bulk Hall mobility of SrTiO320.

The typical ISD–VSD characteristics of Sample B in Fig. 2(a) indicate that the current saturates for large VSD as in conventional semiconductor FETs, where it occurs due to the pinch-off of the channel. The saturation vanishes when the channel current in Fig. 2(a) is plotted against the voltage drop inside the channel ΔV, Fig. 2(b). Hence, the pinch-off region is rather small even at low VG and emerges between the drain and the V2 electrode for VSD below 5V. Fig. 2(c) shows that the current increases monotonically from ~1 nA to ~100 μA as the gate voltage increases up to 40 V, thereby demonstrating a continuous electrostatic control of the sheet carrier density.

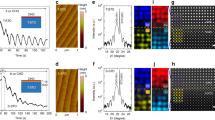

Furthermore, for small fixed values of VG, although the channel current does not change very much (Fig. 3(a)), the ratio ΔV/VSD decreases rapidly with increasing VSD. This feature can be associated with the formation of field domains21. We also observe that in various parameter conditions, ΔV/VSD approaches the geometrical value ~0.37 = (V1–V2 distance 295 μm)/(source-drain distance 800 μm). This indicates that in those regimes the contact resistance between SrTiO3 and Al electrodes, which is expected to be ohmic, is indeed negligibly small compared to the channel resistance of SrTiO3. It is interesting, however, to observe the behaviour of ΔV/VSD with increasing VG and with fixed (small) value of VSD in Fig. 3(a). This feature is the so-called S-type negative differential resistivity (SNDR) associated with the formation of current filaments21.

(a) Channel current of Sample C plotted against ΔV/VSD.VSD is swept from 0 to 10 V for the different values of VG as shown in the thick green lines. The dashed lines indicate the VSD contour, in which SNDR is seen for low VSD and vanishes with increasing VSD. (b) The results of numerical simulations. The voltages are expressed in arbitrary units. See Supplementary Materials for details.

The rather complicated behaviour of the ISD vs (ΔV/VSD) curves in Fig. 3(a) was qualitatively reproduced (Fig. 3(b)) by a model calculation based on the following assumptions: (i) the existence of a low VG regime where charge carriers are mainly spatially and inhomogeneously confined in cells and move through the channel region by incoherent tunnelling, (ii) a higher VG regime where the conductive cells overlap and percolating conduction paths are formed and (iii) a well developed homogeneous 2DEG with barriers formed at the interfaces. We modelled the experimental system through a 2D resistor network array where the transport properties of each cell is determined primarily by the local electron density. The cells are assumed to be randomly distributed shallow potential wells for carriers with a site dependent potential strength ψdis(r). At low VG and VSD, the cells have low density and the carriers are confined. The carriers move between cells by a variable range hopping (VRH) mechanism. At higher applied voltages, the occupation of cells increases and the carriers delocalise, augmenting their mobility. For given external potentials VG and VSD, we solve for the resistor network and compute the local voltages at all cells along the 2D channel. These local voltages are then compared to the corresponding values of the local confining potential of the cell ψdis(r). If their difference is negative, the mobility is assumed to be the VRH type, whereas if it is positive, we adopt a much larger value, consistent with a band-like conduction in the metallic state. The interfaces at the source and drain electrodes are simply modelled as barriers with potential height ψb. The details of the model and the numerical study are presented in the Supplementary Materials. Our numerical study captures the qualitative transport behaviour shown in Fig. 3, providing new insight to the conduction states of 2DEGs in SrTiO3. In fact, it demonstrates that the system evolves through a variety of regimes connected through crossovers depicted schematically in Fig. 4.

Schematic pictures of the evolution of conductive cells in the channel as demonstrated in Fig. 3. For increasing VG, the channel varies from insulator to relatively good metal as the size of the conductive cells increases and a percolating current filament is formed.

This represents SNDR. Meanwhile, for increasing VSD, the region near the drain electrode is pinched off. By controlling the two parameters VSD and VG, we can realise the formation and continuous evolution of field domains and current filaments; i.e., the competition of SNDR and the interface depletion at drain, which is not only the main topic of the research for the resistance change memory9 but also a common problem associated to the future oxide electronics. The filament can be ruptured by the Joule-heating at the interface to the metal electrode (called faucet27); one of the widely accepted models of the non-volatile resistance change (fuse-antifuse resistive switching9).

Discussion

In summary, we have demonstrated that the Parylene-C/Ta2O5 bilayer overcomes previous limitations, achieving the required large electrostatic carrier doping, while keeping a high quality interface with the TMO. The hybrid gate insulator can sustain a sheet carrier density of 8 × 1012 cm−2, without introducing formidable damage to the channel interface, as the field-effect mobility of SrTiO3 exceeds 10 cm2/Vs, even at room temperature. The excellent agreement of our numerical study with measurements on the hybrid gate insulator, indicate a continuous evolution through a variety of different regimes, including tuneability of field domains and current filaments on the surface of SrTiO3. Our findings provide a novel method for paraelectrical tuning of metal-nonmetal transitions in correlated electron devices made of ABO3-type TMOs. Notably, the fabrication details and physical mechanism reported here may be applied towards emergent oxide electronics controlled by low dimensional charge carrier transport.

Further to the practical interest, low temperature studies on similar devices would reveal whether granular superconductivity22 in SrTiO3 could be realised for small VG and VSD. Indeed, the behaviour of possible superconducting cells with dimensions comparable to characteristic length scales may be considerably different from bulk materials. Moreover, the quantum confinement in the cells may lift the degeneracy of the lowest energy band of SrTiO3, affecting the Rashba effect on its surface23.

Methods

Preparation of Parylene-C thin film was performed as follows. In a φ46 mm quartz tube, di-monochloro-para-xylylene was sublimated at 150°C, the dimer flew into a high temperature (800°C) region24, where it was cleaved into two monomer units16. The reactive intermediates were then transported to a room temperature deposition chamber at the pressure of 2 × 10−4 Pa. Upon condensation on the surface of single-crystalline SrTiO3, spontaneous polymerisation into Parylene-C took place. The Parylene-C thin film deposited through this so-called Gorham method16 provides excellent conformal coating on the SrTiO3 surface. The thin film of Ta2O5 was deposited directly on the top of the Parylene-C by radio frequency (rf) sputtering at room temperature. We used a Ta2O5 ceramic target in a flowing Ar gas of 25 sccm and 5.5 Pa. The rf power was 2 W/inch2 and the sample-target distance was 140 mm. The thickness of the Ta2O5 layer was ~200 nm measured by a surface profiler (KLA Tencor). On the top of Ta2O5, a 150 nm thick Au gate electrode with a 5 nm Ti adhesion layer was deposited by electron-beam deposition. The thickness of the Parylene-C layer was estimated from the measured capacitance of a built-in capacitor (of area 800 × 800 μm2), using the known values ε = 3.2 for Parylene-C and ε = 25 for Ta2O5.

We used the Al metal for source and drain electrodes; Al gives ohmic contact to SrTiO3. For the other parts of the device fabrication process, we followed the same method and used the same materials as reported by Nakamura et al.25.

For some samples, the thickness of the gate insulator was also measured by an S-4800 (Hitachi High-Tech) scanning electron microscope (SEM); the values were in good agreement with those estimated from the capacitance. Since the Parylene-C is much softer than Ta2O5, when we tried to expose the cross sections for the SEM measurement, either cutting with a scalpel or simply cleaving, the bilayer at room temperature easily deformed (stretches and shrinks at the ends) the Parylene-C layer and the fibrils of Parylene-C always extended out of the cross section. We found that freezing the samples in liquid N2 facilitates the cleaving.

Fig. 1 (b) shows the comparison of the cross section of a sample cleaved at room-temperature and one at liquid-N2 temperature. The Parylene-C cross section in the latter case appears rather lumpy. However, this was never observed in the cross sections of the samples cleaved at room-temperature; thus, it is likely that the uneven cross section is due to the steep rise of temperature with heavy bedewing in air after the cleavage in liquid-N2. It has been shown that a conventionally deposited planar Parylene-C thin film16 does not possess nanostructured morphology26.

References

Chakhalian, J., Millis, A. J. & Rondinelli, J. Whither the oxide interface. Nat. Mater. 11, 92–94 (2012).

Hwang, H. Y. et al. Emergent phenomena at oxide interfaces. Nat. Mater. 11, 103–113 (2012).

Hormoz, S. & Ramanathan, S. Limits on vanadium oxide Mott metal-insulator transition field-effect transistors. Solid-State Electr. 54, 654–659 (2010).

Inoue, I. H. Electrostatic carrier doping to perovskite transition-metal oxides. Semicond. Sci. Technol. 20, S112–S120 (2005).

Xiang, P.-H. et al. Strain-mediated phase control and electrolyte-gating of electron-doped manganites. Adv. Mat. 23, 5822–5827 (2011).

Asanuma, S. et al. Tuning of the metal-insulator transition in electrolyte-gated NdNiO3 thin films. App. Phys. Lett. 97, 142110 (2010).

Nakano, M. et al. Collective bulk carrier delocalization driven by electrostatic surface charge accumulation. Nature 487, 459–462 (2012).

Yang, Z., Ko, C. & Ramanathan, S. Oxide electronics utilizing ultrafast metalinsulator transitions. Ann. Rev. Mater. Res. 41, 337–367 (2011).

Yang, J. J., Inoue, I. H., Mikolajick, T. & Hwang, C. S. Metal oxide memories based on thermochemical and valence change mechanisms. MRS Bull. 37, 131–137 (2012).

Phillips, J. C. Physics of complex metals — temperature-dependent resistivities in ionic superconductors and stable quasi-crystals. Phys. Rev. B 46, 8542–8558 (1992).

Miyashita, S. Phase transition in spin systems with various types of fluctuations. Proc. Jpn. Acad. Ser. B 86, 643–666 (2010).

Dagotto, E. The conducting face of an insulator. Nature 469, 167–168 (2011).

Yuan, H. et al. High-density carrier accumulation in ZnO field-effect transistors gated by electric double layers of Ionic Liquids. Adv. Funct. Mater., 19, 1046–1053 (2009).

Ueno, K. et al. Electric-field-induced superconductivity in an insulator. Nature Mater. 7, 855–858 (2008).

Ueno, K., Shimotani, H., Iwasa, Y. & Kawasaki, M. Electrostatic charge accumulation versus electrochemical doping in SrTiO3 electric double layer transistors. Appl. Phys. Lett. 96, 252107 (2010).

Gorham, W. F. A new general synthetic method for preparation of linear polyp-xylylenes. J. Polym. Sci. A-1 4, 3027–3039 (1966).

Sethi, G. et al. Structure and Dielectric Properties of Amorphous Tantalum Pentoxide Thin Film Capacitors. 2007 Annual Report Conference on Electrical Insulation and Dielectric Phenomena, 815–818 (2007).

Deman, A.-L. & Tardy, J. PMMA-Ta2O5 bilayer gate dielectric for low operating voltage organic FETs. Org. Electron. 6, 78–84 (2005).

Nakamura, H. Electrostatic carrier density control in SrTiO3. D. Eng. Thesis, University of Tokyo., 2006.

Ahrens, M., Merkle, R., Rahmati, B. & Maier, J. Effective masses of electrons in n-type SrTiO3 determined from low-temperature specific heat capacities. Physica B 393, 239–248 (2007).

Ridley, B. K. Specific negative resistance in solids. Proc. Phys. Soc. 82, 954–966 (1963).

Beloborodov, I. S., Lopatin, A. V., Vinokur, V. M. & Efetov, K. B. Granular electronic systems. Rev. Mod. Phys. 79, 469–518 (2007).

Nakamura, H., Koga, T. & Kimura, T. Experimental evidence of cubic Rashba effect in an inversion-symmetric oxide. Phys. Rev. Lett. 108, 206601 (2012).

Williams, J. M. & Rowen, J. T. Diagnosis and therapy for a recalcitrant parylene coater. J. Vac. Sci. Technol. A 5, 2760–2762 (1987).

Nakamura, H. et al. Low temperature metallic state induced by electrostatic carrier doping of SrTiO3 . Appl. Phys. Lett. 89, 133504 (2006).

Demirel, M. C. Emergent properties of spatially organized poly(p-xylylene) films fabricated by vapor deposition. Col. Surf. A 321, 121–124 (2008).

Inoue, I. H., Yasuda, S., Akinaga, H. & Takagi, H. Nonpolar resistance switching of metal/binary-transition-metal oxides/metal sandwiches: Homogeneous/inhomogeneous transition of current distribution. Phys. Rev. B 77, 035105 (2008).

Acknowledgements

We are grateful to H. Shima, T. Yamada and T. Hasegawa for technical help. This work was supported by the Japan-Singapore Joint-Research Program, the Japan Society for the Promotion of Science (JSPS) and the National Research Foundation, Singapore through Competitive Research Programme (CRP Award No. NRF-CRP-4-2008-04). I. H. I. was partly supported by Grants-in-Aid for Scientific Research (category A, grant number 24244062).

Author information

Authors and Affiliations

Contributions

I.H.I. and C.P. conceived and supervised the project. A.B.E. fabricated the devices and performed all the measurements. I.H.I. contributed to the experimental setup. P.S. and M.J.R. did the numerical simulation study. All the authors discussed the results and cowrote the manuscript.

Ethics declarations

Competing interests

The authors declare no competing financial interests.

Electronic supplementary material

Supplementary Information

Supplementary Material

Rights and permissions

This work is licensed under a Creative Commons Attribution-NonCommercial-NoDerivs 3.0 Unported License. To view a copy of this license, visit http://creativecommons.org/licenses/by-nc-nd/3.0/

About this article

Cite this article

Eyvazov, A., Inoue, I., Stoliar, P. et al. Enhanced and continuous electrostatic carrier doping on the SrTiO3 surface. Sci Rep 3, 1721 (2013). https://doi.org/10.1038/srep01721

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/srep01721

This article is cited by

-

A large modulation of electron-phonon coupling and an emergent superconducting dome in doped strong ferroelectrics

Nature Communications (2021)

-

Enhanced electronic-transport modulation in single-crystalline VO2 nanowire-based solid-state field-effect transistors

Scientific Reports (2017)

-

Anomalous enhancement of the sheet carrier density beyond the classic limit on a SrTiO3 surface

Scientific Reports (2016)

-

Tunnel vision

Nature Physics (2014)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.