Abstract

A new concept of read-out method for ferroelectric random-access memory (FeRAM) using a graphene layer as the channel material of bottom-gated field effect transistor structure is demonstrated experimentally. The transconductance of the graphene channel is found to change its sign depending on the direction of spontaneous polarization (SP) in the underlying ferroelectric layer. This indicates that the memory state of FeRAM, specified by the SP direction of the ferroelectric layer, can be sensed unambiguously with transconductance measurements. With the proposed read-out method, it is possible to construct an array of ferroelectric memory cells in the form of a cross-point structure where the transconductance of a crossing cell can be measured selectively without any additional selector. This type of FeRAM can be a plausible solution for fabricating high speed, ultra-low power, long lifetime, and high density 3D stackable non-volatile memory.

Similar content being viewed by others

Introduction

There has been an enormous amount of interest in utilizing ferroelectric materials for fabricating non-volatile memory devices, so-called ferroelectric random-access memory (FeRAM), with low power consumption and high operation speed stemming from the voltage-driven fast switching of spontaneous polarization (SP) in a ferroelectric material1,2,3,4,5,6. However, the FeRAM structures that have been explored so far possess a couple of critical limitations including short cell lifetime due to the destructive read-out process or depolarization field7,8,9,10.

As one way of overcoming such limitations, the FeRAM structure based on a field-effect transistor composed of graphene channel and ferroelectric gate insulator (ferroelectric GFET or FeGFET) has been studied by several research groups11,12,13,14,15,16. Most recently, there has been an experimental report demonstrating a quaternary-level memory device based on the four different polarization states observed in a semicircular top-gated ferroelectric nanowire FET17. In a FeGFET structure, the conductance of the graphene channel can vary depending on the direction of SP in the ferroelectric gate insulator due to the low density-of-states (DOS) of graphene associated with its unique energy-momentum relation near the Dirac point. Hence, the SP direction of the ferroelectric layer corresponding to the memory state of FeGFET can be sensed by measuring the conductance of the graphene channel. The main objective of all the previous works for FeGFET is basically for verifying this sensing mechanism. Although they could resolve the destructive read-out problem, the low on/off ratio of graphene channel conductance originating from the minimal conductance of graphene itself brings about the necessity of attaching a separate selector (transistor or diode) to each memory cell for realizing the random accessibility in read-out and write-in processes15,16,18,19.

In this work, we demonstrate experimentally a new type of non-destructive read-out method for FeGFET structure which does not require any additional selector for random accessing. The proposed read-out method relies on measuring the transconductance of the graphene channel which is quantified to be the change of channel current divided by the change of gate voltage. Due to the ambipolar characteristics of graphene in its carrier transport, the sign of transconductance is found to be reversed as the SP direction of the ferroelectric layer switches. This sign reversal of transconductance can ensure the unambiguous read-out for the memory state of each cell specified by the SP direction of the ferroelectric layer. The physical mechanism for the sign reversal of transconductance will be discussed in detail.

Results

Non-destructive read-out scheme enabling self-selective operation of FeGFET

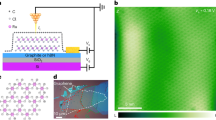

The working principle of the non-destructive read-out method proposed in this work is as follows. For a typical back-gated FeGFET with its cross-sectional structure shown in Fig. 1a, the transconductance of graphene channel near-zero gate voltage (Vg) is expected to vary depending on the doping of graphene channel determined by the SP direction of ferroelectric layer thanks to the low DOS and the ambipolar carrier type of graphene20,21. Since the transconductance can be measured with a relatively small range of gate voltage around Vg = 0, the memory state specified by the SP direction of the ferroelectric layer can be read without being influenced by the gate voltage used for the transconductance measurement at all. In an ideal case, the transconductance of the graphene channel near Vg = 0 will be positive when the SP points upward since the graphene channel will be electron-doped due to the positive polarization charges induced on the top surface of the ferroelectric layer (Fig. 1b). On the other hand, if the SP points downward as shown in Fig. 1c, the negative polarization charges on the ferroelectric surface will make the graphene channel hole-doped so that the transconductance of the graphene channel will become negative. However, what has been observed experimentally so far is indeed opposite to the ideal expectation. It is found that the upward SP (positive surface polarization charges) makes the graphene channel hole-doped and the downward SP (negative surface polarization charges) electron-doped as shown in Fig. 1d, e, respectively15,22,23,24,25. This so-called anti-hysteretic behavior is considered to be due to the electron trapping and detrapping on the surface of the blocking insulator which is deposited on top of the ferroelectric layer. A more detailed discussion of the anti-hysteretic behavior will be given later. Here, it is noted that the proposed method is directly applicable for operating a cross-point type of FeGFET memory cell array, illustrated in Fig. 1a, with no selector device. The split bit-line structure of Fig. 1a makes all the memory cells in the same bit-line connected in parallel between shared source and drain electrodes. Accordingly, the gated channel properties of each FeGFET memory cell can be probed independently for the common source and drain voltages by ensuring that the ungated channel currents of the other FeGFET memory cells will just become an offset current as a sum. With this split bit-line structure, the operational characteristics of a single stand-alone FeGFET are naturally expected to manifest themselves even when being incorporated in an array form. Since the transconductance represents how the channel current is modulated as the gate voltage changes, the configuration of transconductance measurement will be established only for the crossing cell in the cross-point type array in Fig. 1a. This ensures that the memory state of the crossing cell, specified by its transconductance, can be sensed selectively without any additional selector device.

a Schematic illustration of FeGFET and its array structure. Drain-to-source current (Ids) vs. gate voltage (Vg) curves for FeGFET showing the normal hysteretic (b upward and c downward SP), and anti-hysteretic (d upward and e downward SP) behaviors. The Fermi level matching with the doping of graphene channel is shown in the inset of each curve.

Fabrication of FeGFET memory cell

A prototype of FeGFET demonstrating the validity of the proposed read-out scheme was fabricated by following the procedures below. A 200 nm thick lead zirconate titanate (PZT, Pb1.1Zr0.35Ti0.65O3) layer grown with the sol–gel process on a Pt/Ti/SiO2/Si substrate was chosen for the ferroelectric layer. The Pt/Ti (150 nm/10 nm) stacked layer acts as the back-gate electrode. The surface of the PZT layer is found to be somewhat rough as shown in the atomic force microscopy (AFM) image (Fig. 2a), typical for thin films grown with the sol–gel process. The average roughness is measured to be ~2.30 nm. This is noticeably large compared with the thickness of graphene (~0.34 nm) and the morphology of a graphene layer transferred on top of it can become quite undulated. Hence, a 15–30 nm thick Al2O3 film was deposited by using atomic layer deposition (ALD) on the PZT layer to reduce the surface roughness, down to ~1.07 nm as shown in Fig. 2b, and also block the leakage current through the PZT layer. In order to investigate the effect of the Al2O3 blocking layer on the apparent coercive field (Ec) and polarization, polarization vs. electric field (P–E) hysteresis loops were measured on both metal/PZT/metal and metal/Al2O3/PZT/metal capacitor structures as shown in Fig. 2c. In this case, the Al2O3 blocking layer is ~30 nm thick. The hysteresis loop measurements were performed with a triangular voltage sweep at 1 kHz frequency (Precision LC, Radiant Technologies). As shown in Fig. 2c, the existence of the Al2O3 layer is observed to increase the apparent coercive field noticeably to widen the curve while the saturation polarization (Ps) decreases moderately, and the remnant polarization (Pr) changes minimally as summarized in Table 1. In the sense of reducing the operation voltage of FeGFET, the Al2O3 layer is preferable to be as thin as possible. However, it should be thick enough to block the leakage current effectively. A non-ferroelectric insulating layer inserted in a metal/ferroelectric/metal stack can increase the depolarization field to cause the formation of reverse domains26, reducing the polarization switching speed and limiting the device scaling. Therefore, it will be always beneficial to minimize the thickness of the Al2O3 layer by improving the insulating property of the ferroelectric layer. After the deposition of the Al2O3 layer, single-layer graphene synthesized with chemical vapor deposition (CVD) on Cu foil was transferred on the Al2O3 surface by using the semi-dry transfer method demonstrated in ref. 27. The transferred graphene layer was found to be mostly monolayer from Raman spectrum measurements. As shown in Supplementary Fig. 1, the ratio of 2D peak to G peak is close to two. Following the graphene transfer, the photolithography patterning and O2 plasma etching processes were performed to form the graphene channel. Finally, the source and drain contacts were made with Au/Ti (50 nm/10 nm) stacked layers to complete the basic structure of FeGFET. For some of the fabricated FeGFETs, an additional AlOx overlayer was formed on the graphene channel to modulate its doping type and density.

Operational characteristics of FeGFET without doping overlayer

Once the prototypic FeGFETs were fabricated, the drain-to-source current (Ids) vs. back-gate voltage (Vg) curve with a small (0.1 V) drain-to-source voltage (Vds) applied was measured first for the basic structure without the doping overlayer the schematic view of which is shown in Fig. 3a. The transfer curve (Ids–Vg) measured at room temperature in air for the gate voltage sweeping between −8.0 V and 8.0 V is shown in Fig. 3b. The graphene channel is found to become hole-doped with positive back-gate voltages inducing upward SP and electron-doped with negative back-gate voltages inducing downward SP, which reveals the anti-hysteretic behaviors described earlier. Additionally, it is noted that the charge neutral point of the graphene channel appears larger in magnitude for p-type doping than n-type doping, implying that the graphene channel becomes p-type doped more easily than becoming n-type doped. This asymmetric doping tendency is considered to be another manifestation of the electron trapping and detrapping on the surface of the blocking insulator. A graphene film is known to be p-type doped typically when it is transferred on the surface of an oxide layer27,28,29. This is considered to be caused by the electron transfer from the graphene film into the trap states on the oxide surface as depicted in Fig. 3c. When the SP points downward, the repulsive force from the negative polarization charges induced on the ferroelectric surface will push some electrons trapped in the surface states back into the graphene channel. Then, the holes residing in the graphene channel will be annihilated by being recombined with the transferred electrons to reduce the p-type doping of the graphene channel. If the electron transfer from the trapped states to the graphene channel goes beyond the level of annihilating all the holes in the graphene channel, the doping type of graphene channel will change to n-type (anti-hysteretic). In the case of upward SP, the positive polarization charges induced on the ferroelectric surface will make some electrons transferred from the graphene channel into the surface trap states and the graphene channel will become p-type with the accompanying hole generation (anti-hysteretic). Since some amount of electrons in the graphene channel will be transferred already to the surface trap states even with no aid of SP, the additional electron transfer due to the upward SP will just enhance the p-type doping of the graphene channel.

a Schematic view of the FeGFET without doping overlayer together with the configuration of electrical measurements. b Transfer curve (Ids–Vg) obtained by sweeping the back-gate voltage as indicated by the arrows. c Schematic view of the electron transfer between graphene and Al2O3 layer causing the anti-hysteretic behavior in the drain-to-source current modulated by the ferroelectric SP. d Operational characteristics of the FeGFET showing the transfer curve in (b): (top) a series of triangular gate voltage pulses for write-in to switch SP direction of PZT layer alternatively (+5 V and −8 V) and saw-tooth gate voltage pulses for read-out (−0.1 V to +0.1 V), (middle) drain-to-source current obtained during read-out and (bottom) transconductance extracted from it showing the clear switching between upward and downward SP direction. e Operational characteristics of the FeGFET possessing relatively strong p-type doping tendency of graphene channel measured with the write-in voltages of +5 V and −25 V.

In order to assess the operational characteristics of fabricated FeGFET as a memory device, the opposite-polarity voltage pulses were applied repeatedly on the back-gate electrode to switch the direction of SP in the ferroelectric layer and the transconductance of the graphene channel was measured between the voltage pulses. More concretely, as shown in the top graph of Fig. 3d, the high-voltage write-in triangular pulses were applied with their polarities being changed alternatively. Then, the low-voltage read-out saw-tooth pulses (from −0.1 V to 0.1 V) were applied between the write-in pulses. Just as a note, these switching characteristics measurements were performed at room temperature in the air. In our prototypic FeGFET, the PZT/Pt/Ti stack is global to cover the entire substrate. Hence, a substantial amount of capacitively-induced transient current decaying somewhat slowly can flow when a square pulse accompanied with abrupt voltage change is applied to the Pt/Ti back-gate electrode due to the large area of PZT/Pt/Ti stack. This transient current can disturb the subsequent transconductance measurement. The triangular pulse with its voltage increasing gradually was used to minimize the transient current. The middle and bottom graphs of Fig. 3d show the measured drain-to-source current and transconductance extracted from it, respectively. The write-in voltages used here were +5 V (upward SP) and −8 V (downward SP) which were chosen to ensure the clear switching of carrier type in the graphene channel within the range of back-gate voltage for the transfer curve shown in Fig. 3b. By considering the p-type doping tendency of graphene channel associated with the electron trap states on the blocking insulator surface, the write-in voltage for switching the graphene channel to n-type is preferable to be larger in magnitude than that for switching to p-type in order to make the measured transconductance more like symmetric between upward and downward SP. It is apparent that the transconductance of the graphene channel changes its sign with the SP switching in the ferroelectric layer. One important notion here is that the sign of transconductance indicates the anti-hysteretic behavior of fabricated FeGFET, matching with the transfer curve in Fig. 3b. As described previously for the anti-hysteretic case, the graphene channel is found to be p-type (n-type) doped with the upward (downward) SP in the ferroelectric layer, leading to the negative (positive) transconductance. Since the electron trap density on the surface can change from batch to batch in growing the Al2O3 blocking insulator with ALD, the p-type doping tendency of the graphene channel can be various among the fabricated FeGFETs. Hence, the write-in voltage, especially for downward SP, also needs to be adjusted for switching the carrier type of graphene channel to n-type clearly. Figure 3e shows the operational characteristics of the FeGFET for which the p-type doping tendency was found to be stronger than other devices. In this case, the write-in voltage of −25 V was used for downward SP to achieve the associated transconductance comparable to the case of Fig. 3d. The endurance of fabricated FeGFET for multiple cyclic switching of memory state is also an important performance measure. Supplementary Fig. 3 shows the working cycle endurance of the FeGFET tested by performing the cyclic switching 1000 times in the air. The transconductance for downward SP is found to become saturated after decreasing shortly in the early stage of cycling while the transconductance for upward SP remains more steady throughout the entire cycling process. Most importantly, the sign of transconductance remains well-maintained for both directions of SP even after 1000 cycles.

Figure 4a shows the retention characteristics of the fabricated FeGFET obtained for both memory states (upward and downward SP) at room temperature and in vacuum (~10−3 Torr) for 24 h after a single write-in operation. As seen in the figure, the magnitude of measured transconductance decreases noticeably in the early stage of measurement. However, the decrease slows down and the transconductance gets saturated as time goes on. Most relevantly, the sign of transconductance is maintained for both upward and downward SP, indicating that the retention of memory state is pretty reliable. It is not quite conclusive what causes the decrease of transconductance after the write-in operation. One plausible explanation is the electrostatic screening for the surface polarization charges of the ferroelectric layer due to the hydronium (H3O+) and hydroxide (OH−) ions residing between the graphene channel and the Al2O3 layer. It is known that the water molecules can be ionized into H3O+ and OH− ions with the catalytic aid of oxide30. Hence, if there are water molecules sneaking into the gap between the graphene channel and the Al2O3 layer, some of them will be ionized, resulting in the coexistence of water molecules and H3O+ and OH− ions. Although the graphene channel was formed by using the semi-dry transfer process with NO water involved27, there will be always chances for ambient water molecules to go through some defective sites of graphene and stay between the graphene channel and the Al2O3 layer nearby those sites. The defective sites include the local tearing and loss occurring during the transfer process as well as the intrinsic grain boundaries and vacancies formed during the growth of the graphene layer. The FeGFET used for the retention test in the vacuum was also exposed to the air for a while before being put into the vacuum. Hence, a fair amount of water molecules is expected to go into the gap between the graphene channel and the Al2O3 layer. Once it was put into the vacuum, some of those water molecules might be released into the vacuum due to the pressure difference between inside and outside the gap, reducing the number of water molecules in the gap. When the polarization charges on the ferroelectric surface switch to the positive (upward SP), OH- ions will be attracted toward the Al2O3 layer, and H3O+ ions will be repelled toward the graphene layer. Conversely, if the polarization charges switch to the negative (downward SP), H3O+ ions will be attracted toward the Al2O3 layer, and OH− ions will be repelled toward the graphene layer. In either case, the two types of ion separated spatially will generate the electric field in the gap between graphene and Al2O3 layer along the direction opposite to that of the electric field originating from the polarization charges on the ferroelectric surface. Hence, some of the electrons transferred to either graphene channel or Al2O3 layer by the electric field from the ferroelectric polarization charges can be transferred backward (electron back-transfer) to reduce the doping concentration of the graphene channel (Fig. 4b, c). The motion of attracted ions is very likely to be slower than the electron transfer between the graphene channel and the surface trap states of the Al2O3 layer. Therefore, just after the SP of the ferroelectric layer switches upward or downward, the electron back-transfer will be pretty weak and the graphene channel will be doped maximally for the given SP. Since then, the number of spatially-separated ion pairs, determining the degree of electron back-transfer, will increase somewhat rapidly in the beginning and becomes saturated slowly. Synchronously, the doping of the graphene channel will also decrease rapidly and get saturated slowly. In fact, this trend of graphene channel doping matches well with the measured transconductance of FeGFET shown in Fig. 4a.

a The retention of memory state tested for both upward (black squares) and downward (red circles) SP at room temperature and in vacuum for 24 h after write-in process. The schematic time-evolving band profiles of graphene/Al2O3/PZT stack structure for b downward and c upward SP. After the write-in process, the H3O+ and OH− ions separated spatially between graphene and Al2O3 layer weaken gradually the electric field effect from the surface polarization charges of ferroelectric layer, making some of the electrons transferred to either graphene channel or Al2O3 layer by the electric field from the surface polarization charges transferred backward (electron back-transfer). Here, EF: Fermi level, ED: Dirac point, E0: Vacuum level, Ec: Conduction band edge, Ev: Valence band edge.

In order to validate the electron back-transfer scenario, the retention measurements were performed also in the air and the measured data are shown in Supplementary Fig. 2. Since the water molecules residing between the graphene channel and the Al2O3 layer will hardly come out in the air, the transconductance change is expected to be more significant and rapid. The measured transconductance indeed shows the expected trend. Moreover, the transconductance is found to change its sign for downward SP, more concretely from positive (n-type) to negative (p-type), as time goes on. This behavior can be understood with the notion of the electric field effect from the negative polarization charges on the ferroelectric surface being suppressed strongly by the opposite-direction electric field between H3O+ and OH− ions, making the situation become as if the ferroelectric layer does NOT exist (Fig. 3c).

Operational characteristics of FeGFET with AlOx doping overlayer

In order to make the write-in voltage of FeGFET more symmetric, it is necessary to minimize the initial doping of the graphene channel so that the associated charge neutrality point becomes as close to 0 V as possible. Since it was quite challenging to passivate the surface trap states of the Al2O3 layer, the counter-doping of graphene channel achievable by forming a doping overlayer on top of it has been pursued. We first formed a ~2 nm thick Al film pattern covering the graphene channel by using e-beam evaporation and photolithography. Then, the Al film pattern was left in the air over a day to make it oxidized (Fig. 5a). Because of the relatively low work-function of Al, some amount of electrons are expected to be transferred from the Al film to the p-type doped graphene channel so that the graphene channel becomes nearly intrinsic. Once this counter-doping of graphene channel is completed, the subsequent ambient oxidation process will convert the Al film to a non-stoichiometric AlOx layer. The AlOx overlayer formed this way will be sufficiently insulating to make the flow of charge carriers confined in the graphene channel.

a Schematic view of the FeGFET with AlOx doping overlayer together with the configuration of electrical measurements. b A series of triangular gate voltage pulses for write-in to switch the SP direction of the PZT layer alternatively (+7 V and −5 V) and saw-tooth gate voltage pulses for read-out (−0.1 V to +0.1 V). c Drain-to-source current obtained during the read-out voltage sweep which is more symmetric with respect to zero gate voltage compared with that of FeGFET without doping overlayer and d transconductance extracted from (c). e Schematic view showing the electron transfer between graphene and Al2O3 doping layer and the influence of AlOx overlayer on the drain-to-source current modulated by the ferroelectric SP.

Figure 5b shows triangular voltage pulses applied on the back-gate electrode where the write-in voltages are +7 V and −5 V for upward and downward SP, respectively. As before, the saw-tooth pulses sweeping from −0.1 V to 0.1 V were used for read-out. The anti-hysteretic behavior in the doping of graphene channel is observed again with the clear sign reversal of channel transconductance depending on the SP direction as noticed in Fig. 5c, d. As illustrated in Fig. 5e, the electrons transferred from the doping overlayer will be recombined with the holes in the graphene channel to reduce its p-type doping. If so, the write-in voltage for switching the SP downward to convert the graphene channel doping to n-type can decrease accordingly. This expectation indeed matches well with the measurements, confirming that −5 V is sufficient to turn the graphene channel into n-type. Another important notion is that the drain-to-source current and the channel transconductance were suppressed quite a lot, both over 10 times, compared with the case of no doping overlayer. This suppression is considered to be due to the Coulomb scattering from the charge impurities in the AlOx overlayer which reduces the carrier mobility in the graphene channel. Since the channel conductance and transconductance are proportional to the carrier mobility, the reduction of carrier mobility will deteriorate them apparently. The Ids–Vg curves sketched at the bottom of Fig. 5e represent this influence of carrier mobility reduction. Indeed, the carrier mobility reduction due to the AlOx overlayer varies somewhat noticeably from sample to sample. This variation is considered to stem mainly from the inconsistent ambient condition, especially humidity, for oxidizing the overlayer in air and the thickness difference of the overlayer. The Al film for forming the AlOx overlayer is very thin, targeted to be 2 nm. Hence, the deviation of its thickness from the target value, occurring during deposition, can be non-trivial. Differently from the FeGFET shown in Fig. 5, some FeGFETs show less reduction of transconductance. In addition to the counter-doping effect, the AlOx overlayer was found to improve the memory retention of FeGFET. Supplementary Fig. 4 shows the retention characteristics of FeGFET with the AlOx overlayer measured at room temperature and in vacuum (~10−3 Torr). Compared with the case of NO overlayer (Fig. 4a), the measured transconductance appears more stable. In the Al deposition process, the graphene channel stays in a high vacuum (~10−7 Torr) over an hour before starting the deposition. Accordingly, the water molecules residing in the gap between graphene and Al2O3 layer can be removed well, and the Al layer deposited subsequently can encapsulate the graphene channel to prevent water molecules from sneaking into the gap afterward. The improved retention of FeGFET with the AlOx overlayer is considered to signify the reduced number of water molecules in the gap between graphene and Al2O3 layer. By the way, the encapsulation of the Al layer will NOT be perfect since the complete surface coverage is hardly expected for only ~2 nm thick thin film. Therefore, the retention characteristics of FeGFET with the AlOx overlayer are also likely to deteriorate when the device sits in air. This tendency has actually been observed in our measurements.

Discussion

Based on the experimental data presented so far, it can be claimed that the proposed read-out scheme measuring the transconductance of graphene channel in FeGFET can be an efficient and reliable way to realize the selector-free random-access non-volatile memory in the form of a cross-point array (Fig. 1a). The configuration of transconductance measurement is established only for the crossing cell where the top row of graphene channel (bit line) and the bottom gate electrode (word line) are crossed perpendicularly with each other, enabling the random-access to an arbitrary memory cell without any selection device. The random-access aspect will be valid also for write-in since the switching of SP in the ferroelectric layer is driven by the electric field stemming from the voltage difference between the top graphene channel and the bottom gate electrode. If the voltages applied on the graphene channel and the bottom gate electrode are smaller in magnitude than the coercive voltage of the ferroelectric layer but their difference is beyond the coercive voltage, only the ferroelectric layer of the crossing cell will have a sufficiently large electric field to switch the SP in it. Another advantage of measuring transconductance is that the direction of SP can be sensed in non-destructive manners. This implies that there is no need to switch the SP momentarily for figuring out its direction by inducing a displacement current (conventional destructive read-out). The non-destructive read-out is a crucial factor for resolving the fatigue problem of the ferroelectric layer which is a long-standing weakness of the conventional ferroelectric memory31,32.

In conclusion, we proposed a new concept of read-out method for FeRAM with the bottom-gated FET structure composed of a graphene channel33,34 and a ferroelectric gate insulator and demonstrated its validity and reliability experimentally. The transconductance of the graphene channel was measured to have opposite signs for two opposite directions of SP in the underlying ferroelectric layer, which is the essential working principle of the proposed read-out method. The unambiguous sensing of SP direction, corresponding to the memory state of FeRAM, with transconductance measurements, makes it possible to construct an array of ferroelectric memory cells in the form of cross-point structure where the memory state of a crossing cell can be read out selectively without any additional selector. Accompanied by the voltage-driven fast switching of ferroelectric SP, this FeRAM structure can be a plausible solution for fabricating high speed, ultra-low power, long lifetime, and high density 3D stackable non-volatile memory. As compared in Table 2, its operational performances even might be comparable to the Si-based Dynamic Random Access Memory (DRAM), the most representative high-speed memory, with an additional benefit of being non-volatile.

Methods

Device fabrication (more detailed)

As described previously, a 200 nm thick PZT (Pb1.1Zr0.35Ti0.65O3) ferroelectric layer was grown with the sol–gel process on a Pt/Ti/SiO2/Si substrate. The Pt/Ti (150 nm/10 nm) stacked layer was used as the back-gate electrode. After cleaning the surface of PZT film consecutively with acetone and methanol in an ultrasonic bath for 5 min each, a 15–30 nm thick Al2O3 film was deposited by using ALD at 250 °C. The trimethylaluminum (TMA) and H2O were used as the precursor and the oxidant, respectively. Then, a single layer of CVD graphene was transferred onto the Al2O3 surface by using the semi-dry transfer method where the graphene layer supported by a Polymethyl Methacrylate (PMMA) layer is transferred directly on the surface with the aid of an additional flexible supporter (Kapton tape) attached to the PMMA layer of PMMA/graphene stack. After the graphene transfer, the photoresist etch mask was patterned with the photolithography process which consists of spin-coating Hexamethyldisilazane (HMDS) and AZ5214E photoresist layers successively (HMDS: 1500 rpm for 30 s, AZ5214E: 4000 rpm for 30 s), exposing the coated layers to ultraviolet light with the power of 100 mJ/cm2, and developing the exposed areas with AZ300MIF developer for 60 s. Then, the portion of graphene film uncovered with the photoresist mask was etched with O2 plasma to form a strip-shaped graphene channel of ~10 μm width. Finally, the source and drain electrodes were formed on both ends of the graphene channel by depositing Au/Ti (50 nm/10 nm) film stacks on the patterned photoresist layer with electron beam (e-beam) evaporation and performing the lift-off process in acetone over a day. Excluding the area of the graphene channel covered with the source and drain electrodes, the actual channel length of the fabricated FeGFET is ~20 μm. For the AlOx doping overlayer, a ~2 nm thick Al film pattern covering the entire width of graphene channel was formed by using photolithography, e-beam evaporation, and lift-off process in successive manners, and then it was oxidized in the atmosphere over a day.

Data availability

The datasets generated and/or analyzed during the current study are available from the corresponding author on reasonable request.

References

Meena, J. S., Sze, S. M., Chand, U. & Tseng, T. Y. Overview of emerging nonvolatile memory technologies. Nanoscale Res. Lett. 9, 526 (2014).

Han, S. T., Zhou, Y. & Roy, V. A. L. Towards the development of flexible non-volatile memories. Adv. Mater. 25, 5425–5449 (2013).

Bez, R. & Pirovano, A. Non-volatile memory technologies: emerging concepts and new materials. Mater. Sci. Semicond. Process. 7, 349–355 (2004).

Huang, F. et al. HfO2-based highly stable radiation-immune ferroelectric memory. IEEE Electron Device Lett. 38, 330–333 (2017).

Sharma, A. & Roy, K. 1T non-volatile memory design using sub-10nm ferroelectric FETs. IEEE Electron Device Lett. 39, 359–362 (2018).

Ni, Y., Wang, Y. & Xu, W. Recent process of flexible transistor-structured memory. Small 17, 1905332 (2021).

Scott, J. F. & De Araujo, C. A. P. Ferroelectric memories. Science 246, 1400–1405 (1989).

Zhao, D. et al. Polarization fatigue of organic ferroelectric capacitors. Sci. Rep. 4, 5075 (2014).

Ma, T. P. & Han, J. P. Why is nonvolatile ferroelectric memory field-effect transistor still elusive? IEEE Electron Device Lett. 23, 386–388 (2002).

Jung, S. et al. Giant electroresistance in edge metal-insulator-metal tunnel junctions induced by ferroelectric fringe fields. Sci. Rep. 6, 30646 (2016).

Lee, S. & Lee, Y. Graphene/lead-zirconate-titanate ferroelectric memory devices with tenacious retention characteristics. Carbon 126, 176–182 (2018).

Kim, W. Y. et al. Graphene-ferroelectric metadevices for nonvolatile memory and reconfigurable logic-gate operations. Nat. Commun. 7, 10429 (2016).

Zheng, Y. et al. Gate-controlled nonvolatile graphene-ferroelectric memory. Appl. Phys. Lett. 94, 163505 (2009).

Zheng, Y. et al. Graphene field-effect transistors with ferroelectric gating. Phys. Rev. Lett. 105, 166602 (2010).

Zhang, X. et al. Single-layer graphene field-effect transistors with ferroelectric PZT gate. in Proc. 12th IEEE International Conference on Solid-State and Integrated Circuit Technology (ICSICT). 1–3 (Guilin, China, 2014).

Zafar, Z. et al. Nonvolatile memory based on molecular ferroelectric/graphene field effect transistor. ACS Appl. Mater. Interfaces 10, 39187–39193 (2018).

Xu, W. et al. Supra-binary polarization in a ferroelectric nanowire. Adv. Mater. 33, 2101981 (2021).

Kim, G. H. et al. Schottky diode with excellent performance for large integration density of crossbar resistive memory. Appl. Phys. Lett. 100, 213508 (2012).

Son, M. et al. Excellent selector characteristics of nanoscale VO2 for high-density bipolar ReRAM applications. IEEE Electron Device Lett. 32, 1579–1581 (2011).

Sarma, S. D., Adam, S., Hwang, E. H. & Rossi, E. Electronic transport in two-dimensional graphene. Rev. Mod. Phys. 83, 407 (2011).

Geim, A. K. & Novoselov, K. S. The rise of graphene. Nat. Mater. 6, 183–191 (2007).

Hong, X. et al. Unusual resistance hysteresis in n-layer graphene field effect transistors fabricated on ferroelectric Pb(Zr0.2Ti0.8)O3. Appl. Phys. Lett. 97, 033114 (2010).

Baeumer, C., Rogers, S. P., Xu, R., Martin, L. W. & Shim, M. Tunable carrier type and density in graphene/PbZr0.2Ti0.8O3 hybrid structures through ferroelectric switching. Nano Lett. 13, 1693–1698 (2013).

Rajapitamahuni, A., Hoffman, J., Ahn, C. H. & Hong, X. Examining graphene field effect sensors for ferroelectric thin film studies. Nano Lett. 13, 4374–4379 (2013).

Kurchak, A. I. & Strikha, M. V. Antihysteresis of the electrical resistivity of graphene on a ferroelectric Pb(ZrxTi1−x)O3 substrate. J. Exp. Theor. Phys. 116, 112–117 (2013).

Kim, Y. J. et al. Voltage drop in a ferroelectric single layer capacitor by retarded domain nucleation. Nano Lett. 17, 7796 (2017).

Jung, S. et al. Reduction of water-molecule-induced current-voltage hysteresis in graphene field effect transistor with semi-dry transfer using flexible supporter. J. Appl. Phys. 125, 184302 (2019).

Goniszewski, S. et al. Correlation of p-doping in CVD graphene with substrate surface charges. Sci. Rep. 6, 22858 (2016).

Song, S. M. & Cho, B. J. Investigation of interaction between graphene and dielectrics. Nanotechnology 21, 335706 (2010).

Henderson, M. A. The interaction of water with solid surfaces: fundamental aspects revisited. Surf. Sci. Rep. 46, 1–308 (2002).

Singh, D. & Garg, A. The combined effect of mechanical strain and electric field cycling on the ferroelectric performance of P(VDF-TrFE) thin films on flexible substrates and underlying mechanisms. Phys. Chem. Chem. Phys. 18, 29478–29485 (2016).

Tagantsev, A. K., Stolichnov, I., Colla, E. L. & Setter, N. Polarization fatigue in ferroelectric films: Basic experimental findings, phenomenological scenarios, and microscopic features. J. Appl. Phys. 90, 1387–1402 (2001).

Ferrari, A. C. et al. Raman spectrum of graphene and graphene layers. Phys. Rev. Lett. 97, 187401 (2006).

Ferrari, A. C. Raman spectroscopy of graphene and graphite: Disorder, electron-phonon coupling, doping and nonadiabatic effects. Solid State Commun. 143, 47–57 (2007).

Acknowledgements

This work was supported by Samsung Research Funding & Incubation Center of Samsung Electronics under Project Number SRFC-TA1903-02 and also by Next-Generation Intelligent Semiconductor Technology Development Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Science and ICT (2020M3F3A2A02082437). This work has also benefited from the use of the facilities at UNIST Central Research Facilities.

Author information

Authors and Affiliations

Contributions

S.J., J.P., and K.P. conceived and designed the device structure and the experiments. S.J., J.P., J.K., and W.S. fabricated FeGFETs. S.J., J.P., J.J., H.P., and M.S. performed the electrical characterization for the fabricated devices. S.J., J.P., J.K., W.S., J.J., M.S., and K.P. analyzed the measured data. S.J., J.P., J.K., W.S., J.J., H.P., M.K., S.K., M.S., I.W.K., T.H.K., and K.P. discussed the results and wrote the paper.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Jung, S., Park, J., Kim, J. et al. Self-selective ferroelectric memory realized with semimetalic graphene channel. npj 2D Mater Appl 5, 90 (2021). https://doi.org/10.1038/s41699-021-00272-7

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41699-021-00272-7