Abstract

In this paper, a new topology is introduced for capacitor-based multi-level inverters. The proposed topology is based on combination of two Cross-Square-Switched T-Type inverters. This structure can be generalized in two modular and cascaded modes. In the cascaded mode, higher voltage levels are produced with low power switches. The main features of the proposed topology include the level generation without the utilization of the H-bridge module, the low number of switching components, a lower number of DC voltage sources, and low total blocking voltage. Besides, in the proposed topology, the number of conducting switches in the current path for each different voltage level is low, which leads to a conduction loss decrement. The loss simulations are performed, and the results are presented. A study provides a detailed comparison of the proposed topology in terms of various parameters. In this paper, the nearest level modulation switching, which is low-frequency switching, is utilized to generate voltage levels. To confirm the performance of the proposed topology, a simulation was performed with MATLAB/Simulink software, and a laboratory sample was implemented. Comparative results, simulation results, and implementation results indicate the appropriate performance of the proposed structure in different steady-state and dynamic conditions.

Similar content being viewed by others

Introduction

Since interconnecting a two-level inverter to a high-voltage network is not possible, with the growing development of renewable energy resources such as photovoltaic arrays and wind energies, the demand for the progress of high-voltage, high-power inverters have increased. Multi-level inverters (MLIs) are a suitable solution for this purpose, where new topologies are being developed. MLIs include power electronics switches and DC sources that generate different voltage levels from a combination of voltage sources. The main feature of MLIs compared to two-level inverters is generating voltage waveforms with better quality and close to the sine waves, which this improvement in voltage waveform will reduce the total harmonic distortion. Other features of MLIs are switching loss reduction, low voltage stress of switches, high-quality output power, less electromagnetic interference, etc.1,2,3,4,5.

Traditional MLIs mainly consist of three categories, which include neutral point clamped (NPC), flying capacitor (FC), and cascading H bridge (CHB). NPC and FC MLIs utilize multiple capacitors to generate voltage levels, making these configurations challenging in regulating the voltage of these capacitors. Moreover, with increasing the number of voltage levels at the output of these MLIs, the number of capacitors and power switches increases6,7,8,9. Due to the increment in the number of components, the power circuit of these MLIs will be complicated, and it will also involve a complex control scheme. CHB MLIs consist of some H-bridge modules, which is connected in series. These MLIs do not require clamped or flying capacitors. Additionally, CHB MLIs have advantages such as modularity, simple control, reliability, and utilizing low-power switches10,11. The CHB MLIs are divided into symmetric and asymmetric topologies in terms of equal or unequal input voltage sources. In the first category, the DC voltage sources have the same values, whereas this configuration has good modularity. Nevertheless, in the second category, the DC voltage source values are different and unequal. In this type of configuration, the number of output voltage levels rises using the number of switches equal to the symmetric topology. Traditional MLIs have one major drawback, and that is a large number of switches, which becomes a significant issue at higher voltage levels11,12.

In MLIs, the quality of the output voltage improves with an increasing number of output voltage levels10. The principal challenge for MLIs is the number of switches, the number of gate-drivers, and the number of circuit components, which severely increase with the increasing output voltage levels. This increment in the number of components will increase the volume, cost, and complexity. Accordingly, it is tried to minimize the number of circuit components of MLIs for high voltage levels13,14,15,16,17,18,19,20.

The necessity for multiple DC voltage sources is also a significant challenge for MLIs. This challenge is significant in CHBs, which have many voltage sources. In some studies, capacitors have been utilized instead of some DC voltage sources to reduce the number of DC voltage sources in the CHB structure13,14,15. In these configurations, capacitor voltage control is complex, and the process of charging and discharging the capacitor voltage may not be complete, and the output voltage may include unwanted harmonics. Some MLIs use only one DC voltage source to generate multi-level voltage, known as a switched-capacitor structure. In some of these configurations, the procedure of charging capacitors is complex and does not have a modular structure. In these configurations, a DC voltage source provides all the power required, which may not be suitable for high power applications. In addition, in these configurations, because the output power must be supplied by a DC source, the DC input current is high, which increases the conduction losses of the switches and thus reduces the efficiency of these configurations10.

In MLIs used for high power, utilizing a structure based on a single DC source is not appropriate, and to provide high power, using some DC voltage sources is inevitable. In some topologies, a DC-DC interface circuit is utilized to increase the number of DC voltage sources9. The DC-DC interface circuit can increase one voltage source to several voltage sources. However, this circuit has circuit elements such as inductors, capacitors, diodes, and switches that increase the volume of the circuit. So, this approach is not a practical solution to supply the required number of DC sources. Furthermore, the total efficiency of the converter will be reduced simply because of adding such a single-input multiple-output DC-DC converter.

The proposed multi-level inverter offers an improved arrangement in which the switches are designed to maximize the number of output voltage levels with limited circuit components. This paper introduces a cross-square-switched T-type (CSST-type) topology that is capable of operating with both equal and unequal sources. The proposed topology in unequal configuration can be implemented in both incremental and decremental combinations, which further increases the output voltage levels. The number of conducting switches at each of the voltage levels is small in the proposed topology, which will reduce the conduction losses. Additionally, the voltage stress of the proposed topology switches is low, and high output power can be achieved with low power switches. The proposed topology reduces the number of DC voltage sources to 2 by providing the voltage division between the capacitors and requires only 2 DC voltage sources. Moreover, the proposed topology can be developed in series and provide a cascaded structure in which the number of output voltage levels will be increased significantly.

“CSST-type topology” section of this paper discusses the principles of CSL-type MLI operation, including basic cell configuration, generalized structure configuration, voltage sources reduction, cascaded structure, and symmetric and asymmetric topologies. Power losses and efficiencies are calculated in “Loss-thermal analysis” section. Comparative studies are presented in “Comparing the proposed MLI configuration with other configurations” section. simulation results followed by laboratory results are presented in Sect. “Simulation and laboratory results”.

CSST-type topology

The proposed structure

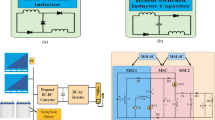

In The CSST configuration utilizes the T-type module, which is displayed in Fig. 1. As Fig. 1 demonstrates, the T-type module consists of N DC sources, and N − 1 bidirectional switches. The t-type module only produces positive voltage levels and requires an H bridge to generate negative voltage levels.

The proposed CSST-type structure configuration consists of two back-to-back three-level T-type modules. T-type modules are connected with a cross-square-switched module. The configuration of the proposed CSST-type structure is shown in Fig. 2. The proposed CSST-type structure consists of two parts: the right part, which is labeled R, and the left part, which is labeled L. Due to the inverse connection of the T-Type module on the left and right, the output voltages of these two modules are added together at the output of the proposed structure, and the number of output voltage levels increases. The proposed CSST-type structure can be used in both equal or unequal modes. In the unequal mode, the sources can be incremental/decremental combinations, thus providing more output levels. As the number of output voltage levels increases, the voltage THD decreases considerably.

In the proposed CSST-type structure, each T-type module utilizes two DC sources. In this case, the number of resources is significant, and providing this number of resources is a big challenge. To reduce the number of sources in the proposed CSST-type cell configuration, voltage division is used between capacitors. With this approach, the number of structure resources is declined to 2. Figure 3 presents the proposed CSST-type cell configuration by reducing the number of sources by voltage division method.

In the DC source reduction configuration, the capacitor is used to divide the voltage of the DC sources, and the voltage of the capacitors is equal to:

The proposed CSST-type structure does not require a side circuit (one-input multi-output DC-DC converter) to balance the voltage of the capacitors by reducing the number of DC sources and using capacitors. In other words, the proposed structure can automatically adjust the voltage of the capacitors. The proposed CSST-type structure consists of 2 sources that can be designed in equal and unequal modes. In equal topology, the proposed structure can produce nine voltage levels. In the equal topology, the proposed CSST-type structure can generate voltage levels only as an incremental combination of capacitor voltages. In other words, in generating different output voltage levels, it is only possible to add the voltage of the capacitors together. In this topology, the VR and VL voltage sources are equal to VDC, and different modes of generating voltage levels are presented in Table 1.

As Table 1 displays, the (S1, S2), (S3, S4), and (S5, S6) switch pairs act as complementary and never turn on together. Besides, the number of switching modes of the CSST-type structure in generating 0, ± 1, ± 2, ± 3 voltage levels has more than one switching, which is a helpful feature in space vector modulation. In space vector modulation, the switching state is selected to have the most minor change in switching states to reduce switching losses21.

The total blocking voltage (TBV) of the Multi-level structure is calculated from the maximum blocking voltage (MBV) of the switches. The maximum voltage across the switch in the off mode determines the voltage stress of the switches. The maximum blocking voltage of the proposed CSST-type switches is given by the following equations:

In the equal topology, since the size of the VR and VL voltage sources is equal to VDC, the proposed TBV of the proposed CSST-type cell is obtained as follows:

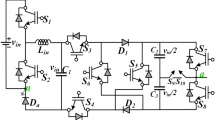

In the unequal topology, the ratio of the size of the left and right voltage sources of the proposed CSST-type structure is 1:5. In other words, the VL voltage source is equal to VDC, and VR is equal to 5VL = 5VDC. In an unequal topology, the combination of voltage sources is incremental/decremental. In other words, in the different output voltage level generation, in addition to the possibility of adding the voltage of the capacitors together, it is also possible to subtract the voltage of the capacitors from each other. This leads to a significant increase in the number of output voltage levels, and the unequal topology of the proposed structure can produce 25 levels. Figure 4 displays the different modes of positive voltage level generation. This figure illustrates the current path and light switches in red. The negative voltage levels are obtained in the same way.

The maximum blocking voltage of the proposed CSST-type structure switches is obtained by Eq. (3)–(8), which for an unequal topology, the TBV value is equal to:

The value of TBV in both equal and unequal modes is low due to the number of voltage levels produced, indicating that the voltage range of the switches is low.

The proposed modular structure

The proposed CSST-type structure can be generalized in both modular and cascading methods. The configuration of the modular CSST-type structure is presented in Fig. 5. In this configuration, T-type cells are generalized modularly, for which bidirectional switches are added to T-type cells.

The modular CSST-type configuration has several distinctive features that are mentioned. (1) To extend the output levels to higher levels, only one bidirectional switch is added to the structure. Each bidirectional switch requires only one driver. Thus, the number of drivers in this configuration will be low at high voltage levels. (2) The number of DC voltage sources in this configuration is only two. (3) This configuration can be designed with both equal and unequal sources. (4) The number of active switches and current conductors at different voltage levels is only three switches, which will reduce the conduction losses.

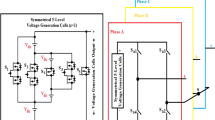

The number of switches (NS), number of gate drivers (NGD), number of capacitors (NC), and number of sources (NDC) of the modular CSST-type configuration are as follows:

N and M are the numbers of bidirectional switches on the left and right of the modular CSST-type configuration. In the equal topology, the voltage source ratio of the modular CSST-type configuration is 1:1. In the unequal topology of the modular structure, the number of source voltages can be selected based on the following:

The CSST-type cascade configuration consists of the Z number of the basic CSST-type structure shown in Fig. 6. The purpose of providing cascade configuration is to achieve high voltage levels using low voltage and power switches.

The number of switches (NS), number of gate drivers (NGD), number of capacitors (NC), and number of sources (NDC) in the cascading CSST-type configuration are as follows:

To determine the size of voltage sources of cells, many algorithms can be used. Table 2 presents some examples of possible algorithms. In this table, \(\hat{V}_{{O_{z} }}\) is the output voltage level peak of the Zth cell. In the third algorithm, the number of levels increases sharply. With two CSST-type cells, it is possible to generate 625 voltage levels at the output.

Loss-thermal analysis

The power semiconductor devices, such as DC-DC converters, rectifiers, matrix converters, and two-level or multi-level inverters, generally have two types of loss, which are: conduction loss (Pc) and switching loss (Psw). The conduction loss is due to the internal resistance and voltage drop in the ON state of the semiconductor devices. This loss consists of the conduction loss of IGBT or MOSFET, and its anti-parallel diode, denoted by (Pc,s) and (Pc,d), respectively. These losses are calculated by the following Equations:

where Vs,ON and Vd,ON are the voltage drop when the switch or its anti-parallel diode is turned on. The resistances Rs, Rd, are the internal resistance of the switch or its anti-parallel diode, and α is a constant coefficient that depends on the specifications of the switch. These parameters are prepared in the datasheet of the switches by the manufacturer. The following Equation is used to calculate the average conduction loss of all switches and their anti-parallel diodes in an output period:

Another part of the semiconductor power loss is switching loss. The switching loss is due to the non-ideal performance of power semiconductor devices. In order to calculate the switching loss, it is assumed that the voltage and current of the switch change linearly when it is turned on and off. Therefore:

where ts,ON and ts,OFF are the time intervals required to turn a switch on and off, Es,ON and Es,OFF are the energy dissipation of the switch at the moments of turning on and turning off, and fs represents the switching frequency. So, the total loss of a switch (PT) is the sum of the conduction loss of the switches and their anti-parallel diodes, as well as the switching loss, presented in Eq. (25).

Also, the efficiency of the converter is calculated according to (25):

The switching and conduction loss considering the thermal model of power electronics components is simulated in MATLAB/Simulink software. The performance of the proposed CSST-type structure is investigated in both symmetric and asymmetric topologies at pure resistance load, where the peak voltage of the load is considered to be 400 V. The parameters of the IGBT IKFW60N60DH3E switch is used for this simulation. The simulation is conducted based on Pulse Width Modulation (PWM) switching pattern. The efficiency of the proposed CSST-type structure for both symmetric and asymmetric topologies in terms of output power from light load to full load is shown in Fig. 7. The total loss, the output power, and the efficiency of the proposed CSST-type structure in symmetric topology for two different output loads (Z1 = 10 Ω + 25mH), (Z2 = 5 Ω + 25 mH) are demonstrated in Fig. 8a. In addition, the loss and temperature of the switches are demonstrated separately in Fig. 8b,c.

Comparing the proposed MLI configuration with other configurations

In this section, a comparison is made to demonstrate the advantages of the proposed CSST-type configuration. The comparison is based on the number of components in the proposed configuration compared to the classic multi-level inverter topologies and new reduced components. In this section, the output voltage levels of inverters (NL) are compared to the number of switches (NSwitch), number of gate drivers (NGD), number of DC sources (NDC), number of capacitors (NC), and TBV of the switches. Table 3 compares the proposed CSST-type structure with other new structures. In this table, in addition to the mentioned parameters, the number of active switches (NAS), the number of diodes (ND), the demand for an H-bridge to generate negative polarity, the need for a DC-DC interface circuit to reduce the number of DC sources, number of switches to the number of output levels (NSwitch/NL), and DC voltage ratio (VDC ratio) are also presented.

Switches are a critical element in the structure of multi-level inverters, which increase the output voltage levels, and the number of switches. As the number of switches and circuits of multi-level inverters grows, the cost, complexity, and size of the circuit increases. Figure 9 compares the number of proposed CSST-type structure switches with the number of output levels in the unequal mode. Figure 9 demonstrates that the CSST-type topology has a smaller number of switches than other similar structures, decreasing the cost and complexity of the circuit.

A large number of drivers in multi-level inverters increases the cost. Each switch requires a gate driver to be turned on and turned off, which boosting the gate pulses of the micro-controller is the gate driver's duty. Bidirectional switches will need only one driver if designed as a common-emitter. In a modular CSST-type configuration, a bidirectional switch is required to generate two additional voltage levels. Therefore, the number of drivers in the proposed CSST-type configuration is low. Figure 10a compares the number of proposed CSST-type structure drivers with other topologies. The number of drives used in the proposed CSST-type structure is lower than other topologies. TBV of the proposed CSST-type structure is compared with other topologies in Fig. 10b. It can be seen from Fig. 10b that the TBV value of the proposed CSST-type modular structure is lower than other structures.

The number of independent voltage sources in multi-level inverters is one of the significant challenges. Providing a large number of sources in multi-level inverters is a huge problem. Figure 11 displays the number of independent voltage sources of the proposed CSST-type structure with other topologies. Based on this figure, the number of independent voltage sources of the proposed topology is very low. The number of sources of the proposed structures in15,18,19 is equal to the proposed topology. However, in these structures, the interface circuit is used to balance the voltage of the capacitors. The interface circuit consists of circuit elements such as switches, diodes, inductors, and capacitors, which increase the complexity of the whole system and decrease its efficiency. Besides, the number of switches, drivers, and TBV of the structures presented in15,18,19 are high.

Simulation and laboratory results

In this section, simulation and laboratory results are presented to confirm and validate the proposed CSST-type structure. The simulated and implemented version of the proposed CSST-type structure is controlled and switched by the nearest surface modulation (NLM) method. The results of the proposed CSST-type structure are presented for both equal and unequal modes, and information on circuit parameters is presented in Table 4. Figure 12 displays the control method in the laboratory sample. As this figure shows, the range of pulses generated by the Arduino microcontroller is 5 V, and to drive the MOSFETs, a pulse signal with an approximate range of 15 V is required, which is done by the driver circuit with the help of TLP250 Optocoupler. Figure 13 presents a laboratory sample of the proposed CSST-type structure.

Figure 14 demonstrates the voltage and current waveforms of the capacitors in the equal mode and the harmonic voltage spectrum. Figure 14a displays the simulation and implementation results of the proposed CSST-type structure at a purely resistive load (Z = 30 Ω); Fig. 14b displays similar results in the resistive-inductive output load (Z = 60 Ω + 100mH), and Fig. 14c demonstrates the harmonic voltage spectrum of the load. The nine-level voltage THD of the load in the equal mode is 9.29%, and all harmonic degrees are less than 3%. Figure 15 displays the voltage and current waveform of a load in the equal mode under dynamic conditions and exchange for an instantaneous change in the size of the output resistive-inductive impedance (Z = 53 Ω + 80 mH) to a pure resistive load (Z = 18 Ω). According to this figure, the proposed structure can feed the variable output load correctly in the dynamic conditions of instantaneous change of output load size.

Figure 16 displays the reverse voltage of the switches of the proposed CSST-type structure. Based on these figures, the maximum blocking voltage of each switch and the total blocking voltage of the converter can be evaluated. Based on this figure, the correctness of Eqs. (3)–(8) are available.

Figure 17 displays the voltage and current waveform of the load and the voltage of the capacitors, and the harmonic voltage spectrum for unequal topology according to the values in Table 4. Figure 17a presents the simulation and implementation results of the proposed CSST-type structure in pure resistive load with Z = 36 Ω, Fig. 17b shows the same results in resistive-inductive load with Z = 60 Ω + 90 mH, and Fig. 17c displays the harmonic voltage spectrum for unequal topology. In this case, the number of load voltage levels with the same number of circuit components has increased to 25 levels, and the output voltage THD has decreased by 3.25%. The THD value of the load voltage in unequal topology can meet the IEEE std. 519–2014 standard. According to this standard, the maximum allowable distortion of a certain harmonic in a low-voltage network (V ≤ 1 kV) is 5%, and in a medium voltage network (1 kV ≤ V ≤ 69 kV) is 3%. Moreover, the maximum allowable total harmonic distortion in a low-voltage network can be equal to 8%, and in a medium-voltage network can be equal to 5%32. In such cases, the volume and frequency of the output filter are significantly reduced and can lead to a reduction in the cost of the output filter of the multi-level inverter.

Figure 18 displays the voltage and current waveform of unequal topology for dynamic conditions in exchange for instantaneous change of the modulation index. Based on this figure, the proposed structure executes the dynamic conditions of modulation index change well and produces the appropriate output voltage in these dynamic conditions.

Figure 19 shows the output voltage and current waveform in the unequal mode under dynamic load change conditions (Z = 53 Ω + 80 mH to Z = 18 Ω). According to the dynamic test results (change in output load and modulation index) validate the real-time operation of the proposed MLI.

Comparing simulation results and laboratory results reveal that the resulting waveforms are well matched. The proposed structure correctly generates the required multi-level voltage under dynamic conditions such as changing the size, type of output load, and the modulation index. The voltage of the capacitors of the structure is well balanced without the necessity for a side circuit.

Conclusion

In this paper, a new capacitor-based multi-level inverter (MLI) topology is introduced to reduce components, including the number of switches and independent voltage sources. The proposed topology is derived from a combination of two Cross-Square-Switched T-Type (CSST-type). The proposed inverter topology can be utilized for both equal and unequal sources. This topology can also be generalized in two modular and cascading modes, in which higher voltage levels can be achieved using switches with a low voltage/power range in cascading mode. The advantages of the proposed topology include positive and negative level generation without the H bridge, the low number of switching devices, the lower number of DC sources, and the acceptable blocking voltage. Besides, in the proposed structure, there are a small number of current-conducting switches at different voltage levels, which increases the efficiency of the converter. The efficiency of the proposed topology at the output power of 10 kW is about 98%, and the loss-temperature analysis of each switch indicates the uniform temperature distribution of each of the switches of the proposed structure. Additionally, in the unequal THD mode, the output voltage is only 3.25% which can pass the IEEE standard. To confirm the performance of the proposed topology, simulation and laboratory results are presented in different load modes, dynamic load change, and modulation index change modes, and the correct performance of the proposed structure is illustrated.

Data availability

All data generated and analysed during the current study are available from the corresponding author on reasonable request.

References

Sarebanzadeh, M. et al. A 15-level switched-capacitor multilevel inverter structure with self-balancing capacitor. IEEE Trans. Circuits Syst. II Express Briefs 69(3), 1477–1481 (2021).

Zheng, Z. et al. A hybrid cascaded multilevel converter for battery energy management applied in electric vehicles. IEEE Trans. Power Electron. 29(7), 3537–3546 (2013).

Omer, P., Kumar, J. & Surjan, B. S. A review on reduced switch count multilevel inverter topologies. IEEE Access 8, 22281–22302 (2020).

Gupta, K. K. et al. Multilevel inverter topologies with reduced device count: A review. IEEE Trans. Power Electron. 31(1), 135–151 (2015).

Bughneda, A. et al. Review of multilevel inverters for PV energy system applications. Energies 14(6), 1585 (2021).

Sochor, P. & Akagi, H. Theoretical comparison in energy-balancing capability between star-and delta-configured modular multilevel cascade inverters for utility-scale photovoltaic systems. IEEE Trans. Power Electron. 31(3), 1980–1992 (2015).

Hosseinpour, M., Seifi, A. & Babaei, E. An improved switched-ladder bidirectional multilevel inverter: Topology, operating principle, and implementation. Int. J. Circuit Theory Appl. 49(12), 4274–4293 (2021).

Essakiappan, S. et al. Multilevel medium-frequency link inverter for utility scale photovoltaic integration. IEEE Trans. Power Electron. 30(7), 3674–3684 (2014).

Seifi, A. et al A new generalized multilevel inverter topology based on cascaded connection of basic units. In 2019 International Power System Conference (PSC). (IEEE, 2019).

Babaei, E., Kangarlu, M. F. & Sabahi, M. Extended multilevel converters: an attempt to reduce the number of independent DC voltage sources in cascaded multilevel converters. IET Power Electron. 7(1), 157–166 (2014).

Vemuganti, H. P. et al. A survey on reduced switch count multilevel inverters. IEEE Open J. Ind. Electron. Soc. 2, 80–111 (2021).

Babaei, E., Laali, S. & Alilu, S. Cascaded multilevel inverter with series connection of novel H-bridge basic units. IEEE Trans. Ind. Electron. 61(12), 6664–6671 (2014).

Shayeghi, H. et al. Developing a generalized multi-level inverter with reduced number of power electronics components. Sustainability 14(9), 5545 (2022).

Ali, J. S. M. et al. A new generalized multilevel converter topology based on cascaded connection of basic units. IEEE J. Emerg. Sel. Top. Power Electron. 7(4), 2498–2512 (2018).

Hosseini Montazer, B. et al. A generalized diode containing bidirectional topology for multilevel inverter with reduced switches and power loss. Int. J. Circuit Theory Appl. 49(9), 2959–2978 (2021).

Alishah, R. S. et al. A new switched-ladder multilevel converter structure with reduced power electronic components. J. Circuits Syst. Comput. 30(12), 2150217 (2021).

Siddique, M. D. et al. A new multilevel inverter topology with reduce switch count. IEEE Access 7, 58584–58594 (2019).

Alishah, R. S. et al. A new general multilevel converter topology based on cascaded connection of submultilevel units with reduced switching components, DC sources, and blocked voltage by switches. IEEE Trans. Ind. Electron. 63(11), 7157–7164 (2016).

Alishah, R. S. et al. Optimal design of new cascaded switch-ladder multilevel inverter structure. IEEE Trans. Ind. Electron. 64(3), 2072–2080 (2016).

Jayabalan, M., Jeevarathinam, B. & Sandirasegarane, T. Reduced switch count pulse width modulated multilevel inverter. IET Power Electron. 10(1), 10–17 (2017).

Shalchi Alishah, R. et al. A new generalized cascade multilevel converter topology and its improved modulation technique. Int. J. Circuit Theory Appl. 49(4), 1103–1120 (2021).

Meraj, S. T., Hasan, K. & Masaoud, A. A novel configuration of cross-switched T-type (CT-type) multilevel inverter. IEEE Trans. Power Electron. 35(4), 3688–3696 (2019).

Selvaraj, S., Kumaresan, G. & Sathik, M. A. J. Modified “K”-type multilevel inverter topology with reduced switches, DC sources, and power loss. Int. Trans. Electr. Energy Syst. 30(5), e12345 (2020).

Siddique, M. D. et al. Optimal design of a new cascaded multilevel inverter topology with reduced switch count. IEEE Access 7, 24498–24510 (2019).

Samadaei, E. et al. An envelope type (E-Type) module: Asymmetric multilevel inverters with reduced components. IEEE Trans. Ind. Electron. 63(11), 7148–7156 (2016).

Ponraj, R. P., Sigamani, T. & Subramanian, V. A developed H-bridge cascaded multilevel inverter with reduced switch count. J. Electr. Eng. Technol. 16, 1445–1455 (2021).

Samadaei, E. et al. A square T-type (ST-type) module for asymmetrical multilevel inverters. IEEE Trans. Power Electron. 33(2), 987–996 (2017).

Panda, K. P., Bana, P. R. & Panda, G. A reduced device count single DC hybrid switched-capacitor self-balanced inverter. IEEE Trans. Circuits Syst. II Express Br. 68(3), 978–982 (2020).

Gautam, S. P. Novel H-bridge-based topology of multilevel inverter with reduced number of devices. IEEE J. Emerg. Sel. Top. Power Electron. 7(4), 2323–2332 (2018).

Meraj, M. et al. A new variable frequency control of 49-level cascaded packed U-cell voltage source inverter. IEEE Trans. Ind. Appl. 55(6), 7537–7548 (2019).

Laali, S., & Nasiri‐Zarandi, R. New cascaded multilevel inverter with series connection of novel capacitor based basic units. In IET Power Electronics (2023).

Langella, R., Testa, A., & Alii, E. IEEE recommended practice and requirements for harmonic control in electric power systems. In IEEE recommended practice (IEEE, 2014).

Funding

This work is based upon research funded by Iran National Science Foundation (INSF) under project No. 4015899.

Author information

Authors and Affiliations

Contributions

Conceptualization, A.S., S.H.H., M.T.H., and M.H.; methodology, A.S.; software, A.S., and M.H.; validation, S.H.H., M.T.H., and M.H.; investigation, A.S., S.H.H., and M.T.H.; resources, S.H.H.; data curation, S.H.H.; writing—original draft preparation, A.S., S.H.H., and M.H..; supervision, S.H.H., M.T.H., and M.H..; Funding acquisition: A.S., and S.H.H.; Visualization: A.S.; writing—review and editing: A.S., S.H.H., M.T.H., and M.H.; project administration, A.S., and S.H.H.; Formal analysis: A.S., and M.H.,. All authors have read and agreed to the published version of the manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher's note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Seifi, A., Hosseini, S.H., Tarafdar Hagh, M. et al. Capacitor based topology of cross-square-switched T-type multi-level inverter. Sci Rep 14, 3166 (2024). https://doi.org/10.1038/s41598-024-53568-1

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-024-53568-1

This article is cited by

-

A 17-level quadruple boost switched-capacitor inverter with reduced devices and limited charge current

Scientific Reports (2024)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.