Abstract

The impact of spacer on the single event response of SOI FinFET at 14 nm technology node is investigated. Based on the device TCAD model, well-calibrated by the experimental data, it is found that the spacer presents the enhancement on single event transient (SET) compared with no spacer configuration. For single spacer configuration, due to enhanced gate control capability and fringing field, the increments in SET current peak and collected charge for HfO2 are the least with 2.21%, 0.97%, respectively. Four possible dual ferroelectric spacer configurations are proposed. The placement of ferroelectric spacer at S side and HfO2 spacer at D side brings to weaken SET with the variation in current peak and collected charge by 6.93%, 1.86%, respectively. The reason may be its enhanced gate controllability over the S/D extension region, which improves the driven current. With linear energy transfer increasing, SET current peak and collected charge present the trend of increase while the bipolar amplification coefficient reduces.

Similar content being viewed by others

Introduction

When an energetic particle strikes into the sensitive area of FinFET device, single event transient (SET) may be occurred by the diffusion and drift effects1,2,3. Due to the reduced parasitic capacitance from silicon-on- insulator (SOI) technology and the improved tolerance from thin fins, FinFET, with narrow silicon fin, combined with SOI and high k/metal gate stacked technology, brings benefits to radiation effects2,3,4. It was indicated that single event responses of FinFET may be significantly affected by ion hit angular, position and energy, supply voltage, device size and number of fins, technology node, and so on3,5,6,7. With the aggressive shrinking of device dimensions, spacer configuration and permittivity play the dominant roles in overall device performance8,9,10,11,12,13,14. It has been indicated that the device performance in terms of SS, current drivability, drain induced barrier lowering (DIBL) could be improved using an optimized spacer configuration13,14. However, at the best of our knowledge, no one has discussed the impact of spacer on single event response of FinFET.

In this paper, the single event response of spacer configuration and permittivity in SOI FinFET at 14 nm technology node is investigated. The rest of the paper is organized as follows: in Section II, FinFET device structure and fabrication processes flow are discussed. Section III presents the results and analyses of the impact of spacer on SET, followed by conclusions in Section IV.

Finfet model

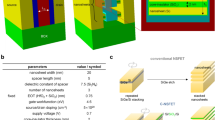

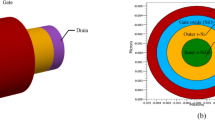

Based on TCAD, a 3D simulation model for n-type SOI FinFET at 14 nm technology node has been presented, shown in Fig. 1a–c. The gate is stacked with high-k dielectric material (HfO2) and metal contact (TiN). The length of the gate is 14 nm and the equivalent thickness of gate oxide is 0.5 nm. The width, height of fin is 10 nm, 18 nm, respectively. The length of S/D spacer is 33 nm. The channel silicon film is firstly uniformly p-type doped at a level of 5 × 1015 cm−3. The substrate silicon is uniformly p-type doped at a level of 1 × 1015 cm−3. Then, the S/D areas are Gaussian profile n-type doped with a peak value of 1 × 1021 cm−3. The extent S/D areas are also Gaussian profile n-type doped with a peak value of 8 × 1019 cm−3. The model fits well the experiment data3. In order to obtain accurate results, many physic models are included, such as, remote phonon scattering mobility model, Philips unified mobility model, Bohm quantum potential model, Shockley–Read–Hall (SRH) and Auger recombination models, heavy ion model, and so on3. For simulating the effects of high dielectric constants, polarization and hysteresis of ferroelectric materials (HZO), the Ferroelectric model is also set15. The permittivity of HZO is 22, and coercive field Ec = 1.0 MV/cm, remnant polarization Pr = 23 μC/cm2, saturated polarization Ps = 28 μC/cm216. The fabrication processes flow of the spacer configuration is shown in Fig. 1d. 17,18

Impact of spacer on set

The energetic particle hit the middle of fin between the drain and gate contact perpendicularly. The source and gate are connected to the ground and the drain of the device is set to 0.8 V. The linear energy transfer (LET) of the ion is 5 MeV cm2/mg. The strike has a radius of 10 nm and a delay time of 4 ps and the Gaussian profile has a characteristic time of 0.5 ps3,19. The run time is set to 1 ns.

Single configuration spacer variation on SET

In Ref.8, it has been indicated that FinFET with the high-k spacer material showed the concerning improvement of the performance parameters towards analog and RF design with a little compromise in speed of the device. The effects of the spacer materials with different dielectric constants on SET are investigated. For the single configuration spacer, low-k, high-k dielectric materials and ferroelectric materials are used, including Air (k = 1), SiO2 (k = 3.9), HfO2 (k = 25), HZO (k = 22). The direction of polarization is perpendicular to the fin surface by the same L-K parameters and thickness being used13. The drain currents and the collected charges are obtained, shown in Fig. 2. Here, the collected charge is achieved by integrating the simulated drain current over the transient duration.

It can be found that the spacer configuration impacts SET. As the spacer dielectric constant increases, the SET current peak presents in the trend of decrease. The relative decrement of SET current peak in single HfO2 spacer configuration is 2.21%. However, due to the spacer, the collected charges in all of the configurations are larger than that with no the spacer. The spacer exhibits non-monotonic trend of the collected charge. For low-k spacer, the collected charge increases with the dielectric constant increase. When the dielectric constant increases from 1 (Air) to 3.9 (SiO2), the relative increment in the collected charge varies from 0.15% to 6.43%. However, for high-k spacer, the trend in the collected charge presents different. The relative increments in the collected charge for HZO (k = 22) and HfO2(k = 25) spacer configurations are 4.92%, 0.97%, respectively. As well-known, the spacer generates the fringing field in the extension of source-to-gate and drain-to-gate. For the same physical thickness, the larger the dielectric constant of the material is, the smaller the equivalent thickness is. Therefore, it results in that the parasitic capacitances (CGS) formed between the source to the gate (or between the drain to the gate (CGD)) are larger and the generated surface potential of the channel is larger.

Figure 3 shows the distribution of the electron quantum potential in the device, where the similar conclusion can be obtained. Also, due to the polarization effect of the ferroelectric material, the fringing field is stronger. The fringing field promotes the charge collection by the drain contact. On the other hand, the spacer increases the equivalent gate length. With the same physical thickness, the larger the dielectric constant of the material is, the greater the gate control capability of on the channel is. This leads to the stronger counteraction effect on the drift and diffusion of electron–hole pairs. Under the common effects of the fringing field and the gate controllability, the formed electric field distribution in the channel is shown in Fig. 4. It can be found that the electric field intensities in the devices of Air and HfO2 spacer configurations are relatively weaker, resulting in a smaller amount of charges collected by the drain and a weaker SET in the drain. Because of the strong electric field intensities in the devices of SiO2 and HZO, the drain will collect more charge. However, the fringing electric field is enhanced due to the ferroelectric material polarization, which increases the current driven capability13. It has been indicated that the device with a larger driven current was better immunity to SET3,6. This means that the increase of the driven current leads to the decrease of the collected charge by the drain.

Dual configuration spacer variation on SET

It has been indicated that ferroelectric spacer strongly couples the gate fringing fields between the gate and S/D extension, which impacts the performance of the device13. In order to improve the performance of the device with spacer to harden SET, four possible dual spacer materials configurations are proposed, based on the spacer alignment, i.e., (D1) D-side HfO2 and S-side HZO; (D2) D-side HZO and S-side HfO2; (D3) D-side SiO2 and S-side HZO; (D4) D-side HZO and S-side SiO2. The drain currents are achieved, shown in Fig. 5.

It is clear that the SET current peaks decrease for D1 and D3 configurations compared with the other two configurations. The collected charges for D1 and D2 configurations are less than the other two configurations. It can be found that the configurations with D-side ferroelectric material will strengthen SET. The reason may be that due to the polarization effect, D-side ferroelectric material promotes the ionization electron–hole pairs collected by the drain contact while S-side ferroelectric material attracts some electron–hole pairs to the source contact, leading to less collected charges. Figure 6 shows the recombination rate and the electron concentration along the channel after the ion hit the devices with different spacer configurations. It can be found that on the side with ferroelectric spacer, such as S-side at D1, D-side at D2, shown in Fig. 6a, the electron concertation is more than that on the side with HfO2 or SiO2. The fact is consistent with the above mentioned reason. Due to the larger recombination rate in D1 configuration, shown in Fig. 6b, the amount of the collected charge by the drain at D1 is less.

Compared with no spacer, the collected charge increases by relative 3.74%, 9.68% for D2 and D4 configurations while that increases by relative 1.86%, 5.12% for D1 and D3 configurations, respectively. As mentioned above, the larger the dielectric constant of the spacer is, the more the gate control capability is. It results in decreasing the current peak and the collected charge. Compared with no spacer, the relative variation of the current peak for D1 and D2 is 6.93%, 2.98%, respectively. However, the relative decrement of the current peak for D3 and D4 is 1.97% and 0.87%, respectively. Therefore, D1 configuration is the best one to harden SET.

Figure 7 shows the impact of LET on SET with different spacer configurations. The range of LET is set from 1 MeV cm2/mg to 50 MeV cm2/mg. Here, the bipolar amplification coefficient is achieved by the ratio between the collected charge and the deposited charge, which is obtained by considering the Gaussian distribution of the ion track and the 3D geometry of the silicon body3.

It is clear that as LET increases, the SET current peak and the collected charge increase while the bipolar amplification coefficient decreases. When LET increases from 1 MeV cm2/mg to 50 MeV cm2/mg, the increment of the current peak for four configurations is 2538.0μA, 2576.5μA, 2532.6μA, 2549.3μA, respectively. Also, the increment of the collected charge for four configurations is 4.62fC, 4.76fC, 4.68fC, 4.68fC, respectively. The decrement of the bipolar amplification coefficient for four configurations is 4.64, 3.66, 4.71, 4.73, respectively. There is no significant variation in bipolar amplification coefficient for both configurations found when LET is larger than 30 MeV cm2/mg. However, when LET is smaller than 30 MeV cm2/mg, the bipolar amplification coefficient for D1 and D2 is always less than the other configurations. It can be concluded that SET for D1 configuration is weaker than the other configurations. Compared with no spacer3, the bipolar amplification effect for spacer configurations is strengthened at LET lower than 10 MeV cm2/mg while the bipolar amplification effect is reduced at LET more than 10 MeV cm2/mg. This means that the spacer improves the collection of the charge. Also, it reduces the collected charge when LET is more than 10 MeV cm2/mg.

Conclusion

With technology node scaled down, spacer configuration plays an important role in the overall device performance. Based on the calibrated 3D model for SOI FinFET at 14 nm technology node, the impact of spacer on SET is investigated for the first time. The single event responses in terms of current peak, collected charge and bipolar amplification coefficient for different spacer configurations and permittivity are obtained. The impacts of single spacer material and dual spacer placement with ferroelectric material on SET are analyzed and the potential mechanisms are also discussed. For single spacer configuration, SET for HfO2 spacer presents less increment in current peak and collected charge compared with no spacer configuration. For dual ferroelectric spacer configurations, the placement of FE spacer at the S side enhances the gate controllability over the extension region and thus improves the drive current, which weakens the single event response. The study of the single event response of all the possible ferroelectric spacer configurations in FinFET provides a great insight into the application of the device with enhanced the capability to harden SET under radiation environment.

Data availability

All data generated or analyzed during this study are included in this published article.

References

Saremi, M. et al. Physically based predictive model for single event transients in CMOS gates. IEEE Trans. Electron. Devices 63(6), 2248–2254 (2016).

Wu, W. et al. Line-edge roughness induced single event transient variation in SOI FinFETs. J. Semicond. 36(11), 114001 (2015).

Liu, B., Li, C., Zhou, P. & Zhu, J. Analysis of location and LET dependence of single event transient in 14nm SOI FinFET. Nucl. Instrum. Methods Phys. Res. Sect. B 530(8), 13–17 (2022).

Gaillardin, M. et al. High tolerance to total ionizing dose of Ω-shaped gate field-effect transistors. Appl. Phys. Lett. 88(22), 223511 (2006).

Zhang, H. et al. Angular effects of heavy-ion strikes on single-event upset response of flip-flop designs in 16-nm bulk FinFET technology. IEEE Trans. Nucl. Sci. 64(1), 491–496 (2017).

Harrington, R. C. et al. Effect of transistor variants on single-event transients at the 14-/16-nm bulk FinFET technology generation. IEEE Trans. Nucl. Sci. 65(8), 1807–1813 (2018).

Qin, J. R. et al. Temperature and drain bias dependence of single event transient in 25-nm FinFET technology. Chin. Phys. B 21(8), 089401 (2012).

Pradhan, K. P., Priyanka, M. & Sahu, P. K. Exploration of symmetric high-k spacer (SHS) hybrid FinFET for high performance application. Superlattices Microstruct. 90, 191–197 (2016).

Gupta, S. & Nandi, A. Effect of air spacer on analog performance of underlap tri-gate FinFET. Superlattices Microstruct. 109, 693–701 (2017).

Dwivedi, S., & Saini, G. Effect of random dopant fluctuation in nanoscale junctionless FinFET using low and high-k spacers. 8th ICCCNT 2017, July 3–5, 2017, IIT Delhi, Delhi, India, 40222 (2017)

Jain, N. & Raj, B. Impact of underlap spacer region variation on electrostatic and analog performance of symmetrical high-k SOI FinFET at 20 nm channel length. J. Semicond. 38(12), 122002 (2017).

Cheng, K. et al. Improved air spacer for highly scaled CMOS technology. IEEE Trans. Electron Devices 67(12), 5355–5361 (2020).

Chauhan, V., Samajdar, D. P., Bagga, N. & Dixit, A. A novel negative capacitance FinFET with ferroelectric spacer: proposal and investigation. IEEE Trans. Ultrason. Ferroelectr. Freq. Control 68(12), 3654–3657 (2021).

Sreenivasulu, V. B. & Narendar, V. Performance improvement of spacer engineered n-type SOI FinFET at 3-nm gate length. Int. J. Electron. Commun. (AEÜ) 137, 153803 (2021).

ATLAS User’s Manual. SILVACO International Inc, www.silcaco.com (2012)

Li, H. M., Hou, P. F., Wang, J. B., Song, H. J. & Zhang, X. L. Single-event-upset effect simulation of HfO2-based ferroelectric field effect transistor read and write circuits. Acta Phys. Sin. 69(9), 098502 (2020) ((in Chinese)).

Raju, V., PankajNelapati, R. & Sivasankaran, K. Impact of device geometrical parameter variation on RF stability of SELBOX Inverted-T Junctionless FinFET. SILICON 13, 2605–2617 (2021).

Lin, Y. K. et al. Spacer Engineering, in Negative capacitance FinFETs. IEEE Electron. Device Lett. 40(6), 1009–1012 (2019).

D’Amico, J. V. IV. et al. Single-event upsets in a 7-nm bulk FinFET technology with analysis of threshold voltage dependency. IEEE Trans. Nucl. Sci. 68(5), 823–829 (2021).

Funding

This work was supported by the National Natural Science Foundation of China under Grant No. 11975311, 11405270.

Author information

Authors and Affiliations

Contributions

All authors contributed to the study conception and design. Conceptualization, methodology, writing- reviewing and editing, validation, and data curation were performed by B.L. Original draft preparation, visualization and formal analysis were done by J.Z. All authors read and approved the final manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher's note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Liu, B., Zhu, J. Single event response of ferroelectric spacer engineered SOI FinFET at 14 nm technology node. Sci Rep 13, 11111 (2023). https://doi.org/10.1038/s41598-023-36952-1

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-023-36952-1

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.