Abstract

For two-dimensional electron gas device applications, it is important to understand how electrical-transport properties are controlled by gate voltage. Here, we report gate voltage-controllable hysteresis in the resistance–temperature characteristics of two-dimensional electron gas at LaAlO3/SrTiO3 heterointerface. Electron channels made of the LaAlO3/SrTiO3 heterointerface showed hysteretic resistance–temperature behavior: the measured resistance was significantly higher during upward temperature sweeps in thermal cycling tests. Such hysteretic behavior was observed only after application of positive back-gate voltages below 50 K in the thermal cycle, and the magnitude of hysteresis increased with the applied back-gate voltage. To explain this gate-controlled resistance hysteresis, we propose a mechanism based on electron trapping at impurity sites, in conjunction with the strong temperature-dependent dielectric constant of the SrTiO3 substrate. Our model explains well the observed gate-controlled hysteresis of the resistance–temperature characteristics, and the mechanism should be also applicable to other SrTiO3-based oxide systems, paving the way to applications of oxide heterostructures to electronic devices.

Similar content being viewed by others

Introduction

Since the discovery of a two-dimensional electron gas (2DEG) at the all-oxide LaAlO3 (LAO)/SrTiO3 (STO) heterointerface and the ensuing exploration for its various novel properties such as superconductivity1, ferromagnetism2,3 and strong spin–orbit coupling4, there has been a flurry of study to uncover the origin of such peculiar characteristics and their correlations. The efforts have been paid for by inventions of new devices; the LAO/STO heterostructure is as a strong candidate for novel application in electronics because the discovered properties are gate-tunable. For example, superconductor-to-insulator transition, phase diagram similar to those of high-temperature superconductors5 and Lifshitz transition6 have been observed via back-gate biasing across the gate insulator single crystal STO that has a high dielectric constant. The gate-controllability of physical properties via STO substrate was also shown in other STO-based 2DEG systems such as γ-Al2O3/STO7, LAO/La1-xSrxMnO3/STO8, CaZrO3/STO9. In addition, the two-dimensional property of electrical channels in those systems allows the devices to be significantly reduced in thickness, which is another advantage of these 2DEG systems10.

The band insulator STO used as the substrate of LAO/STO heterostructure is one of the key elements for the formation of a 2DEG. According to the polar catastrophe scenario, whether the interface has n-type or p-type carriers after electronic reconstruction is determined by the termination of the STO substrate surface11. Experimentally, 2DEGs (two-dimensional hole gases, 2DHGs) showing n-type (p-type) properties were found at the interface between LAO and TiO2 (SrO) terminated STO12,13. Additionally, oxygen vacancies, strain, and the structural phase transition of STO have been reported to affect the properties of the 2DEG14,15,16,17,18,19. A notable peculiarity in properties of STO is that the bulk STO undergoes a structural phase transition from cubic to tetragonal at 105 K. Kalisky et al. observed that the domain structure, attributed to the direction of TiO6 octahedral rotation via the phase transition, caused an inhomogeneous electrical transport showing locally enhanced conductivity near the domain boundaries17. Because the domain boundaries were formed randomly after each cubic-to-tetragonal phase transition, electrical transport was sensitive to thermal cycling above the structural phase transition temperature2,17.

The domain boundary effect was especially pronounced in patterned devices with dimensions comparable with or smaller than the typical domain size. Anisotropic electrical resistance was observed in the patterned devices with domain walls inside, and there was a hysteresis in the temperature versus resistance loop measured during the cool-down and warm-up processes18. The hysteresis of electrical resistance was reported to be maximized in nanoscaled devices19. However, considering the fact that the domain structure will remain the same when the temperature is cycled within the temperature range below the phase transition point (T ~ 105 K)17, the domain wall mechanism suggested in the previous studies does not fully explain the observed hysteric behavior in resistance.

Here, we investigate the hysteretic behavior in the temperature-dependent resistance (R(T)) of a microscale Hall bar-patterned LAO/STO device. It is found that application of gate voltages causes hysteresis in the R(T) loop, and the magnitude of hysteresis increases with the applied positive gate voltage. To explain the observed R(T) loop, we introduce a model that relates the R(T) hysteresis to the temperature-dependent dielectric constant of STO, and to electron trapping within the STO substrate.

Results and discussion

Figure 1a shows a top-view SEM image and a cross-sectional schematic of the device. The hall bar-patterned device was fabricated by using photolithography and Ar-ion milling on a LAO/STO sample grown by pulsed laser deposition. After the fabrication, the back-gate electrode was prepared by directly attaching a gold film deposited on an Al2O3 single crystal plate to the bottom surface of the STO substrate using a silver paste. Therefore, as shown in Fig. 1a, the Au electrode was sandwiched between the bottom of the STO substrate and Al2O3 single crystal, and was used to apply back-gate voltage (VBG) to investigate the gate dependence of resistance. The Al2O3 plate was used for electrical insulation.

(a) SEM image of the Hall bar-patterned device. Inset shows schematic device cross section with a metallic back-gate electrode. In gating experiments, VBG was applied between Au and 2DEG electrodes. (b) Temperature dependence of resistance for cool-down and warm-up processes with no VBG applied. (c) Temperature-dependent carrier density for the cool-down process with VBG = 0 V.

Figure 1b shows the inherent temperature dependence of resistance with no back-gate voltage applied. The resistance shows metallically decreasing behavior with lowering temperature, and there is no hysteresis in R(T) between the cool-down and the warm-up processes. This ensures that our experimental instruments, such as the temperature control system and the gate voltage source, do not cause any problem that may result in false hysteresis or anomalies in R(T). Figure 1c shows temperature dependence of the carrier density for VBG = 0 V. The carrier density is changed from 8 × 1013 cm−2 to 4.5 × 1013 cm−2 with lowering temperature. At T = 4 K, the carrier density is higher than 1 × 1013 cm−2, a value known as the Lifshitz transition point6.

To investigate if a resistance hysteresis occurs when VBG is applied, R(T) for both cool-down and warm-up processes were measured. Figure 2a–c show the temperature dependence of the normalized resistance (R(T)/RT = 300 K) measured under different applied VBG. During the cool-down processes, R(T)/RT = 300 K shows metallic property for all VBG, similar to that for VBG = 0 V. On the other hand, during the warm-up processes, anomalous R(T)/RT = 300 K showing hysteric behavior are observed. In the lowest temperature range, that is, while the temperature is warmed from 4 to 6 K, R(T)/RT = 300 K are similar to those obtained during the cool-down. However, the R(T)/RT = 300 K curves start to deviate from the respective cool-down curves above 6 K, and the deviation intensifies with increasing temperature: the values of resistance are higher than those measured during the cool-down. Furthermore, the R(T)/RT = 300 K for the warm-up processes show some common features which can be summarized as follows. First, when the applied VBG is higher, the difference in the normalized resistance between the cool-down and warm-up processes becomes larger. Second, smooth decreases of the slope of R(T)/RT = 300 K curve are observed from T = 20 K during the warm-up, and sudden decreases immediately followed by recoveries in resistance are observed at a higher temperature around T = 80 K. Third, even though there is a hysteresis in R(T)/RT = 300 K, the values of resistance near room temperature approach a single value (~ 105 Ω) irrespective of the process history.

Temperature dependence of the normalized resistance (R(T)/RT = 300 K) for cool-down and warm-up processes with (a) VBG = 10 V, (b) VBG = 20 V, (c) VBG = 30 V. Black and red curves show R(T)/RT = 300 K for cool down and warm-up processes, respectively. (d) R(T)/RT = 300 K for several warm-up process at VBG = 30 V with various Tmin, where Tmin is the target base temperature for the preceding cool-down sequence from room temperature.

Figure 2d shows the dependence of R(T)/RT = 300 K on the minimum temperature (Tmin) measured for several warm-up processes with a common VBG = 30 V, where Tmin is the target base temperature to which the device is cooled down from room temperature. To obtain the data in Fig. 2d, the temperature was lowered to Tmin, then R(T) was measured while increasing the sample temperature from Tmin to room temperature. The same experimental procedure was repeated for several different Tmin. As shown in Fig. 2d, R(T)/RT = 300 K with Tmin = 50 K is qualitatively similar to that obtained with VBG = 0 V (Fig. 1b). On the other hand, when Tmin is below ~ 40 K, strongly increased R(T)/RT = 300 K is observed for warm-up sequences, and the magnitude of hysteresis increases with decreasing Tmin.

Experimental results similar to that shown in Fig. 2 have been reported not only for LAO/STO19 but also for SrNbO3/STO20, while we also have observed a similar R(T) hysteresis from STO/LAO/STO trilayer (see Fig. S1 in supplementary). These previous studies argue that the observed resistance hysteresis is originated from the domain walls created by the cubic-to-tetragonal structural phase transition of STO at T = 105 K. Furthermore, it is also claimed that the formation of domain wall network at low temperatures causes the 2DEG to change from metal to insulator with increasing temperature, only for the devices with nanoscale channel width19. If the domain wall structure is an important factor of the R(T) hysteresis, it should be observed randomly18 and also should be sensitive to thermal cycling, when the electron channel of the LAO/STO device is laterally confined within the typical domain size. However, the hysteresis in R(T) was always observed whenever we applied positive VBG on the device and lowered the sample temperature below 50 K. Considering these observations, especially the influence of VBG on the hysteresis, we propose that the dielectric characteristic of STO, rather than domain walls, is the main origin of the hysteretic behavior of R(T). This idea is also supported by the fact that Tmin being less than 50 K is essential for the hysteresis to occur, as shown in Fig. 2d. If the domain wall were the main cause of the resistance hysteresis, we should have observed a small or little dependence of hysteresis on Tmin, owing to the fact that the structural phase transition of STO occurs at T = 105 K.

To figure out the detailed effect of VBG at the lowest temperature, which is the turning point of the thermal cycling processes in Fig. 2a–c, we measured the sample resistance while sweeping VBG in forward and backward directions at T = 4 K. Here, the forward sweep (backward sweep) was carried out by changing VBG from 0 V (50 V) to 50 V (0 V). Figure 3a shows the VBG dependence of resistance, which is strongly hysteretic: the measured resistance was much larger for the backward sweep than for the forward sweep. As is indicated by a dotted circle in Fig. 3a for the backward sweep of VBG, the increasing trend of resistance with decreasing VBG subsides and R(VBG) forms a depression between VBG = 30 V and 10 V. We should note that this retracing curve of R(VBG) is similar to the shape of R(T)/RT = 300 K observed near T = 20 K during the warm-up process in Fig. 2. This suggests that the observed hysteresis of R(T)/RT = 300 K in Fig. 2 is closely related to the hysteretic behavior of resistance shown in Fig. 3a, which took place just by sweeping VBG to and back from a positive value.

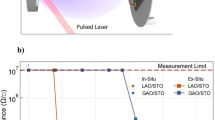

(a) VBG dependence of the resistance at 4 K. Black (red) line shows the gate voltage-dependent resistance with increasing (decreasing) VBG from 0 V (50 V) to 50 V (0 V). (b) Black squares represent the ratio of resistance after gate sweeping at VBG = 50 V (Rafter sweep) to resistance without any gate voltage (Rinitial). The red line is a curve fitted based on the revised empirical formula. The temperature-dependent dielectric constant in the inset (obtained from Barrett's formula)30 and VBG = 50 V were used for the curve fitting. We obtained the following parameters for a 95% confidence interval: α = 200 ± 35 V, β = 0.9 ± 0.18, n0 = (1.3 ± 0.17) × 1014 cm−2.

To investigate the relationship between the hysteresis in the R(T) and R(VBG) in Figs. 2 and 3, we used a planar capacitor model21 where the electron density injected by applying VBG is described as ε0εrVBG/ed, where ε0 is the vacuum permittivity, εr is the relative permittivity of STO, e is the electron charge, and d is the thickness of the STO substrate. Considering that the dielectric constant εr of STO increases drastically at low temperatures, it can be seen that sweeping down the temperature under a fixed VBG plays a role that is similar to a VBG sweep with regard to the injected electron density. Thus, it can be deduced that the hysteretic R(T) phenomenologically arises from the same origin with that for the hysteretic R(VBG) at a fixed temperature. Therefore, it is necessary to figure out the origin of hysteresis in the R(VBG) to understand the hysteresis of R(T).

It has been reported by Yin et al. that the gate-dependent resistance of LAO/STO shows a similar hysteretic behavior, which has been attributed to electron trapping that results in a difference in the electron density of 2DEG between the forward and backward VBG sweeps22. When VBG is swept, the amount of total injected electrons during the forward sweep should be same with the amount of removed electrons during the backward sweep. During the forward sweep, electrons are injected into the 2DEG channel and the impurity sites as well. In the backward sweep, on the other hand, electrons are removed only from the 2DEG because the electrons trapped at the impurity sites are energetically more stable. As a result, the electron density of 2DEG after a VBG sweep is decreased as much as the trapped electron density (ntr). In that report, the trapped electron density is described by an empirical formula, ntr = n0{1 − exp(− VBG/α)}, where n0 is the maximum electron density that can be trapped at the impurity sites, and α is a fitting parameter for each sample. However, it is not possible to correlate the hysteresis in R(T) to the trapped electrons using that empirical formula, because the influence of the dielectric constant of STO substrate is not factored in. Since the injected electron density in the planar capacitor model is proportional to the electric displacement, which is dependent not only on VBG but also on the temperature via εr(T), we modified the above formula into ntr = n0{1 − exp(− εr(T)VBG/εr(0)α)}, which becomes practically identical to the original formula when the temperature is fixed 0 K. The use of εr(0) instead of εr(Tmin) is just for simplicity; any difference between the two values will be compensated by the fitting parameter α.

To confirm the reliability of this revised formula for description of electron trapping at impurity sites, we fit the temperature dependence of the resistance ratio, that is Rafter sweep/Rinitial, where Rafter sweep is the resistance measured after a VBG sweep up to 50 V and Rinitial is that measured before the application of VBG. Considering that the electron density of 2DEG decreases to (nin − ntr) after a VBG sweep due to the electron trapping, Rafter sweep/Rinitial equals μinnin/{μafter sweep(nin − ntr)} according to the Drude formula (R = 1/neμ), where nin, μin, and μafter sweep are the initial electron density, the initial mobility, and the mobility after the VBG sweep of the 2DEG, respectively. Assuming that μafter sweep = μinβ, where β is another fitting parameter and ntr is described by the revised empirical formula, the measured Rafter sweep/Rinitial is fit by using the parameters: α = 200 V, β = 0.9, and n0 = 1.3 × 1014 cm−2. Figure 3b shows the temperature dependence of Rafter sweep/Rinitial along with the fitted curve. The conformity of the fitting result demonstrates that the revised empirical formula correctly reflects the effect of electron trapping at the impurity sites throughout the experimental temperature range. This also indicates that the hysteretic R(T) is owing to the electron trapping caused by application of VBG, along with the strongly temperature-dependent dielectric property of STO23.

Now we present an explanation for the observed hysteresis in R(T). When a positive gate voltage is applied, electrons are injected not only into the 2DEG but also into the impurity sites, as is explained above. The electron density injected into the impurity sites (ntr) is described by the revised empirical formula with the constraint of nm + ntr = ε0εrVBG/d from the planar capacitor model21, where nm is the injected electron density in the 2DEG and thus stays itinerant. When the device is cooled down with an applied gate voltage, increasing dielectric constant of the STO with lowering temperature causes nm and ntr to be increased (see Fig. 4). This does not change the metallic property of R(T) for the cool-down process. On the other hand, when the device is being warmed up after the cool-down, the injected electrons should be removed due to the decreased dielectric constant of the STO with increasing temperature. However, because the electrons trapped at the impurity sites are energetically stable, the itinerant electrons at the 2DEG are removed prior to the trapped electrons, as in the case of the VBG sweep in Fig. 3a. As a result, there occurs a difference in the electron density of 2DEG between the cool-down and warm-up processes, which produces the observed resistance hysteresis. At higher temperatures (T ≥ 250 K), the resistance values measured during the warm-up process approach those measured during the cool-down, as a greater part of the trapped electrons can now escape due to the thermal effect22,24.

Schematic of our model for the R(T) hysteresis. During the cool-down process, the temperature-dependent dielectric constant of STO makes ntr and nm to be increased even though a fixed positive VBG is applied throughout. For the warm-up process, the electrons that have been injected into the 2DEG, as well as preexisting electrons, are removed prior to the electrons injected and trapped at impurity sites, owing to the said temperature dependence of dielectric constant.

The above scenario provides a good explanation of the VBG dependence of the observed resistance hysteresis intensity shown in Fig. 2a–c. It also rationalizes well the Tmin dependence of resistance hysteresis shown in Fig. 2d, in the light of the dielectric constant of STO that increases with decreasing temperature especially rapidly below 50 K. Since the temperature dependence of the dielectric constant of STO is the key factor of the R(T) hysteresis, similar gate-dependent R(T) hysteresis is expected to occur commonly in STO-based 2DEG devices.

As a final remark, we comment on the differences and improvements of our model from preexisting explanations for the resistance hysteresis in LAO/STO. Some of previous studies pointed out the domain boundary structure as the main cause of the resistance hysteresis18,19,20 However, the data shown in Fig. 2 reveals that the R(T) hysteresis starts to develop from as low as 6 K, which is much lower than the structural phase transition temperature 105 K. Our model provides a good rationale of this experimental observation. There have been a number of experimental studies on the VBG-dependent hysteretic resistance at fixed temperatures that attribute the gate hysteresis to electron trapping22,24,25,26,27,28,29. In this work, we introduce the dramatically strong temperature dependence of dielectric constant of the quantum paraelectric STO into the picture of gate hysteresis by electron trapping, and develop a model that successfully reproduces the observed R(T) hysteresis. We further infer that the channel width dependence of R(T) hysteresis reported previously19 may be explained partly in terms of stronger focusing of the gating field near a narrower channel.

Conclusion

We studied gate voltage-controllable hysteresis in the resistance–temperature characteristics of two-dimensional electron gas at LaAlO3/SrTiO3 heterointerface. Without an applied gate voltage, the R(T) curves measured during cool-down and warm-up processes were almost the same. However, a hysteresis in R(T) was manifest after applying a gate voltage, and its intensity was increased by increasing the applied gate voltage VBG. The magnitude of the hysteresis also increased with lowering the base temperature of the cool-down process. These observations of resistance hysteresis were explained in terms of electron injection into the 2DEG conduction channel at the LAO/STO heterointerface and electron trapping at the impurity sites of STO substrate. In the presented scenario, the strongly temperature-dependent dielectric constant of STO plays an important role. We believe that our model of gate-dependent R(T) hysteresis can also be applied to interpretation of electrical transport in other STO-based devices, and may lead to better control over the device properties.

Methods

LaAlO3 thin films growth

Before deposition of LAO, TiO2-terminated STO was annealed to obtain an atomically flat terrace on the STO surface at 950 °C under oxygen partial pressure of 2 × 10–5 Torr for two hours. The LAO thin film of 8 unit-cells was deposited on the TiO2-terminated STO by using pulsed laser deposition at 750 °C under oxygen partial pressure of 10–5 Torr. For the deposition, a KrF excimer laser with an energy of 120 mJ and a repetition rate of 4 Hz was used. After the LAO layer deposition, the sample was maintained in an oxygen partial pressure of 500 mTorr at 750 °C for 30 min and cooled down from 750 °C to room temperature.

Electrical transport measurements

R(T) was measured during cool-down from room temperature to minimum temperature (Tmin) and the subsequent warm-up. The temperature was changed at a rate of 3 K/min, while applying a back-gate voltage to the electrode coated on the back-side surface of STO. The temperature was controlled by Quantum Design PPMS, and the sample resistance was measured using standard lock-in techniques.

References

Reyren, N. et al. Superconducting interfaces between insulating oxides. Science 317, 1196–1199 (2007).

Ngo, T. D. N. et al. Polarity-tunable magnetic tunnel junctions based on ferromagnetism at oxide heterointerfaces. Nat. Commun. 6, 8035 (2015).

Ariando, et al. Electronic phase separation at the LaAlO3/SrTiO3 interface. Nat. Commun. 2, 188 (2011).

Caviglia, A. D. et al. Tunable Rashba spin-orbit interaction at oxide interfaces. Phys. Rev. Lett. 104, 126803 (2010).

Richter, C. et al. Interface superconductor with gap behaviour like a high-temperature superconductor. Nature 502, 528–531 (2013).

Joshua, A., Pecker, S., Ruhman, J., Altman, E. & Ilani, S. A universal critical density underlying the physics of electrons at the LaAlO3/SrTiO3 interface. Nat. Commun. 3, 1129 (2012).

Chen, Y. Z. et al. A high-mobility two-dimensional electron gas at the spinel/perovskite interface of γ-Al2O3/SrTiO3. Nat. Commun. 4, 1371 (2013).

Chen, Y. Z. et al. Extreme mobility enhancement of two-dimensional electron gases at oxide interfaces by charge-transfer-induced modulation doping. Nat. Mater. 14, 801–806 (2015).

Chen, L. et al. Extreme reconfigurable nanoelectronics at the CaZrO3/SrTiO3 interface. Adv. Mater. 30, 1801794 (2018).

Lee, S. R. et al. First Observation of ferroelectricity in ∼1 nm ultrathin semiconducting BaTiO3 films. Nano Lett. 19, 2243–2250 (2019).

Nakagawa, N., Hwang, H. Y. & Muller, D. A. Why some interfaces cannot be sharp. Nat. Mater. 5, 204–209 (2006).

Ohtomo, A. & Hwang, H. Y. A high-mobility electron gas at the LaAlO3/SrTiO3 heterointerface. Nature 427, 423–426 (2004).

Lee, H. et al. Direct observation of a two-dimensional hole gas at oxide interfaces. Nat. Mater. 17, 231–236 (2018).

Brinkman, A. et al. Magnetic effects at the interface between non-magnetic oxides. Nat. Mater. 6, 493–496 (2007).

Kalabukhov, A. et al. Effect of oxygen vacancies in the SrTiO3 substrate on the electrical properties of the LaAlO3/SrTiO3 interface. Phys. Rev. B 75, 121404 (2007).

Bark, C. W. et al. Tailoring a two-dimensional electron gas at the LaAlO3/SrTiO3 (001) interface by epitaxial strain. Proc. Natl. Acad. Sci. 108, 4720–4724 (2011).

Kalisky, B. et al. Locally enhanced conductivity due to the tetragonal domain structure in LaAlO3/SrTiO3 heterointerfaces. Nat. Mater. 12, 1091–1095 (2013).

Goble, N. J. et al. Anisotropic electrical resistance in mesoscopic LaAlO3/SrTiO3 devices with individual domain walls. Sci. Rep. 7, 44361 (2017).

Minhas, M. Z., Müller, A., Heyroth, F., Blaschek, H. H. & Schmidt, G. Temperature dependent giant resistance anomaly in LaAlO3/SrTiO3 nanostructures. Sci. Rep. 7, 5215 (2017).

Yan, X., Zhang, H., Shen, B., Hu, F. & Sun, J. Transport abnormity and its modulations via gating effect and light illumination at the SrNbO3/SrTiO3 interface. Mater. Res. Express 7, 96407 (2020).

Novoselov, K. S. et al. Electric field effect in atomically thin carbon films. Science 306, 666–669 (2004).

Yin, C. et al. Electron trapping mechanism in LaAlO3/SrTiO3 heterostructures. Phys. Rev. Lett. 124, 17702 (2020).

Sawaguchi, E., Kikuchi, A. & Kodera, Y. Dielectric constant of strontium titanate at low temperatures. J. Phys. Soc. Japan 17, 1666–1667 (1962).

Biscaras, J. et al. Limit of the electrostatic doping in two-dimensional electron gases of LaXO3(X = Al, Ti)/SrTiO3. Sci. Rep. 4, 6788 (2014).

Bell, C. et al. Dominant mobility modulation by the electric field effect at the LaAlO3/SrTiO3 interface. Phys. Rev. Lett. 103, 226802 (2009).

Biscaras, J. et al. Two-dimensional superconducting phase in LaAlO3/SrTiO3 heterostructures induced by high-mobility carrier doping. Phys. Rev. Lett. 108, 247004 (2012).

Pallecchi, I. et al. Irreversible multi-band effects and lifshitz transitions at the LaAlO3/SrTiO3 Interface under field effect. Adv. Electron. Mater. 7, 2001120 (2021).

Liu, W. et al. Magneto-transport study of top- and back-gated LaAlO3/SrTiO3 heterostructures. APL Mater. 3, 62805 (2015).

Lee, J. N., Hou, X., Takahashi, R. & Lippmaa, M. Tuning the carrier density in SrTiO3/LaTiO3/SrTiO3 quantum wells. Appl. Phys. Lett. 116, 171601 (2020).

Barrett, J. H. Dielectric constant in perovskite type crystals. Phys. Rev. 86, 118–120 (1952).

Acknowledgements

This work was supported by Korea Institute for Advancement of Technology (KIAT) grant funded by the Korea Government (MOTIE) (P0008458, The HRD Program for Industrial Innovation), Basic Science Research Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Education (NRF-2020R1A6A1A03047771), the Max Planck POSTECH/Korea Research Initiative, Study for Nano Scale Optomaterials and Complex Phase Materials (2016K1A4A4A01922028), though NRF funded by MSIP of Korea, NRF grant funded by MSIP (2020R1A2C1011000).

Author information

Authors and Affiliations

Contributions

Y.K. and W.H. performed sample growth, measurement. Y.K. wrote the manuscript. J.S.L., J.S. and J.K. contributed to interpretation of the results. J.S. and J.K. supervised the findings of this work. All authors discussed the results and reviewed the manuscript.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher's note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary Information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Kwak, Y., Han, W., Lee, J.S. et al. Hysteretic temperature dependence of resistance controlled by gate voltage in LaAlO3/SrTiO3 heterointerface electron system. Sci Rep 12, 6458 (2022). https://doi.org/10.1038/s41598-022-10425-3

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-022-10425-3

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.