Abstract

This study presents a model to calculate the border trap density (Nbt) of atomic layer deposition high-k onto In0.53Ga0.47As on a 300-mm (001) Si substrate. This model considers the quantum confinement effect and band nonparabolicity. Capacitance-equivalent thickness (CET) was used to reflect the distance of the charge centroid from the oxide–semiconductor interface. The border trap values based on CET were found to be approximately 65% lower than the extracted values based on physical thickness in the In0.53Ga0.47As material. In an investigation of two different post-metal annealing effects on border traps, the border trap was more effectively passivated by N2-based forming gas annealing (FGA) compared with rapid thermal annealing (RTA), whereas a lower interface state density was observed in RTA-annealed samples compared with FGA-annealed samples. Nbt extraction at different bias voltages demonstrated that the applied frequencies travel deep into the oxide and interact with more traps as more the Fermi level passes the conduction band, thus creating tunneling with the carriers.

Similar content being viewed by others

Introduction

As a substitute for conventional SiO2/n-type Si metal-oxide-semiconductor field-effect-transistors (MOSFETs), the combination of different higher dielectric constant (k) oxides along with InxGa1−xAs (x > 0.5) as a channel material has been extensively investigated for its potential equivalent oxide thickness (EOT) scaling and use in forthcoming logic-applicable devices that will require high-speed and depressed power consumption1,2,3,4,5. Among the different high dielectric constant (k) oxides, studies on Al2O3, HfO2, La2O3, ZrO2, and their nanolaminate and nano-mixture structures have already been reported6,7,8,9,10,11.

In0.53Ga0.47As is often used instead of silicon because of its high electron mobility, which results from its lower effective mass of electrons. However, because of this lower effective mass of electrons, In0.53Ga0.47As suffers from low density of states (DOS)12. To be more precise, the DOS of In0.53Ga0.47As is less than that of Si by approximately two order of magnitudes13,14. As a result, this insufficient DOS causes the Fermi level of In0.53Ga0.47As to move inside the conduction band; otherwise, the benefit of its high mobility would be lost4. The band offset of high-k and In0.53Ga0.47As substrate is comparatively smaller than that of a conventional SiO2/Si interface.

Once the fermi level, EF, has biased near the conduction band, the effective barrier height between the oxide and In0.53Ga0.47As, which is denoted as Eox − EF, is reduced. As a result, the trap inside the oxide starts the charge/discharge process with electrons from the semiconductor through tunneling14. These traps, which are positioned in the dielectric near the oxide–In0.53Ga0.47As interface, are commonly known as border traps15,16,17. The idea of these traps was first introduced by Fleetwood15. Border traps are characterized by their location: the farther they are from the interface, the longer it takes for the majority carrier to fill them. Their charge exchange is also determined by the applied alternating current (ac) frequency. A lower frequency provides deep tunneling by decreasing the apparent thickness of the oxide, whereas the tunneling probability decreases at a higher frequency16.

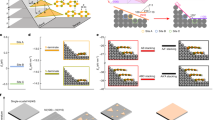

Figure 1a shows how the tunneling of electrons occurs from the semiconductor to oxide layer in response to an applied AC frequency with sufficient direct current (DC) bias voltage. However, the effect of these near-interfacial dielectric traps is a great stimulus for the on-state act of a MOSFET. Because the fermi level (EF) is pinned inside the conduction band, border traps prevent the formation of sufficient carriers in the channel, which leads to reduced carrier mobility by phonon scattering and eccentricity of the threshold voltage17,18. These traps are also responsible for reduction of gate voltage control on the channel current, enhancing gate leakage current, a degradation of transconductance as well as for hysteresis19,20. The impact of border traps is more prominent in the accumulation region, where a dispersion is always observed in the capacitance-voltage (C-V) response of the metal-oxide-semiconductor (MOS) capacitor because of the transportable carrier exchange among the border traps and conduction band states via tunneling, as described previously21,22,23,24.

(a) Energy-band diagram of a metal/Al2O3/n-InGaAs MOS capacitor with the interface and border traps when an AC signal is applied. (b) Response regions of the interface and border traps in the capacitance-voltage (C-V) behavior of the Al2O3/n-InGaAs MOS capacitor. (c) Equivalent circuit diagram for the gate capacitance of the III–V MOSFET.

Figure 1b illustrates the region where border traps are prominent as an active trap state in capacitance-voltage (C-V) with a frequency dependency from 10 kHz to 1 MHz. Unlikely, the typical interface state model cannot explain this dispersion because the time constant of these traps at accumulation is much smaller than that of the bulk oxide traps, within the typical measurement frequency range from 1 kHz to 1 MHz25. The electrical behavior of border traps is quite different from that of interface traps in several ways. Firstly, the interface traps are inactive at the energy value of the accumulation region, where the frequency scattering occurs22. Secondly, compared with the time constant that is responsible for the interface trap’s charging/discharging, the dispersion performance is less temperature dependent because of the border traps26. Finally, the chemical treatment has no effect on border traps but successfully diminishes the dispersion caused by interface traps27.

Researchers have proposed several methods for modelling the dispersion of capacitance at accumulation and making electrical characterizations of border traps22,23,24,25,28,29,30,31. Among them, the distributed border trap model from Yuan et al. is the most well known28,31. In this model, the oxide thickness (tox) is segregated into immeasurable quantities of small fragments, with each part contributing an amount of oxide capacitance, ΔCox, connected in parallel with the admittance proportional to the border trap density; this parallel combination is connected in series with the semiconductor capacitance. The border trap density is then extracted by making a best-fit condition between the calculated capacitance and the conductance achieved from this model and experimental values. Usually, this oxide thickness is mainly the physical thickness (tox) or EOT, which is the result of either ellipsometry or transmission electron microscopy analysis.

When determining the semiconductor capacitance Cs, it is not clear that previous studies’ consideration about the quantum mechanical effect12,25,32,33,34. For practical purposes, this capacitance is not only the oxide capacitance but also a series combination of inversion capacitance (Cinv), which includes quantum capacitance (CQ) and centroid capacitance (Ccent), by assuming that the first electron sub-band in the channel is occupied35,36. Therefore, the total capacitance includes a series combination of insulator capacitance (Cins), quantum capacitance (CQ), and centroid capacitance (Ccent). The equivalent electrical circuit is shown in Fig. 1c. In a large-scale device, the series combination of CQ and Ccent is larger than Cox, so the gate capacitance approaches only Cox. However, in small-scale devices, the oxide thickness is on a nanometer scale; thus, Cox becomes commensurate with the other components of total capacitance35.

Quantum capacitance (CQ), which is proportional to the DOS of the channel material, physically originates from the Fermi-level penetration onto the conduction band. In the III–V channel material, a two-dimensional electron gas requires energy to be created in the semiconductor quantum well region because of low density-of-states (DOS). Therefore, the Fermi level moves above the conduction band to increase the charge in the quantum well. This movement requires energy and conceptually is equivalent to quantum capacitance. However, charges in the quantum well take a bell-shaped distribution rather than distributing themselves in a sheet form with zero thickness, which means that the physical distance of each charge is quite different from the metal gate. Moreover, the center of the charge distribution may be away from the insulator–semiconductor interface due to the confinement in the quantum well. These effects should be considered when modelling the total capacitance. When these factors are excluded, the overall capacitance is overestimated, so the extracted border trap density (Nbt) is inaccurate32. To improve the extraction of border trap density, total semiconductor capacitance (Cs) should be included with the quantum confinement effect and band nonparabolicity in the model. Additionally, because of the quantum mechanical confinement consequence of the carriers, the supplementary thickness of the conductive channel should be considered because the charge centroid in the conductive channel is located deeper beneath the interface of the dielectric and semiconductor, as described previously37.

Capacitance-equivalent thickness (CET) reflects a more realistic set-up because it considers the above-mentioned effect. Therefore, border trap extraction using a CET metric is a more reliable way to obtain the accurate density of border traps. In this study, we used the CET metric for the extraction of Nbt in addition to using physical thickness and determined that border trap density is overestimated when the quantum mechanical effect is not considered. In addition, because a border trap is an oxide’s native property, the parameters of oxide growth from atomic layer deposition (ALD) must have some effects on border trap formation. In this regard, we also examined the effects of ALD growth temperature on border traps. Moreover, several studies have passivated border traps using a variety of annealing processes33,38. Thus, we also examined the passivating effects of two types of annealing processes on border traps. Lastly, the interface trap density (Dit) was also extracted for samples that were differentiated with the passivation scheme.

Model Description

Gate capacitance model

The total capacitance of III–V MOS structures is modelled as a series combination of insulator capacitance (Cins) and inversion capacitance (Cinv) by assuming no doping level underneath the channel as demonstrated in Fig. 1c. It consists of a parallel combination of contributions of each occupied electron subband in the channel. From the figure it is evident that, for each subband i, the inversion-layer capacitance (Cinv_i) consists of the quantum capacitance (CQ_i) and the centroid capacitance (Ccent_i) which are connected in series. So, inversion-layer capacitance can be defined as

where, ψs is the surface potential, EF is the fermi level, EC is the conduction band edge at the barrier-channel interface on the channel side, and Qs is the total electron charge in the channel which is the sum of all the charges in each of the sub bands. This can be formulated as

where, Qi is the electron charge of subband i in the channel, Ei is the energy level of subband i, and \({{\rm{m}}}_{||}^{\ast }\) is the in plane effective mass of the channel material. The effective mass is a function of energy due to nonparabolicity of the band structure which can be expressed as follows39.

where, \({{\rm{m}}}_{0}^{\ast }\) is the effective mass at k = 0, E and k are the energy and wave number of the charge carrier, ħ is the reduced Plank’s constant and α is the nonparabolicity parameter.

Now, we can define quantum capacitance for any subband (CQ_i) as the derivative of electron charge in subband i with respect to energy difference between EF and Ei. Mathematically,

Similarly, centroid capacitance of subband i (Ccent_i) can be defined as the derivative of electron charge in subband i with respect to energy difference between Ei and EC.

Then Cinv_i can be formulated as

So, if the location of each subband energy level (Ei) and the fermi level (EF) are known with respect to conduction band edge, then all the capacitance component can be evaluated.

Border trap extraction model

For a quantitative analysis of border trap density, we followed the distributed border trap model as mentioned previously. This model enumerates the border traps by analyzing the frequency dispersion at an accumulation region at any specific bias voltages. The whole oxide capacitance is modelled onto an abundant number of small capacitive components, ΔCox, where each component characterizes the capacitance of a very small piece of oxide thickness. The induced charge storage and energy loss from the border traps are modelled by a series of connected capacitance (ΔCbt) and conductance (ΔGbt) for any portion of oxide thickness. This admittance due to border traps is connected in parallel to the oxide capacitance. This parallel combination is then connected in series with the semiconductor capacitance. Figure 2 shows the equivalent electrical circuit of the model. The whole model can be described by a first-order non-linear ordinary differential equation, as follows:

with the boundary condition at x = 0, Y = jωCs where Y is the total admittance at any distance x from the oxide–semiconductor interface; ω = 2πf is the angular ac frequency, where f is the measurement frequency and Cs is the semiconductor capacitance corresponding to a specific surface potential ψs.

The other important parameters of this model are described as follows: q is the elementary electron charge in Coulombs; εox = εr · ε0 is the permittivity of any dielectric film, where εr is the relative permittivity of the oxide layer and ε0 is the permittivity of the air; Cox is the oxide capacitance per cm2, which is defined as εox/tox, where tox is the thickness of the oxide layer in centimeters; Nbt is the volume concentration of border traps in the oxide at a distance x from the oxide–semiconductor interface at any energy level, expressed as eV−1 cm−3; and τ is the average time in seconds for electron capturing of an empty trap. τ maintains an exponential relationship with the distance x, which is the distance of the trap within the oxide from the interface. τ can be described as follows:

Here, τ0 is the capture/emission time constant of the trap having the same energy level of τ. k is the attenuation coefficient of the tunneling process, which can be described by the effective mass of dielectric film (m*), the barrier height between the conduction band of oxide and semiconductor (Eb), and the reduced Plank’s constant (ħ). Moreover, τ0 can be described more specifically as:

Here, vth is the thermal velocity of any electron at any temperature T, ns is the semiconductor surface’s electron density, and σ is the border trap’s capture cross-sectional area. As described elsewhere13, at the accumulation region where the Fermi level is near the conduction band, a good approximation is to consider ns as equal to the DOS (Nc) of the conduction band. Moreover, the border traps that are deeply inside of the oxide do not respond at any applied frequency ω having a time constant τ that is greater than 1/ω; however, the traps closer to the interface with a smaller τ are more willing to respond. Using the condition ωτ = 1, the probing depth at any applied frequency for a border trap can be calculated as follows:

Here, f is the measurement frequency.

Results and Discussion

Figure 3 shows the evolution of the sub-band energy levels and all capacitance component modelling, along with experimental data from an Al2O3 ALD-deposited sample. For our modelling, we solved the self-consistent solution of the one-dimensional Poisson and Schrodinger equations using the Nextnano simulation tool40. This tool provides the values of sub-band energy (Ei) and conduction band energy (EC) with respect to the fermi level energy (EF). The inset of Fig. 3 shows the evolution of the sub-band energy levels (Ei) with respect to the fermi level (EF) at the applied bias voltage range. From the figure, it is evident that the fermi level penetrates the first and second energy levels while being very close to the third energy level. Thus, both the first and second sub-bands of the quantum well are populated by electrons in the operational voltage range.

Figure 3 also illustrates the measured capacitance of rapid thermal annealing (RTA) and forming gas annealing (FGA)-processed samples with modelled gate capacitance and its components. The model extraction was done by considering the conduction band effective mass of In.53Ga.47As to be 0.043m0 (m0 = electron mass at rest) by considering a non-parabolicity effect as reported in literature41 as well as optimizing other material parameters according to their physical structures13. The extracted gate capacitances were well harmonized with the modelled data. The insulator capacitance was calculated by considering the ideal dielectric constant (k), which is 9, and the measured oxide thickness. However, in the experimental cases, the gate capacitance approached approximately 63% of Cins for the RTA-processed sample. The same condition is also valid for FGA processed samples as depicted in the Fig. 3. This capacitance deprivation mostly results from the effects of inversion capacitance. As demonstrated, Cinv1 is quite comparable with the insulator capacitance; in addition, CQ1 is more dominant than Ccent1 because of the smaller effective mass of the In0.53Ga0.47As channel. It is also clear that the capacitance dominance of any sub-band energy depends on its electron population density. Therefore, Cinv2 is much smaller than Cinv1 and Cinv3 is negligible according to the fermi level penetration into the sub-band, as shown in the inset of Fig. 3.

For the extraction of border traps, the parameters of “Eq. (7)” were executed as follows. The oxide capacitance was calculated by dividing the oxide permittivity by the oxide thickness. The oxide relative permittivity was calculated according to the formula in “Eq. (11)” for every case, using the maximum capacitance value at a frequency of 10 kHz from the measured C-V data. To calculate the attenuation coefficient, the electron effective mass in Al2O3 was considered to be 0.23 m0 based on the literature33, where m0 is the electron mass at rest; in addition, the barrier height between the oxide and semiconductor conduction band edge was calculated using the electron affinity rule. The semiconductor capacitance Cs was taken at the extraction voltage of the border traps using a one-dimensional Poisson-Schrodinger solver simulation tool (Nextnano) by simultaneously considering quantum confinement and non-parabolic band effects40. CET was calculated according to “Eq. (12)” in the Methods section using the capacitance value from 100 kHz at the border trap extraction voltage. Both Nbt and τ0 were used as fitting parameters to achieve the best-fit curve for capacitance from the model by solving “Eq. (7)” with the measured data. A list of parameters that were used for the modelling is presented in Table 1.

Figure 4 shows the Nbt extraction fitting curves at 1 V using physical thickness tox for both the RTA- and FGA-processed cases. In both cases, the samples deposited at 200 °C show the lowest capacitance compared with the 250 °C and 300 °C deposited samples. This variation in capacitance values is mainly due to the difference in thickness between the samples deposited at different temperatures. As mentioned previously, the 200 °C processed samples showed the greatest thickness and henceforth the lowest capacitive value. The opposite case was observed for the 300 °C deposited samples. In another interesting observation, the FGA-processed samples showed somewhat lower capacitance in three different deposition cases compared with their respective RTA-processed samples. However, in the RTA-processed samples shown in Fig. 4a, there was more distortion of capacitance at the lower frequencies of the measurement window (10 kHz to 1 MHz) than at the higher ones. This disturbance in capacitance may be attributed to the noise associated with lower frequency measurements42. On the contrary, the FGA-processed samples did not suffer from this limitation.

Model fitting of the capacitance versus frequency curves for the measured data (solid symbols) and calculated data from distributed border trap model (solid lines) using physical thickness (tox) at an applied DC gate bias of 1 V. The fitting was performed for three different deposition conditions of Al2O3 on n-InGaAs. Shown here are the (a) RTA conditions and (b) FGA conditions.

In both cases at higher frequencies of the measurement window, the experimental data diverged from the fitting curve and displayed a different slope of capacitance versus log(ω). This change in the gradient of the capacitance versus log(ω) at higher frequencies is consistent at the measurement frequency range, which may be attributed to the distribution of border traps. A high concentration of traps (in the range of 1021 cm−3 eV−1) was reported at <1 nm from the oxide–semiconductor interface. Notably, this high density of traps that are positioned at <1 nm from the Al2O3/InGaAs interface are also found at the lower frequencies of measurement33. However, the extracted border trap densities of the 200 °C, 250 °C, and 300 °C deposited RTA samples were 1.28 × 1020 cm−3 eV−1, 1.1 × 1020 cm−3 eV−1 and 1 × 1020 cm−3 eV−1, respectively. For FGA samples, the extracted border trap densities were 9.6 × 1019 cm−3 eV−1, 9.75 × 1019 cm−3 eV−1 and 7.6x × 1019 cm−3 eV−1, respectively. The value of τ0 in these extractions was in the range of 10−12 s, which is attributed to the lower capture cross-sectional areas of the traps.

Figure 5 shows the Nbt extraction for the same samples by considering the quantum mechanical effect. In this case, the physical thickness was replaced by the CET, and these CET values were extracted for all six cases. Both Nbt and τ0 were used as fitting parameters as before, while keeping the other parameters unchanged. Both the disturbance in capacitance at lower frequencies and the distortion of the gradient of capacitance versus log(ω) also existed in this case. The simulated curves obtained from the model showed a better fit than previous cases. The Nbt values extracted for RTA samples were 4 × 1019 cm−3 eV−1, 4.1 × 1019 cm−3 eV−1, and 3.09 × 1019 cm−3 eV−1 for the deposition conditions of 200 °C, 250 °C, and 300 °C, respectively. For the FGA samples, the Nbt values were 2.98 × 1019 cm−3 eV−1, 3.58 × 1019 cm−3 eV−1, and 2.72 × 1019 cm−3 eV−1, respectively. τ0 was also in the same range as earlier. However, the Nbt values extracted using CET were much lower than the values obtained by using physical thickness, tox. This comparison is illustrated in Fig. 6a,b. The Nbt values by CET were approximately one third of (~65% lower than) the values by tox. The overestimation of Nbt values using physical thickness may be because the additional thickness of the oxide layer due to quantum confinement in the In0.53Ga0.47As layer is not considered. Because the charge centroid is shifted, it causes the oxide–semiconductor interface to shift a finite thickness. As a result, the interface traps, which may contribute to energy loss, are excluded.

Model fitting of the capacitance versus frequency curves for the measured data (solid symbols) and calculated data (solid lines) as in Fig. 4 using capacitance-equivalent thickness (CET) at an applied DC gate bias of 1 V. Shown here are (a) RTA conditions and (b) FGA conditions.

Figure 7a,b compare the extracted Nbt values of both RTA- and FGA-processed samples at three different deposition temperatures, as described previously. In both cases, the FGA-processed samples showed lower values of Nbt than did the RTA-treated samples. This indicates that defect passivation is more effective during the FGA process. In addition, more hydrogen (H2) is incorporated to passivate the dangling bonds, which is the reason for the border traps within the amorphous Al2O3 dielectric in the FGA process38. However, the RTA-processed samples showed comparatively lower Dit values than did the FGA-processed samples. Therefore, RTA treatment passivated the interface traps, whereas border traps are treated by FGA effectively. Furthermore, Nbt was observed to be the lowest for the 300 °C deposited sample comparing with the 200 °C and 250 °C deposited samples for both RTA- and FGA-processed cases. This lower Nbt indicates structural differences in the film stoichiometry at 300 °C, which leads to more hydrogen (H2) incorporation during FGA, as reported elsewhere38. Therefore, the probability of hydrogen (H2) bonding to defects is increased.

Figure 8 shows the Nbt spatial distribution as a function of gate voltage, as well as the distance of the probing depth from the interface into the oxide. The values of Nbt were extracted at different applied DC voltages, whereas the values of τ0 were used to determine the probing depth into the oxide at any measurement frequency. Because border traps are more responsive at lower frequencies and the physical distance into the oxide up to where the traps respond is inversely proportional to the applied frequency, we used the lowest frequency of the measurement window (i.e., 10 kHz) to calculate the response region. The Nbt distribution increases as the applied voltage is increased. With the applied voltage increase, the Fermi level penetration into the conduction band also increases; in addition, the effective barrier height decreases, which makes the majority of carriers more likely to tunnel into the deep traps. When the applied voltage increases, traps with smaller electron capture cross-sectional areas in the deep oxide layer respond. Because all parameters, excluding τ0, are the same at different extraction voltages, a smaller τ0 results in a larger tunneling distance.

Conclusion

We extracted the border trap density of an Al2O3 oxide layer deposited at three different temperatures to n-In0.53Ga0.47As on a 300-mm Si substrate by considering the quantum mechanical effect. Because quantum confinement and charge centroid effects are more prominent in relatively small-scale devices, these effects must be considered to model Nbt in the oxide layer.

We calculated the density of border traps using both physical thickness and CET while keeping other parameters constant. The Nbt values extracted using CET were approximately 65% lower than Nbt values obtained by physical thickness. The samples were also processed by different annealing treatments. FGA-annealed samples showed comparatively lower Nbt values than did than RTA-processed samples, although the RTA-processed samples had lower Dit values. The FGA treatment helps to passivate the border traps, whereas the interface traps are passivated by RTA. Moreover, samples deposited at 300 °C showed moderately low border trap concentrations because of their different stoichiometric structure, which allowed for more H2 incorporation during FGA. The relationship between tunneling distance and border trap concentration with respect to border trap extraction voltage was also studied. With an increase of applied voltage as the Fermi level penetrated into the conduction band, the tunneling distance was observed to be deeper from the response of more traps with relatively small electron capture areas.

Methods

Sample preparation and measurements

An In0.53Ga0.47As n-type heterostructure was created by metal-organic chemical vapor deposition (MOCVD) according to the procedure described here. First, two strain-relaxation buffer epitaxies of GaAs and InP were grown on a typical 300-mm n-type Si (001) substrate following the Volmer-Weber growth mode, with a carrier concentration of 2 × 1018 cm−3 on each layer and thicknesses of 350 nm and 800 nm, respectively. Then, an upper structure was formed, which consisted of a 110-nm Si-doped n-In0.53Ga0.47As layer with an electron density of 5 × 1017 cm−3 as the bottom layer and another 160-nm Si-doped n-In0.53Ga0.47As layer with an electron density of 1 × 1017 cm−3 as the upper layer.

A total of six samples of ALD Al2O3 with a configuration of 30 cycles on In0.53Ga0.47As were prepared. They were deposited at three different growth temperatures of 200 °C, 250 °C, and 300 °C, while two samples were arranged at any specific temperature. Prior to deposition of the dielectric, the In0.53Ga0.47As substrates were treated with several wet cleaning processes to remove any native oxide or other contaminants. At the start, the substrates were cleaned with acetone and isopropyl alcohol for 5 minutes each. Then, they were treated with a solution of diluted hydrochloric acid (HCl) and deionized (DI) water, maintaining a ratio of 1:10 at room temperature for 30 s to eliminate any native oxide. Subsequently, they were cleaned with deionized water for 2 minutes and dried in a nitrogen (N2) environment to displace the water from the wafer surface so that no water mask could form.

After the solution treatment, the substrates were transported to an ALD chamber within a minimal time interval. Before starting the actual deposition, 10 cycles of trimethylaluminium (TMA) preclean were performed because it was reported to be beneficial for passivating the interface trap density due to a self-cleaning effect20,42,43. Then, the Al2O3 dielectric was deposited by ALD using TMA and water (H2O) as the metal precursor and oxidant, respectively. The deposition process began with a TMA pulse onto the In0.53Ga0.47As surface and then was followed with a water pulse. The pulse time was 0.1 s in both cases. Between the TMA pulse and water pulse, a purge duration of 20 s was maintained. Nitrogen (N2) was used for both the purge and carrier gas, with a flow rate of 300 sccm. Both the TMA and water reservoirs were at room temperature.

The physical thickness (tox) of the ALD-deposited Al2O3 layers was quantified by ellipsometry at an incident angle of 70°. The thicknesses were found to be 4.2006 nm, 3.867 nm, and 3.5128 nm for the 200 °C, 250 °C, and 300 °C deposition cases, respectively. Therefore, for MOS capacitor formation after Al2O3 deposition, an ALD 5-nm TiN layer was deposited on top of the dielectric. Then, a metal layer of Ti/Au (200/2000 Å) was deposited by electron-beam (E-beam) evaporation for frontside metal contact by a lift-off process. The same metal layer was again deposited for backside metal contact. Reactive-ion etching based on SF6/Ar Gas (30/10 sccm) was used to etch the TiN layer.

After the MOS capacitor formation, one set of samples deposited at three different temperatures was processed by RTA for 2 minutes at 350 °C in nitrogen (N2) ambient, whereas another set was annealed at 300 °C in forming gas (N2:H2 = 96%:4%) for 30 minutes. The C-V curves at a frequency range from 10 kHz to 1 MHz were measured at room temperature using a Keithley 4200A-SCS parameter analyzer by applying a gate voltage. The effective relative permittivity (εr) and CET were calculated according to the following equations:

Here, Cmax is the maximum capacitance per unit area and tox is the oxide thickness.

Here, Caccum is the accumulation capacitance per unit area. The interface trap density (Dit) was calculated through the conductance method by measuring the parallel conductance (Gp/ωmax)44.

References

Del Alamo, J. A. Nanometre-scale electronics with III–V compound semiconductors. Nature 479, 317–323 (2011).

Lin, H. C., Wang, W. E., Brammertz, G., Meuris, M. & Heyns, M. Electrical study of sulfur passivated In0.53Ga0.47As MOS capacitor and transistor with ALD Al2O3 as gate insulator. Microelectronic Engineering, https://doi.org/10.1016/j.mee.2009.03.112 (2009).

Lin, D. et al. Enabling the high-performance InGaAs/Ge CMOS: a common gate stack solution. In IEEE International Electron Devices Meeting (IEDM) 1–4, https://doi.org/10.1109/IEDM.2009.5424359 (IEEE, 2009).

Taoka, N. et al. Impact of Fermi Level Pinning inside Conduction Band on Electron Mobility of InxGa1−xAs MOSFETs and Mobility Enhancement by Pinning Modulation. In International Electron Devices Meeting 27.2.1–27.2.4, https://doi.org/10.1109/IEDM.2011.6131622 (IEEE, 2011).

Heyns, M. et al. Advancing CMOS beyond the Si roadmap with Ge and III/V devices. In International Electron Devices Meeting 3, 13.1.1–13.1.4 (IEEE, 2011).

Hu-Dong, C. et al. Effect of the Si-doped In0.49Ga0.51P barrier layer on the device performance of In0.4Ga0.6As MOSFETs grown on semi-insulating GaAs substrates. Chinese Physics B 22, 077306 (2013).

Chang, Y. C. et al. Atomic-layer-deposite HfO2 on In0.53Ga0.47As Passivation and energy-band parameters. Applied Physics Letters 072901, 1–4 (2008).

Zadeh, D. H. et al. La2O3/In0.53Ga0.47As metal–oxide-semiconductor capacitor with low interface state density using TiN/W gate electrode. Solid State Electronics 82, 29–33 (2013).

Chobpattana, V., Mates, T. E., Zhang, J. Y. & Scaled, S. S. ZrO2 dielectrics for In0.53Ga0.47As gate stacks with low interface trap densities. Applied Physics Letters 104, 182912 (2014).

Mahata, C. et al. Comparative Study of Atomic-Layer-Deposited Stacked (HfO2/Al2O3) and Nanolaminated (HfAlOx) Dielectrics on In0.53Ga0.47As. ACS: Applied Material and Interfaces 5, 4195–4201 (2013).

Feng, X. et al. The Study of Electrical Properties for Multilayer La2O3/Al2O3 Dielectric Stacks and LaAlO3 Dielectric Film Deposited by ALD. Nanoscale Research Letters 12, 10–13 (2017).

Dou, C. et al. Determination of energy and spatial distribution of oxide border traps in In0.53Ga0.47As MOS capacitors from capacitance–voltage characteristics measured at various temperatures. Microelectronics Reliability 54, 746–754 (2014).

Vurgaftman, I., Meyer, J. R. & Ram-Mohan, L. R. Band parameters for III–V compound semiconductors and their alloys. Journal of Applied Physics 89, 5815–5875 (2001).

Sze, S. M. Physics of Semiconductor Devices. (Wiley-Interscience, 1983).

Fleetwood, D. M. “Border Traps” in MOS Devices. IEEE Transactions On Nuclear Science 39, 269–271 (1992).

Gan, J. Extraction of Border Trap Density in InAs Nanowire Transistors. (M.Sc Thesis in Nanoscience,Lund University, SWEDEN, 2012).

Lin, D. et al. Beyond interface: the impact of oxide border traps on InGaAs and Ge n-MOSFETs. In International Electron Devices Meeting 28.3.1–28.3.4, https://doi.org/10.1109/IEDM.2012.6479121 (IEEE, 2012).

Huang, J. et al. InGaAs MOSFET Performance and Reliability Improvement by Simultaneous Reduction of Oxide and Interface Charge in ALD (La)AlOx/ZrO2 Gate Stack. In IEEE International Electron Devices Meeting (IEDM) 1–4, https://doi.org/10.1109/IEDM.2009.5424357 (IEEE, 2009).

Fleetwood, D. M. Border traps and bias-temperature instabilities in MOS devices. Microelectronics Reliability 80, 266–277 (2018).

Krylov, I., Ritter, D. & Eizenberg, M. The physical origin of dispersion in accumulation in InGaAs based metal oxide semiconductor gate stacks. Applied Physics Letters 117, 174501 (2015).

Yu, B. et al. Effect and extraction of series resistance in Al2O3 - InGaAs MOS with bulk-oxide trap. Electronics Letters 49, 3–4 (2013).

Chen, H. et al. Interface-State Modeling of Al2O3 - InGaAs MOS From Depletion to Inversion. IEEE Transactions on Electron Devices 59, 2383–2389 (2012).

Brammertz, G. et al. A Combined Interface and Border Trap Model for High-Mobility Substrate Metal–Oxide–Semiconductor Devices Applied to In0.53Ga0.47As and InP Capacitors. IEEE Transactions on Electron Devices 58, 3890–3897 (2011).

Zhang, C., Xu, M., Ye, P. D. & Li, X. A Distributive-Transconductance Model for Border Traps in III–V/High-k MOS Capacitors. IEEE Electron Device Letters 34, 735–737 (2013).

Lu, H.-H., Xu, J.-P., Liu, L., Lai, P.-T. & Tang, W.-M. Equivalent distributed capacitance model of oxide traps on frequency dispersion of C-V curve for MOS capacitors. Chinese Physics B 25, 118502 (2016).

Kim, E. J. et al. Atomically abrupt and unpinned Al2O3/In0.53Ga0.47As interfaces: Experiment and simulation. Journal of Applied Physics 106, 124508 (2009).

Ahn, J. et al. Arsenic decapping and pre-atomic layer deposition trimethylaluminum passivation of Al2O3/InGaAs (100) interfaces. 103, 071602 (2013).

Yuan, Y. et al. A Distributed Bulk-Oxide Trap Model for Al2O3 InGaAs MOS Devices. IEEE Transactions on Electron Devices 59, 2100–2106 (2012).

Preier, H. Contributions of surface states to mos impedance. Applied Physics Letters 10, 361–363 (1967).

Mui, D. S. L., Reed, J., Biswas, D. & Morkoç, H. A new circuit model for tunneling related trapping at insulatorsemiconductor interfaces in accumulation. Journal of Applied Physics 72, 553 (1992).

Yu, Y. et al. A Distributed Model for Border Traps in Al2O3 - InGaAs MOS Devices. IEEE Electron Device Letters 32, 485–487 (2011).

Babadi, A. S., Lind, E. & Wernersson, L. E. Modeling of n-InAs metal oxide semiconductor capacitors with high - κ gate dielectric. Journal of Applied Physics 116, 214508 (2014).

Lin, J. et al. Examining the relationship between capacitance-voltage hysteresis and accumulation frequency dispersion in InGaAs metal-oxide-semiconductor structures based on the response to post-metal annealing. Microelectronic Engineering 178, 204–208 (2017).

Galatage, R. V. et al. Accumulation capacitance frequency dispersion of III–V metal-insulator- semiconductor devices due to disorder induced gap states. Journal of Applied Physics 116, 014504 (2014).

Jena, K., Swain, R. & Lenka, T. R. Impact of oxide thickness on gate capacitance – Modelling and comparative analysis of GaN-based MOSHEMTs. Pramana—Journal of physics 85, 1221–1232 (2015).

Pal, H. S., Cantley, K. D., Shahid, S. & Lundstrom, M. S. Influence of Bandstructure and Channel Structure on the Inversion Layer Capacitance of Silicon and GaAs MOSFETs. IEEE Transactions On Electron Devices 55, 904–908 (2008).

Yoshio Nishi, R. D. Handbook of Semiconductor Manufacturing Technology. (CRC Press, 2007).

Tang, K. et al. Border trap reduction in Al2O3/InGaAs gate stacks. Applied Physics Letters 107, 202102 (2015).

Maiorano, P. et al. Non-parabolic band effects on the electrical properties of superlattice FETs. In 2013 14th International Conference on Ultimate Integration on Silicon (ULIS) 93–96, https://doi.org/10.1109/ULIS.2013.6523499 (IEEE, 2013).

Birner, S. The nextnano software for the simulation of semiconductor heterostructures. Topological nanodevice modeling 85586 Available at, https://www.nextnano.de/downloads/publications/abstracts/Abstract_TopologicalNanodeviceModeling_2014_Delft_Birner.pdf (2014).

Sirtori, C., Capasso, F., Faist, J. & Scandolo, S. Nonparabolicity and a sum rule associated with bound-to-bound and bound-to-continuum intersubband transitions in quantum wells. Physical Review B 50, 8663–8674 (1994).

Trinh, H., Chang, E. Y., Wong, Y., Chang, C. & Yu, C. Self-cleaning Effects on Atomic Layer Deposition (ALD) of Al2O3 on InGaAs with Several Surface Treatments. In Extended Abstracts of the 2009 International Conference on Solid State Devices and Materials 478–479 (2009).

Gao, J., Li, W., Mandal, S. & Chowdhury, S. A study of the effect of surface pretreatment on atomic layer deposited Al2O3 interface with GaN. In Proceedings of the SPIE 10381 (2017).

Engel-Herbert, R. H., Hwang, Y. & Stemmer, S. Comparison of methods to quantify interface trap densities at dielectric/III–V semiconductor interfaces. Journal of Applied Physics 108, 124101 (2010).

Acknowledgements

This work was supported by the National Research Foundation of Korea (NRF) grant funded by the Korea government (MSIP; Ministry of Science, ICT and Future Planning, NRF-2019R1A2C1009816) and Nano-Material Technology Development Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Science, ICT and Future Planning (2009-0082580).

Author information

Authors and Affiliations

Contributions

Md. Mamunur Rahman conducted most of the experiments and wrote the manuscript including preparing figures. Jun-Gyu Kim helped in capacitor fabrication, metal deposition and electrical characterization. Dae-Hyun Kim supervised the work and reviewed the manuscript. Tae-Woo Kim initiated the work, gave the main idea and supervised the entire process. All authors analysed and discussed the results.

Corresponding authors

Ethics declarations

Competing Interests

The authors declare no competing interests.

Additional information

Publisher’s note: Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Rahman, M.M., Kim, JG., Kim, DH. et al. Border Trap Extraction with Capacitance- Equivalent Thickness to Reflect the Quantum Mechanical Effect on Atomic Layer Deposition High-k/In0.53Ga0.47As on 300-mm Si Substrate. Sci Rep 9, 9861 (2019). https://doi.org/10.1038/s41598-019-46317-2

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-019-46317-2

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.