Abstract

Low operating voltages have been long desired for thin-film transistors (TFTs). However, it is still challenging to realise 1-V operation by using conventional dielectrics due to their low gate capacitances and low breakdown voltages. Recently, electric double layers (EDLs) have been regarded as a promising candidate for low-power electronics due to their high capacitance. In this work, we present the first sputtered SiO2 solid-state electrolyte. In order to demonstrate EDL behaviour, a sputtered 200 nm-thick SiO2 electrolyte was incorporated into InGaZnO TFTs as the gate dielectric. The devices exhibited an operating voltage of 1 V, a threshold voltage of 0.06 V, a subthreshold swing of 83 mV dec−1 and an on/off ratio higher than 105. The specific capacitance was 0.45 µF cm−2 at 20 Hz, which is around 26 times higher than the value obtained from thermally oxidised SiO2 films with the same thickness. Analysis of the microstructure and mass density of the sputtered SiO2 films under different deposition conditions indicates that such high capacitance might be attributed to mobile protons donated by atmospheric water. The InGaZnO TFTs with the optimised SiO2 electrolyte also showed good air stability. This work provides a new pathway to the realisation of high-yield low-power electronics.

Similar content being viewed by others

Introduction

Oxide-semiconductor thin-film transistors (TFTs) have attracted much attention recently in industry and academia due to their high carrier mobility, low fabrication temperature, and low cost1. For applications such as displays, sensing devices, low-cost disposable electronics, portable electronics, and low-power electronics, it is highly desirable for TFTs to be capable of operating at low voltages2, 3. In order to achieve a low operating voltage of 1 V, a few-nm-thick gate dielectric layer can be used4. However, such a thin dielectric layer may cause a high leakage current as well as inhomogeneity issues in large-area electronics5. Alternatively, high-κ dielectrics can be employed to increase the gate specific capacitance and hence reduce the switching voltage of TFTs6, 7. However, they often have large fixed charge trap densities, resulting in poor threshold voltage control8 and current leakage problems9, 10.

Another interesting approach to achieving low-voltage operation is by using ionic liquids or ion gels as gate dielectrics, which can form electric double layer (EDL) with very high capacitance, typically more than 1 µF cm−2 at 1 Hz11,12,13. Such a high gate capacitance enables an extremely low TFT operating voltage, typically around 1 V. Despite this, the bottleneck issue is that the existing ionic liquids and gels are not suitable for industrial applications because of their soft and liquid nature and thereby the difficulty to control their shape and thickness in TFT structures. Polymer electrolytes or polyelectrolytes have also shown high specific capacitance14, 15. Such materials can be obtained in solid-state forms, but they usually exhibit poor chemical stability particularly at elevated temperatures16. Oxide-based solid-state electrolytes, such as porous SiO2 and Al2O3, have also emerged as an alternative to the conventional electrolytes recently17,18,19. Their porous structure offers a large effective surface area, capable of accommodating a large number of mobile protons17,18,19. Porous oxide films are normally produced by sol-gel synthesis which usually requires high-temperature annealing and results in poor uniformity20, 21. Plasma-enhanced chemical-vapour deposition (PECVD) has been used to fabricate oxide-based electrolytes at room temperature17,18,19, 22, 23. Sputtering is one of the most favourable deposition methods in electronics industry due to high film uniformity, low cost, and ease of large-area or even roll-to-roll film deposition at room temperature. However, to the best of our knowledge, there has been no report on sputtered solid-state electrolytes for TFTs to date.

In this work, we attempt to produce solid-state SiO2 electrolytes by sputtering technology for the first time. A range of Ar pressures and sputtering powers have been experimented during SiO2 sputtering, which result in very different SiO2 microstructures and therefore TFT behaviours. Under optimised sputtering conditions, InGaZnO (IGZO) TFTs that utilise the SiO2 electrolyte show an ultra-low operating voltage of 1 V, a near-zero threshold voltage, V th, of 0.06 V, a subthreshold swing, SS, of 83 mV dec−1 which is close to the theoretical minimum value, and a high on-off ratio of ~105. The microstructure of the sputtered SiO2 electrolyte is characterised by scanning electron microscopy (SEM) and high-resolution transmission electron microscopy (HRTEM). The mass density of the sputtered SiO2 is determined by using Rutherford backscattering spectrometry (RBS). The EDL formation mechanisms have also been discussed based on studies of the ambient stability of the SiO2-electrolyte-based TFTs.

Results

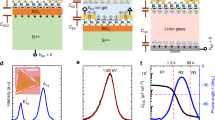

DC and AC characteristics of EDL TFTs

Figure 1a shows the transfer characteristics of the TFT using a sputtered 200 nm-thick SiO2 layer as gate dielectric. The current on/off ratio and subthreshold swing are found to be ~105 and 83 mV dec−1, respectively. In the saturation region, the threshold voltage is found to be very close to zero at 0.06 V. An anticlockwise hysteresis with a small threshold voltage shift of −0.02 V is observed at a sweep rate of 15 mV s−1. The total leakage current is found to be less than 0.1 nA and the leakage current density is around 6.0 × 10−8 A cm−2. Figure 1b shows the output characteristics of the TFT. A typical linear region is observed at low drain voltages. At a gate voltage, V G, of 1 V, and a drain voltage, V D, of 1 V, a drain current, I D, higher than 2 μA is obtained.

Characteristics of EDL TFTs. (a) Transfer characteristics of the TFT gated with SiO2 deposited at 85 W and an Ar pressure of 5 × 10−3 mbar on a glass substrate. The schematic cross-sectional view of the device is shown in the inset. The channel width and the channel length are 1.5 mm and 80 μm, respectively. (b) Output characteristics of the TFT. (c) Specific capacitance of the sputtered SiO2 layer as a function of frequency and the phase angles during the measurement.

To demonstrate the stability and repeatability of device properties, the performance of ten TFTs fabricated in two batches at different times but under the same conditions were measured. Since the capacitance of electrolyte gate dielectric is a function of frequency (unlike conventional TFTs), we have chosen to analyse the transconductance g m rather than mobility itself. A detailed statistical analysis of on/off ratio, subthreshold swing, threshold voltage and transconductance at V G = 1 V and V D = 2 V with the average value and standard deviation bar is shown in Supplementary Figure S1. Devices numbered 1 to 5 were fabricated in one batch and devices 6 to 10 were fabricated in another batch. The electrolyte dielectrics were deposited with an RF power of 85 W and an Ar pressure of 5 × 10−3 mbar. According to the statistical results, the devices fabricated in different batches showed similar performance. The on/off ratios of the devices are all around 3 × 105 with a minimum value still higher than 1 × 105. The magnitude of subthreshold swing is always better than 100 mV dec−1 with an average value of 85 mV dec−1. The transconductance values of the devices are also close to each other, indicating good uniformity and reproducibility.

It should be noted that our sputtered SiO2 electrolyte layer is a new type of dielectric to enable an extremely low operating voltage. Conventional SiO2 insulator has a relative dielectric constant of 3.9, meaning that a layer of 200-nm-thick SiO2 insulator provides a specific capacitance of around 17 nF cm−2. However, our 200 nm SiO2 electrolyte exhibited a specific capacitance of about 300 nF cm−2 which is more than one order of magnitude higher. Indeed, our IGZO TFTs showed an operating voltage of 1 V, which is a drastic improvement from more than 10 V operating voltage of TFTs gated with conventional SiO2 dielectric24,25,26. This is also significantly better than that of IGZO TFTs gated with 200-nm-thick high-κ dielectrics, such as Ta2O5 (3 V)27, HfO2 (5 V)28 and ZrO2 (6 V)28.

Figure 1c shows the specific capacitance of the 200 nm-thick SiO2 film at frequencies ranging from 20 Hz to 100 kHz using an Al/SiO2/Al sandwich structure. The low phase angle, smaller than −45°, indicates the sputtered SiO2 layer remains capacitive up to 100 kHz (ref. 29). A maximum capacitance of 0.45 µF cm−2 is obtained at 20 Hz, which is 26 times larger than that of thermally oxidised 200 nm-thick SiO2 (17.3 nF cm−2). Such a high capacitance enables the ultra-low operating voltage of the TFT in this work. Moreover, unlike thermally oxidised SiO2, the capacitance of the sputtered SiO2 shows a strong frequency dependence which is similar to the gate capacitance of other EDL transistors17, 29, 30.

Effects of different sputtering conditions

In order to explore the origin of such high capacitance, a series of sputtering conditions have been experimented during the deposition of the SiO2 layer. Figure 2a shows the transfer characteristics of three IGZO TFTs gated with 200 nm-thick SiO2 dielectrics sputtered at different Ar pressures of 1 × 10−2, 5 × 10−3, and 1 × 10−3 mbar, respectively. The sputtering power is fixed at 85 W. The TFT with the SiO2 layer sputtered at 1 × 10−3 mbar shows a much lower on-current compared with the values obtained by the other two TFTs. An anticlockwise hysteresis is observed for all three devices, indicting mobile ions in the dielectric layer31. The TFT with the SiO2 layer sputtered at 1 × 10−2 mbar also shows a small region of clockwise hysteresis at gate voltages higher than −0.5 V, indicating electron trapping at the dielectric/channel interface31. Previous studies indicate that protons are common mobile ions in solid-state EDL transistors29, 30, 32. As the deposition process in this work does not involve any noticeable source of protons, it is plausible that they are introduced by moisture in the ambient air. It has been reported that water might be able to diffuse into the sputtered IGZO layer33, 34. Since the size of a water molecule is only around 2.5 Å (ref. 35), it is reasonable to assume that there might be some water molecules at the surface of, or inside, the SiO2 layer if the structure of SiO2 is porous.

Effects of difference sputtering conditions. (a) Transfer characteristics of the IGZO TFTs based on the SiO2 gate dielectric sputtered at 85 W with Ar pressures of 1 × 10−2, 5 × 10−3, and 1 × 10−3 mbar, respectively. (b) High resolution cross-section SEM images of the TFTs with the SiO2 gate dielectric sputtered at Ar pressures of 1 × 10−2 (left, Sample A), 5 × 10−3 (middle, Sample B), and 1 × 10−3 mbar (right, Sample C), respectively. (c) Cross-sectional HRTEM bright field micrograph of the SiO2 layer. The SAED image of the SiO2 film is shown in the inset. (d) Rutherford backscattering spectrum of the SiO2 electrolyte deposited on Al/Si substrate at 85 W with an Ar pressure of 5 × 10−3 mbar. (e) Transfer characteristics of the TFTs using 45 W-sputtered and 85 W-sputtered SiO2 as gate dielectric after one month in atmospheric conditions.

According to Thornton’s model, increasing deposition pressure shall result in a reduction of deposition rate and even a porous film structure36, 37. Thus it is important to analyse the microstructures of the sputtered SiO2 films. Figure 2b shows the cross-sectional SEM images of these three TFTs, corresponding to the three different sputtering pressures, 1 × 10−2 (Sample A), 5 × 10−3 (Sample B), and 1 × 10−3 mbar (Sample C), respectively (Full images can be found in Supplementary Figures S2–4). It is found that there are more granular-like structures in Sample A than those in Sample B. There are hardly any granular-like structures in Sample C when the sputtering pressure is the lowest which is as expected. A highly granular-like microstructure is capable of absorbing water molecules and desirable for proton conduction38, 39. The absorbed water molecules may be ionised into H+ and OH−. When a positive bias is applied to the gate electrode, protons are repelled to the dielectric/channel interface32. These repelled protons will induce a large number of electrons in the channel, thus forming an EDL at the dielectric/channel interface. Because of the lack of granular-like microstructure in Sample C, the SiO2 layer sputtered at the lowest Ar pressure cannot absorb a significant amount of water to form an EDL, resulting in a much lower TFT current as shown in Fig. 2a.

Figure 2c shows an HRTEM image of the SiO2 layer sputtered at 5 × 10−3 mbar, which is obtained in bright field mode where a darker region indicates a higher material density. The SiO2 film exhibits an amorphous structure with an inhomogeneous density distribution. The selected area electron diffraction (SAED) image in the inset of Fig. 2c only shows a diffuse halo without clear rings or spots, confirming the amorphous structure of the material. These results suggest that the sputtered SiO2 has a low-density network structure surrounding higher density regions. Such low-density structure may promote proton hopping between oxygen atoms in the SiO2 layer32, 40, 41.

For thermally oxidised SiO2 films, the Si/O atom ratio and mass density are around 1:2.1 and 2.25 g cm−3, respectively42, 43. However, the RBS spectrum, as shown in Fig. 2d, indicates that the Si/O atom ratio and mass density for the SiO2 films sputtered at 85 W with an Ar pressure of 5 × 10−3 mbar are 1:2.7 and 1.87 g cm−3, respectively. The low mass density confirms that the sputtered SiO2 film at high Ar pressures has a porous structure. The small value of the Si/O ratio indicates the existence of excess oxygen atoms, suggesting that there are a large number of hydroxyl groups or water molecules at the surface of, or inside, the SiO2 layer.

The power dependence of the SiO2 electrolyte has also been studied. Figure 2e shows the transfer characteristics of two TFTs gated with dielectrics sputtered at the same Ar pressure of 5 × 10−3 mbar but different RF powers of 45 W (low power) and 85 W (high power), respectively. According to Messier’s model, the kinetic energy of sputtered particles from the target is positively correlated to the RF power36, 37. As such, at the lower RF power (45 W), the sputtered particles will have lower energy to self-organise to form a denser film on the substrate. The turn-on voltage of the lower-power-sputtered device is indeed lower than the value obtained for the higher-power-sputtered device as shown in Fig. 2e.

Stability test

As protons in the sputtered SiO2 film may be generated by ionised water molecules, testing the air stability of the SiO2 electrolyte TFTs may offer a deeper understanding of the EDL formation mechanism. As shown in Fig. 2e, the performance of the TFT with SiO2 electrolyte sputtered at the higher power (85 W) remains almost the same after one-month storage in ambient atmosphere. On the contrary, the transfer characteristic of the TFT with SiO2 electrolyte sputtered at the lower power (45 W) shows a significant degradation. However, the performance of the lower-power-sputtered device can be recovered after annealing for 1 h in N2 at 100 °C (shown in Supplementary Figure S5). The annealing treatment may remove the water molecules inside the electrolyte and restore the device performance. However, the exact mechanism that causes the very different ambient stabilities of the 45 W and 85 W devices is not clear and needs further studies. Figure 3a shows the transfer characteristics of the TFT with higher-power-sputtered SiO2 gate dielectric before and after treatment in dry N2 for 12 h. The drain current at a gate voltage of 2 V is 4.6 µA before the N2 treatment and slightly drops to 1.2 µA immediately after taking the device out of the N2 ambient. The drain current increases continuously after leaving the device in ambient atmosphere until the device regains its high performance after about 20 min. This confirms that the sputtered SiO2 electrolyte functions by absorbing water and suggests that protons are the mobile ions that are responsible for the formation of EDL layer.

Stability of EDL TFTs. (a) Transfer characteristics of the TFT gated with 200-nm thick SiO2 sputtered at 85 W before (dashed line) and recovering from (solid lines) a treatment in dry N2 for 12 hours. (b) Transfer characteristics of IGZO EDL TFTs with and without a capping layer of 400 nm PMMA, before and after a dry N2 treatment for 12 hours.

It is common for electrolyte-based TFTs to be sensitive to the environment. Such a property itself can be useful in developing environmental sensors44, 45. Furthermore, it is possible to apply a capping layer to control the environmental stability of the devices. Here, we deposited a layer of 400 nm PMMA as a capping layer on some of the devices, and compared their environmental stability before and after PMMA capping. As shown in Fig. 3b, a device without PMMA capping shows a much lower on current after a dry N2 treatment for 12 hours due to the reduction of protons or hydrogen ions in the electrolyte. The TFT was then placed in ambient atmosphere for one hour, which resulted in a recovery in device performance as shown by the green curve. After capping the TFT by spin coating a 400 nm-thick PMMA layer, the device was placed in the dry N2 chamber for 12 hours and measured again. No clear degradation was observed as indicated by the dashed green curve. Such an experiment confirms that adding a capping layer can improve and control the stability of our TFTs, and the useful method is most likely applicable also to other types of EDL devices.

Discussion

In summary, we report the first SiO2 solid-state electrolyte deposited by sputtering technology. TFTs based on the sputter ed SiO2 electrolytes exhibit high performance including 1 V operation, nearly ideal subthreshold swing, low leakage current and small hysteresis. Since sputtering technology is widely used in industry for large-area and even roll-to-roll film deposition, the solid-state electrolyte developed in this work could have timely implications in low-cost, low-power, portable electronics applications.

Methods

Device Fabrication

IGZO TFTs were fabricated with a bottom-gate top-contact structure using photolithography. Glass substrates were cleaned with deionised water, acetone, and methanol. Thermal evaporation was used to deposit a 30 nm-thick Al layer for use as the gate electrode. A 200 nm-thick SiO2 gate dielectric was deposited by using RF sputtering under various conditions in Ar from a SiO2 target. Then a 50 nm-thick IGZO film was deposited as the channel layer by RF sputtering at 45 W and an Ar pressure of 5 × 10−3 mbar. Finally, 30 nm-thick Al source/drain electrodes of the TFTs were thermally evaporated. To deposit a capping layer on the top of a device, a 400 nm-thick layer of PMMA was spin-coated onto the device from a 4% solution in anisole (950PMMA A4, diluted to 4% with anisole). A shadow mask based IGZO TFT, which requires no chemical process, was also fabricated to prove that the ions were not induced during the photolithography process. The transfer characteristics of such IGZO TFT are shown in Supplementary Figure S6.

Device Characterisation

I-V characteristics of the IGZO TFTs were measured by using a Keysight E5270 semiconductor analyser at room temperature in dark. A Keysight E4980A LCR meter was used to measure the C-V characteristics. The high-resolution SEM images were obtained by using an FEI Nova NanoSEM 450 scanning electron microscope. The HRTEM analysis was performed by using a Tecnai F30 transmission electron microscope operating at 300 kV. The mass density and Si/O atom ratio were measured by using National Electrostatics Corporation (NEC) 5SDH-2 RBS with a 2 MeV He2+ ion beam in vacuum.

References

Nomura, K. et al. Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors. Nature 432, 488–492 (2004).

Park, Y. D. et al. Low-voltage polymer thin-film transistors with a self-assembled monolayer as the gate dielectric. Appl. Phys. Lett. 87, 243509 (2005).

Klauk, H., Zschieschang, U., Pflaum, J. & Halik, M. Ultralow-power organic complementary circuits. Nature 445, 745–748 (2007).

Majewski, L. A., Schroeder, R. & Grell, M. One volt organic transistor. Adv. Mater. 17, 192–196 (2005).

Kuo, Y. Metal oxide high-k thin films–from gate dielectrics to nonvolatile memories to LEDs. ECS Trans. 54, 273–281 (2013).

Zhou, C. et al. Low voltage and high ON/OFF ratio field-effect transistors based on CVD MoS2 and ultra high-k gate dielectric PZT. Nanoscale 7, 8695–8700 (2015).

Ling, Z.-P., Zhu, J.-T., Liu, X. & Ang, K.-W. Interface engineering for the enhancement of carrier transport in black phosphorus transistor with ultra-thin high-k gate dielectric. Scientific reports 6, 26609 (2016).

Tan, S. Y. Challenges and performance limitations of high-k and oxynitride gate dielectrics for 90/65 nm CMOS technology. Microelectron. J. 38, 783–786 (2007).

Park, J.-S., Kim, H. & Kim, I.-D. Overview of electroceramic materials for oxide semiconductor thin film transistors. J. Electroceram. 32, 117–140 (2014).

Lin, W.-K., Liu, K.-C., Chang, S.-T. & Li, C.-S. Room temperature fabricated transparent amorphous indium zinc oxide based thin film transistor using high-κ HfO 2 as gate insulator. Thin Solid Films 520, 3079–3083 (2012).

Pu, J. et al. Highly flexible MoS2 thin-film transistors with ion gel dielectrics. Nano Lett. 12, 4013–4017 (2012).

Yuan, H. et al. High‐density carrier accumulation in ZnO field‐effect transistors gated by electric double layers of ionic liquids. Adv. Funct. Mater. 19, 1046–1053 (2009).

Bubel, S., Menyo, M. S., Mates, T. E., Waite, J. H. & Chabinyc, M. L. Schmitt trigger using a self‐healing ionic liquid gated transistor. Adv. Mater. 27, 3331–3335 (2015).

Kim, S. H. et al. Electrolyte‐Gated Transistors for Organic and Printed Electronics. Adv. Mater. 25, 1822–1846 (2013).

Thiemann, S. et al. High-mobility ZnO nanorod field-effect transistors by self-alignment and electrolyte-gating. ACS Appl. Mat. Interfaces 5, 1656–1662 (2013).

Du, H., Lin, X., Xu, Z. & Chu, D. Electric double-layer transistors: a review of recent progress. J. Mater. Sci. 50, 5641–5673 (2015).

Sun, J., Wan, Q., Lu, A. & Jiang, J. Low-voltage electric-double-layer paper transistors gated by microporous SiO2 processed at room temperature. Appl. Phys. Lett. 95, 2108 (2009).

Jiang, J., Wan, Q., Sun, J. & Lu, A. Ultralow-voltage transparent electric-double-layer thin-film transistors processed at room-temperature. Appl. Phys. Lett. 95, 2114 (2009).

Dou, W., Jiang, J., Sun, J., Zhou, B. & Wan, Q. Low-Voltage Oxide-Based Electric-Double-Layer TFTs Gated by Stacked Electrolyte/Chitosan Hybrid Dielectrics. IEEE Electron Device Lett. 33, 848–850 (2012).

Borras, A., Barranco, A. & González-Elipe, A. R. Design and control of porosity in oxide thin films grown by PECVD. J. Mater. Sci. 41, 5220–5226 (2006).

Macias-Montero, M. et al. Vertical and tilted Ag-NPs@ ZnO nanorods by plasma-enhanced chemical vapour deposition. Nanotechnology 23, 255303 (2012).

Jiang, J., Sun, J., Zhou, B., Lu, A. & Wan, Q. Vertical Oxide Homojunction TFTs of 0.8 V Gated by-Treated Nanogranular Dielectric. IEEE Electron Device Lett. 31, 1263–1265 (2010).

Zhu, L. Q., Sun, J., Wu, G. D., Zhang, H. L. & Wan, Q. Self-assembled dual in-plane gate thin-film transistors gated by nanogranular SiO2 proton conductors for logic applications. Nanoscale 5, 1980–1985 (2013).

Geng, D., Kang, D. H. & Jang, J. High-performance amorphous indium-gallium-zinc-oxide thin-film transistor with a self-aligned etch stopper patterned by back-side UV exposure. IEEE Electron Device Lett 32, 758–760 (2011).

Huang, X. et al. Enhanced bias stress stability of a-InGaZnO thin film transistors by inserting an ultra-thin interfacial InGaZnO: N layer. Appl. Phys. Lett. 102, 193505 (2013).

Liu, S. E. et al. Influence of passivation layers on characteristics of a-InGaZnO thin-film transistors. IEEE Electron Device Lett. 32, 161–163 (2011).

Chiu, C. J., Chang, S. P. & Chang, S. J. High-Performance a-IGZO Thin-Film Transistor Using Ta2O5 Gate Dielectric. IEEE Electron Device Lett 31, 1245–1247 (2010).

Lee, S. Y., Chang, S. & Lee, J. S. Role of high-k gate insulators for oxide thin film transistors. Thin Solid Films 518, 3030–3032 (2010).

Zhang, H., Guo, L. & Wan, Q. Nanogranular Al2O3 proton conducting films for low-voltage oxide-based homojunction thin-film transistors. J. Mater. Chem. C 1, 2781–2786 (2013).

Lu, A., Sun, J., Jiang, J. & Wan, Q. Microporous SiO2 with huge electric-double-layer capacitance for low-voltage indium tin oxide thin-film transistors. Appl. Phys. Lett. 95, 222905 (2009).

Wager, J. F., Keszler, D. A. & Presley, R. E. Transparent electronics. (Springer, 2008).

Nogami, M., Kato, A., Nakayama, M. & Lakshminarayana, G. Proton conduction in ionic liquid-modified P2O5–SiO2 glasses. J. Non-Cryst. Solids 358, 3495–3500 (2012).

Shin, H. S., Rim, Y. S., Mo, Y. G., Choi, C. G. & Kim, H. J. Effects of high‐pressure H2O‐annealing on amorphous IGZO thin‐film transistors. Phys. Status Solidi A 208, 2231–2234 (2011).

Park, J. S., Jeong, J. K., Chung, H. J., Mo, Y. G. & Kim, H. D. Electronic transport properties of amorphous indium-gallium-zinc oxide semiconductor upon exposure to water. Appl. Phys. Lett. 92, 72104–72500 (2008).

Raviv, U., Laurat, P. & Klein, J. Fluidity of water confined to subnanometre films. Nature 413, 51–54 (2001).

Messier, R., Giri, A. P. & Roy, R. A. Revised structure zone model for thin film physical structure. J. Vac. Sci. Technol. A 2, 500–503 (1984).

Thornton, J. A. Influence of apparatus geometry and deposition conditions on the structure and topography of thick sputtered coatings. J. Vac. Sci. Technol 11, 666–670 (1974).

Suzuki, S., Nozaki, Y., Okumura, T. & Miyayama, M. Proton conductivity of mesoporous silica incorporated with phosphorus under high water vapor pressures up to 150 °C. J. Ceram. Soc. Jpn. 114, 303–307 (2006).

Seol, J.-H., Won, J.-H., Yoon, K.-S., Hong, Y. T. & Lee, S.-Y. SiO2 ceramic nanoporous substrate-reinforced sulfonated poly (arylene ether sulfone) composite membranes for proton exchange membrane fuel cells. Int. J. Hydrogen Energy 37, 6189–6198 (2012).

Vanheusden, K. et al. Non-volatile memory device based on mobile protons in SiO2 thin films. Nature 386, 587–589 (1997).

Sun, J., Wan, Q., Lu, A. & Jiang, J. Low-voltage electric-double-layer paper transistors gated by microporous SiO2 processed at room temperature. Appl. Phys. Lett. 95, 2108 (2009).

Miller, M. L. & Linton, R. W. X-ray photoelectron spectroscopy of thermally treated silica (SiO2) surfaces. Anal. Chem. 57, 2314–2319 (1985).

Irene, E. A., Tierney, E. & Angilello, J. A viscous flow model to explain the appearance of high density thermal SiO2 at low oxidation temperatures. J. Electrochem. Soc. 129, 2594–2597 (1982).

Liu, N., Liu, Y., Zhu, L., Shi, Y. & Wan, Q. Low-cost pH sensors based on low-voltage oxide-based electric-double-layer thin film transistors. IEEE Electron Device Lett. 35, 482–484 (2014).

Liang, L. et al. Extended-gate-type IGZO electric-double-layer TFT immunosensor with high sensitivity and low operation voltage. Appl. Phys. Lett. 109, 173501 (2016).

Acknowledgements

We are grateful to the support by the Engineering and Physical Sciences Research Council (EPSRC) (Grant Nos. EP/N021258/1 and EP/G03737X/1), the National Key Research and Development Program of China (Grant Nos. 2016YFA0301200 and 2016YFA0201800), the National Natural Science Foundation of China (Grant Nos 11374185 and 11304180), the Natural Science Foundation of Shandong Province (ZR2013EMQ011), and an Independent Innovation Funds of Shandong University (2013TB008 and 2014QY005).

Author information

Authors and Affiliations

Contributions

X.M. fabricated the devices, measured and analysed data from the devices. J.Z., W.C., and J.W. analysed data from the devices. H.W., Q.W., and Q.X. carried out SEM analysis. A.S. conceived and designed the experiments.

Corresponding authors

Ethics declarations

Competing Interests

The authors declare that they have no competing interests.

Additional information

Publisher's note: Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Electronic supplementary material

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Ma, X., Zhang, J., Cai, W. et al. A Sputtered Silicon Oxide Electrolyte for High-Performance Thin-Film Transistors. Sci Rep 7, 809 (2017). https://doi.org/10.1038/s41598-017-00939-6

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-017-00939-6

This article is cited by

-

Low Voltage a-IGZO Thin Film Transistor Using Tantalum Oxide by Thermal Oxidation

Electronic Materials Letters (2024)

-

Oxide-based synaptic transistors gated by solid biopolymer electrolytes

Journal of Materials Science (2023)

-

Multimode transistors and neural networks based on ion-dynamic capacitance

Nature Electronics (2022)

-

Double Junction Characteristics of Amorphous TiO2 Thin Film Due to Various Potential Barriers

Transactions on Electrical and Electronic Materials (2020)

-

Silicon germanium photo-blocking layers for a-IGZO based industrial display

Scientific Reports (2018)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.