Abstract

Strong demand for power reduction in state-of-the-art semiconductor devices calls for novel devices and architectures. Since ternary logic architecture can perform the same function as binary logic architecture with a much lower device density and higher information density, a switch device suitable for the ternary logic has been pursued for several decades. However, a single device that satisfies all the requirements for ternary logic architecture has not been demonstrated. We demonstrated a ternary graphene field-effect transistor (TGFET), showing three discrete current states in one device. The ternary function was achieved by introducing a metal strip to the middle of graphene channel, which created an N-P-N or P-N-P doping pattern depending on the work function of the metal. In addition, a standard ternary inverter working at room temperature has been achieved by modulating the work function of the metal in a graphene channel. The feasibility of a ternary inverter indicates that a general ternary logic architecture can be realized using complementary TGFETs. This breakthrough will provide a key stepping-stone for an extreme-low-power computing technology.

Similar content being viewed by others

Introduction

According to Moore’s law, the number of transistors in an integrated circuit doubles approximately every two years. The channel length and gate oxide thickness of field-effect transistors (FETs) should decrease accordingly, but the scaling of these parameters creates many challenges such as increases in the gate leakage current, process cost, and system power, and a degradation of reliability1,2,3. Therefore, there has been a strong demand for novel devices and architectures that can drastically reduce the power consumption in high-performance computing systems.

At the device level, a number of novel devices have been explored, including carbon nanotube (CNT) FETs, graphene FETs, nanowire FETs, ferroelectric FETs, tunnel FETs, nanoelectromechanical systems (NEMS), single-electron transistors (SETs), and transition metal dichalcogenide (TMD)-material-based FETs4,5,6,7,8,9,10. At the architecture level, starting with monolithic 3D architecture, many new architectures such as neuromorphic architecture, reconfigurable logic architecture, logic-memory hybrid architecture, multivalued logic architecture are being investigated11,12,13,14,15,16. However, none of the above devices or architecture options have been accepted as a dominant technical option for post-silicon and post von Neumann technology.

Although multivalued logic architecture may be the least popular option among the abovementioned technologies, a multivalued logic architecture—more specifically, a ternary logic architecture—has been investigated for more than six decades. The first ternary computer, SETUN, was commercialized in 195817,18. SETUN used only 60% of the vacuum tubes in a binary system because the circuits could be simplified using ternary logic architecture19,20. However, the binary logic architecture has dominated computing technology since the 1970 s because there was no ternary device that could perform a ternary logic at a single-device level. Since then, numerous electronic devices have been explored to realize a simple ternary architecture or further multivalued logic. These include resonant tunneling diodes, resonant tunneling transistors, neuron MOS transistors, SETs, CNT FETs, and quantum dot FETs16,20,21,22,23,24,25,26. Resonant tunneling diode had to use multiple devices to generate multiple states, and the fabrication processes using compound semiconductors were too complex to be competitive with silicon technology22,23. Ternary logic using SET was only functional at cryogenic temperatures, and the separation of logic states was only a few tens of mV9,16. Quantum dot FETs exhibited three states at room temperature, but the scalability and stability of the devices were limited by the size of the quantum dots and the reliability of the gate dielectric20,21. So far, the search for a single-device that performs ternary logic has not been successful even though the general architecture is already in place.

An ideal ternary switch should have distinctly separated multiple states within a given operational bias range. For low-power operation, the operational bias should be low enough, for example lower than 1 V. In addition, it is preferred to use an intrinsic mechanism to generate multiple device states rather than combining multiple devices to maximize power efficiency and achieve system scalability. For example, it is possible to generate different states by applying different biases to a silicon MOSFET. However, the variability between the ON and OFF state of a silicon MOSFET will be too high because the thermal emission rate of electrons overcoming the energy barrier at the source side changes exponentially as a function of gate bias.

In this sense, graphene is an ideal material for the ternary device function because the conductivity of graphene is linearly proportional to the gate bias. Intrinsic material properties of graphene, such as a zero bandgap and the density of the state being linearly proportional to the external bias, provide this unique opportunity. Thus, the conductivity of a graphene channel can be engineered to have a stepwise function by making a small region of opposite charge carriers in a graphene channel. For example, if a positive gate bias applied to a graphene FET with a channel having an N-P-N doping profile is progressively increased, the channel doping will be eventually changed to N-N-N doping profile. When the P-type region is changed to N-type by the gate bias, the Fermi level moves through the charge neutrality point where the density of state is zero, and then the resistance of that portion of the graphene channel increases rapidly. Because of this increase in the resistance, the transfer curve of graphene EFT shows flat or decreasing shape. Because of this phenomenon, stepwise current-voltage characteristics can be achieved.

To realize this device, a stable method to shift the Fermi level of graphene into an electron or hole branch is necessary. Various kinds of doping process for graphene have been reported, including chemical doping, metal contact, self-assembled monolayer, and electrical doping27,28,29,30. Among these methods, the doping method using metals with different work functions is adopted in this work because this approach is thermally stable, and it is easy to control the area of doping. Theoretically, when graphene is in contact with a low- (or high-) work function metal, it should be doped with an electron (or hole)31. For example, an Al strip in contact with graphene will move the Fermi level of graphene from 4.5 eV to 4.08 eV, and a Pt strip will move the Fermi level of graphene toward 5.35 eV. However, it has been difficult to obtain p-type graphene using a metal contact because of a phenomenon similar to the Fermi-level pinning effect, which limits the effective work function of Pt strip on a graphene to ~4.3 eV.

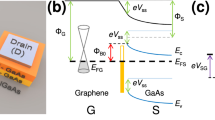

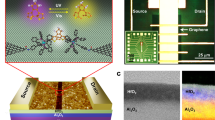

We found that this problem could be alleviated by using a low-temperature high-pressure hydrogen annealing process. Using this result, the doping profile of graphene under the metal strip could be controlled from 4.315 eV to 4.688 eV, and a complementary ternary device could be demonstrated. Figure 1a shows a schematic illustration of a ternary graphene field effect transistor (TGFET). The inset figure shows the schematic of a cross-sectional view of a TGFET, consisting of Al2O3/metal strip/graphene. Al2O3 was deposited over the graphene channel to improve the stability of the TGFET by blocking the water-related molecules from ambient condition. Figure 1b shows a scanning electron microscope (SEM) image of the graphene channel with the metal strip. Gold source/drain contacts were formed after the graphene channel patterning. An Al or Pt metal strip was formed in the middle of the graphene channel. As a result, a P-N-P or N-P-N junction profile is formed in the graphene channel, depending on the work function of the metal strip.

Structure and electrical characteristics of TGFETs.

(a) Schematic of three-dimensional view of TGFETs. Inset figure shows the schematic of cross-sectional view of device. (b) SEM image of TGFETs. In this device, metal strips (Al, Pt) were inserted in the middle of the graphene channel to control the Fermi-level of graphene under the metal strip. (c) Rtot−Vg characteristics of TGFETs with metal strip. This device shows additional Dirac voltage (VDirac,1) with evidence of controlling the graphene channel using metal strip. Inset figure shows formation of P-N-P junction and changes in Fermi level of graphene and junction profile with gate voltage through band diagram of graphene. (d) Id−Vg curve of TGFET with different metal strips. Additional Dirac voltage appeared in hole branch of TGFETs with both Al and Pt strips.

Figure 1c shows a representative resistance curve of a graphene channel with an Al strip. Two distinct Dirac points (VDirac,0 and VDirac,1) shown in Fig. 1c originate at the Dirac point of the p-type region and n-type region. The original and additional Dirac voltages (represented as VDirac,0 and VDirac,1, respectively) are the charge neutrality point of the graphene channel without and with the metal strip. The inset of Fig. 1c shows a representative band diagram for different gate bias regions. At zero bias, the graphene under the Al strip is doped as n-type, while the other channel regions are slightly doped in p-type, forming P-N-P doping regions. As the gate bias increases (or decreases), the channel doping will be converted to n-type (or p-type). During the transition, the channel resistance sharply increases at the Dirac point of the p-type (or n-type) region. As a result, the transfer characteristics of the TGFET with an Al strip show three distinct current levels (I0’, I1’, and I2’) as a function of gate bias, as shown in Fig. 1d. This curve shape is similar to that of the QDFET mentioned above, but the scaling of this device is only limited by the additional width of the Al strip.

Figure 1d also shows the transfer characteristics of TGFETs with a Pt strip. Since the work function of a Pt strip is higher than the Dirac point of a graphene channel, the graphene should be strongly doped in p-type, and VDirac,1 is expected to be in the electron branch. However, both the Pt and Al strips show VDirac,1 in the hole branch (Fig. 1d). The detail shape of Id-Vg curve near I1’ is primarily affected by the residual charge density in the graphene channel under the metal strip. When a residual charge density increases, the transfer curve near the I1’ shows more flat region. Thus, from the shape of Id-Vg curve near I1’ for Pt and Al strip, we can tell that the residual charge density under the Pt strip is higher than Al strip case. The effective work function of Pt is close to 4.36 eV in this case. The physical mechanism of unintended work function shift is not clearly understood yet, but we have developed a method to reduce this problem.

Among various annealing processes in different ambient conditions, only high-pressure annealing in hydrogen (20 atm at 300 °C for 2 h) was found to be effective in recovering the effective work function of Pt. The sign of VDirac,1 is reversed after the hydrogen annealing, as shown in Fig. 2a, indicating that the effective work function of Pt is increased substantially. Interestingly, annealing under the same conditions in nitrogen ambient did not yield noticeable changes in the effective work function of Pt (Supplementary Fig. S1). Thus, the restoration of the work function seems to be related to the interaction between metal, graphene, and hydrogen. Interestingly, the same annealing treatment on the graphene devices with Al strip didn’t yield any substantial change. In fact, any changes after the annealing observed in the devices with the Al strip appear to be the impacts of thermal annealing.

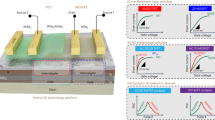

Controlling Fermi-level of graphene under metal strip with high-pressure hydrogen annealing.

(a) Rtot (Vg−VDirac) characteristics of TGFETs with Pt strip. Left-hand figure shows electrical characteristics before high-pressure hydrogen annealing. Right-hand figure shows electrical characteristics after high-pressure hydrogen annealing. After high-pressure hydrogen annealing, additional Dirac voltage in this device transfers from hole to electron branch. This behavior indicates that the junction profile of graphene changes from P-N-P to N-P-N. In these figures, symbols indicate experimental results, and the dotted line indicates simulated results using equation (1). (b) Definition of effective work function of metal on graphene, represented by  . (c) Change in effective work function of Pt with different ambient conditions (N2 and H2). After high-pressure nitrogen annealing, the effective work function of Pt shifted from 4.350 eV to 4.364 eV. Effective work function of Pt shifted from 4.315 eV to 4.688 eV after high-pressure hydrogen annealing.

. (c) Change in effective work function of Pt with different ambient conditions (N2 and H2). After high-pressure nitrogen annealing, the effective work function of Pt shifted from 4.350 eV to 4.364 eV. Effective work function of Pt shifted from 4.315 eV to 4.688 eV after high-pressure hydrogen annealing.

Since the hydrogen annealing may affect the interface of graphene and SiO2 substrate, we checked the influence of high pressure hydrogen annealing on the devices that don’t have metal strip (Supplementary Fig. S2). The electrical characteristics of graphene FETs showed only a slight change in the VDirac, which can be explained with the effects of thermal annealing. Thus, we can conclude that the Fermi-level pinning-like work function shift only occurred at the interface of graphene and a high-work-function metal, and it can only be alleviated by a high-pressure annealing in hydrogen.

The actual amount of the Fermi-level shift in graphene by the metal strip can be extracted by fitting the experimental data using a modified constant mobility model32. Assuming the graphene channel as a variable resistor, the doping profile of graphene can be represented by a series connection of two different variable resistances. Then, the total resistance of the graphene channel with a metal strip is represented by following equation:

where Rc is the contact resistance; the resistance of the graphene beyond the metal strip is R0; the resistance of the graphene under the metal strip is R1; the carrier concentration in the graphene is  ; L and W are the channel length and width, respectively; and μ is the mobility of graphene. Using this equation, the Dirac voltages (VDirac,0, VDirac,1) of graphene with/without metal strip were estimated simultaneously, and the corresponding effective work functions of metal were obtained. As shown in Fig. 2b, the effective work function can be represented by equation (2).

; L and W are the channel length and width, respectively; and μ is the mobility of graphene. Using this equation, the Dirac voltages (VDirac,0, VDirac,1) of graphene with/without metal strip were estimated simultaneously, and the corresponding effective work functions of metal were obtained. As shown in Fig. 2b, the effective work function can be represented by equation (2).

where WM,eff is the effective work function of the metal strip, WG is the work function of graphene (4.5 eV), and C/e is 2.4 × 1011 cm−2V−1. Figure 2c shows the change in the effective work function of Pt before and after nitrogen or hydrogen annealing. The effective work function was shifted by 34 meV after the nitrogen annealing and by 374 meV after the hydrogen annealing. As expected, the same high-pressure annealing did not affect the transfer characteristics of the TGFETs with an Al strip (Supplementary Fig. S3) as significantly as in the device with a Pt strip. The effective work function of Al was shifted by only 46 mV, which is close to the effect of thermal annealing in the Pt case.

We suppose that this improvement might be a result of the elimination of interface bonding through hydrogenation at the graphene/metal interface33. When the metal strip was formed on graphene, charge carriers were transferred between graphene and the metal strip. In the case of Pt whose work function is higher than that of graphene, the electrons moved to the metal side. Then, dipoles were generated at the interface of the metal and graphene. The direction of the dipoles were in a direction opposite to the work function of the metal, resulting in a decrease in work function, WM,eff = WM−ΔV(d), where ΔV(d) is the potential change generated by the metal-graphene interaction, WM,eff is the effective work function of metal on graphene, and WM is the work function of the metal.

To further investigate the physical mechanism, the stability of effective work function modulation using hydrogen annealing was examined. Figure 3a shows the transfer characteristics of TGFETs measured at different temperatures. Id−Vg curves were measured with VG = 0 V while the substrate temperature was changed from 25 °C to 125 °C with a step size of 25 °C. Since the drain currents at −10 V and +25 V are not significantly affected, the substantial temperature dependence appears to be related to the conductance change in the graphene under the Pt strip. In other words, the effective work function of Pt changes as a function of temperature. When this test was extended for 7200 s, similar stability characteristics were observed at even higher temperatures, as shown in Fig. 3b. VDirac,1 was not significantly changed during operation up to 1,000 s. This indicates that the stability of an effective work function shift is more directly affected by the device operation temperature than the stress time.

Temperature and time dependence of Id−Vg characteristics for TGFETs with Pt strip, and mechanism of junction profile change after high-pressure hydrogen annealing.

(a) Temperature dependence of Id−Vg characteristics for TGFETs with Pt strip. (b) Time and temperature dependence of additional Dirac voltage (VDirac,1), extracted from Id−Vg curve (a). Id−Vg was measured during stress time from 1 s to 10,000 s and with different temperatures from 25 °C to 125 °C. (c) Extraction of activation energy related to diffusion of hydrogen molecules. ΔVDirac satisfied Arrhenius plot, and activation energy decreased with increasing temperature based on 75 °C. (d) Schematic of diffusing hydrogen molecules with increasing temperature. Hydrogen molecules diffused from graphene/Pt strip interface, and this reaction accelerated after 75 °C.

These observations provide a clue to a possible mechanism that explains the effective work function shift after hydrogen annealing. Figure 3c shows the change in Dirac voltage (VDirac,0 and VDirac,1) and the activation energy extracted from the temperature dependence of the Dirac voltage change (see supplementary information). The activation energy could be extracted using the Arrhenius equation  . The activation energy decreased from 0.375 eV to 0.15 eV at temperatures above 75 °C. This change indicates there is another mechanism that reverses the effective work function increase by hydrogen annealing at higher temperatures.

. The activation energy decreased from 0.375 eV to 0.15 eV at temperatures above 75 °C. This change indicates there is another mechanism that reverses the effective work function increase by hydrogen annealing at higher temperatures.

Based on these observations, we tentatively concluded that the effective work function shift (i.e., VDirac,1 shift) of Pt was caused by hydrogen diffusion into the interface of the graphene/Pt strip. The hydrogen molecules are adsorbed to the surface of Pt, forming Pt-H or Pt-OH complexes (Fig. 3d). These hydrogen bondings may deter the charge transfer process between Pt and graphene, and contribute to the restoration of the work function. Since the adsorption of hydrogen is not thermodynamically favorable at the low temperature ~300 °C, high-pressure annealing at 20 atm might have been necessary. In addition, as hydrogen bonding is not thermally stable, the effective work function of Pt decreased as the device operational temperature increased. The decrease in activation energy at higher temperatures may be attributed to enhanced hydrogen out-diffusion through the Pt layer. This rough model provides a consistent explanation for the experimental results, but the detailed mechanism should be studied in the future.

Since our primary interest is applying TGFETs to ternary logic architecture, the device characteristics of an n-type TGFET with an Al strip and p-type TGFET with a Pt strip are used to demonstrate complementary TGFETs and ternary inverter circuit, as shown in Fig. 4a. However, since the threshold voltage and gate dielectric of individual TGFETs were not fully optimized, the output characteristics of ternary inverters was modeled using the device parameters obtained from experimental devices.

Circuits and simulated results of ternary inverter using TGFETs.

(a) Circuits of ternary inverters, which are standard ternary inverters (STIs). Both n-type (Pt strip) and p-type (Al strip) TGFETs were connected in series. (b) Change in output voltage with input voltage of STI at VDD = 2 V. In this research, characteristics of ternary inverter could be achieved using only two simple devices.

Figure 4b shows the transfer characteristics of a standard ternary inverter consisting of only two ternary devices, simulated with an input voltage from 0 V to 2 V and VDD = 2 V. The Dirac voltage of the p-type TGFETs was adjusted from 10 V to 30 V to balance the current level between the n-type and p-type TGFETs (Supplementary Fig. S4). With these adjustments, a reasonable working transfer curve for the standard TGFET inverter was obtained as shown in Fig. 4b. This result confirms that complementary TGFETs can be used for more general ternary logic circuits.

A unit ternary device showing three distinct current states was demonstrated using graphene FETs having P-N-P or N-P-N channel doping profiles. While the performances of these devices are not fully optimized, their feasibility for performing ternary logic functions was confirmed using experimentally extracted device parameters. This breakthrough will provide an important stepping-stone for future extreme-low-power electronics technology.

Methods

Methods Summary

A large sheet of single-layer graphene film grown by a chemical vapor deposition (CVD) method was prepared using a wet transfer process. After completing a back-gate graphene FET structure having a Pt source and drain, metal strips (Al, Pt) were inserted in the middle of the graphene channel. Then, the doping profile of the graphene channel was tuned to produce N-P-N and P-N-P profiles using high-pressure hydrogen annealing. The electrical characteristics of all devices were measured using a Keithley 4200 parameter analyzer.

Graphene synthesis and transfer

A 1 cm × 1 cm monolayer of graphene sheet grown on Cu foil using a CVD process was transferred to 90-nm SiO2 thermally grown on a highly P-doped Si substrate using a poly (methyl methacrylate) (PMMA)-mediated transfer method34,35. When the transfer process was complete, the quality of graphene was assessed using Raman spectroscopy (Renishaw, λ = 248 nm, power = 20 mW). The Raman data of the graphene used in this work showed that the graphene is mostly a monolayer and that the integrated ratio of Raman peaks, I(D)/I(G), representing the quality of the graphene channel, was ~0.22 (Supplementary Fig. S5). The presence of a D peak indicates that the quality is reasonably good, but a considerable number of physical defects are still present.

Fabrication of TGFET devices

For device fabrication, 20-nm Au was deposited on a graphene sheet and patterned using i-line contact photolithography and an etching process. Then, the graphene layer open to air was etched using an oxygen plasma process (process power = 50 W, process time = 90 s). After channel patterning using a Au hard mask, a 100-nm Au layer was deposited again using e-beam evaporation and patterned using i-line photolithography and an etching process. The Au hard-mask process was adopted to pattern both the channel and the source/drain region of graphene while minimizing the impact of photoresist residues in the graphene channel. The metal strip (Al, Pt of 10 nm) was formed in the middle of the graphene channel using i-line contact photolithography and a lift-off process. The surface of the graphene channel was passivated with 20-nm Al2O3 using an atomic layer deposition (ALD) process at 130 °C to improve the stability of devices, and annealed in ambient H2 at 300 °C for 2 h at 0 atm and 20 atm to control the doping profile of the graphene channel

Additional Information

How to cite this article: Kim, Y. J. et al. Demonstration of Complementary Ternary Graphene Field-Effect Transistors. Sci. Rep. 6, 39353; doi: 10.1038/srep39353 (2016).

Publisher's note: Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

References

Zeitzoff, P. M. & Chung, J. E. A perspective from the 2003 ITRS: MOSFET scaling trends, challenges, and potential solutions. IEEE Circuits Devices Mag. 21, 4–15 (2005).

Ferain, I., Colinge, C. A. & Colinge, J.-P. Multigate transistors as the future of classical metal-oxide-semiconductor field-effect transistors. Nature 479, 310–316 (2011).

Huang, R. et al. Challenges of 22 nm and beyond CMOS technology. Sci. China Ser. F Inf. Sci. 52, 1491–1533 (2009).

Franklin, A. D. In Emerging Nanoelectronic Devices (eds Chen, A., Hutchby, J., Zhirnov, V. & Bourianoff, G. ) 315–335 (John Wiley & Sons Ltd, 2014).

Wu, Y.-H., Tseng, P.-Y., Hsieh, P.-Y., Chou, H.-T. & Tai, N.-H. High mobility of graphene-based flexible transparent field effect transistors doped with TiO2 and nitrogen-doped TiO2. ACS Appl. Mater. Interfaces 7, 9453–9461 (2015).

Le Borgne, B., Salaün, A.-C. & Pichon, L. Electrical properties of self-aligned gate-all-around polycrystalline silicon nanowires field-effect transistors. Microelectron. Eng. 150, 32–38 (2016).

Ma, W. C. Y. & Chen, Y.-H. Performance improvement of poly-Si tunnel FETs by Ttrap density reduction. IEEE Trans. Electron Devices 63, 864–868 (2016).

Moldovan, C. F., Vitale, W. A., Sharma, P., Bernard, L. S. & Ionescu, A. M. Fabrication process and characterization of suspended graphene membranes for RF NEMS capacitive switches. Microelectron. Eng. 145, 5–8 (2015).

Ciccarelli, C., Campion, R. P., Gallagher, B. L. & Ferguson, A. J. Intrinsic magnetic refrigeration of a single electron transistor. Appl. Phys. Lett. 108, 53103 (2016).

Iqbal, M. W. et al. High-mobility and air-stable single-layer WS2 field-effect transistors sandwiched between chemical vapor deposition-grown hexagonal BN films. Sci. Rep. 5, 10699 (2015).

Qiu, Q. et al. A Neuromorphic architecture for context aware text image recognition. J. Signal Process. Syst. 1–15 (2015).

Murapaka, C., Sethi, P., Goolaup, S. & Lew, W. S. Reconfigurable logic via gate controlled domain wall trajectory in magnetic network structure. Sci. Rep. 6, 20130 (2016).

Becherer, M. et al. A monolithic 3D integrated nanomagnetic co-processing unit. Solid-State Electron. 115, Part B, 74–80 (2016).

Hanyu, T. et al. Challenge of MOS/MTJ-hybrid nonvolatile logic-in-memory architecture in dark-silicon era. In Proc. IEEE International Electron Devices Meeting (IEDM). 28.2.1–28.2.3 (2014).

Seo, M. et al. Multi-Valued logic gates based on ballistic transport in quantum point contacts. Sci. Rep. 4 (2014).

Zhang, W. C., Wu, N. J., Hashizume, T. & Kasai, S. Multiple-valued logic gates using asymmetric single-electron transistors. In Proc. 39th International Symposium on Multiple-Valued Logic. 337–342 (2009).

Glusker, M., Hogan, D. M. & Vass, P. The ternary calculating machine of Thomas Fowler. IEEE Ann. Hist. Comput. 27, 4–22 (2005).

Morisue, M., Endo, J., Morooka, T., Shimizu, N. & Sakamoto, M. A Josephson ternary memory circuit. In Proc. 28th IEEE International Symposium on Multiple-Valued Logic. 19–24 (1998).

Balla, P. C. & Antoniou, A. Low power dissipation MOS ternary logic family. IEEE J. Solid-State Circuits 19, 739–749 (1984).

Karmakar, S., Chandy, J. A. & Jain, F. C. Design of ternary logic combinational circuits based on quantum dot gate FETs. IEEE Trans. Very Large Scale Integr. VLSI Syst. 21, 793–806 (2013).

Karmakar, S. Ternary logic gates using quantum dot gate FETs (QDGFETs). Silicon 6, 169–178 (2014).

Lin, H. C. Resonant tunneling diodes for multi-valued digital applications. In Proc. Twenty-Fourth International Symposium on Multiple-Valued Logic. 188–195 (1994).

Waho, T. Resonant tunneling transistor and its application to multiple-valued logic circuits. In Proc. 25th International Symposium on Multiple-Valued Logic. 130–138 (1995).

Hang, G., Yang, Y., Zhang, D. & Li, X. Neuron-MOS-based dynamic circuits for multiple-valued logic. In Proc. Tenth International Conference on Computational Intelligence and Security (CIS), 166–170 (2014).

Keshavarzian, P. & Sarikhani, R. A novel CNTFET-based ternary full adder. Circuits Syst. Signal Process. 33, 665–679 (2014).

Lin, S., Kim, Y. B. & Lombardi, F. A novel CNTFET-based ternary logic gate design. In Proc. 52nd IEEE International Midwest Symposium on Circuits and Systems. 435–438 (2009).

Farmer, D. B., Lin, Y.-M., Afzali-Ardakani, A. & Avouris, P. Behavior of a chemically doped graphene junction. Appl. Phys. Lett. 94, 213106 (2009).

Feng, T. et al. Back-gate graphene field-effect transistors with double conductance minima. Carbon 79, 363–368 (2014).

Sojoudi, H., Baltazar, J., Tolbert, L. M., Henderson, C. L. & Graham, S. Creating Graphene p–n junctions using self-assembled monolayers. ACS Appl. Mater. Interfaces 4, 4781–4786 (2012).

Chiu, H.-Y., Perebeinos, V., Lin, Y.-M. & Avouris, P. Controllable p-n junction formation in monolayer graphene using electrostatic substrate engineering. Nano Lett. 10, 4634–4639 (2010).

Giovannetti, G. et al. Doping graphene with metal contacts. Phys. Rev. Lett. 101, 26803 (2008).

Kim, S. et al. Realization of a high mobility dual-gated graphene field-effect transistor with Al2O3 dielectric. Appl. Phys. Lett. 94, 62107 (2009).

Pallecchi, E. et al. High Electron mobility in epitaxial graphene on 4H-SiC(0001) via post-growth annealing under hydrogen. Sci. Rep. 4, 4558 (2014).

Li, X. et al. Large-area synthesis of high-quality and uniform graphene films on copper foils. Science 324, 1312–1314 (2009).

Reina, A. et al. Large area, few-layer graphene films on arbitrary substrates by chemical vapor deposition. Nano Lett. 9, 30–35 (2009).

Acknowledgements

This work was supported by the Creative Materials Discovery Program of the Creative Multilevel Research Center (2015M3D1A1068062), the Nano Materials Technology Development Program (2016M3A7B4909942), and the Global Frontier Program for Global Frontier Hybrid Interface Materials (GFHIM) (NRF-2013M3A6B1078873) through the National Research Foundation (NRF) of Korea, funded by the Ministry of Science, ICT & Future Planning.

Author information

Authors and Affiliations

Contributions

Y.J.K. fabricated TGFET devices and performed electrical measurement and data analysis. S.-Y.K., J.N. and C.H.S. modeled TGFET devices and simulated inverter circuit presented in Fig. 4. U.J. and K.E.C. performed the electrical measurement of devices and data analysis. S.K.L. and C.C. developed the graphene transfer process and fabrication process of TGFET. B.H.L. and Y.J.K. analyzed data and wrote the main manuscript. All authors reviewed the manuscript.

Ethics declarations

Competing interests

The authors declare no competing financial interests.

Electronic supplementary material

Rights and permissions

This work is licensed under a Creative Commons Attribution 4.0 International License. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in the credit line; if the material is not included under the Creative Commons license, users will need to obtain permission from the license holder to reproduce the material. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/

About this article

Cite this article

Kim, Y., Kim, SY., Noh, J. et al. Demonstration of Complementary Ternary Graphene Field-Effect Transistors. Sci Rep 6, 39353 (2016). https://doi.org/10.1038/srep39353

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/srep39353

This article is cited by

-

Dual-channel P-type ternary DNTT–graphene barristor

Scientific Reports (2022)

-

Controllable potential barrier for multiple negative-differential-transconductance and its application to multi-valued logic computing

npj 2D Materials and Applications (2021)

-

CMOS technology on another level

Nature Electronics (2019)

-

Tunnelling-based ternary metal–oxide–semiconductor technology

Nature Electronics (2019)

-

Compact Analog-To-Digital Converter (ADC) Using Quantum Dot Gate-Quantum Dot Channel Field Effect Transistor (QDG-QDCFET)

Silicon (2019)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.