Abstract

2D transition metal dichalcogenides (TMDs) have attracted a lot of attention recently for energy-efficient tunneling-field-effect transistor (TFET) applications due to their excellent gate control resulting from their atomically thin dimensions. However, most TMDs have bandgaps (Eg) and effective masses (m*) outside the optimum range needed for high performance. It is shown here that the newly discovered 2D material, few-layer phosphorene, has several properties ideally suited for TFET applications: 1) direct Eg in the optimum range ~1.0–0.4 eV, 2) light transport m* (0.15 m0), 3) anisotropic m* which increases the density of states near the band edges and 4) a high mobility. These properties combine to provide phosphorene TFET outstanding ION ~ 1 mA/um, ON/OFF ratio ~ 106 for a 15 nm channel and 0.5 V supply voltage, thereby significantly outperforming the best TMD-TFETs and CMOS in many aspects such as ON/OFF current ratio and energy-delay products. Furthermore, phosphorene TFETS can scale down to 6 nm channel length and 0.2 V supply voltage within acceptable range in deterioration of the performance metrics. Full-band atomistic quantum transport simulations establish phosphorene TFETs as serious candidates for energy-efficient and scalable replacements of MOSFETs.

Similar content being viewed by others

Introduction

Metal-Oxide-Semiconductor Field-Effect-Transistors (MOSFETs) have been the workhorse of most modern-day electronics. Although aggressive size scaling of MOSFETs have ushered in an era of ultra-fast miniature electronics, the advantages of scaling are fast disappearing as MOSFETs enter the sub-20 nm regime. In state-of-the-art MOSFETs, direct source to drain tunneling through the channel potential barrier degrades the OFF-state current and causes excessive power dissipation1. Tunnel FETs (TFETs) have been proposed to be energy-efficient alternatives to the MOSFET that can reduce the supply voltage (VDD) and satisfy the low power requirements in integrated circuits2,3. Although TFETs, in principle, provide a steep OFF to ON transition needed to minimize power dissipation, the ON-currents of TFETs are quite low4,5, which deteriorates their operational speed and energy-delay product6. The current level in TFETs is the result of band to band tunneling (BTBT) of carriers and hence, highly sensitive to the effective masses (m*) and bandgaps (Eg) of the channel material. While a small m* and Eg improve the ON-current (ION) and supply voltage scaling, the same also deteriorate the OFF-current and channel length (Lch) scaling through direct source-to-drain tunneling7. To meet the simultaneous requirement of the semiconductor industry of both power supply and size scaling, materials need to be carefully chosen with optimized m* and Eg. In this work, it is shown that the newly studied few-layer phosphorene8 provides the ideal material properties to obtain high performance in TFETs as well as to simultaneously achieve both VDD and Lch scaling.

There are several solutions to the low ION challenge of TFETs4. ION depends exponentially on Eg, m* and the electric field F at tunnel junction (i.e.  ). Hence, ION can be enhanced either by a) increasing F or by b) using a channel material with optimum Eg and m*. A number of approaches for increasing the electric field F were proposed before such as 1) atomically thin 2D channel materials that provide a tight gate control and small tunneling distance4,9,10, 2) dielectric engineering with high- and low-k spacers11,12, 3) internal polarization in Nitrides13.

). Hence, ION can be enhanced either by a) increasing F or by b) using a channel material with optimum Eg and m*. A number of approaches for increasing the electric field F were proposed before such as 1) atomically thin 2D channel materials that provide a tight gate control and small tunneling distance4,9,10, 2) dielectric engineering with high- and low-k spacers11,12, 3) internal polarization in Nitrides13.

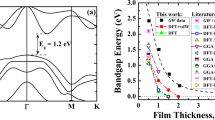

In addition to having an atomically thin channel that improves F, few-layer phosphorene also has the optimum Eg and m* required for high performance TFETs. Moreover, the bandgap of phosphorene remains direct as the number of layers increases. In this regard, phosphorene has a great advantage over other 2D materials, such as graphene and transition metal dichalcogenides (TMDs). Graphene lacks a bandgap and even with engineered bandgaps, it remains unsuitable for transistor applications14. Most monolayer TMDs have a bandgap larger than 1 eV. While the Eg of some multi-layer TMDs may reach below 1 eV, multi-layer TMDs are usually indirect gap materials in which the requirement of momentum change of the carriers by phonons causes very low ON-currents. Among TMDs, only WTe2 in 2H phase has a moderate Eg of 0.75 eV, however it suffers from a large m*15 and the 2H phase of WTe2 has not been experimentally demonstrated yet. Density Functional Theory (DFT) calculations predict that Eg of phosphorene varies from about 1.4 eV in monolayer to 0.3 eV in bulk16. Also, phosphorene has lighter m* for both electrons and holes of ~0.15 m0. Hence, phosphorene is expected to provide the highest performance among all the 2D material TFETs considered so far.

In a few-layer phosphorene flake, each layer is a hexagonal honey comb lattice with puckered surface, as shown in Fig. 1a. The electron and hole effective masses m* are highly anisotropic; m* is low in the armchair direction (≈0.15 m0) and is very high in the zigzag direction (>1 m0)16. Since the tunneling probability decreases exponentially with the transport effective mass17, it is best to have the channel oriented along the armchair direction for high ION. In such a case, the very large m* in the transverse zigzag direction results in a high density of states near the band edges. This m* anisotropy ultimately leads to a large ION, as shown later in the paper. The scaling of TFETs to the sub-10 nm regime also require engineering Eg and m* to keep the ON and OFF state performance intact7. However, to achieve this in most conventional materials such as III-Vs, complicated experimental techniques need to be adopted such as application of strain or forming alloys, which can also introduce disorder in the device. In this regard, the layer dependent Eg and m* in phosphorene already provides an additional knob to optimize the performance for sub-10 nm TFETs, as shown later.

(a) The device structure of a monolayer phosphorene TFET. The channel is oriented along the armchair direction. (b) The transfer characteristics (Ids − Vgs) and (c) the gate capacitance voltage (Cg − Vgs) characteristics of bilayer-phosphornene (2L-phosphorene), monolayer WSe2 and monolayer WTe2 TFETs for Lch of 15 nm and Vds of 0.5 V. Phosphorene TFET has 7.5 times higher ION, 4.9 times lower capacitance and 176 times lower intrinsic energy-delay product than WTe2.

Experimentally, phosphorene flakes as thin as a single layer have been realized recently by means of mechanical exfoliation8. The experimental Eg of a single layer phosphorene has been measured to be approximately 1.45 eV which is way higher than the bulk Eg of black phosphorus (≈0.3 eV). Measured few-layer phosphorene carrier mobility is very high in the armchair direction, it is ≈256 cm2/Vs for few-layers and ≈1000 cm2/Vs for bulk8. In addition, strong anisotropy of m* was verified by angle dependent conductivity8. Later, Saptarshi et al. reported experimental measurements of the thickness dependent transport gap and Schottky barriers of phosphorene18. However, there are challenges to the development of phosphorene based electronics as well. Few-layer phosphorene is unstable in atmosphere and is prone to humidity and oxygen. Hence, it degrades within several hours when left in air19,20. However, there are many efforts to solve this stability challenge; e.g. Junhong et al. stabilized phosphorene for two months by encapsulating it within Al2O321.

In this work, we performed full band atomistic quantum transport simulations of phosphorene TFETs based on the non-equilibrium Green’s function simulator NEMO5 with a second nearest neighbor sp3d5s* tight-binding (TB) Hamiltonian. The electrostatics of the device is obtained by solving a 3D finite-element Poisson equation self-consistently with the quantum transport equations described in the Methods section. The simulated phosphorene TFET assumes a double gated structure as shown in Fig. 1a. The channel length is 15 nm and the transport direction is oriented along the armchair direction. The source and drain doping levels are set to 1020 cm−3 in a p-i-n configuration, effective oxide thickness (EOT) is 0.5 nm and the drain bias Vds equals 0.5 V unless mentioned otherwise. The device specifications are compatible with the international technology road-map for semiconductors (ITRS)22.

Figure 1b,c compare the current-voltage (Ids − Vgs) and capacitance-voltage (Cg − Vgs) characteristics respectively of bilayer-phosphorene (2L-phosphorene) with those of WTe2 and WSe2 (which have been identified as the best TMD material candidates for TFETs15) for a supply voltage VDD of 0.5 V. 2L-phosphorene provides an inverse sub-threshold slope (SS) much lower than the other two TMDs (well below the Boltzmann limit of 60 mV/dec at room temperature) and provides an ION of nearly 1 mA/um (about 7.5 times higher than WTe2 in 2H phase). The ON-state capacitance of 2L-phosphorene is also about 5 times lower than that of WTe2. The large ION and small VDD and Cg translate into a very small switching energy and switching delay for the 2L-phosphorene. The most important metric of performance for low power transistors is the product of the switching energy and the delay (energy-delay product or EDP)6. The lower the EDP, the more energy-efficient and faster the device is. 2L-phosphorene has 176 times lower intrinsic EDP compared to the best TMD TFET (WTe2). The origins of these improvements are discussed next.

Figure 2a,b show Eg and m* in the armchair direction ( ) as a function of the number of phosphorene layers extracted from phosphorene bandstructures computed with the atomistic tight-binding model of this work. In ref. 7, optimum Eg and m* values needed to maximize ION/IOFF in TFETs were presented for various supply voltages and channel lengths Lch. It was suggested that for Lch = 15 nm and VDD = 0.5 V, Eg and m* need to be roughly about 0.7 V and 0.15 m0 respectively. It is seen in Fig. 2b that the electron and hole m* are roughly about 0.15 m0 and do not vary much with the number of layers. While the Eg in Fig. 2a is seen to be strongly dependent on the number of layers, apart from the 1.4 eV value for monolayer phosphorene, Eg is mostly in the range of 0.7 to 0.4 eV, with the optimum value of 0.7 eV reached for 2L-phosphorene. It is to be noted that there is still some experimental discrepancy about the actual values of Eg in phosphorene with transport measurements yielding smaller bandgaps than optical measurements (as also seen in TMDs). DFT and TB calculations used in this work yield bandgaps closer to the transport measurements. Moreover, the bandgap of phosphorene varies about 1 eV from bulk to monolayer which provides a knob to tune Eg to its optimum value by the right choice of channel thickness.

) as a function of the number of phosphorene layers extracted from phosphorene bandstructures computed with the atomistic tight-binding model of this work. In ref. 7, optimum Eg and m* values needed to maximize ION/IOFF in TFETs were presented for various supply voltages and channel lengths Lch. It was suggested that for Lch = 15 nm and VDD = 0.5 V, Eg and m* need to be roughly about 0.7 V and 0.15 m0 respectively. It is seen in Fig. 2b that the electron and hole m* are roughly about 0.15 m0 and do not vary much with the number of layers. While the Eg in Fig. 2a is seen to be strongly dependent on the number of layers, apart from the 1.4 eV value for monolayer phosphorene, Eg is mostly in the range of 0.7 to 0.4 eV, with the optimum value of 0.7 eV reached for 2L-phosphorene. It is to be noted that there is still some experimental discrepancy about the actual values of Eg in phosphorene with transport measurements yielding smaller bandgaps than optical measurements (as also seen in TMDs). DFT and TB calculations used in this work yield bandgaps closer to the transport measurements. Moreover, the bandgap of phosphorene varies about 1 eV from bulk to monolayer which provides a knob to tune Eg to its optimum value by the right choice of channel thickness.

(a) The bandgap Eg and (b) effective masses along armchair direction  as function of the number of layers N. Bandgaps measured in transport experiments18 differ from those of optical measurements8,33 and both are shown as reference. The DFT guided TB bandgaps follow the transport measurements more closely for multi-layer phosphorene. (c) The complex band structure of 2L-phosphorene and monolayer WTe2. The complex bands are plotted at transverse wave-vector Ky = 0 and 0.1π/b for both materials. The area enclosed by the imaginary wave-vector and the vertical axis (i.e. the shaded area) determines the BTBT decay rate. Bilayer phosphorene not only has smaller BTBT decay rate at Ky = 0 due to small transport mass, but also at non-zero Ky due to large transverse m*.

as function of the number of layers N. Bandgaps measured in transport experiments18 differ from those of optical measurements8,33 and both are shown as reference. The DFT guided TB bandgaps follow the transport measurements more closely for multi-layer phosphorene. (c) The complex band structure of 2L-phosphorene and monolayer WTe2. The complex bands are plotted at transverse wave-vector Ky = 0 and 0.1π/b for both materials. The area enclosed by the imaginary wave-vector and the vertical axis (i.e. the shaded area) determines the BTBT decay rate. Bilayer phosphorene not only has smaller BTBT decay rate at Ky = 0 due to small transport mass, but also at non-zero Ky due to large transverse m*.

The bandgap alone does not explain why the phosphorene TFET significantly outperforms WTe2 TFET since 2L-phosphorene has a similar Eg as 1L-WTe2. The difference actually originates from 2L-phosphorene having a light transport m* in the armchair direction ( ) and a heavy transverse m* in the zigzag direction (

) and a heavy transverse m* in the zigzag direction ( ). This is conveniently illustrated in the complex bandstructure in Fig. 2c, which shows the energy-momentum dispersion of the carriers in the forbidden bandgap connecting the conduction and valence band states. The complex part of the bandstructure corresponds to the evanescent wavefunctions e−κz in the bandgap with imaginary momentum iκ and the area enclosed by the imaginary band and the energy axis corresponds to the band to band tunneling (BTBT) decay rate23. The smaller the area, the larger is the transmission probability. Figure 2c compares the complex band structure of 2L-phosphorene with 1L-WTe2. The complex bands are plotted at transverse wave-vector Ky = 0 and 0.1π/b for both materials. 2L-phosphorene not only has a smaller BTBT decay rate at Ky = 0 (due to small transport m*), but also at a non-zero Ky. This is due to a large transverse m* (

). This is conveniently illustrated in the complex bandstructure in Fig. 2c, which shows the energy-momentum dispersion of the carriers in the forbidden bandgap connecting the conduction and valence band states. The complex part of the bandstructure corresponds to the evanescent wavefunctions e−κz in the bandgap with imaginary momentum iκ and the area enclosed by the imaginary band and the energy axis corresponds to the band to band tunneling (BTBT) decay rate23. The smaller the area, the larger is the transmission probability. Figure 2c compares the complex band structure of 2L-phosphorene with 1L-WTe2. The complex bands are plotted at transverse wave-vector Ky = 0 and 0.1π/b for both materials. 2L-phosphorene not only has a smaller BTBT decay rate at Ky = 0 (due to small transport m*), but also at a non-zero Ky. This is due to a large transverse m* ( ) which prevents the decay rate from increasing significantly with Ky. In other words, phosphorene has a high density of states of carriers with optimum transport m* and Eg(Ky).

) which prevents the decay rate from increasing significantly with Ky. In other words, phosphorene has a high density of states of carriers with optimum transport m* and Eg(Ky).

Next, the performance of the phosphorene TFET and its scalability in VDD and Lch are evaluated as a function of the number of layers. Figure 3a shows the transfer characteristics of mono- (1L), bi- (2L) and tri-layer (3L) phosphorene TFETs with Lch of 15 nm. The 2L-phosphorene provides the highest ON/OFF current ratio. Notice that although 3L phosphorene provides higher ION, it has a higher IOFF compared to the 2L case. Figure 3b–d show the transfer characteristics of scaled few-layer phosphorene at different technology nodes. Constant electric field E scaling (i.e.  ) of 30 V/nm is considered here. Doping level of source and drain is assumed to be symmetric unless mentioned otherwise. In almost all of the three cases, the phosphorene TFET seems to scale very well from 15 nm to 9 nm channel lengths. Although for very short Lch such as 6 nm, IOFF degrades significantly, asymmetric doping can be used to suppress the p-branch of the TFET and reduce IOFF. For the Lch = 6 nm case, reducing the drain doping (Nd) increases the drain to channel tunneling distance24 and helps to block IOFF. However, there is a lower limit to Nd. Reducing Nd reduces the carrier density (through Ec − EF) and the tunneling window. For the Lch = 6 nm case, the optimum Nd is found to be 1019 cm−3 in 1L and 5 × 1018 cm−3 in 2L and 3L as shown in Fig. 3b–d). 1L case shows the highest ON/OFF current ratio in the 6 nm case.

) of 30 V/nm is considered here. Doping level of source and drain is assumed to be symmetric unless mentioned otherwise. In almost all of the three cases, the phosphorene TFET seems to scale very well from 15 nm to 9 nm channel lengths. Although for very short Lch such as 6 nm, IOFF degrades significantly, asymmetric doping can be used to suppress the p-branch of the TFET and reduce IOFF. For the Lch = 6 nm case, reducing the drain doping (Nd) increases the drain to channel tunneling distance24 and helps to block IOFF. However, there is a lower limit to Nd. Reducing Nd reduces the carrier density (through Ec − EF) and the tunneling window. For the Lch = 6 nm case, the optimum Nd is found to be 1019 cm−3 in 1L and 5 × 1018 cm−3 in 2L and 3L as shown in Fig. 3b–d). 1L case shows the highest ON/OFF current ratio in the 6 nm case.

(a) The transfer characteristics of the mono- (1L), bi- (2L) and tri-layer(3L) phosphorene TFETs for 15 nm channel length Lch. Transfer characteristics of constant electric field E scaling (i.e.  30 V/nm) for (b) 1L, (c) 2L and (d) 3L phosphorene. For the Lch = 6 nm case, the Ids − Vgs can be optimized through asymmetric doping.

30 V/nm) for (b) 1L, (c) 2L and (d) 3L phosphorene. For the Lch = 6 nm case, the Ids − Vgs can be optimized through asymmetric doping.

The total gate capacitances (Cg) of 1L- to 3L-phosphorene TFETs are shown in Fig. 4 for the same constant electric field scaling discussed before. As expected, the gate capacitances also scale quite well up to Lch = 9 nm. 2L-phosphorene offers the lowest capacitances. Although the capacitances for the Lch = 6 nm case are slightly larger than the 9 nm case, asymmetric doping can decrease the capacitance for 2L and 3L, as shown Fig. 4. The gate capacitances predicted here for phosphorene are much less (<10%) than those reported for TMDs15. The lower Cg in phosphorene originates from its optimum Eg and m*. The Ids − Vgs and Cg − Vgs are shifted in voltage axis such that the current at zero gate voltage IOFF is set to 1 nA/um as required by ITRS22. TMDs have lower I60 currents (the current value where SS becomes 60 mV/dec25) which is a result of their higher Eg and m*. This makes 0 gate voltage to be closer to threshold voltage if compared with phosphorene. Accordingly, TMDs operate closer to ON-state which results in a higher amount of charge in channel and a higher Cg. In summary, the benefits of optimum Eg, small transport m* and large transverse m* in phosphorene are two-fold: 1) higher ION and 2) lower capacitance.

The outstanding Ids − Vgs and Cg − Vgs characteristics of few-layer phosphorene translate into impressive intrinsic energy-delay products (EDP), which is used ultimately to compare ultra-fast energy-efficient transistors. Figure 5a shows the computed intrinsic energy and delay of phosphorene TFETs. In the energy-delay figure, the bottom left corner with the lowest EDP is preferred. It is woth mentioning that WTe2 has been benchmarked as the best TMD TFET12,15. Nevertheless, as seen in Fig. 5, the EDPs of phosphorene TFETs are much smaller than the best TMD TFET. Intrinsic EDP of 2L-phosphorene with Lch of 15 nm is two orders of magnitude smaller than the EDP of the WTe2 TFET. Not only does phosphorene provide record ION and Cg but also a record energy delay product among 2D materials. The optimized asymmetric doping also improves the intrinsic EDP of TFETs specially for sub-9 nm channel lengths. Although intrinsic EDP is an important measure of the transistor’s potential, intrinsic EDP alone does not indicate how good the device is in a real circuit with interconnects and parasitic capacitances. For this reason, ED calculations of a 32-bit adder circuit based on these TFETs have been performed and shown in Fig. 5b. The 32-bit adder simulation has been performed using the software BCB 3.026. The scaling of circuit parameters as a function of gate length follows the ITRS roadmap22. As seen in the Fig. 5b, phosphorene 32-bit adder EDP is better than CMOS and WTe2 and improves further with scaling. These improvements are not as significant as the ones promised by the intrinsic EDP due to the presence of interconnects and parasitic capacitances. This calls for better circuit designs for lowering parasitic capacitances to fully realize the potential of phosphorene TFETs especially in the sub-10 nm regime. Moreover, phosphorene TFET surpasses CMOS in other metrics such as static power consumption and ON/OFF ratio22,27. For example, 15 nm high performance CMOS has 100 times more OFF current and 50 times less ON/OFF current ratio than the corresponding phosphorene TFET. Also, the low operating power 15 nm CMOS has 5 times more OFF current and 6350 times less ON/OFF current ration than the phosphorene TFET.

The energy delay (ED) of 2L-phosphorene at different scaling nodes calculated for (a) intrinsic device and (b) 32-bit adder circuit.

Phosphorene provides lower energy delay product (EDP) than WTe2 and CMOS. Although, scaling down significantly improves the intrinsic EDP, the improvement in the adder EDP is less due to the dominance of parasitics in smaller dimensions. For the 6 nm node, optimized 2L-phosphorene with asymmetric doping provides the lowest possible intrinsic EDP, such improvements are not felt in the adder EDP due to the dominance of parasitics.

In conclusion, few-layer phosphorene has a unique set of properties which makes it an excellent candidate for future ultra-scaled low power electronics: 1) atomistically thin body thickness, 2) tune-able Eg and m* with number of layers within the optimum range for TFET applications, 3) anisotropic m* and 4) direct band gap even in multi-layer. These features make phosphorene an exceptional candidate among 2D materials for TFET applications. The Ids − Vgs and Cg − Vgs characteristics of few-layer phosphorene exhibit significant improvements in energy-delay product compared to other 2D TFETs (e.g. TMD TFETs) and CMOS. Bilayer phosphorene shows optimum performance and is recommended for adoption as the future material of 2D-TFETs.

Methods

In the quantum transport simulations performed in this work, the phosphorene Hamiltonian employs a 10 band sp3d5s* 2nd nearest neighbor tight binding model (TB). The TB parameters have been optimized to reproduce the band structures obtained from density functional theory (DFT) using HSE06. A general TB parameter set was obtained that captured the bandstructure of monolayer to bulk phosphorene. This DFT to TB mapping is a standard technique in semi-empirical TB28. The Hamiltonian is represented with TB instead of DFT, since DFT is computationally expensive and is size limited. Our TB model agrees well with previous calculations of m* and Eg of few-layer phosphorene obtained from DFT with Becke Johnson functional (DFT-mBJ)16.

For transport simulations, a self- consistent Poisson-quantum transmitting boundary method (QTBM) has been used with the TB Hamiltonian. QTBM is equivalent to the non equilibrium Green’s function (NEGF) approach in the ballistic case, but it entails the solution of a linear system of equations instead of obtaining the Green’s function by matrix inversion which is more computationally inefficient29. In QTBM, the Schroedinger equation with open boundary conditions is given as,

where E, I, H and Σ are the carrier energy, identity matrix, device Hamiltonian and self-energy due to open boundaries and Ψ and S are the wave function and a carrier injection term respectively from either source (S) or drain (D). 3D Poisson equation is solved using the finite-element method. It should be noted that the dielectric tensor ε of few-layer phosphorene is anisotropic and has been obtained from DFT calculations30. The Poisson equation reads as follows :

where V and ρ are the electrostatic potential and total charge, respectively. In this paper, the transport simulations have been performed with the Nanoelectronics Modeling tool NEMO531,32.

Additional Information

How to cite this article: Ameen, T. A. et al. Few-layer Phosphorene: An Ideal 2D Material For Tunnel Transistors. Sci. Rep. 6, 28515; doi: 10.1038/srep28515 (2016).

References

Ionescu, A. M. & Riel, H. Tunnel field-effect transistors as energy-efficient electronic switches. Nature 479, 329–337 (2011).

Appenzeller, J., Lin, Y.-M., Knoch, J. & Avouris, P. Band-to-band tunneling in carbon nanotube field-effect transistors. Phys. Rev. Lett. 93, 196805 (2004).

Appenzeller, J., Lin, Y.-M., Knoch, J., Chen, Z. & Avouris, P. Comparing carbon nanotube transistors-the ideal choice: a novel tunneling device design. EEE Trans. Electron Devices 52, 2568–2576 (2005).

Sarkar, D. et al. A subthermionic tunnel field-effect transistor with an atomically thin channel. Nature 526, 91–95 (2015).

Choi, W. Y., Park, B.-G., Lee, J. D. & Liu, T.-J. K. Tunneling field-effect transistors (tfets) with subthreshold swing (ss) less than 60 mv/dec. IEEE Electron Device Lett. 28, 743–745 (2007).

Nikonov, D. & Young, I. Benchmarking of beyond-cmos exploratory devices for logic integrated circuits. IEEE J. Explor. Solid-State Computat. Devices Circuits 1, 3–11 (2015).

Ilatikhameneh, H., Klimeck, G. & Rahman, R. Can tunnel transistors scale below 10 nm? IEEE Electron Device Lett. 37, 115–118 (2016).

Liu, H. et al. Phosphorene: an unexplored 2d semiconductor with a high hole mobility. ACS Nano 8, 4033–4041 (2014).

Fiori, G. et al. Electronics based on two-dimensional materials. Nat. Nanotechnol. 9, 768–779 (2014).

Zhang, Q., Iannaccone, G. & Fiori, G. Two-dimensional tunnel transistors based on thin film. IEEE Electron Device Lett. 35, 129–131 (2014).

Ilatikhameneh, H., Ameen, T., Klimeck, G., Appenzeller, J. & Rahman, R. Dielectric engineered tunnel field-effect transistor. IEEE Electron Device Lett. 36, 1097–1100 (2015).

Chen, F. W., Ilatikhameneh, H., Klimeck, G., Chen, Z. & Rahman, R. Configurable electrostatically doped high performance bilayer graphene tunnel fet. IEEE Journal of the Electron Devices Society, vol. 4, no. 3, pp. 124–128 (2016).

Li, W. et al. Polarization-engineered iii-nitride heterojunction tunnel field-effect transistors. IEEE J. Explor. Solid-State Computat. Devices Circuits 1, 28–34 (2015).

Zhang, Y. et al. Direct observation of a widely tunable bandgap in bilayer graphene. Nature 459, 820–823 (2009).

Ilatikhameneh, H. et al. Tunnel field-effect transistors in 2-d transition metal dichalcogenide materials. IEEE J. Explor. Solid-State Computat. Devices Circuits 1, 12–18 (2015).

Qiao, J., Kong, X., Hu, Z.-X., Yang, F. & Ji, W. High-mobility transport anisotropy and linear dichroism in few-layer black phosphorus. Nat. Commun. 5, 4475 (2014).

Ilatikhameneh, H., Salazar, R. B., Klimeck, G., Rahman, R. & Appenzeller, J. From fowler-nordheim to non-equilibrium green’s function modeling of tunneling. IEEE Trans. on Elect. Dev. (TED), doi: 10.1109/TED.2016.2565582 (2016).

Das, S. et al. Tunable transport gap in phosphorene. Nano Lett. 14, 5733–5739 (2014).

Castellanos-Gomez, A. et al. Isolation and characterization of few-layer black phosphorus. 2D Materials 1, 025001 (2014).

Kou, L., Chen, C. & Smith, S. C. Phosphorene: Fabrication, properties and applications. J. Phys. Chem. Lett. 6, 2794–2805 (2015).

Na, J. et al. Few-layer black phosphorus field-effect transistors with reduced current fluctuation. ACS Nano 8, 11753–11762 (2014).

International technology roadmap for semiconductors (itrs) (2011). URL http://www.itrs2.net/itrs-reports.html. (Date of access:4/3/2016).

Guan, X., Kim, D., Saraswat, K. C. & Wong, H.-S. P. Complex band structures: From parabolic to elliptic approximation. IEEE Electron Device Lett. 32, 1296–1298 (2011).

Salazar, R. B., Ilatikhameneh, H., Rahman, R., Klimeck, G. & Appenzeller, J. A predictive analytic model for high-performance tunneling field-effect transistors approaching non-equilibrium green's function simulations. J. Appl. Phys. 118 (2015).

Vandenberghe, W. G. et al. Figure of merit for and identification of sub-60 mv/decade devices. Appl. Phys. Lett. 102, 013510 (2013).

Nikonov, D. E. Benchmarking of devices in the nanoelectronics research initiative. (2014). URL https://nanohub.org/tools/nribench/browser/trunk/src/. (Date of access:4/3/2016).

Salmani-Jelodar, M., Kim, S., Ng, K. & Klimeck, G. Transistor roadmap projection using predictive full-band atomistic modeling. Appl. Phys. Lett. 105, 083508 (2014).

Tan, Y. P., Povolotskyi, M., Kubis, T., Boykin, T. B. & Klimeck, G. Tight-binding analysis of si and gaas ultrathin bodies with subatomic wave-function resolution. Phys. Rev. B 92, 085301 (2015).

Luisier, M., Schenk, A., Fichtner, W. & Klimeck, G. Atomistic simulation of nanowires in the s p 3 d 5 s* tight-binding formalism: From boundary conditions to strain calculations. Phys. Rev. B 74, 205323 (2006).

Wang, V., Kawazoe, Y. & Geng, W. Native point defects in few-layer phosphorene. Phys. Rev. B 91, 045433 (2015).

Steiger, S., Povolotskyi, M., Park, H.-H., Kubis, T. & Klimeck, G. Nemo5: a parallel multiscale nanoelectronics modeling tool. IEEE Trans. Nanotechnol. 10, 1464–1474 (2011).

Fonseca, J. E. et al. Efficient and realistic device modeling from atomic detail to the nanoscale. J Comput. Electron. 12, 592–600 (2013).

Zhang, S. et al. Extraordinary photoluminescence and strong temperature/angle-dependent raman responses in few-layer phosphorene. ACS Nano 8, 9590–9596 (2014).

Acknowledgements

This work was supported in part by the Center for Low Energy Systems Technology (LEAST), one of six centers of STARnet, a Semiconductor Research Corporation program sponsored by MARCO and DARPA. nanoHUB.org computational resources are used. operated by the Network for Computational Nanotechnology funded by the US National Science Foundation under grant EEC-1227110, EEC-0228390, EEC-0634750, OCI-0438246 and OCI-0721680 is gratefully acknowledged.

Author information

Authors and Affiliations

Contributions

T.A.A. and H.I. performed the simulations and analyzed the data. G.K. and R.R. supervised the work. All authors contributed to writing the manuscript.

Ethics declarations

Competing interests

The authors declare no competing financial interests.

Rights and permissions

This work is licensed under a Creative Commons Attribution 4.0 International License. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in the credit line; if the material is not included under the Creative Commons license, users will need to obtain permission from the license holder to reproduce the material. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/

About this article

Cite this article

Ameen, T., Ilatikhameneh, H., Klimeck, G. et al. Few-layer Phosphorene: An Ideal 2D Material For Tunnel Transistors. Sci Rep 6, 28515 (2016). https://doi.org/10.1038/srep28515

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/srep28515

This article is cited by

-

2D materials-based nanoscale tunneling field effect transistors: current developments and future prospects

npj 2D Materials and Applications (2022)

-

A Study on the Effect of the Structural Parameters and Internal Mechanism of a Bilateral Gate-Controlled S/D Symmetric and Interchangeable Bidirectional Tunnel Field Effect Transistor

Nanoscale Research Letters (2021)

-

Charge Plasma-Based Phosphorene Tunnel FET Using a Hybrid Computational Method

Journal of Electronic Materials (2021)

-

Recent Developments in Black Phosphorous Transistors: A Review

Journal of Electronic Materials (2021)

-

High-Performance Two-Dimensional InSe Field-Effect Transistors with Novel Sandwiched Ohmic Contact for Sub-10 nm Nodes: a Theoretical Study

Nanoscale Research Letters (2019)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.