Abstract

In this work, we present a comprehensive theoretical and experimental study of quantum confinement in layered platinum diselenide (PtSe2) films as a function of film thickness. Our electrical measurements, in combination with density functional theory calculations, show distinct layer-dependent semimetal-to-semiconductor evolution in PtSe2 films, and highlight the importance of including van der Waals interactions, Green’s function calibration, and screened Coulomb interactions in the determination of the thickness-dependent PtSe2 energy gap. Large-area PtSe2 films of varying thickness (2.5–6.5 nm) were formed at 400 °C by thermally assisted conversion of ultra-thin platinum films on Si/SiO2 substrates. The PtSe2 films exhibit p-type semiconducting behavior with hole mobility values up to 13 cm2/V·s. Metal-oxide-semiconductor field-effect transistors have been fabricated using the grown PtSe2 films and a gate field-controlled switching performance with an ION/IOFF ratio of >230 has been measured at room temperature for a 2.5–3 nm PtSe2 film, while the ratio drops to <2 for 5–6.5 nm-thick PtSe2 films, consistent with a semiconducting-to-semimetallic transition with increasing PtSe2 film thickness. These experimental observations indicate that the low-temperature growth of semimetallic or semiconducting PtSe2 could be integrated into the back-end-of-line of a silicon complementary metal-oxide-semiconductor process.

Similar content being viewed by others

Introduction

Two-dimensional (2D) transition metal dichalcogenides (TMDs) have attracted extensive interest as this class of layered materials exhibit electronic properties from semimetals to semiconductors. In addition, their properties may significantly change when moving from bulk to ultra-thin films due to strong spin–orbit coupling (SOC).1,2,3 These properties open up new opportunities in bandgap engineering for future optical and electronic devices. In addition, TMDs have the potential to form atomically abrupt heterostructures from materials that are not lattice matched.4 TMD materials are also promising with respect to the integration of memory, logic, photonic, sensor, and general input/output functions above conventional silicon-integrated circuits in the back-end-of-line (BEOL) provided low thermal budget processes can be developed at ≤400 °C.5

2D atomic crystals of platinum diselenide (PtSe2) exhibit distinct electronic structures and properties. PtSe2 is a layered material in which individual atomic layers are stacked together by van der Waals (vdW) interactions. Although the bulk crystal is a semimetal with a slight indirect overlap of the conduction and valence bands,6 monolayer (ML) PtSe2 has been revealed to be a semiconductor.7,8 Thus, PtSe2 has attracted growing attention due to its high performance in photocatalysis for water splitting,7 gas and pressure sensors,9,10 electronics,11 optoelectronics,12 and as a potential candidate for spintronics and valleytronics8 applications.

In 2015, Wang et al.8 reported that the surface of a Pt(111) crystal can be selenized to form ML PtSe2 at 270 °C. This method is convenient to yield large-area films up to millimeter size and allows the band structure of ML PtSe2 to be studied. However, the metallic Pt substrate hinders electronic applications where an insulating substrate is generally needed. Although atomically thin PtSe2 flakes with different thickness can be mechanically exfoliated from the bulk crystals13,14 and are very well suited for fundamental studies, this approach is not scalable. Recently, the growth of PtSe2 films on sapphire substrates by chemical vapor deposition (CVD) at 900 °C15 and PtSe2 synthesis through direct reaction of metal platinum foil and selenium powder under high pressure and high temperature (600–800 °C)16 have been reported. PtSe2 films grown on sapphire substrate by CVD at 500 °C was recently reported indicating how the doping type of the films can be modified by the stoichiometry of the PtSe2 films by a rapid or slow cool down process, which modifies the Se precursor supply.17 In ref.,18 1 ML to 22 ML PtSe2 films have been grown on bilayer graphene/6H-SiC (0001) substrates by molecular beam epitaxy, which in principle could be extended to grow large size films on dielectric substrates.

In this study, the electronic structure and carrier transport properties of PtSe2 films with different thicknesses are investigated theoretically and experimentally. First-principles calculations considering vdW interactions for pristine PtSe2 films are performed. Calibration of Green’s function with screened Coulomb interaction (GW) is utilized to predict the quantitative values of the bandgap energy. The bandgap opening in few-layer PtSe2, reported in other works,7,8,14,19,20,21,22,23 is shown to depend strongly on the simulation framework, with a progressive increase in the PtSe2 energy gap when considering density function theory (DFT), to DFT with the addition of vdW interactions, and finally to DFT with vdW interactions and screened Coulomb interaction. The Bohr radius provides an estimation of when the quantum effects modify the band structure. The Bohr radius of 10 nm is calculated for bulk PtSe2 with electron-effective mass of 0.22 × m0 and bulk PtSe2 dielectric constant of 40.24 Within this simulation framework, we investigate the impact of Pt vacancies on the PtSe2 band structure and the density of states (DoS). For ML and bilayer structures, our atomic-scale simulations reveal that Pt vacancies lead to the creation of localized energy states in the bandgap and a shift in the Fermi level towards the PtSe2 valence band.

To explore these effects experimentally, we have synthesized large-area PtSe2 films by thermally assisted conversion (TAC) of pre-deposited Pt layers at 400 °C on Si/SiO2 substrates. Hall measurements of the PtSe2 films reveal p-type majority carriers for all TAC-grown PtSe2 films with mobilities in the range of 5–13 cm2/V·s. Back-gated PtSe2 metal-oxide-semiconductor field-effect transistors (MOSFETs) demonstrate p-channel behavior, consistent with the experimental van der Pauw Hall measurements of the large-scale films. The Hall analysis and the back-gated PtSe2 MOSFET characteristics are both consistent with the theoretical calculations, showing p-type PtSe2 films and a transition from semimetallic behavior for films from 5 to 6.5 nm to a semiconducting behavior for a film thickness of 2.5 to 3 nm.

Results

First-principles ab initio calculations

Bulk PtSe2 is a semimetal with trigonal symmetry, where Pt atoms are coordinated by six neighboring Se atoms. In ultra-thin PtSe2 films a bandgap opens up. The effects of quantum confinement (QC) determine the value of the confinement-induced bandgap in the PtSe2 thin films. Ab initio techniques are applied to study PtSe2 thin films. Standard theoretical methods for calculating band structure based on DFT are well known to under-estimate the predicted bandgaps primarily due to approximations for the electronic exchange and correlation energies. VdW interlayer interaction in layered materials such as PtSe2 improves the structural and electronic properties description obtained by DFT calculations. Hence, we have incorporated vdW interaction in our calculations by adding a nonlocal vdW term to local and semi-local exchange correlation functionals. In addition, to provide further improved quantitative description of the bandgap energies, GW (G: Green’s function and W: screened Coulomb interaction) calibration in combination with a many-body perturbation theory is also implemented.25 Green’s function theory provides quasi-particle energies using the electron self-energy operator containing the effects of exchange and correlations with other quasi-particles.

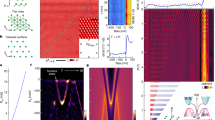

Figure 1a illustrates the band structure of a ML PtSe2 film. The ML PtSe2 exhibits an indirect bandgap of 1.2 eV when GW correction is not accounted for. The band structure of bulk PtSe2 is shown in Supplementary Fig. 1, which exhibits the semimetallic characteristic and is in good agreement with literature,14 where both electron and hole pockets coexist at the Fermi surface. With the increase of number of PtSe2 layers, the energy level of valence band maximum (VBM) exceeds that of conduction band minimum (CBM), leading to overlap of bands and hence semiconductor-to-semimetal evolution. In the GW calculations, the method in ref. 26 has been used enabling improved convergence in the bandgap energies with a reduced set of empty states. Due to the computational demands of GW calculations, this approach was applied to films between 0.5 and 2 nm thickness and used to extrapolate the effect of QC for thicker films as shown in Fig. 1b. A decrease in bandgap energy by increasing the number of layers has been shown to be due to interlayer coupling and screening effects, which change the electronic wave function hybridization in the valleys of both the valence and conduction bands.27 As can be seen in Fig. 1b, bandgap values calculated using DFT, DFT + vdW, and GW calibration are 1.2 (0.15) eV, 1.2 (0.51) eV, and 2.43 (1.5) eV for ML (bilayer) PtSe2 film, respectively. In other words, comparable bandgaps to conventional semiconductors are expected in thin PtSe2 films; for example, bilayer and trilayer PtSe2 films have bandgaps comparable with GaAs and Ge, respectively. Our predicted bandgap values are benchmarked against other values from literature in Fig. 1b.

Thickness-dependent bandgap of platinum diselenide (PtSe2) films from first-principles calculations. a Band structure of a monolayer pristine PtSe2 film obtained from our density function theory (DFT) calculations. b Bandgap energy versus PtSe2 film thickness from our DFT (solid green), DFT corrected by van der Waals interactions (solid red), and calibrated by GW calculations (solid black). Dash-dotted lines are guide for the eye. The black dashed curve shows a power law fit α/Lβ, where L is the film thickness with α and β as fitting parameters. Data from the literature is benchmarked in this figure. PBE: Perdew–Burke–Ernzerhof; LDA: local density approximation; GGA: generalized gradient approximation; SOC: spin–orbit coupling; HSE: Heyd–Scuseria–Ernzerhof

The role of vacancies is also investigated from first-principles using fully relativistic electronic structure calculations based on DFT implemented in OpenMx28 and QuantumATK.29 The electronic energy within the framework of Kohn–Sham DFT is calculated using pseudo-atomic localized basis functions. The localized basis functions allow the consideration of larger supercell dimensions and hence lower vacancy density. The effect of SOC must be considered in PtSe2 films due to its strong effect in the 5d orbitals of the transition metal atoms. Grimme’s dispersion correction for the vdW interaction is also incorporated in our calculations.30 Periodic boundary conditions are applied to create simulation supercells and the cell dimension along the film growth axis is chosen to be >2 nm to avoid any interaction between the periodic images of the neighboring slabs. The geometries are fully relaxed until the force acting on each atom is <0.01 eV/Å. The structure consists of a single defect in 6 × 6 × 1 supercell corresponding to defect density of 2.3 × 1013 cm−2. The periodic images of the point defects are more than 2 nm apart from each other, where defect–defect interaction is negligible. In the calculation of point defects, instead of removing the atom from the lattice, it is replaced by an “empty” atom. Empty atoms are basis functions in the vacancy center with zero pseudopotential cores and zero number of electrons. These basis set orbitals can be populated to host a finite electron density in a region where there are no real atoms. The lattice parameters of the relaxed pristine PtSe2 film after geometry optimization are shown in Supplementary Fig. 2. After the geometry optimization of the structure with the Pt vacancy, the position of the point-defect neighbor atoms is modified in comparison with their position in the pristine structure as shown in this figure. The Se atoms at the top layer next to the Pt vacancy move outward, while the Se atoms at the bottom layer move downward. This movement of the Se atoms results in a slight shrinkage of Pt-Se bond lengths (bPt-Se) near the vacancy from 2.54 to 2.51 Å and an increase in the diagonal separation between the Se-Se atoms from 2 × bPt-Se = 5.08 to 5.45 Å, as indicated in the Supplementary Fig. 2, and are consistent with the previously reported results (ref. 23 and ref. 45 therein; ref. 31 and ref. 42 therein).

Using supercells in studying the effects of vacancies is inevitable in first-principles calculations. However, as the size of the supercell increases, the corresponding first Brillouin zone (BZ) shrinks and as a result bands of the supercell are extremely “folded” into the first BZ. Therefore, it is challenging to analyze the effects of vacancies and impurities perturbation and to directly compare the folded bands with the reference band structure of a primitive cell or with the experimental results obtained by angle-resolved photoemission spectroscopy (ARPES) measurements. A procedure to unfold the primitive cell Bloch character hidden in the supercell eigenstates is known as “unfolding.” By applying the unfolding procedure, the band structure of a supercell will be mapped to the band structure of a reference primitive cell.32,33 Utilizing linear combination of atomic orbital basis sets in the presence of a perturbation, such as vacancy, allows mapping of the symmetry breakers, which perturb the band structure.

The unfolded band structures of the ML and bilayer PtSe2 films with a Pt vacancy are shown as contour plots in Fig. 2. The primitive cell band structure of the pristine structure is shown by black solid lines as a reference. As mentioned above, SOC is considered, which provides a band structure that could directly be comparable with spin-ARPES measurements. As can be seen in Fig. 2, the CBM of the ML and bilayer PtSe2 films is located halfway between the Γ and M points. In the PtSe2 ML, the VBM is located at the Γ point, while there are two peaks in the valence band edge at either side of the Γ point (M-shape signature) for the bilayer PtSe2, which are in excellent agreement with previously reported band structures experimentally obtained by ARPES measurements for ML PtSe28 and bilayer PtSe2.18 The band structure of ML PtSe2 supercell with Pt vacancy before unfolding is presented in Supplementary Fig. 3, which in comparison with Fig. 2 demonstrates that the unfolded band structure of the supercell can be directly compared with corresponding pristine unit cell structures.

Effects of Pt vacancy on the band structure of platinum diselenide (PtSe2) films. Unfolded band structure of (left) monolayer PtSe2 and (right) bilayer PtSe2 film with Pt vacancy shown using contour plots of total weight intensity. The primitive cell band structure of pristine PtSe2 is shown using black solid lines, which are in excellent agreement with band structures experimentally obtained by angle-resolved photoemission spectroscopy (ARPES) measurements for monolayer8 and bilayer18 PtSe2. Total density of states (DoS) of each film is shown in the right panel. The localized states corresponding to the Pt vacancy are located close to the edge of the valence band within the bandgap and are shown by arrows. Zero of the energy shows the Fermi level. These results indicate indirect bandgap nature of monolayer and bilayer PtSe2 films. The calculated band structures also indicate an increased hole mobility moving from the monolayer to the bilayer structure in PtSe2

The unfolding method also reveals vacancy-induced almost-flat localized energy states within the bandgap indicating high carrier mass and hence low mobility and strong localized nature of vacancies in these supercells, which can also be realized from partial density of states (DoS) presented in Supplementary Fig. 4. The total DoS on the right panel of Fig. 2 is mapped to the band structure, where arrows indicate the defect-induced states. In this figure, the energy axis is referenced to the Fermi energy (EF), and as can be seen, the Fermi level is shifted towards the valence band edge in the case of Pt vacancy, indicating that the Pt vacancy results in a p-type characteristic of the PtSe2 films. Another important outcome of this study is that on the contrary to most of the other ultra-thin TMDs, indirect-to-direct transition of bandgap is not observed in ML PtSe2 film (ref. 34 and references therein).

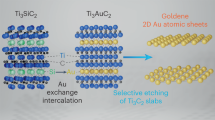

Experimental results

In this study, PtSe2 thin films are synthesized by TAC of pre-deposited Pt layers on Si/SiO2 substrates. A growth temperature of 400 °C was used, and growth was achieved directly on the Si/SiO2 substrate (see the Methods section for more details). In order to investigate the influence of QC effects in PtSe2, films with different thicknesses are prepared. Cross-sectional transmission electron microscope (XTEM) images of the as-grown films with 0.7 and 1 nm Pt nominal thickness as the staring material are shown in Fig. 3, illustrating the layered structure and polycrystalline nature of the PtSe2 films after conversion. The PtSe2 film thicknesses are 2.5–3 and 5–6.5 nm for the two Pt starting films after the TAC process. XTEM images of the transferred films are shown in Supplementary Fig. 5, demonstrating successful film transfer. Raman spectra of the PtSe2 films grown from various Pt thicknesses, that is, 0.7, 1, and 1.5 nm, are shown in Supplementary Fig. 6.

As pointed out earlier, PtSe2 films are synthesized on centimeter-scale substrates allowing us to perform Hall measurements. From four-point I–V measurements and Hall measurements, we determined the resistivity, the majority carrier type, the carrier density, and the Hall mobility of the PtSe2 films. The Hall-effect measurements are performed in a van der Pauw configuration with a LakeShore Model 8404 AC/DC (alternate current/direct current) Hall-effect measurement system. See the Methods section for more details. The room temperature Hall-extracted properties of the PtSe2 films are summarized in Table 1. A typical two-point I–V characteristic is shown in Supplementary Fig. 7. The sample has an almost square area of 1 cm2. To ensure reproducibility, 5–6.5 nm PtSe2 samples were made on different occasions over the course of 3 months. The Hall-effect measurement results of the two different batches made with 3-month intervals are shown in Supplementary Table 1, confirming the reproducibility of the process. Very consistent Hall data are obtained growing the PtSe2 films on different substrates, for example, sapphire, results of which are shown in Supplementary Table 2.

The few-layer structure and the approximate thickness of the PtSe2 films, examined by high-resolution XTEM (HR-XTEM), are presented in Fig. 4a. As can be seen, the PtSe2 thin films synthesized from 0.7 to 1 nm Pt starting nominal thickness are 2.5–3 and 5–6.5 nm thick, corresponding to 5–6 and 10–12 atomic layers, respectively. Films are all planar and layered along the XTEM lamella and are polycrystalline, with several nanometer-sized crystalline domains. Hall-effect measurements on all PtSe2 films indicate p-type dominant carrier type, consistent with our atomic-scale simulation including the effects of Pt vacancies in the films (see Fig. 2). The presence of grain boundaries and vacancies is not unexpected given the polycrystalline nature of the films. It is important to note that adsorbates could also be contributing to the p-type behavior observed in the PtSe2 films; hence, an investigation of how the ambient and pressure influence the electrical properties of the PtSe2 films would be valuable in terms of providing a more complete understanding of the factors, which impact the carrier type and carrier density in PtSe2 films. This is the area of an on-going study. The Hall measurements in Table 1 indicate an increase in sheet carrier concentration, and a corresponding decrease in sheet resistivity, as the PtSe2 thickness increases. This is consistent with a semiconductor-to-semimetal evolution in ultra-thin PtSe2 films calculated with our atomic-scale simulations (Fig. 1). As presented in Table 1, the Hall hole mobility values are in the range of 5 to 13 cm2/V·s.

Cross-sectional transmission electron microscopy (XTEM) of platinum diselenide (PtSe2) films and electrical characterization of PtSe2 back-gate devices. a Cross-section TEM image of PtSe2 film with thickness of 2.5–3 nm (left) before and (right) after transfer. Red arrows point to the dark regions under the PtSe2 film inside the oxide. Scale bar is 10 nm. b Room temperature transfer characteristic of a back-gated field-effect transistor (FET) device with a channel thickness of 2.5–3 nm PtSe2, a channel length of 15 µm, and channel width of 45 µm at VDS = 1 V. P-type characteristic and high ON/OFF ratio of 230 has been measured. Field-effect mobility is µFE = 0.3 cm2/V·s. c Room temperature output characteristic of the same device as in b illustrating linear and symmetric variation of the channel current with the drain voltage. d Transfer characteristic of a device with channel length of 15 µm and channel width of 45 µm, and PtSe2 channel thickness of >5 nm at VDS = 50 mV, showing very small current modulation. EA, ON and EA, OFF in b and d are the activation energies at “ON” and “OFF” states, respectively. b and d demonstrate the layer-dependent quantum confinement (QC)-induced bandgap opening reflected in the electrical characteristics of the PtSe2 FETs

To further explore the electrical properties of the PtSe2 films, back-gated FETs were fabricated by patterning Ni/Au metal stack as the source and drain metal contacts to the PtSe2 films on ~85 nm SiO2 on p++-Si (Si/SiO2), followed by defining channel regions of different lengths and widths through etching (see Methods section for details). The p++-Si is used as a shared “metal” back-gate electrode. A polymer-support film transfer process was carried out to allow transfer of the PtSe2 films from their original synthesized Si/SiO2 substrates onto an unprocessed Si/SiO2 for the fabrication of back-gate FETs (see Methods section for details). The motivation for the PtSe2 film transfer is evident from Fig. 4a, indicating potential diffusion of Pt into the underlying SiO2 during the film synthesis,35 shown by the red arrows. A range of samples were diced from the same growth run to allow transfer and processing of nominally identical PtSe2 films. The layered structure and the exact thickness of the PtSe2 films (as-grown and transferred) are evaluated by TEM images as shown in Fig. 4a, demonstrating the successful PtSe2 film transfer. PtSe2 back-gated MOSFETs were fabricated using conventional complementary metal-oxide-semiconductor (CMOS) processing steps, on as-grown and transferred PtSe2 films, with different thicknesses. Details of device fabrication are provided in the Methods section. MOSFETs with different channel lengths and widths were fabricated and typical transfer and output characteristics of the fabricated transistors are shown in Fig. 4b, c. The transfer and output characteristics highlight decreased drain current with positive gate voltage indicating p-type transport behavior of the PtSe2 films consistent with the Hall measurements of large-area films. The ION/IOFF ratio for the PtSe2 MOSFET shown in Fig. 4b is 230, which is higher than previous reports for room temperature operation of PtSe2 devices with channel thickness values in the range 2.5–3 nm.13,17 The same characteristic in semi-log scale is shown in Supplementary Fig. 8a. In the case of the PtSe2 MOSFET based on a channel thickness of 5–6.5 nm (see Fig. 4d), the ION/IOFF ratio decreases to 1.4.36 Based on the DFT calculations, this is consistent with a suppression of QC effect, and hence to the decrease in channel bandgap, as PtSe2 film becomes thicker (see Fig. 1b). Devices with different channel dimensions show similar qualitative behavior of FET devices with p-type channels as shown in Supplementary Figs. 8b and c. Further experimental evidence to support the transition from a semimetal to a semiconductor with decreasing PtSe2 thickness is evident from the activation energy (EA) of the drain current in the ON state and OFF state of the transfer characteristics, as shown in Fig. 4b, d for the 2.5–3 nm and 5–6.5 nm PtSe2 samples, respectively. The activation energy is extracted from temperature-dependent measurements shown in Supplementary Fig. 9. For the 5–6.5 nm PtSe2 sample, the vdW and GW corrected DFT calculations extrapolated to 5–6.5 nm (see Fig. 1b) indicate a close to zero energy gap. This is confirmed by the lack of modulation of the PtSe2 current with gate voltage and the activation energy of the current, which is 50 meV across the gate voltage sweep. By contrast, as shown in Fig. 4b for the 2.5–3 nm PtSe2 device, the activation energy changes from 200 meV in the OFF state to 50 meV in the ON state. It is noted that the OFF state current activation energy of 200 meV is close to the extrapolated theoretical bandgap of the PtSe2 at 2.5 nm, which is ∼250 meV (see Fig. 1b).

From the characteristic presented in Fig. 4b and using \(g_{\mathrm{m}} = \frac{{\partial I_{\mathrm{DS}}}}{{\partial V_{\mathrm{GS}}}} = \frac{{W_{\mathrm{ch}}}}{{L_{\mathrm{ch}}}}C_{\mathrm{ox}}\mu _{\mathrm{FE}}V_{\mathrm{DS}}\), where Wch = 45 µm is the channel width, Lch = 15 µm is the channel length, and Cox = ε0εr/tox, where εr = 3.9 and tox = 85 nm, and Cox is the capacitance per unit area, we extract the field-effect mobility of µFE = 0.3 cm2/V·s. As expected, the field-effect mobility is smaller than the Hall-effect extracted mobility. This calculation represents the lower limit on the channel hole mobility, as contact resistance will result in a reduced voltage drop across the channel. To investigate this point, we calculated the channel resistance Rch = ρchLch/(Wchtch) ≈ 105 Ω, where ρch is the channel resistivity (see Table 1). Considering the total resistance Rtot = VDS/IDS ≈ 3.4 × 106 Ω at a given back-gate bias of VGS = 0 V, we obtain a large contact resistance of Rc = (Rtot – Rch)/2 ≈ 1.65 × 106 Ω compared to the channel resistance; hence, the actual voltage drop across the channel would be Vch ≈ 0.03 V. Using Vch instead of VDS in the gm equation, we obtain µFE ≈ 10 cm2/V·s, which is close to the value obtained from Hall analysis and comparable to reported mobility for CVD-grown films.17 It is important to note that the corrected µFE value of ≈10 cm2/V·s is only an indicative value at the given VGS since the channel and contact resistances are expected to vary with the gate field. The polycrystalline nature of our synthesized PtSe2 films could be another origin of the relatively low mobility compared to previously reported values of 7–210 cm2/V·s obtained from mechanically exfoliated PtSe2 flakes.14 However, considering the benefits of our growth process, namely, the low synthesis temperature, scalability and ease of controlling layer thickness, and the back-gated MOSFET characteristics in Fig. 4b and c, this is quite promising for a p-channel material formed at 400 °C. Contact engineering could further improve the device performance by structuring PtSe2 films, benefiting from thick “bulk” semimetallic regions as source and drain contacts, and thin semiconducting channel connecting source and drain regions.37,38 Due to the linear behavior of the output characteristic of the FETs (Fig. 4c), the possibility of a Schottky barrier-limited field-effect mobility is discarded.39 This linear behavior could also be attributed to the small band offset at the source and drain contacts with respect to the edge of the valence band of the channel region in the case of Pt vacancies (see Fig. 2). Many reports in literature have indicated an ambipolar behavior in the transfer characteristic for TMD-based MOSFETS.40,41 Our devices do not indicate an ambipolar response, and are consistent with a tunnel junction for holes and a Schottky barrier for electrons at the PtSe2/Ni interface.

Electrical behavior of the PtSe2 FETs was also characterized at different temperatures. The variation of the drain current activation energy with back-gate voltage is shown in Supplementary Fig. 9. For the transferred PtSe2 film, in Supplementary Fig. 9a, the activation energy changes from 190 meV in the OFF state, which is close to the extrapolated PtSe2 bandgap, to around 50 meV in the ON state. In the case of the non-transferred PtSe2 films (see Supplementary Fig. 9b), the extracted EA is in the range of 140–160 meV and does not change by the back-gate voltage. This result, in conjunction with the TEM analysis in Fig. 4a, indicates an interaction of the Pt with the SiO2 substrate during growth, which prevents back-gate modulation of the current. The effect is removed after PtSe2 film transfer, where back-gate modulation of the drain current and variation in the associated activation are evident. In the case of the PtSe2 films with a thickness >5 nm, shown in Supplementary Fig. 9c, the extracted EA is around ~50 meV and demonstrates no variation with back-gate voltage consistent with our atomic-scale simulations (see Fig. 1), suggesting very small bandgap for a >5 nm PtSe2 films. These results demonstrate that bulk PtSe2 exhibits metallic-like properties, in clear contrast to the semiconducting few-layer PtSe2.

As shown in Supplementary Fig. 10, for the transferred film with 2.5–3 nm PtSe2 channel thickness, the ION/IOFF of a typical device (Wch = 40 µm and Lch = 15 µm) increases with reducing temperature. From Supplementary Fig. 10, it is evident that the temperature dependence of the drain current activation energy is primarily driven by the 200 meV activation energy of the OFF state current, which results in the increase of ION/IOFF from ~80 (at 30 °C) to ~4.5 × 102 (at −50 °C). From a technology point of view, room temperature characteristics of FET devices is of most importance; nonetheless, by extrapolating the temperature-dependent data of Supplementary Fig. 10, the ION/IOFF could increase to >1.5 × 105 at 20 K, which would be comparable with the previously reported ratio on an exfoliated PtSe2 flake at cryogenic temperatures.13

Discussion

Considering the potential technology implications of this work, TAC of Pt to PtSe2 is a scalable process that can be achieved at 400 °C. Figure 5 shows the results presented in this work compared to alternative approaches to form PtSe2, which have been reported in the literature. The figure plots the maximum temperature of the process against the area of the PtSe2 samples formed. The plot highlights that the TAC process can form PtSe2 below the BEOL thermal budget limit for silicon CMOS (at around 450 °C), and importantly, this growth is achieved on amorphous SiO2. This opens up the possibility that these films could be integrated into the BEOL of a silicon CMOS process, to provide semiconducting or semimetallic layers above conventional integrated circuits.42 For the samples presented in this work, it was necessary to transfer the PtSe2 films, with evidence that Pt was interacting with the SiO2 near-surface region during PtSe2 formation. This motivates the need to study in detail the potential interaction of the Pt with the SiO2, as well as exploring insulating diffusion barriers, which could circumvent the need for PtSe2 film transfer. This is an area of ongoing research.

In conclusion, this work presents a theoretical and experimental study of QC effects in layered PtSe2 films as a function of film thickness. PtSe2 films with layer numbers increasing from 1 to 4 were studied by ab initio simulations with fully relaxed structures. VdW interactions and GW calibration have shown significant modification in the bandgap energy of the films, predicting QC-induced bandgaps comparable with conventional semiconductors for ML (2.43 eV) and bilayer (1.50 eV) PtSe2 consistent with film thickness less than the calculated Bohr radius. The influence of Pt vacancies on the PtSe2 band structure considering SOC has been investigated, indicating that a Pt vacancy acts as an acceptor, moving the Fermi level towards the PtSe2 valence band edge. Large-area PtSe2 films with different thicknesses were synthesized by a TAC process at 400 °C on Si/SiO2 substrates. The PtSe2 films exhibit a p-type nature with mobility values in the range of 5–13 cm2/V·s as measured by van der Pauw Hall characterization. Back-gated FET devices with different channel dimensions were fabricated using CMOS standard photolithography and etching showing room temperature ION/IOFF of excess 230 for a 2.5–3 nm PtSe2 film, which drops to about 1.4 for 5–6.5 nm PtSe2 channel, consistent with the ab initio simulations of a semimetal-to-semiconductor transition due to QC effects in thin films.

Our theoretical and experimental results demonstrate the potential for large area growth of polycrystalline PtSe2 thin films for applications in the next generation of nanoelectronic devices. The ability to form layered PtSe2 at 400 °C on an amorphous SiO2 substrate, with hole mobilities exceeding 10 cm2/V·s, opens up potential applications in areas such as flexible electronics and integrating new functions into the BEOL of existing semiconductor technologies.

Methods

Details of DFT and GW calculations

PtSe2 electronic structures are calculated using DFT as implemented in OpenMX28, QuantumATK29 and Quantum Espresso.43 OpenMX and Quantum Espresso calculate the electronic energy within the framework of Kohn–Sham DFT using pseudo-atomic localized basis and plane wave basis functions, respectively. The plane wave calculations are performed with an energy cutoff of 180 Rydberg and 16 × 16 × 1 k-point Monkhorst–Pack grid. Norm-conserving pseudopotentials and generalized gradient approximation (GGA) for the exchange correlation potential28,44 are considered. Numerical atomic orbital basis sets of s3p3d2 are used for both Pt and Se atoms in OpenMX. Green’s function theory provides quasi-particle energies using the electron self-energy operator containing the effects of exchange and correlations with other quasi-particles. The Yambo program is used in this work to perform the GW calibration to quasi-particle energies within first-order perturbation theory starting from the Kohn–Sham eigenstates.45 The effective Coulomb interaction is set to zero in real space within the vacuum region such that quasi-particles do not interact with their periodic images.46 As a result, the periodicity of the structure is reduced using a cutoff for the Coulomb interaction in the direction transverse to the PtSe2 film. In the GW calculations, the method in ref. 26 has been used enabling improved convergence in the bandgap energies with a reduced set of empty states as well as requiring the GW correction to be applied for individual k-points of interest. A 16 × 1 × 1 k-point Monkhorst–Pack grid in the irreducible BZ is used with all G-vectors included in the GW calculations.

Materials synthesis

PtSe2 thin films were synthesized using a TAC process similar to that previously described for MoS2 and WS2,47 MoSe2 and WSe2,48 and PtSe2.9,11 Pt layers of different thicknesses were sputtered onto Si/SiO2 substrates using a Gatan precision etching and coating system. The Pt samples were selenized in a quartz tube furnace with two independently controlled heating zones. Pt samples were loaded in the primary heating zone and heated to 400 °C. The Se source Se powder (Sigma-Aldrich, 99.99%) was loaded in the secondary heating zone, which was heated to the melting point of Se (∼220 °C). Ar/H2 (9:1), with a flow rate of 150 sccm, was used to transport the vaporized Se to the Pt samples. A rotary vane pump was used to evacuate the system and keep it under vacuum, and the pressure during selenization was typically ∼0.7 Torr. A dwell time of 2 h was used to ensure complete selenization.

Hall-effect measurements

The Hall-effect measurements were performed in a van der Pauw configuration49 with a LakeShore Model 8404 AC/DC Hall-effect measurement system.50 The system can provide DC or AC magnetic fields over a variable range up to ± 1.7 T (DC) or a fixed range up to ~1.2 T root mean square at a frequency of 0.1 or 0.05 Hz. The measurements in this work were performed at room temperature. The main parameters directly applied, measured, and extracted with the Hall-effect measurement system are the measured Hall voltage, VH = IBRH-sheet (where RH-sheet = RH/t) = (IBhf)/(nse) = IBµHρs = (IBµHRW)/L, where I is the applied excitation current, B is the applied DC or AC magnetic field, RH-sheet is the extracted sheet Hall coefficient (and RH is the Hall coefficient), ns is the extracted sheet carrier concentration (where the carrier concentration (n) is given by n = ns/t), hf is the applied Hall factor (equal to unity for this work), µH is the extracted Hall mobility, ρs is the measured sheet resistivity by four-point measurement, where ρs = (πFAB(RA + RB)/(2ln(2))), with the resistivity given by p = tρs, and RA and RB are the measured four-point orthogonal resistances, and FAB is the solution to the van der Pauw equation and is proportional to the ratio of the perpendicular four-point orthogonal resistances between the equivalent geometrical contacts (i.e., RA and RB). FAB is between 0 and 1.0 depending on the accuracy of the solution to the van der Pauw equation (all results reported here are between 0.99 and 1.0).

Transmission electron microscopy

XTEM was prepared using a Dual Beam Focused Ion Beam (FIB) FEI Helios NanoLab 600i. A 50 nm carbon layer, which was followed by a 300 nm platinum layer, were deposited within the Dual Beam FIB by electron beam-induced deposition and 2 µm-thick carbon layer with ion beam-induced deposition. These three layers were grown for protection before the milling process. The lamella was prepared and thinned down to less than 200 nm thickness. The thinning at 30 kV was finished by polishing at 5 kV to reduce the ion beam-induced damage to a <2 nm thin layer on both sides. TEM analysis was performed using a JEOL JEM-2100 at 200 kV in bright field mode.

Back-gated device fabrication and electrical characterization

Back-gate field-effect transistors were fabricated by patterning source and drain metal contacts using standard photolithography followed by e-beam evaporation of Ni (20 nm)/Au (200 nm) and lift-off process. The PtSe2 film was then patterned using a photoresist mask and an SF6-based inductively coupled plasma etch to form the channel, as shown in the inset of Fig. 4b. Electrical transport properties of the back-gated devices were measured with a semiconductor device parameter analyzer (Agilent B1500a) and using Cascade semi-automated probestation at room and different temperatures.

Film transfer process

The synthesized as-grown PtSe2 thin films were transferred onto unprocessed Si/SiO2 substrates using a typical polymer-support transfer technique. Polymethyl methacrylate (PMMA, MicroChem) was spin coated onto the as-grown PtSe2. The SiO2 layer under the PtSe2 was removed by a wet-etching process using 2 M sodium hydroxide at room temperature. After cleaning in de-ionized water, the PtSe2 with PMMA layers were transferred onto the substrates. The PMMA was removed by immersion in acetone at room temperature for 20 min.

Data availability

The data that support the findings of this study are available from the corresponding author upon reasonable request.

References

Wang, Q. H., Kalantar-Zadeh, K., Kis, A., Coleman, J. N. & Strano, M. S. Electronics and optoelectronics of two-dimensional transition metal dichalcogenides. Nat. Nanotechnol. 7, 699–712 (2012).

Chhowalla, M. et al. The chemistry of two-dimensional layered transition metal dichalcogenide nanosheets. Nat. Chem. 5, 263–275 (2013).

Xu, X., Yao, W., Xiao, D. & Heinz, T. F. Spin and pseudospins in layered transition metal dichalcogenides. Nat. Phys. 10, 343–350 (2014).

Novoselov, K. S., Mishchenko, A., Carvalho, A. & Castro Neto, A. H. 2D materials and van der Waals heterostructures. Science 353, aac9439 (2016).

Batude, P. et al. 3D sequential integration: application-driven technological achievements and guidelines. IEEE International Electron Devices Meeting (IEDM), 52–55, San Francisco, CA, USA (2017).

Guo, G. Y. & Liang, W. Y. The electronic structures of platinum dichalcogenides: PtS2, PtSe2 and PtTe2. J. Phys. C 19, 995–1008 (1986).

Zhuang, H. L. & Henning, R. G. Computational search for single-layer transition-metal dichalcogenide photocatalysts. J. Phys. Chem. C 117, 20440–20445 (2013).

Wang, Y. et al. Monolayer PtSe2, a new semiconducting transition-metal-dichalcogenide, epitaxially grown by direct selenization of Pt. Nano Lett. 15, 4013–4018 (2015).

Yim, C. et al. High-performance hybrid electronic devices from layered PtSe2 films grown at low temperature. ACS Nano 10, 9550–9558 (2016).

Wagner, S. et al. Highly sensitive electromechanical piezoresistive pressure sensors based on large-area layered PtSe2 films. Nano Lett. 18, 3738–3745 (2018).

Yim, C. et al. Electrical devices from top-down structured platinum diselenide films. npj 2D Mater. Appl. 2, 5 (2018).

Yim, C. et al. Wide spectral photoresponse of layered platinum diselenide-based photodiodes. Nano Lett. 18, 1794–1800 (2018).

Ciarrocchi, A., Avsar, A., Ovchinnikov, D. & Kis, A. Thickness-modulated metal-to-semiconductor transformation in a transition metal dichalcogenide. Nat. Commun. 9, 919 (2018).

Zhao, Y. et al. High‐electron‐mobility and air‐stable 2D layered PtSe2 FETs. Adv. Mater. 29, 1604230 (2017).

Wang, Z., Li, Q., Besenbacher, F. & Dong, M. Facile synthesis of single crystal PtSe2 nanosheets for nanoscale electronics. Adv. Mater. 28, 10224–10229 (2016).

Liu, K. et al. Synthesis of two-dimensional semiconductor single-crystal PtSe2 under high pressure. J. Mater. Sci. 53, 1256–1263 (2018).

Xu, H. et al. Controlled doping of wafer-scale PtSe2 films for device application. Adv. Funct. Mater. 29, 1805614 (2019).

Yan, M. et al. High quality atomically thin PtSe2 films grown by molecular beam epitaxy. 2D Mater. 4, 045015 (2017).

O’Brien, M. et al. Raman characterization of platinum diselenide thin films. 2D Mater. 3, 021004 (2016).

Miro, P., Ghorbani-Asl, M. & Heine, T. Two dimensional materials beyond MoS2: noble-transition-metal dichalcogenides. Angew. Chem. Int. Ed. 53, 3015–3018 (2014).

Kandemir, A. et al. Structural, electronic and phononic properties of PtSe2: from monolayer to bulk. Semicond. Sci. Technol. 33, 085002 (2018).

Huang, Z., Zhang, W. & Zhang, W. Computational search for two-dimensional MX2 semiconductors with possible high electron mobility at room temperature. Materials 9, 716 (2016).

Zulfiqar, M., Zhao, Y., Li, G., Nazir, S. & Ni, J. Tunable conductivity and half metallic ferromagnetism in monolayer platinum diselenide: a first-principles study. J. Phys. Chem. C 120, 25030–25036 (2016).

Clark, O. J. et al. Dual quantum confinement and anisotropic spin splitting in the multivalley semimetal PtSe2. Phys. Rev. B 99, 045438 (2019).

Schilfgaarde, M., Kotani, T. & Faleev, S. Quasiparticle self-consistent GW theory. Phys. Rev. Lett. 96, 226402 (2006).

Berger, A., Reining, L. & Sottile, F. Efficient GW calculations for SnO2, ZnO, and rubrene: he effective-energy technique. Phys. Rev. B 85, 085126 (2012).

Bradley, A. J. et al. Probing the role of interlayer coupling and coulomb interactions on electronic structure in few-layer MoSe2 nanostructures. Nano Lett. 15, 2594–2599 (2015).

Ozaki, T. Variationally optimized atomic orbitals for large-scale electronic structures. Phys. Rev. B 67, 155108 (2003).

Grimme, S. Semiempirical GGA-type density functional constructed with a long-range dispersion correction. J. Comput. Chem. 27, 1787–1799 (2006).

Manchanda, P., Enders, A., Sellmyer, D. J. & Skomski, R. Hydrogen-induced ferromagnetism in two-dimensional Pt dichalcogenides. Phys. Rev. B 94, 104426 (2016).

Ku, W., Berlijn, T. & Lee, C. C. Unfolding first-principles band structures. Phys. Rev. Lett. 104, 216401 (2010).

Lee, C. C., Yamada-Takamura, Y. & Ozaki, T. Unfolding method for first-principles LCAO electronic structure calculations. J. Phys. Condens. Matter 25, 345501 (2013).

Zhang, Y. et al. Direct observation of the transition from indirect to direct bandgap in atomically thin epitaxial MoSe2. Nat. Nanotechol. 9, 111–115 (2014).

Jones, S. W. Diffusion in Silicon 37 (IC Knowkedge LLC, 2008).

Li, L. et al. Wafer-scale fabrication of recessed-channel PtSe2 MOSFETs with low contact resistance and improved gate control. IEEE Trans. Electron Dev. 65, 4102–4108 (2018).

Ansari, L., Fagas, G., Colinge, J. P. & Greer, J. A proposed confinement modulated gap nanowire transistor based on a metal (tin). Nano Lett. 12, 2222–2227 (2012).

Gity, F. et al. Metal-semimetal Schottky diode relying on quantum confinement. Microelectron. Eng. 195, 21–25 (2018).

Bartolomeo, A. D. et al. Asymmetric Schottky contacts in bilayer MoS2 field effect transistors. Adv. Funct. Mater. 28, 1800657 (2018).

Bartolomeo, A. D. et al. Pressure‐tunable ambipolar conduction and hysteresis in thin palladium diselenide field effect transistors. Adv. Funct. Mater. 29, 1902483 https://doi.org/10.1002/adfm.201902483 (2019).

Podzorov, V., Gershenson, M. E., Kloc, Ch, Zeis, R. & Bucher, E. High-mobility field-effect transistors based on transition metal dichalcogenides. Appl. Phys. Lett. 84, 3301 (2004).

IRDS. The International Roadmap for Devices and Systems: More Moore 2017 Edition. In IEEE Advancing Technology for Humanity (2018). https://irds.ieee.org/images/files/pdf/2017/2017IRDS_MM.pdf (2017).

Giannozzi, P. et al. QUANTUM ESPRESSO: a modular and open-source software project for quantum simulations of materials. J. Phys. Condens. Matter 21, 395502 (2009).

Perdew, J. P., Burke, K. & Ernzerhof, M. Generalized gradient approximation made simple. Phys. Rev. Lett. 77, 3865 (1996).

Marini, A., Hogan, C., Grüning, M. & Varsano, D. Yambo: an ab initio tool for excited state calculations. Comput. Phys. Commun. 180, 1392–1403 (2009).

Rozzi, C. A., Varsano, D., Marini, A., Gross, E. K. U. & Rubio, A. Exact Coulomb cutoff technique for supercell calculations. Phys. Rev. B 73, 205119 (2006).

Gatensby, R. et al. Controlled synthesis of transition metal dichalcogenide thin films for electronic applications. Appl. Surf. Sci. 297, 139–146 (2014).

Gatensby, R., Hallam, T., Lee, K., McEvoy, N. & Duesberg, G. S. Investigations of vapour-phase deposited transition metal dichalcogenide films for future electronic applications. Solid-State Electron. 125, 39–51 (2016).

Van der Pauw, L. J. A method of measureing specific resistivity and Hall effect of discs of arbitrary shape. Philips Res. Rep. 13, 1 (1958).

User’s Manual. Model 8404 AC/DC Hall effect measurement system, P/N 119-841, Rev. 1.3, 25 March 2014, Lake Shore Cryotronics, Inc., 575 McCorkle Blvd., Westerville, OH 43082-8888 USA (www.lakeshore.com).

Acknowledgements

This work is supported by Science Foundation Ireland (SFI) through grants 15/IA/3131, 12/RC/2278, and 15/SIRG/3329. SFI/HEA Irish Center for High-End Computing (ICHEC) is acknowledged for the provision of computational facilities and support. F.G. and L.A. would also like to acknowledge funding from Irish Research Council (IRC) through awards GOIPD/2016/643 and GOIPD/2018/653, respectively. G.S.D. acknowledges Graphene Flagship under Contract 785219. Special thanks to Fearghal Donnellan and Sinéad Barnett from Cork Institute of Technology for artistic contribution.

Author information

Authors and Affiliations

Contributions

L.A. conducted the theoretical calculations and atomic-scale simulations. N.M., C.O.C. and C.P.C. synthesized PtSe2 films and performed spectroscopic characterization. F.G. conceived and designed the experiments and the mask layout, performed Hall-effect measurements, film transfer and device fabrication, and electrical characterization. S.M., K.F.B., and J.L. helped with device characterization. G.M. performed TEM. R.S., T.S.-L., R.D., E.C. and R.E.N. performed other sample characterizations. F.G. and L.A. wrote the manuscript. P.K.H. and G.S.D. helped with the planning of the experiments and the interpretation of the results, and supervised the project. All authors discussed the results and reviewed the manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher’s note: Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Ansari, L., Monaghan, S., McEvoy, N. et al. Quantum confinement-induced semimetal-to-semiconductor evolution in large-area ultra-thin PtSe2 films grown at 400 °C. npj 2D Mater Appl 3, 33 (2019). https://doi.org/10.1038/s41699-019-0116-4

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41699-019-0116-4

This article is cited by

-

Effect of crystallinity and thickness on thermal transport in layered PtSe2

npj 2D Materials and Applications (2022)

-

Two-dimensional noble transition-metal dichalcogenides for nanophotonics and optoelectronics: Status and prospects

Nano Research (2022)

-

Anisotropic electrical properties of aligned PtSe2 nanoribbon arrays grown by a pre-patterned selective selenization process

Nano Research (2022)

-

Versatile band structure and electron—phonon coupling in layered PtSe2 with strong interlayer interaction

Nano Research (2022)

-

Morphology-controlled growth of large-area PtSe2 films for enhanced hydrogen evolution reaction

Rare Metals (2022)