Abstract

Source-gated transistors (SGTs) are thin-film devices which rely on a potential barrier at the source to achieve high gain, tolerance to fabrication variability and low series voltage drop, relevant to a multitude of energy-efficient, large-area, cost effective applications. The current through the reverse-biased source barrier has a potentially high positive temperature coefficient, which may lead to undesirable thermal runaway effects and even device failure through self-heating. Using numerical simulations we show that, even in highly thermally-confined scenarios and at high current levels, self-heating is insufficient to compromise device integrity. Performance is minimally affected through a modest increase in output conductance, which may limit the maximum attainable gain. Measurements on polysilicon devices confirm the simulated results, with even smaller penalties in performance, largely due to improved heat dissipation through metal contacts. We conclude that SGTs can be reliably used for high gain, power efficient analog and digital circuits without significant performance impact due to self-heating. This further demonstrates the robustness of SGTs.

Similar content being viewed by others

Introduction

Thin-film transistor-based large area electronics have a long and successful history1,2,3,4. Simple circuits and arrays of display elements have been produced with increasing sophistication, area, density and performance for several decades5. Recently, advances in technology have permitted rapid performance gains of research devices6,7,8 and a diversification of applications attempted9,10,11,12,13,14,15,16,17,18,19,20. This is in part due to fabrication refinements, but mainly a result of completely new processes18,21,22,23,24,25,26,27,28,29,30,31,32, substrate materials33,34,35 and semiconductors26,36,37,38,39,40,41,42,43,44,45,46.

Throughout this surge in complexity, speed and extent of applicability, the fundamental device, the thin-film field effect transistor (TFT FET), has witnessed several proposed developments25,38,40,47,48,49,50,51,52,53,54 with a wide range of practicality, yet its operation has remained essentially unchanged. With the introduction of new material systems, challenges such as contact effects have become increasingly more obvious and efforts have been devoted to understanding and addressing them55,56,57,58,59,60.

One device which uses contact effects constructively is the source-gated transistor (SGT)61,62,63,64,65. It is a type of field-effect device realized in a very similar manner to conventional TFTs. The main functional difference is a consequence of the deliberate introduction of a potential barrier at the source electrode, usually through the use of a Schottky contact: when the source barrier is reverse-biased by the applied drain voltage in normal operation, the depletion region at the contact extends across the semiconductor forming a pinch-off region at the edge of the source closest to the drain. This results in low saturation voltage and, with proper design66, in output characteristics independent of drain voltage in saturation. From an application point of view, this allows very high gain to be achieved starting at low voltages, for energy-efficient operation67.

A number of other properties arise from the current-control method (at the source, as opposed to within the semiconducting channel): tolerance to some geometrical variations, stability under bias stress, but also drain current which is unavoidably lower than that of a FET with the same geometry but with an ohmic source contact.

Furthermore, the current in a Schottky barrier SGT is potentially highly dependent on temperature68,69,70,71,72,73. High sensitivity integrated temperature sensors are possible applications74,75,76, but for generic use, where temperature dependence should be low, design decisions can be taken to minimize drain current temperature coefficient (TC)77. In both situations, however, TC is positive. In principle, self-heating during normal operation could lead to performance degradation, or even catastrophic failure through thermal runaway.

In this paper we investigate self-heating effects in Schottky-barrier source-gated transistors. Multi-physics numerical simulations on low-barrier, high current SGTs provide insight into device operation and design strategies for optimization. Measurements on polysilicon SGTs confirm our findings.

The functional features of source-gated transistors make them well suited to specific applications at strategic points in circuit design. Their value is augmented by the fact that their technology is very similar to conventional TFT FETs, allowing the fabrication of SGTs and TFT with very small changes to the process. In practice, circuits including both types of devices would make the most of the characteristics of each: the high speed segments would be designed with FETs (high current devices), while the low power, high gain, or high matching requirement sub-circuits would use the SGT (high gain, geometrically tolerant device) as the main component. By understanding and providing solutions to the limitations of the SGT architecture, the overall performance and reliability of future circuits can be improved, at a time when a significant increase in complexity and environmental constraints are projected for upcoming TFT applications.

Results

Two dimensional simulations of a conventional bottom-gate, top-contact polysilicon SGT were performed with the Silvaco TCAD suite. The structure’s cross-section is shown in Fig. 1a, with its corresponding output (Fig. 1b) and transfer characteristics (Fig. 1c). Flat saturated output curves, early saturation and supra-linear dependence of drain current on nominal barrier height are observed.

Source-gated transistor (SGT) structure and characteristics.

(a) Cross section of the SGT defined in Silvaco Atlas for 2D electrical and multi-physics simulation; (b) Typical output characteristic of the simulated SGTs showing flat saturation characteristics and low saturation voltage, for source barrier height ϕB = 0.35 eV; (c) Transfer characteristics of simulated SGTs for three values of potential barrier at the source metal-semiconductor contact, ϕB, (calculated here as the difference between the conduction band energy and the Fermi level of the metal). For equal steps in barrier height change, the curves are equally spaced on the logarithmic Y scale.

The effect of enabling self-heating (SH) in the simulator (lattice heating) is shown in Fig. 2a, in which one output curve was traced for three cases: (I) SH disabled, (II) SH enabled with gate as heat sink and (III) SH enabled, with only the base of the device (bottom of 10 μm-thick polymer film) as heat sink. Figure 2b shows the temperature distribution for case III, which is the worst-case scenario. For this biasing condition (high VG and high VD), the hot spot is approximately 9 K higher than ambient temperature and is located at the edge of the source closest to the drain. A horizontal cross-section of heat generation at the semiconductor-insulator interface is given in Fig. 2c. For practical purposes, heat power consists entirely of Joule (resistive) heating. The full map of heat generation in the semiconductor (Fig. 2d) shows that it is concentrated around the depletion region at the source edge, with some contribution from the accumulated channel region at the insulator interface and at the extremities of the source and drain.

Self-heating in poly-silicon source-gated transistors for (VG = 10 V, VD = 5 V, ϕB = 0.35 eV).

(a) Output characteristic showing the effect of self-heating with no heat-sink and with the gate acting as heat-sink; (b) Cross-section of SGT device and temperature distribution when a 25 μm-thick, low thermal conductivity plastic substrate is used and none of the electrodes are designated as heat sinks (worst case, hypothetical scenario). Peak temperature is localized around the edge of the source contact closest to the drain; (c) cut-line of heat generation taken 10 nm into the semiconductor at the insulator interface. The Joule (resistive) power dissipation dominates greatly and losses due to recombination are proportionally small; (d) device cross section with power generation overlay (logarithmic scale). All power generation takes place in the semiconductor. The data for other materials results from meshing and is spurious89.

Case II (gate as heat sink) leads to lower self-heating effects, on the order of 2 K, as presented in Fig. 3. Source and drain electrode shape was changed to compare rectangular contacts (Fig. 3a) with practical (design rule-obeying) metallizations which overlap the contact hole in the insulator, creating passive field relief66,78 structures (Fig. 3b). The drain-side field plate has no effect, but the source field plate extending into the source-drain gap moves the hot-spot away from the source contact edge. The hot-spot temperature is also lower than in the case without field plate. A cross-section of temperature taken at the semiconductor-insulator interface for the four possible combinations of field plates is shown in Fig. 3c. The higher temperature increase in the device without the field plate results in an larger increase of the drain current (positive TC) as illustrated by Fig. 3d. Figure 3e shows the shape of the corresponding output characteristics, as a visual comparison of the output conductance (saturated characteristic flatness).

Effects of field relief structures built into electrodes and of ambient temperature on self-heating characteristics of polysilicon source-gated transistors (VG = 10 V, VD = 5 V, ϕB = 0.35 eV).

(a) device cross-section and temperature distribution when the gate is a constant-temperature heat-sink (300 K); (b) The same structure but with field-relief structures (field plates) built into the source and drain electrodes; (c) cut-line of temperature distribution showing the effect of source field plate: the hot-spot is translated away from the tip of the source and the maximum temperature is smaller. The effect of the drain field plate is negligible; (d) excess drain current against the reference (self-heating mechanism disabled in simulator) for devices with different source electrode architectures; (e) Output characteristics illustrating the effect of incorporating field plates into the source and drain electrodes; (f) The positive temperature coefficient of drain current results in higher current levels as ambient temperature increases. Consequently, self-heating increases, but peak temperature increase relative to ambient is low (no field plate).

Figure 3f illustrates the consequences of operating the device at higher ambient temperature: increased self-heating.

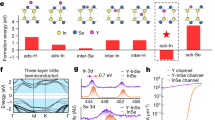

The recently-described method79 of lowering the overall temperature coefficient of SGT drain current by increasing the source length, S, was applied to the simulated structure. Current from the “bulk” of the source has a lower temperature dependence than that injected at the edge of the source closest to the drain. In Fig. 4a, the net temperature at the semiconductor-insulator interface is plotted for four values of S, while in Fig. 4b, the effect of changing S on the output characteristics of devices with and without source plates is presented.

Effect of source electrode length (S) on the self-heating behaviour of source-gated transistors.

(a) for short S, the current increases with S, thus the heating in the depletion region at the edge of the source also increases. For very long S, the current stops increasing with S, since the potential drop across the semiconductor far from the source edge closest to the drain becomes negligible and heating (and temperature remain constant); (b) Output characteristics for VG = 10 V and two extreme values of S. Due to the different temperature dependence of the currents being injected from the edge and from the bulk of the source, the short-source device is more susceptible to changes to drain current due to self-heating. Incorporating a field plate lowers the local temperature at the tip of the source, restoring the low output conductance to the saturated current of the device with a short source.

Polysilicon SGT output characteristics have been measured using three shapes of drain voltage (sweep) waveforms. The photograph of the glass substrate with an array of devices and the micrograph of a single device are shown in Fig. 5a,b, respectively. The main difference between the waveforms is illustrated in Fig. 5c. Figure 5d represents the measured output characteristics using the three input waveforms. Finally, Fig. 5e shows the additional current generated by self-heating as a function of drain voltage.

Measurements on fabricated polysilicon source-gated transistors confirm low self-heating effects.

(a) Photograph of substrate (glass) with array of SGTs; (b) micrograph (top view) of typical fabricated SGT. Drain 1 is used during measurements, with Drain 2 floating; (c) Waveforms for measuring output characteristics: to measure an output curve, the gate voltage is set (step), then the drain voltage is changed (sweep) in equal increments for a “regular” measurement – (1), or pulsed, returning to zero between consecutive measurements (“pulsed” – 2), with a 500 ms pause is introduced between each pulse. To ensure that the effect measured is to do with heating rather than time-dependent processes (e.g. trapping), a version of (1) with a 500 ms pause between a VD increase and current measurement was also performed (“pause”); (d) Output characteristics obtained by measuring with the three VD–changing methods; (e) In saturation, the “regular” and “pause” curves are identical, while the difference in current between the “regular” and “pulsed” measurements increases with VD, revealing the self-heating effect.

Discussion

Polysilicon was chosen as the material system for this study as it allows the use of a low source barrier for high currents and maximum self-heating. Additionally, the kink effect due to impact ionization80,81,82,83,84, present in high mobility silicon TFTs and MIS85 structures and albeit small in SGTs66,67 contributes to the total current and SH at high drain bias, making this material the most susceptible to self-heating effects.

However, due to the complexity of the calculation, the multi-physics algorithms did not converge when material defects, impact ionization and lattice heating were enabled simultaneously. For this reason, the defect statement was abandoned in favour of a reduction of carrier mobility throughout the semiconductor to model a crystalline material with polysilicon-like current capability. We deemed this to be a reasonable simplification, as the impact ionization model was kept enabled and likewise the essential lattice heating routine. The discrepancy with real polycrystalline material behaviour is largely related to transport in the accumulated channel. In SGTs, current is controlled in the source region and the source-drain channel acts as a proportionally small series resistor and its precise magnitude should not play a role in current control, just like source-drain gap, d, is not an essential SGT design parameter within a large range of values.

In the output characteristics we chose a relatively small maximum value for drain voltage, 5V. Previous studies, including measurements on polysilicon66,67, amorphous silicon61,62,86 and amorphous polymer77 devices have shown that the SGT architecture successfully suppresses kink effect for flat output characteristics up to at least |VD| = 10 V. For this study, we have focused on the low range VD, as one of the most likely applications for SGTs in an analog environment involves operation in saturation at VD lower than VG − Vth, impossible for conventional FET structures.

The value for effective barrier height in the absence of bias, ϕB0 was chosen as 0.35 eV: low enough to inject current at a level suitable for practical applications and simultaneously to contribute significantly to self-heating; but high enough to be the exclusive current-limiting and control mechanism (as opposed to the accumulated channel between the source and the drain in a standard FET).

The effects of heating are most pronounced in the structure with a thick insulating polymeric substrate which is a poor heat conductor and a single heat sink on the bottom of the substrate. Figure 2a shows the gradual divergence of curves obtained with lattice heating enabled and disabled as drain voltage is increased. For the range of VD considered, it is important to note that at VG = 10 V the source is pinched off, but the drain is not (the accumulated channel is operating in the FET linear region). Changes in VD above the source pinch-off voltage (VSAT1) are almost entirely dropped across the pinch-off region at the source, changing the shape of the depletion region to reach equilibrium, with small or no changes in drain current (see Supplementary Figure S1). The resistance seen by the current travelling horizontally through the pinched off area underneath the tip of the source, however, increases with the expansion of the source depletion region. Larger heat generation is observed at high VD due to Joule heating (P = R2I) and the hot spot is in the region where resistance is highest: the source pinch-off region (Fig. 2b). Heating occurs, naturally, in the regions of the device with the largest current density, with the majority localized in the resistive source pinch-off region (Fig. 2c,d). The edge of the metal-semiconductor contact closest to the drain sees the most severe temperature increase. This is the most temperature-sensitive area of the device, as it corresponds to a metal-semiconductor contact in reverse bias and its reverse current has a large, positive temperature dependence. As a consequence, current injected by that area of the source increases with temperature, leading to the effect seen in Fig. 2a.

We have previously found that field relief plates at the source of SGTs have beneficial effects in suppressing drain field dependence of drain current74, including kink effect, up to comparatively high VD. These structures are normally part of contact design in photolithographically-defined top contacts. Incorporating a field plate into the source contact creates a pinch-off region at its tip and away from the edge of the source (Supplementary Figures S2 and S3). This resistive region screens the edge of the source from drain-induced electric field, but it also contributes to heat generation as drain current crosses it. The effect is a shift of the hot spot away from the highly temperature-sensitive edge of the source (Fig. 3a,b). A drain field plate, while easy to implement, has practically no effect on self-heating (Fig. 3c), largely due to the fact that at the drain voltages considered the drain is not pinched off. The drain current increase due to self-heating is significantly suppressed when a source field plate is included (Fig. 3e).

As the control mechanism in the area of the source closest to the drain (reverse-biased Schottky barrier) has a strong positive dependence on temperature, ambient temperature variations will also lead to changes in the magnitude of current injected at the source. Figure 3f shows the effect of raising the ambient temperature by 31 K. Total current passing through the pinch-off region at the source increases, leading to larger joule heat generation, higher temperature in the critical device region and ultimately even higher current injection from the edge of the source (positive feedback). The temperature increase due to self-heating is small (1 K for an ambient increase of 31 K) and, while somewhat detrimental to output characteristic shape, the effect is not enough to cause catastrophic thermal runaway.

A means of controlling the temperature sensitivity of SGT drain current is changing the length of the source, S. Depending on S, the dominant current injection mechanism changes77. The current from bulk of the source has a lower TC and devices with long sources, in which the bulk injection dominates, should see smaller effects of self-heating on drain current. Figure 4a shows the increase in hot-spot temperature with S. This is to be expected, as larger S implies larger drain current. For very long S, however, the current saturates with S77,87. The lack of increase in current from S = 10 μm to S = 100 μm is reflected in the overlapping temperature cross-section plots. Despite the increase in hot-spot temperature, the long source device has little increase in drain current, as the majority of its current is injected from the low-TC bulk area of the source. The extremely short S (didactical) device, however, has significant modulation of drain current due to self-heating and the presence of a field plate greatly alleviates this problem by shifting the hot spot as discussed previously. Practically, moderate values of S in the few-microns to 10 μm region should produce good self-heating performance while being easily implemented with current technology and keeping gate overlap capacitance in a reasonable range.

Polysilicon SGTs (Fig. 5) have been fabricated on glass substrates according to the recipe in67,88. Measurement routines have been modified in an attempt to isolate the effect of self-heating on drain current. These devices have a built-in field plate and show excellent output characteristics up to VD = 30 V.

Regular measurements use a continuous drain sweep. The pulsed routine keeps the gate voltage constant for the duration of an output scan and asserts the drain voltage only for the duration of the measurement, with a 500 ms pause between data points (Fig. 5c). By keeping VG constant, the trapping effects and large time constants can be eliminated as causes of differences seen between the “regular” and “pulsed” measurements, isolating the self-heating effects. The 500 ms pause was judged to be sufficient for heat dissipation between data point measurements. For completeness, a conventional drain sweep was performed, but with 500 ms pause between measurements and with VD still asserted (“pause”).

Output characteristics (Fig. 5d) show the extent of the differences obtained while measuring with the three waveforms. Differences are minimal, even at high drain voltage. Figure 5e presents the findings. The “regular” and “pause” measurements show virtually identical values in saturation and no drain voltage dependence, denoting negligible time-dependent effects in the settling of the current between the regular measurement (tens of milliseconds) and the one including the 500 ms pause.

The difference between the “regular” and “paused”-type curves shows minimal drain voltage dependence, with a maximum current difference of approximately 0.75% at VG = 20 V and VD = 20 V. The current is larger in the “regular” curve. We deduce that the difference is due to self-heating and we relate the effect to the processes described above. Its magnitude is diminished due to lower current density in the fabricated device (source barrier approximately 50 meV higher); to a comparatively long source (10 μm); to the presence of an effective field plate; extending 2 μm over the edge of the source contact; and to ample metallic connections to all electrodes for improved heat transport. Self-heating plays a minimal role in polysilicon SGTs and is likely to be completely negligible in other, lower-current technologies. The only performance penalties are the slight reduction of intrinsic gain (proportional to (dID/dVD)−1) and minuscule increased power dissipation due to the increase in drain current.

In conclusion, we have studied the effects of self-heating on the performance of polysilicon source-gated thin-film transistors. The temperature coefficient of drain current (TC) in SGTs with Schottky source contacts is positive and potentially very high and could lead to thermal runaway and even device failure. Using Silvaco Atlas we performed multi-physics numerical simulations on a polysilicon structure. Two thermal scenarios were studied: in the first, the gate acted as the constant-temperature heat sink; in the second, theoretically worst-case scenario, none of the electrodes were heat-sinks. In neither case was self-heating more than a few Kelvin, localized in a hot-spot near the edge of the source closest to the drain.

Our findings suggest that self-heating does not significantly increase device temperature for the SGT and thus the (temperature-dependent) drain current is largely unchanged during operation. Device optimizations can, however, reduce the effect of self-heating further. A field plate, incorporated in the source contact and standard practice for adherence to layout design rules in photolithographically defined top contacts to large-area silicon devices, can relieve the tip of the source from drain electric field but also shift the temperature hot-spot away from the source edge, lowering the temperature seen by this highly temperature-sensitive current injection area. Source length, S, can also be used as a parameter for lowering the effective temperature coefficient of drain current, as the bulk of the source is both less sensitive to temperature and experiences a lower temperature increase through self-heating.

We found that practically all self-heating occurs through Joule heating, suggesting that higher current density produces proportionally higher heat dissipation. For this reason, polysilicon was chosen due to its high mobility; for a low source barrier, the current density in the device is high, which in turns leads to increased self-heating. Lower mobility materials and high-barrier, low-current devices will experience still less self-heating.

Measurements on polysilicon devices confirm our simulation results. The measured self-heating effect on drain current is minimal, due to improved heat dissipation and somewhat lower current levels in the measured device.

Thermal runaway and device failure is unlikely. From a circuit design perspective, self-heating may cause modest current increase in devices operating at high currents in close proximity for prolonged periods. Local temperature differences through self-heating across a large-area circuit may lead to mismatched currents and output conductance. Judicious layout matching and proper device design (field plate, S) can all but eliminate these variations for most practical purposes.

Source-gated transistors are well suited to specialized use in high gain, low-power circuit blocks for a variety of analog and digital functions. With proper design, they can be very tolerant to process and operating condition variations, leading to reliable, consistent performance.

Methods

Device modelling

The Silvaco suite (Atlas v. 5.18.3.R; Athena v. 5.20.0.R) was used for source-gated transistor (SGT) device modelling and simulation.

The two-dimensional structure cross-section was defined using Athena (Fig. 1a). A bottom aluminium gate 100 nm thick, a 100 nm layer of silicon oxide which served as a gate dielectric and a 40 nm silicon layer were successively defined on a 10 um-thick polymer substrate. The drain contact was self-aligned to the gate. The source completely overlapped the gate, as is convenient for SGT operation. The drain region was implanted with phosphorus (Athena parameters: dose = 1.0e15 energy = 4) to create the ohmic drain contact. Source (varying length, S) and drain (1 μm) contacts were defined on the semiconductor with and without overhangs (1 μm long, separated from semiconductor by 40 nm oxide), typical of top contact definition, to serve as field relief structures. Source-drain gap was d = 1 μm, typical of current low-cost lithographic technology. The whole structure was passivated with 200 nm silicon oxide. Device width is assumed W = 1 μm.

Device simulation

Electrical and thermal properties were set in Silvaco Atlas prior to multi-physics simulation. Meshing in the x direction was set to 25 nm spacing at the source edge closest to the drain to increase the resolution in the region of interest where both self-heating and temperature-dependent current occur. For reduced simulation time, mesh spacing was relaxed in non-essential areas of the device, such as the edges of the design space and in the substrate.

The drain electrode was set to Aluminium and the contact was made ohmic through implantation in Athena. A source contact barrier was deliberately introduced through defining the source contact as Schottky with a nominal barrier (metal work function to semiconductor electron affinity) of ϕB0 = 0.35 eV. Gate work function was set to 5.2 eV to obtain a turn-on voltage around VG = 0 V.

Thermal properties were set to the defaults for the respective materials. Material conductivity, important for resistive heating estimation, is set through the mobility definition statements. Lattice heating was enabled as a means of simulating self-heating. Both Joule (resistive) heating and generation-recombination heating were extracted as two-dimensional overlays in the device cross-section at a number of operating points. Note that heating results are only valid in the semiconductor and all data in the insulating layers is spurious, resulting from meshing and calculation limitations89.

The worst case scenario was simulated by allowing only the bottom of the structure to act as heat sink. The device is separated from this constant (ambient) temperature heat sink by the thermally insulating plastic substrate (thermal conductivity: 0.15 Wcm−1K−1, thickness 25 μm). A more realistic but still challenging scenario was studied in which the gate acted as the constant temperature heat sink.

Initially, the semiconductor was set to default Atlas polysilicon parameters. However, upon enabling impact ionization and self-heating, convergence was difficult. The material was then modified to crystalline silicon with reduced mobility of 200 for electrons and 20 for holes. This is still a good approximation of the real self-heating effect, as the current is limited by the barrier.

Output and transfer characteristics were saved, together with the device snapshots at various biasing conditions (linear regime, saturation) and for a number of geometrical and electrical variations. A batch run consisted of different permutations of source length S, source work function ϕB0, ambient temperature, heat sink position and presence or absence of drain and source field plates.

Fabrication

Polysilicon structures (Fig. 5a,b) fabricated on glass substrate according to67,88 were studied. Device width was W = 50 μm, source-drain gap d = 10 μm, source length S = 8 μm , semiconductor thickness tsi = 40 nm, insulator thickness 200 nm oxide and 200 nm nitride. Cr and AlTi source/drain contacts were evaporated bulk doping, creating a 2 μm field plate separated by 120 nm oxide from the semiconductor. Bulk doping in the semiconductor was 0.5·1012 BF2.

Measurement

The in-house measurement setup consisted of LabView-controlled Keithley 2400 source-measure units for setting drain and gate voltages and a Keithley 6458 picoammeter for measuring source current. The devices were probed with 5 um W needles on a Wentworth probe station with a heated, electrically isolated, motorized X–Y stage. Ambient temperature was 25C. The devices were exposed to the ambient fluorescent indoor light during measurement.

The control software was modified in order to make the effects of self-heating apparent. For tracing output characteristics, the conventional setup asserted a gate voltage which was kept constant during a drain voltage sweep from zero to maximum voltage. We call this the “regular” measurement sequence (Fig. 5c). The modified “pulsed” sequence involves asserting the drain voltage for the duration of each data point measurement, then returning it to zero for 500 ms to allow induced heat to dissipate. Finally, a dummy mode denoted “pause” was used in which the drain voltage is stepped as per the “regular” scheme without returning to zero after each measurement, but a 500 ms pause was introduced after each data point with drain voltage applied.

Additional Information

How to cite this article: Sporea, R. A. et al. Self-Heating Effects In Polysilicon Source Gated Transistors. Sci. Rep. 5, 14058; doi: 10.1038/srep14058 (2015).

References

Lilienfeld, J. E. inventor; Device for controlling electric current, United States patent US 1,900,018 A. 1933 Mar 7.

Heil, O. inventor; Improvements in or relating to Electrical Amplifiers and other Control Arrangements and Devices, Great Britain patent Pat GB 439,457 A. 1934 Mar 2.

Brody, T. P. The thin film transistor - A late flowering bloom. Electron Devices, IEEE Transactions on 31, 1614–1628, 10.1109/t-ed.1984.21762 (1984).

Weimer, P. K. The TFT A New Thin-Film Transistor. Proceedings of the IRE 50, 1462–1469, 10.1109/jrproc.1962.288190 (1962).

Fischer, A. G., Brody, T. P. & Escott, W. S. Design of a liquid crystal color TV panel. Proc IEEE Conf. on Disp. Dev. 1972. IEEE. 64–66 (1972).

Dimitrakopoulos, C. D. & Mascaro, D. J. Organic thin-film transistors: A review of recent advances. IBM Journal of Research and Development 45, 11–27, 10.1147/rd.451.0011 (2001).

Smith, J. et al. Solution-Processed Small Molecule-Polymer Blend Organic Thin-Film Transistors with Hole Mobility Greater than 5 cm2/Vs. Advanced Materials 24, 2441–2446, 10.1002/adma.201200088 (2012).

Mei, Y. et al. High Mobility Field-Effect Transistors with Versatile Processing from a Small-Molecule Organic Semiconductor. Advanced Materials 25, 4352–4357, 10.1002/adma.201205371 (2013).

Kaltenbrunner, M. et al. An ultra-lightweight design for imperceptible plastic electronics. Nature 499, 458–463, 10.1038/nature12314 (2013).

Hwang, S.-W. et al. A Physically Transient Form of Silicon Electronics. Science 337, 1640–1644, 10.1126/science.1226325 (2012).

Chen, Y. J. E., Yuan-Jiang, L. & Yueh-Hua, Y. Investigation of Polysilicon Thin-Film Transistor Technology for RF Applications. Microwave Theory and Techniques, IEEE Transactions on 58, 3444–3451, 10.1109/tmtt.2010.2076911 (2010).

Guoxuan, Q. et al. RF Characterization of Gigahertz Flexible Silicon Thin-Film Transistor on Plastic Substrates Under Bending Conditions. Electron Device Letters, IEEE 34, 262–264, 10.1109/led.2012.2231853 (2013).

Myny, K. et al. A thin-film microprocessor with inkjet print-programmable memory. Sci. Rep. 4, 10.1038/srep07398 (2014).

Sarma, K. in Handbook of Visual Display Technology (eds Chen, J. et al. ) Ch. 62, 897–932 (Springer Berlin Heidelberg, 2012).

Liao, F., Chen, C. & Subramanian, V. Organic TFTs as gas sensors for electronic nose applications. Sensors and Actuators B: Chemical 107, 849–855, 10.1016/j.snb.2004.12.026 (2005).

Guo, D. et al. Indium-tin-oxide thin film transistor biosensors for label-free detection of avian influenza virus H5N1. Analytica Chimica Acta 773, 83–88 (2013).

Kai, S. et al. Three-Mask Polysilicon Thin-Film Transistor Biosensor. Electron Devices, IEEE Transactions on 61, 2170–2176, 10.1109/ted.2014.2315669 (2014).

Someya, T. et al. Conformable, flexible, large-area networks of pressure and thermal sensors with organic transistor active matrixes. Proceedings of the National Academy of Sciences of the United States of America 102, 12321–12325, 10.1073/pnas.0502392102 (2005).

Kuo, Y. & Nominanda, H. Nonvolatile hydrogenated-amorphous-silicon thin-film-transistor memory devices. Applied Physics Letters 89, 173503 (2006).

Zaumseil, J., Friend, R. H. & Sirringhaus, H. Spatial control of the recombination zone in an ambipolar light-emitting organic transistor. Nat Mater 5, 69–74 (2006).

Sirringhaus, H. 25th Anniversary Article: Organic Field-Effect Transistors: The Path Beyond Amorphous Silicon. Advanced Materials 26, 1319–1335, 10.1002/adma.201304346 (2014).

Feng, L. et al. Ultralow-Voltage Solution-Processed Organic Transistors With Small Gate Dielectric Capacitance. Electron Device Letters, IEEE 34 (1), 129–131 (2012).

Sun, B. & Sirringhaus, H. Solution-Processed Zinc Oxide Field-Effect Transistors Based on Self-Assembly of Colloidal Nanorods. Nano Letters 5, 2408–2413, 10.1021/nl051586w (2005).

Park, S. K., Jackson, T. N., Anthony, J. E. & Mourey, D. A. High mobility solution processed 6,13-bis(triisopropyl-silylethynyl) pentacene organic thin film transistors. Applied Physics Letters 91, 063514 (2007).

Liu, N. et al. High-Performance, All-Solution-Processed Organic Nanowire Transistor Arrays with Inkjet-Printing Patterned Electrodes. Langmuir 27, 14710–14715, 10.1021/la2033324 (2011).

Park, J. H. et al. All-solution-processed, transparent thin-film transistors based on metal oxides and single-walled carbon nanotubes. Journal of Materials Chemistry C 1, 1840–1845, 10.1039/c2tc00405d (2013).

Shahrjerdi, D. et al. High-Performance Air-Stable n-Type Carbon Nanotube Transistors with Erbium Contacts. ACS Nano 7, 8303–8308, 10.1021/nn403935v (2013).

Wang, G., Hirasa, T., Moses, D. & Heeger, A. J. Fabrication of regioregular poly(3-hexylthiophene) field-effect transistors by dip-coating. Synthetic Metals 146, 127–132 (2004).

Wang, G., Swensen, J., Moses, D. & Heeger, A. J. Increased mobility from regioregular poly(3-hexylthiophene) field-effect transistors. Journal of Applied Physics 93, 6137–6141, 10.1063/1.1568526 (2003).

Gleskova, H., Wagner, S., Soboyejo, W. & Suo, Z. Electrical response of amorphous silicon thin-film transistors under mechanical strain. Journal of Applied Physics 92, 6224–6229 (2002).

Tsao, H. N. et al. The Influence of Morphology on High-Performance Polymer Field-Effect Transistors. Advanced Materials 21, 209–212, 10.1002/adma.200802032 (2009).

Yu, X. et al. Flexible spray-coated TIPS-pentacene organic thin-film transistors as ammonia gas sensors. Journal of Materials Chemistry C 1, 6532–6535, 10.1039/c3tc31412j (2013).

Yong-Hoon, K., Dae-Gyu, M. & Jeong-In, H. Organic TFT array on a paper substrate. Electron Device Letters, IEEE 25, 702–704, 10.1109/led.2004.836502 (2004).

Theiss, S. D. & Wagner, S. Amorphous silicon thin-film transistors on steel foil substrates. Electron Device Letters, IEEE 17, 578–580, 10.1109/55.545776 (1996).

Wu, M., Pangal, K., Sturm, J. C. & Wagner, S. High electron mobility polycrystalline silicon thin-film transistors on steel foil substrates. Applied Physics Letters 75, 2244–2246 (1999).

Fortunato, E., Barquinha, P. & Martins, R. Oxide Semiconductor Thin-Film Transistors: A Review of Recent Advances. Advanced Materials 24, 2945–2986, 10.1002/adma.201103228 (2012).

Nomura, K. et al. Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors. Nature 432, 488–492 (2004).

Yang, J., Lee, M. S., Lee, H.-J. & Kim, H. Hybrid ZnO nanowire networked field-effect transistor with solution-processed InGaZnO film. Applied Physics Letters 98, 253106 (2011).

Dimitrakopoulos, C. D. & Malenfant, P. R. L. Organic Thin Film Transistors for Large Area Electronics. Advanced Materials 14, 99–117 (2002).

Cui, Y., Zhong, Z., Wang, D., Wang, W. U. & Lieber, C. M. High Performance Silicon Nanowire Field Effect Transistors. Nano Letters 3, 149–152, 10.1021/nl025875l (2003).

Katz, H. E., Bao, Z. & Gilat, S. L. Synthetic Chemistry for Ultrapure, Processable and High-Mobility Organic Transistor Semiconductors. Accounts of Chemical Research 34, 359–369, 10.1021/ar990114j (2001).

Gao, X. & Hu, Y. Development of n-type organic semiconductors for thin film transistors: a viewpoint of molecular design. Journal of Materials Chemistry C 2, 3099–3117, 10.1039/c3tc32046d (2014).

Chua, L.-L. et al. General observation of n-type field-effect behaviour in organic semiconductors. Nature 434, 194–199 (2005).

Martel, R., Schmidt, T., Shea, H. R., Hertel, T. & Avouris, P. Single- and multi-wall carbon nanotube field-effect transistors. Applied Physics Letters 73, 2447–2449 (1998).

Vaillancourt, J. et al. All ink-jet-printed carbon nanotube thin-film transistor on a polyimide substrate with an ultrahigh operating frequency of over 5 GHz. Applied Physics Letters 93, 243301 (2008).

He, T., Stolte, M. & Würthner, F. Air-Stable n-Channel Organic Single Crystal Field-Effect Transistors Based on Microribbons of Core-Chlorinated Naphthalene Diimide. Advanced Materials 25, 6951–6955, 10.1002/adma.201303392 (2013).

Chen, C.-M., Chien, F.-T. High Performance Four-Masks GOLDD TFT Structure without Additional Ion Implantation. Proc AM-FPD 2014, 165–168 (2014).

Bonfiglietti, A. et al. Analysis of electrical characteristics of gate overlapped lightly doped drain (GOLDD) polysilicon thin-film transistors with different LDD doping concentration. Electron Devices, IEEE Transactions on 50, 2425–2433, 10.1109/ted.2003.819250 (2003).

Inoue, A. et al. Flexible organic field-effect transistor fabricated by thermal press process. physica status solidi (a) 210, 1353–1357, 10.1002/pssa.201228776 (2013).

Li, F. M. et al. Zinc Oxide Nanostructures and High Electron Mobility Nanocomposite Thin Film Transistors. Electron Devices, IEEE Transactions on 55, 3001–3011, 10.1109/ted.2008.2005180 (2008).

Colinge J. P. et al. Junctionless Nanowire Transistor (JNT): Properties and design guidelines. Solid-State Electronics 65, 33–37 (2011).

Opoku, C., Chen, L., Meyer, F. & Shkunov, M. Solution Processable Nanowire Field-Effect Transistors. MRS Online Proceedings Library 1287, null-null, 10.1557/opl.2011.1437 (2011).

Austin, M. D. & Chou, S. Y. Fabrication of 70 nm channel length polymer organic thin-film transistors using nanoimprint lithography. Applied Physics Letters 81, 4431–4433 (2002).

Cui, D., Li, H., Park, H. & Cheng, X. Improving organic thin-film transistor performance by nanoimprint-induced chain ordering. Journal of Vacuum Science & Technology B 26, 2404–2409 (2008).

Valletta, A. et al. Contact effects in high performance fully printed p-channel organic thin film transistors. Applied Physics Letters 99, 233309 (2011).

Lustig, N. & Kanicki, J. Gate dielectric and contact effects in hydrogenated amorphous silicon‐silicon nitride thin‐film transistors. Journal of Applied Physics 65, 3951–3957 (1989).

Gundlach, D. J., Li Li, J. & Jackson, T. N. Pentacene TFT with improved linear region characteristics using chemically modified source and drain electrodes. Electron Device Letters, IEEE 22, 571–573, 10.1109/55.974580 (2001).

Street, R. A. & Salleo, A. Contact effects in polymer transistors. Applied Physics Letters 81, 2887–2889 (2002).

Gundlach, D. J. et al. An experimental study of contact effects in organic thin film transistors. Journal of Applied Physics 100, 3884 (2006).

Deen, M. J., Kazemeini, M. H. & Holdcroft, S. Contact effects and extraction of intrinsic parameters in poly(3-alkylthiophene) thin film field-effect transistors. Journal of Applied Physics 103, 124509 (2008).

Shannon, J. M. & Gerstner, E. G. Source-gated thin-film transistors. Electron Device Letters, IEEE 24, 405–407, 10.1109/led.2003.813379 (2003).

Shannon, J. M. & Gerstner, E. G. Source-gated transistors in hydrogenated amorphous silicon. Solid-State Electronics 48, 1155–1161 (2004).

Lindner, T., Paasch, G. & Scheinert, S. Simulated operation and properties of source-gated thin-film transistors. Electron Devices, IEEE Transactions on 52, 47–55, 10.1109/ted.2004.841279(410) 52 (2005).

Ma, A. M. et al. Zinc oxide thin film transistors with Schottky source barriers. Solid-State Electronics 76, 104–108 (2012).

Valletta, A., Mariucci, L., Rapisarda, M. & Fortunato, G. Principle of operation and modeling of source-gated transistors. Journal of Applied Physics 114, 064501 (2013).

Sporea, R. A., Trainor, M. J., Young, N. D., Shannon, J. M. & Silva, S. R. P. Field Plate Optimization in Low-Power High-Gain Source-Gated Transistors. Electron Devices, IEEE Transactions on 59, 2180–2186, 10.1109/ted.2012.2198823 (2012).

Sporea, R. A., Trainor, M. J., Young, N. D., Shannon, J. M. & Silva, S. R. P. Intrinsic Gain in Self-Aligned Polysilicon Source-Gated Transistors. Electron Devices, IEEE Transactions on 57, 2434–2439, 10.1109/ted.2010.2056151 (2010).

Pipinis, P. A., Rimeika, A. K. & Lapeika, V. A. Temperature dependence of the reverse current in Schottky barrier diodes. Semiconductors 32, 785–788, 10.1134/1.1187506 (1998).

Saito, T., Nitanda, K., Syahiman, A., Tokuda, H. & Kuzuhara, M. Temperature-dependent reverse leakage current characterization of n-GaN Schottky diodes. Proc 2011 International Meeting for Future of. Electron Devices, Kansai (IMFEDK), 19–20 May 2011 80–81, Osaka (2011).

Aboelfotoh, M. O. Temperature dependence of the Schottky-barrier height of tungsten on n-type and p-type silicon. Solid-State Electronics 34, 51–55 (1991).

Werner, J. H. & Güttler, H. H. Temperature dependence of Schottky barrier heights on silicon. Journal of Applied Physics 73, 1315–1319 (1993).

Sporea, R. A., Shannon, J. M., Silva, S. R. P., Trainor, M. J. & Young, N. D. Performance trade-offs in polysilicon source-gated transistors Proceedings of the European Solid-State Device Research Conference (ESSDERC) 2010, Seville, Spain, 222–225 (2010, Sept 13–17).

Sporea, R. A. et al. Performance trade-offs in polysilicon source-gated transistors. Solid-State Electronics 65–66, 246–249 (2011).

Sporea, R. A., Shannon, J. M. & Silva, S. R. P. High-Resolution Temperature Sensing with Source-Gated Transistors. Proc. 69th Annual Device Research Conference (DRC). 2011, June, Santa Barbara, CA, USA, 61–62 (2011).

Cahoon, C. & Baker, R. J. Low-Voltage CMOS Temperature Sensor Design Using Schottky Diode-Based References, Proc. IEEE Workshop on Microelectronics and Electron Devices (WMED) 2008 Apr 18, Boise, ID, USA 16–19 (2008).

Pascu, R. et al. High temperature sensor based on SiC Schottky diodes with undoped oxide ramp termination, Proc. 2011 International Semiconductor Conference (CAS), Sinaia, Romania, 2011 Oct 15–17, 379–382 (2012).

Shannon, J. M., Sporea, R. A., Georgakopoulos, S., Shkunov, M. & Silva, S. R. P. Low-Field Behavior of Source-Gated Transistors. Electron Devices, IEEE Transactions on 60, 2444–2449, 10.1109/ted.2013.2264547 (2013).

Dora, Y. et al. High Breakdown Voltage Achieved on AlGaN/GaN HEMTs With Integrated Slant Field Plates. Electron Device Letters, IEEE 27, 713–715, 10.1109/led.2006.881020 (2006).

Sporea, R. A., Overy, M., Shannon, J. M. & Silva, S. R. P. Temperature dependence of the current in Schottky-barrier source-gated transistors. Journal of Applied Physics 117, 184502 (2015).

Valdinoci, M. et al. Floating body effects in polysilicon thin-film transistors. Electron Devices, IEEE Transactions on 44, 2234–2241, 10.1109/16.644643 (1997).

Valletta, A., Gaucci, P., Mariucci, L., Fortunato, G. & Brotherton, S. D. Kink effect in short-channel polycrystalline silicon thin-film transistors. Applied Physics Letters 85, 3113–3115, 10.1063/1.1806252 (2004).

Hack, M. & Lewis, A. G. Avalanche-induced effects in polysilicon thin-film transistors. Electron Device Letters, IEEE 12, 203–205, 10.1109/55.79556 (1991).

Armstrong, G. A., Brotherton, S. D. & Ayres, J. R. A comparison of the kink effect in polysilicon thin film transistors and silicon on insulator transistors. Solid-State Electronics 39, 1337–1346 (1996).

Mariucci, L. et al. Polysilicon TFT structures for kink-effect suppression. Electron Devices, IEEE Transactions on 51, 1135–1142, 10.1109/ted.2004.829860 (2004).

Ogura, S., Tsang, P. J., Walker, W. W., Critchlow, D. L. & Shepard, J. F. Design and characteristics of the lightly doped drain-source (LDD) insulated gate field-effect transistor. Electron Devices, IEEE Transactions on 27, 1359–1367, 10.1109/t-ed.1980.20040 (1980).

Shannon, J. M. & Balon, F. High-Performance Thin-Film Transistors in Disordered and Poor-Quality Semiconductors. Electron Devices, IEEE Transactions on 54, 354–358, 10.1109/ted.2006.888753 (2007).

Sporea, R. A., Xiaojun, G., Shannon, J. M. & Silva, S. R. P. Effects of process variations on the current in Schottky Barrier Source-Gated Transistors Proc. 2009 International Semiconductor Conference (CAS) 2, Sinaia, Romania, 2009 Oct 12–14, 413–416 (2009).

Sporea, R. A., Trainor, M. J., Young, N. D., Shannon, J. M. & Silva, S. R. P. Source-gated transistors for order-of-magnitude performance improvements in thin-film digital circuits. Sci. Rep. 4, 10.1038/srep04295 (2014).

Atlas Users Manual, Silvaco, 2014 Nov 7, online at https://dynamic.silvaco.com/dynamicweb/jsp/downloads/DownloadManualsAction.do?req=silentmanuals&nm=atlas (2014) date of access: 23/07/2015.

Acknowledgements

The work of R.A. Sporea is supported by the Royal Academy of Engineering Academic Research Fellowship Programme. R.A. Sporea and T. Burridge gratefully acknowledge SATRO for the SATROClub Extended Research Placement through which part of this work was conducted. The authors thank Prof J.M. Shannon for useful discussions and valuable advice.

Author information

Authors and Affiliations

Contributions

R.A.S. conceived the study, adapted the measurement platform and performed the measurements. R.A.S. and T.B. performed the simulation and data processing. R.A.S. and S.R.P.S. analyzed and interpreted the results, wrote the paper and reviewed the manuscript.

Ethics declarations

Competing interests

The authors declare no competing financial interests.

Electronic supplementary material

Rights and permissions

This work is licensed under a Creative Commons Attribution 4.0 International License. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in the credit line; if the material is not included under the Creative Commons license, users will need to obtain permission from the license holder to reproduce the material. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/

About this article

Cite this article

Sporea, R., Burridge, T. & Silva, S. Self-Heating Effects In Polysilicon Source Gated Transistors. Sci Rep 5, 14058 (2015). https://doi.org/10.1038/srep14058

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/srep14058

This article is cited by

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.