Abstract

Horizontal gate-all-around field effect transistors (GAAFETs) are used to replace FinFETs due to their good electrostatics and short channel control. Highly stacked nanowire channels are widely believed to enhance drive current of these devices and improve overall transistor density due to their small footprint. Here we demonstrate the fabrication and characterization of nanowire FETs with stacked 16 Ge0.95Si0.05 nanowires and stacked 12 Ge0.95Si0.05 nanowires without parasitic channels. The device has the high on current (ION) of 190 μA per stack (9400 μA/μm per channel footprint) at overdrive voltage (VOV) = drain-source voltage (VDS) = 0.5 V and the high maximum transconductance (Gm,max) of 490μS (24000μS/μm) at VDS = 0.5 V among reported Si/Ge/GeSi 3D nFETs. Note that the transistor performance can be evaluated by the delay, which is depicted as CV/I. If the transistor ION is improved, the delay of standard cell can be reduced, leading to faster operation of the circuit. The subthreshold slope reduction and ION/IOFF improvement are achieved by the parasitic channel removal. In technology computer aided design (TCAD) simulation, the wrap around contacts are useful to reduce the current difference between the channels. With the proper design of transistor height, the gate delay can be also improved.

Similar content being viewed by others

Introduction

The gate-all-around (GAA) devices are used to replace FinFETs for the advanced technology nodes thanks to the superior electrostatics and short channel control1,2,3,4,5,6. The GAA structure with channel stacking can further enhance the drive current for a fixed footprint to achieve high performance and area scaling4. To improve the ION, most efforts are focused on high mobility channels such as the recently commercialized 5 nm node5,6. Ge is an attractive option for the high mobility channel to boost the drive current thanks to its intrinsic higher mobility than Si7. Alternatively, the highly stacked channels to further increase ION is also a knob to achieve the improvement. The systematic work to increase number of vertically stacked channels for ION enhancement with decreasing gate delay is presented in this work. The high etching selectivity between channels and sacrificial layers (SLs) are required for highly stacked channels. Recently, the radical-based highly selective isotropic dry etching was reported to form the highly stacked channels8,9,10. A simple isotropic wet etching by H2O2 has been reported to form stacked 2 nanowires without high energy ion damage in our previous work11,12. Moreover, the stacked 7 Ge0.95Si0.05 nanowires with high performance by wet etching have been reported13,14. To further improve the IOFF, NH4OH + H2O2 wet etching was used to remove parasitic channels14.

In this work, the highest stacked 16 Ge0.95Si0.05 nanowires and stacked 12 Ge0.95Si0.05 nanowires without parasitic channels are demonstrated by the low temperature epitaxy and wet etching. The isotropic wet etching can reach the sufficient selectivity to fabricate the highly stacked Ge0.95Si0.05 nanowires using n+Ge SLs. Note that Si content as low as 5% can reach the etching selectivity between channels and sacrificial layers. Due to the excessive etching in parasitic channel removal, only the stacked 12 nanowires are remained. As compared with our previous work13, higher ION per stack (per footprint), larger Gm,max per stack (per footprint), SS reduction, and ION/IOFF improvement are achieved by increasing number of stacked channels and parasitic channel removal.

Results

Device structure and epilayer

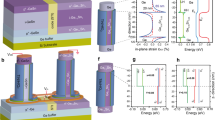

The 3D schematic of the stacked 16 Ge0.95Si0.05 nanowire nFETs are shown in Fig. 1a. The current flows along (110) direction. The highest stacked channels without source/drain (S/D) regrowth is demonstrated. The doping of S/D is obtained by the heavily P-doped Ge sacrificial layers (SLs), which are annealed during the device fabrication to have P diffusion. The process flow of chemical vapor deposition (CVD) epitaxy is shown in Fig. 1b. The top Si of a 200 mm silicon-on-insulator (SOI) substrate was thinned down from 70 to 20 nm by the oxidation in a vertical furnace and dipped into the buffered oxide etchant. After HF dipping to remove the native oxide, a 200 mm SOI substrate was loaded into a rapid thermal chemical vapor deposition system with a cold-wall quartz chamber, followed by 1100 °C H2 baking at 80 torr to further remove the residual native oxide on the SOI surface. GeH4, SiH4, and PH3 were used as the precursors for the following epitaxial growth process. The 150 nm undoped Ge buffer was grown on an SOI wafer at 375 °C using the GeH4 precursor in H2 ambient at 40 torr. Additional in-situ annealing at 800 °C for 3 min in H2 ambient after the Ge buffer growth was used to confine the dislocations near the Ge buffer/SOI interface and to improve the quality of the Ge buffer. For Ge0.95Si0.05 channels, the 25 nm heavily P-doped Ge SL and the 24 nm undoped Ge0.95Si0.05 channel layer were grown on the Ge buffer 16 times repeatedly, followed by the top 44 nm heavily P-doped Ge SL deposition. The thick top n+Ge SL is designed to protect the disappearance of a top channel from etching away after channel release. The n+Ge SLs were grown using GeH4 and PH3 precursors and the Ge0.95Si0.05 channel layers were grown using GeH4 and SiH4 precursors both at 350 °C in H2 ambient at 100 torr. There are a total of 34 epilayers (the undoped Ge buffer + 16 undoped GeSi channel layers + 17 heavily P-doped Ge SLs). The undoped Ge0.95Si0.05 channel layers can suppress the impurity scattering for the high electron mobility, and the heavily P-doped Ge SLs can reduce the S/D resistance. The transmission electron microscopy high angle annular dark field (TEM-HAADF) image of the as-grown epilayers are shown in Fig. 1c. The low-temperature epitaxial growth of channel layers and SLs ensures the entire epilayers metastable without dislocations in the channels and precisely controls the epilayers with good thickness and concentration uniformities both vertically and horizontally. Fig. 1d shows how we achieve high quality epilayers without dislocations in the channels. The total thickness of channel layers should be less than critical thickness for high quality epilayers. The critical thickness versus Ge content is shown is Fig. 1d. The critical thickness of Matthews and Blakeslee theory (thermal equilibrium, high temperature growth) for Ge0.95Si0.05 deposited on Ge is 77 nm, while People and Bean theory (metastable, low temperature growth) has a critical thickness of 4400 nm. In this work, the growth temperature of CVD Ge0.95Si0.05 and n+Ge SL is maintained at 350 °C for the metastable state. The total thickness for stacked 16 undoped Ge0.95Si0.05 channels is 384 nm, which is lower than metastable critical thickness. The low-temperature epitaxial growth of channel layers and SLs ensures the entire epilayers metastable without dislocations.

a 3D schematics of the stacked 16 Ge0.95Si0.05 nanowires. b CVD epitaxy flow with the highlighted features (red). c TEM-HAADF of the epilayers. 16 undoped Ge0.95Si0.05 layers are sandwiched by 17 P-doped Ge sacrificial layers (SLs). Defects are confined at the Ge/Si interface. Note that the 25 nm heavily P-doped Ge SL and the 24 nm undoped Ge0.95Si0.05 channel layer were grown on the Ge buffer 16 times repeatedly, followed by the top 44 nm heavily P-doped Ge SL deposition. d Critical thickness versus Ge content. Note that the material parameter of GeSi is linear combination of Ge and Si (virtual crystal approximation). The critical thickness by Matthews and Blakeslee theory (thermal equilibrium, blue line) of Ge0.95Si0.05 deposited on Ge is 77 nm (blue circle). The critical thickness by People and Bean theory (metastable, orange line) of Ge0.95Si0.05 deposited on Ge is 4400 nm (orange circle). Our growth temperature of CVD Ge0.95Si0.05 and n+Ge SL are maintained at 350 °C for metastable states. The total thickness of stacked 16 undoped Ge0.95Si0.05 channels is 384 nm (red star), lower than critical thickness at metastable state.

Material analysis of epilayers

The as-grown epilayers with stacked 16 Ge0.95Si0.05 channels were analyzed by the high-resolution X-ray diffraction with ω − 2θ scan of (004) reflections (Fig. 2a). The shifting peak to higher 2θ as compared to relaxed Ge indicates the tensile strain in epitaxial Ge buffer. The Ge buffer is 0.2% tensily strained on Si. Note that the tensile strain in Ge buffer is caused by the mismatch of thermal expansion coefficients between Ge and Si. The shoulder in high-resolution X-ray diffraction is the diffraction by Ge0.95Si0.05. To further analyze the strain of epitaxial layers, the reciprocal space mapping was used. The Ge0.95Si0.05 channels are fully tensily strained on the Ge buffer, confirmed by (224) reflections. Ge0.95Si0.05 is 0.4% tensily strained on the Ge buffer (Fig. 2b). Note that the tensile strain in the Ge0.95Si0.05 channels can further improve the electron mobility13,14. The secondary ion mass spectrometry profile of the as-grown epilayers of stacked 16 Ge0.95Si0.05 channels is shown in Fig. 2c. The 16 undoped Ge0.95Si0.05 channel layers are sandwiched by 17 heavily P-doped Ge SLs. For low S/D resistance, the [P] in Ge SLs is as high as ~2 × 1020 cm−3. The minimum [P] in Ge0.95Si0.05 channels are from ~ 4 × 1017 cm−3 to ~2 × 1019 cm−3 and increases from the top to the bottom due to P diffusion during the epi growth (350 °C)13,14,15. The top channel has the lowest [P] due to the least time in CVD epitaxial growth (Fig. 2d). To mitigate this effect, the lower epi growth temperature and less time in CVD epitaxial growth are two key factors. This epilayers were grown using GeH4 and SiH4 precursors. Using high order precursors like Ge2H6 and Si2H6, the epilayers can be grown at lower temperature and enhanced growth rate can reduce the time in CVD epitaxial growth.

High-resolution X-ray diffraction (a), reciprocal space mapping (b), and secondary ion mass spectrometry (c) of the epilayers. d Minimum [P] vs channel number. The Ge and Ge0.95Si0.05 are 0.2% and 0.4% tensily strained, respectively. Note that tensile strain in Ge is caused by the mismatch of thermal expansion coefficients between Ge and Si. The [P] in Ge SLs is as high as ~2 × 1020 cm−3 for low S/D resistance, and the minimum [P] in Ge0.95Si0.05 channels are from ~4 × 1017 cm−3 to ~2 × 1019 cm−3. Note that the Ge, P, and Si are in green, red and blue lines. The minimum [P] increases from top to bottom due to P diffusion, consistent with the diffusion time in the reaction chamber13,14,15. Note that the orange and purple bars correspond to stacked 16 Ge0.95Si0.05 and stacked 8 Ge0.95Si0.05, respectively.

Device fabrication

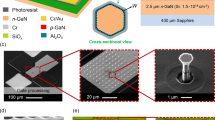

The device fabrication flow of the highly stacked Ge0.95Si0.05 nanowires is summarized in Fig. 3a with the highlighted features. In this work, the S/D and channels are fabricated by the same epilayers without S/D regrowth. The doping of S/D is obtained by the n+Ge SLs, which are annealed during the device fabrication to have P diffusion. The growth temperature of CVD Ge0.95Si0.05 and n+Ge SL is maintained at 350 °C for the metastable state. The total thickness of channel layers should be less than critical thickness to avoid dislocation generation. The additional 800 °C anneal after Ge buffer growth before channel and SL epi was used to confine the misfit dislocations at Ge/SOI interface for epi quality improvement. The thick top n+Ge SL is designed to protect the disappearance of a top channel from etching away after channel release. After CVD epitaxy (34 layers) and SiO2 mask deposition by the plasma enhanced chemical vapor deposition, the e-beam lithography and Cl2-based reactive ion etching (RIE) were used to form the fin structures (Fig. 3b). After fin formation, the plasma enhanced chemical vapor deposition field oxide was deposited. The field oxide was patterned prior to the channel release process to prevent the oxidation and distortion of the released channels. The channel release and Ge buffer were performed by H2O2 wet etching (Fig. 3c) and parasitic SOI channels were removed by NH4OH + H2O2 wet etching. Note that H2O2 wet etching at room temperature was used to etch the Ge buffer and Ge SLs between the channel regions, while NH4OH wet etching at 75 °C16 was used to completely remove the SOI underneath the Ge buffer. The etching selectivity of Ge over Ge0.95Si0.05 is attributed to the heavily doped phosphorus in Si13,14. To investigate the strain after channel release, the strain at the center of GeSi channel is simulated by ANSYS using the average channel width (WCH) and channel height (HCH) in the microbridge structure. The uniaxial tensile strain at the center of the Ge0.95Si0.05 channel increases to 0.44% from the epitaxial strain of 0.4% to further enhance the electron mobility (Fig. 3d). The native oxide was removed by dipping with diluted HCl solution before the gate stack formation to ensure low surface roughness of Ge0.95Si0.05 channels17. After the 10 cycles TMA passivation18, the Al2O3 was conformally deposited around the nanowires by the plasma enhanced atomic layer deposition, followed by the rapid thermal oxidation at 400 °C for 1 min. ZrO2 and in-situ TiN by the plasma enhanced atomic layer deposition were then conformally deposited on the Al2O3. The following 400 °C forming gas annealing was used to crystallize ZrO2 for a large κ value. A thick TiN was then deposited as the gate metal pad by sputtering. The gate metal pad region was defined by RIE and buffered oxide etching. The thick TiN gate metal was used to protect the gate stack and to avoid top nanowires etched away during RIE. Note that RIE with CF4 gas is used to etch TiN/ZrO2/Al2O3 stacks. The S/D pad were then formed by the lithography and wet etching. The wet etching in HF solution to etch field oxide on S/D. After Pt deposited by sputtering, a lift-off process was used to pattern Pt. The 400 °C post metallization annealing were used to form the S/D contacts on Ge:P with [P] ~ 2 × 1020 cm−3 for low S/D resistance. The STEM-HAADF image (Fig. 3e) shows that the stacked 16 Ge0.95Si0.05 nanowires have the largest WCH of 20 nm with all the n+Ge SLs are removed, indicating that the sufficient selectivity of n+Ge SLs over undoped Ge0.95Si0.05 channels by H2O2 wet etching. The nanowires are surrounded by the gate dielectrics and in-situ TiN to ensure the GAA structure (Fig. 3f). The STEM-HAADF image shows the stacked 12 Ge0.95Si0.05 nanowires with total removal of the SOI, Ge buffer, and n+Ge SLs (Fig. 3g). The EDS mapping ensures the GAA structure (Fig. 3h). Note that no S/D regrowth in our process and sacrificial layers are the doping source in S/D. The bending Fig. 3g, h is the artifact of TEM sample preparation due to floating channels affected by ion milling.

Process flow (a) of the highly stacked GeSi nGAAFETs with the highlighted features (red). Tilt 52o SEM after fin formation (b) by the Cl2-based RIE and channel release (c) by H2O2 wet etching. d Simulated strain of 0.44% in the GeSi channel with the average WCH and HCH in the microbridge structure by ANSYS. Note that the orange dash line corresponds the as-grown condition. STEM-HAADF (e) and EDS mapping (f) of the stacked 16 Ge0.95Si0.05 nanowires. STEM-HAADF (g) and EDS mapping (h) of the stacked 12 Ge0.95Si0.05 nanowires w/o parasitic channels. Note that the red arrow points parasitic channel removal. The EDS mapping shows the nanowires surrounded by the in-situ TiN to ensure the GAA structure.

Device performance

The highest stacked 16 Ge0.95Si0.05 nanowires have revolutionary progress, as compared with our previous works13,14,19. The Ge content of 95% in GeSi channels is larger than 85% to ensure the electrons populated in the high mobility L4 valleys13. In previous work20,21, the nanosheets have non-uniform electron distribution across the cross sections, where electron wavefunction is dense at both ends. This causes the degradation of ION per footprint as compared with the nanowires. Increasing the number of stacked channels can further enhance the ION.

The stacked 16 Ge0.95Si0.05 nanowires with LG = 90 nm have the high ION of 190 μA per stack (9400 μA/μm per channel footprint) at VOV = VDS = 0.5 V and the high Gm,max of 490 μS per stack (24,000 μS/μm) at VDS = 0.5 V with the SS of 85 mV/dec (Fig. 4a–c). Note that the ION and Gm,max per channel footprint in this work are normalized by the largest WCH among the stacked channels. The removal of the parasitic channels were made possible by NH4OH + H2O2 etching, and the stacked 12 Ge0.95Si0.05 nanowires were still remained. The high ION of 180 μA per stack (8300 μA/μm) at VOV = VDS = 0.5 V and the high Gm,max of 440 μS per stack (21,000 μS/μm) at VDS = 0.5 V with the good with the good SS of 76 mV/dec are achieved with LG of 70 nm (Fig. 4d–f). The on resistance (RON ≡ VD/ID) is extracted at VDS = 0.5 V and the RON vs VOV is plotted in Fig. 4g. The 0.94X of RON reduction is obtained by stacked 16 nanowires as compared to stacked 12 nanowires at VOV = VDS = 0.5 V. The ideal RON reduction should be 12/16 = 0.75 and the difference is due to parasitic S/D resistance. Moreover, the IOFF of stacked 16 nanowires is dominated by the parasitic channels (Fig. 4i). The parasitic channels have to be removed for further improvement. After the removal of all the stacked nanowires, the low leakage current (~3%) induced by the parasitic channels was measured at VOV = VDS = 0.5 V (Fig. 4i). The stacked 12 Ge0.95Si0.05 nanowires without parasitic channels show lower SS and larger ION/IOFF as compared with the stacked 16 Ge0.95Si0.05 nanowires with parasitic Ge channels by Ge buffer. The SS of stacked 12 Ge0.95Si0.05 nanowires without parasitic channels are 76 mV/dec and 87 mV/dec measured at the VDS of 0.05 and 0.5 V, respectively. The SS of stacked 16 Ge0.95Si0.05 nanowires are 85 mV/dec and 127 mV/dec at VDS of 0.05 and 0.5 V, respectively. The SS is reduced to 76 mV/dec from 85 mV/dec at VDS = 0.05, and the ION/IOFF is improved to ~2 × 105 from ~3 × 104 after removing parasitic channels (Fig. 4j).

ID-VDS (a), Gm-VGS (b), and ID-VGS (c) of the stacked 16 Ge0.95Si0.05 nanowires (red line). ID-VDS (d), Gm-VGS (e), and ID-VGS (f) of the stacked 12 Ge0.95Si0.05 nanowires w/o parasitic channels (blue line). g Ron comparison between stacked 16 nanowires (red line) and stacked 12 nanowires without parasitic channels (blue line). h Benchmarks of ION per stack per footprint vs Gm,max per footprint per floor. i ID-VGS of stacked 16 Ge0.95Si0.05 nanowires (red line) and parasitic Ge channel (orange line). j ID-VGS of stacked 16 Ge0.95Si0.05 nanowires (red line) and stacked 12 nanowires without parasitic channels (blue line). Benchmarks of ION per stack vs Gm,max per stack (k), benchmarks of ION per footprint vs LG (l), and Gm,max per footprint vs SS (m) for Si/Ge/GeSi 3D nFETs. The stacked 16 Ge0.95Si0.05 nanowires have the high ION and Gm,max among reported Si/Ge/GeSi 3D nFETs. Note that solid and open symbols correspond to Ge/GeSi and Si 3D nFETs, respectively. The number in the parentheses in (k), and (l, m) are VDS and WCH, respectively. The red stars correspond to this work.

Benchmarks

The stacked 16 Ge0.95Si0.05 FETs reach the high ION per stack of 190 μA at VOV = 0.5 V and the high Gm,max per stack of 490 μS among reported Si/Ge/GeSi 3D nFETs (Fig. 4k)2,4,7,11,12,13,22,23,24,25,26,27,28,29,30,31,32,33,34. Note that the VDS to benchmark ION and Gm,max is indicated in the parentheses. Ideally, ION and Gm should be enhanced to be 16/12 = 4/3 as the floor number increase from 12 to 16 if S/D resistance is negligible. However, the S/D has neither a sufficient doping concentration nor a sufficient area for metal contact, and the parasitic S/D resistance leads to decreasing ION and Gm per floor with increasing floor number (Fig. 4h). However, the ION and Gm still increases with increasing floor number (Fig. 4k). The benchmarks of ION per footprint vs LG and Gm,max per footprint vs SS are shown in Fig. 4l, m2,4,7,11,12,13,22,23,24,25,26,27,28,29,30,31,32,33,34, respectively. The high ION per footprint of 9400 μA/μm at VOV = 0.5 V and the high Gm,max per footprint of 24,000 μS/μm are achieved among reported Si/Ge/GeSi 3D nFETs. Note that the channel width (WCH) is indicated in the parentheses in Fig. 4l, m.

Improved current distribution, capacitance, and delay by the TCAD simulation

The industrial device structure (Fig. 5a) is used for the simulation of current, capacitances, and delay by the TCAD35. The simulated current vs channel number of the stacked 16 Ge0.95Si0.05 FETs is shown in Fig. 5b. Note that all the current is normalized with respect to the current of the top channel (channel number 16). The series resistance impacts the transistor performance. Three types of S/D are considered in the simulation including S/D doping of 1.3 × 1019 cm−3, S/D doping of 2 × 1020 cm−3, and wrap around contact with S/D doping of 2 × 1020 cm−3 (Fig. 5b). For the S/D doping of 1.3 × 1019 cm−3, the current reduction from the top channel to the bottom channel is as high as 47%. However, for S/D doping of 2 × 1020 cm−3 and the wrap around contact, the series resistance effect can be reduced, leading to only a 3.5% current reduction from the top channel to the bottom channel. Thus, the total current can be proportional to floor#.

a Schematic of simulated device structure. b Simulated current vs channel number. The S/D doping of 1.3 × 1019 cm−3 (magenta bars), 2 × 1020 cm−3 (olive bars), and 2 × 1020 cm−3 with warp around contacts (orange bars) are used. c Schematic of wrap around contact structure at S/D region. d Total parasitic capacitance (Cpar) consisting of shared Cpar (orange) and Cpar proportional to floor# (purple) with the floor# of 2/4/8/16. e Total gate capacitance (Cgg, olive line), Cpar (orange line), intrinsic gate capacitance (Cox, blue line) per floor and f intrinsic gate delay (olive)/gate delay (red) improvement vs floor# using the average WCH = 16 nm and HCH = 13 nm. The current difference between top channel and bottom channel is only 3.5% for the S/D doping of 2 × 1020 cm−3 with wrap around contacts. The effective dielectric constant (κeff = 15) the average of 5 nm Si3N4 inner spacer (κ = 7.2), 1 nm Al2O3 (κ = 9), and 9 nm ZrO2 (κ = 46).

The total gate capacitance (Cgg) is the sum of intrinsic gate capacitance (Cox) and parasitic capacitance (Cpar), i.e., Cgg = Cox+Cpar. In our simulation structure, the effective dielectric constant (κeff) = 15 is used in the inner spacer considering 5 nm Si3N4 (κ = 7.2), 1 nm Al2O3 (κ = 9), and 9 nm ZrO2 (κ = 46) (Fig. 5a). Note that 1 nm Al2O3 and 9 nm ZrO2 used in the inner spacer are due to the conformal deposition of ALD oxide. The overlap area between the gate metal and S/D metal is the main contribution to Cpar. For the overlap area between the gate and S/D, the gate metal width and S/D width are 90 nm (Fig. 5c), while the gate metal height is the sum of channel height (proportional to floor number) and additional 2 vertical pitches above the channel height (Fig. 5d). The gate metal height is 40 nm lower than the S/D metal (Fig. 5a), which can reduce the gate to S/D overlap area, similar to our previous work36. The gate to S/D overlap area above the top channel (2 vertical pitches) is shared by total floors. Therefore, the Cpar per floor decreases as the floor number increases (Fig. 5e), and total Cpar still increases with increasing floor#. Besides, the intrinsic gate capacitance (Cox) per floor remains similar as floor# increases from 2 to 16, and is smaller than Cpar per floor. Thus, Cgg per floor decreases as the floor# increases, similar to the trend of Cpar per floor (Fig. 5e).

Due to the small 3.5% current decrease (Fig. 5b) and the large decrease (40%) of Cgg per floor (Fig. 5e), the intrinsic gate delay (Eq. (1))37 of the floor#=16 is 0.54X of the floor#=2 (Fig. 5f). Moreover, considering the interconnect capacitance (Cinterconnect=Cpar), the gate delay (Eq. (2))38 of the floor#=16 is improved to be 0.23X as compared to floor#=2.

Conclusions

The isotropic wet etching with sufficient selectivity and sophisticated 34 epilayers were used to fabricate the stacked 16 Ge0.95Si0.05 nanowire FETs. The highly stacked nanowire FETs are used to enhance drive current and transistor density due to its small footprint. The wrap around contacts are useful to reduce the current difference between the channels. With the proper design of transistor height, the gate delay can be also improved.

Methods

Device structure and epilayer design

The stacked 16 channels without S/D regrowth is demonstrated. The doping of S/D is obtained by the heavily P-doped Ge sacrificial layers, which are annealed during the device fabrication to have P diffusion. The epilayers were grown in a rapid thermal chemical vapor deposition system with a cold-wall quartz chamber using modified ASM Epsilon 2000 PLUS. The precursor of Ge0.95Si0.05 channels and P-doped Ge SLs are SiH4, GeH4, and PH3.

Material analysis of epilayers

The as-grown epilayers with stacked 16 Ge0.95Si0.05 channels were analyzed by the high-resolution X-ray diffraction with ω − 2θ scan of (004) reflections. The reciprocal space mapping was used to further analyze the strain of epitaxial layers. The doping profile of the as-grown epilayers of stacked 16 Ge0.95Si0.05 channels was analyzed by secondary ion mass spectrometry.

Device fabrication

After epitaxy, the hard mask was deposited to protect epilayers by the plasma enhanced chemical vapor deposition using Oxford 100 PECVD cassette system. The gate lengths of stacked 16 Ge0.95Si0.05 nanowire FETs and stacked 12 Ge0.95Si0.05 nanowire FETs without parasitic channels are 90 nm and 70 nm defined by the E-beam lithography using VISTEC SB3050-2. After E-beam lithography, the SiO2 hard mask and fin formation are formed by the CHF3-based and Cl2-based RIE using LAM 2300 Etcehr Exelan Flex, respectively. The channel release was performed by H2O2 wet etching and parasitic channels (Ge buffer + SOI) were removed by NH4OH + H2O2 wet etching. Note that NH4OH wet etching at 75 °C16 was used to completely remove the SOI underneath the Ge buffer while H2O2 wet etching was used to etch the Ge buffer and Ge SLs between the channel regions. After channel release, the stacked channels were checked by the SEM using FEI Nova 600 Nanolab Dual-Beam FIB. The gate stack of devices used in this work consisted of layers of Al2O3, ZrO2, and TiN by the plasma enhanced atomic layer deposition using Cambridge NanoTech Fiji ALD system. Note that the precursor of Al2O3, ZrO2, and TiN are trimethylaluminum (TMA), Tetrakis(dimethylamino)zirconium (TDMAZr), and Tetrakis(dimethylamino)titanium (TDMAT). The RIE using Samco RIE-10NR. The S/D contact was patterned and etched in HF solution, and was sputtered Pt.

Electrical characterization

ID-VGS and ID-VDS were performed on the stacked 16 Ge0.95Si0.05 nanowire FETs and stacked 12 Ge0.95Si0.05 nanowire FETs without parasitic channel with a Keithley 4200-SCS Semiconductor Analyzer.

TCAD simulation

Current, capacitance, and delay were simulated considering Masetti mobility model39. Capacitance is extracted by the small-signal AC simulation. Cpar is extracted at off-state. Cgg is extracted at Vov = VDS = 0.5 V. Note that Cox=Cgg - Cpar36,40.

Data availability

The data that support the plots within this paper and other findings of this study are available from the corresponding author upon request.

References

Bangsaruntip, S. et al. High performance and highly uniform gate-all-around silicon nanowire MOSFETs with wire size dependent scaling. In Proc. IEEE International Electron Devices Meeting (IEDM) pp. 297 (IEEE, 2009).

Lauer, I. et al. Si nanowire CMOS fabricated with minimal deviation from RMG FinFET technology showing record performance. In Symposium on VLSI Technology Digest of Technical Papers pp. 140 (IEEE, 2015).

Loubet, N. et al. Stacked nanosheet gate-all-around transistor to enable scaling beyond FinFET. In Symposium on VLSI Technology Digest of Technical Papers pp. 230 (IEEE, 2017).

Barraud, S. et al. 7-levels-stacked nanosheet GAA transistors for high performance computing. In Symposium on VLSI Technology Digest of Technical Papers pp. TC1-2 (IEEE, 2020).

Liu, M. Unleashing the future of innovation. In International Solid-State Circuits Conference (ISSCC), Plenary Session 1.1 (IEEE, 2021).

Mii, Y.-J. Semiconductor innovations from device to system. In Symposium on VLSI Technology Digest of Technical Papers P2-2 (IEEE, 2022).

van Dal, M. J. H. et al. Ge CMOS gate stack and contact development for vertically stacked lateral nanowire FETs. In Proc. IEEE International Electron Devices Meeting (IEDM) pp. 492–495 (IEEE, 2018).

Tsai, C.-E. et al. Highly stacked 8 Ge0.9Sn0.1 nanosheet pFETs with ultrathin bodies (~3 nm) and thick bodies (~30 nm) featuring the respective record ION/IOFF of 1.4 × 107 and record ION of 92 μA at VOV = VDS = -0.5 V by CVD epitaxy and dry etching. In Proc. IEEE International Electron Devices Meeting (IEDM) pp. 569–572 (IEEE, 2021).

Huang, B.-W. et al. Highly stacked GeSn nanosheets by CVD epitaxy and highly selective isotropic dry etching. IEEE Trans. Electron Devices 69, 2130–2136 (2022).

Tsai, C.-E. et al. Nearly ideal subthreshold swing and delay reduction of stacked nanosheets using ultrathin bodies. In Symposium on VLSI Technology Digest of Technical Papers pp. 401–402 (IEEE, 2022).

Tu, C.-T. et al. First vertically stacked tensily strained Ge0.98Si0.02 nGAAFETs with no parasitic channel and LG = 40 nm featuring record ION = 48 µA at VOV = VDS = 0.5 V and record Gm,max(µS/µm)/SSSAT(mV/dec) = 8.3 at VDS = 0.5 V. In Proc. IEEE International Electron Devices Meeting (IEDM) pp. 681–684 (IEEE, 2019).

Chen, Y.-R. et al. ION enhancement of Ge0.98Si0.02 nanowire nFETs by high-κ dielectrics. IEEE Electron Device Lett. 43, 1601–1604 (2022).

Liu, Y.-C. et al. First highly stacked Ge0.95Si0.05 nGAAFETs with record ION = 110 μA (4100 μA/μm) at VOV = VDS = 0.5 V and high Gm,max = 340 μS (13000 μS/μm) at VDS = 0.5 V by wet etching. In Symposium on VLSI Technology Digest of Technical Papers pp. T15-2 1-2 (IEEE, 2021).

Liu, Y.-C. et al. Highly stacked GeSi nanosheets and nanowires by low-temperature epitaxy and wet etching. IEEE Trans. Electron Devices 68, 6599–6604 (2021).

Hsieh, W.-H. et al. Diffusion and segregation in highly stacked Ge0.9Sn0.1/Ge:B and Ge0.95Si0.05/Ge:P epilayers. 241st ECS Meeting Abstracts MA2022-01 1284 (2022).

Wang, F. et al. Highly selective chemical etching of Si vs. Si1-xGex using NH4OH solution. J. Electrochem. Soc. 144, L37 (1997).

Sun, S. et al. Surface termination and roughness of Ge(100) cleaned by HF and HCl solutions. Appl. Phys. Lett. 88, 021903 (2006).

Lee, T.-E. et al. Improvement of SiGe MOS interface properties with a wide range of Ge contents by using TiN/Y2O3 gate stacks with TMA passivation. In Symposium on VLSI Technology Digest of Technical Papers pp. T9-5 100–101 (IEEE, 2019).

Thomas, S. Germanium nanowire transistors stack up. Nat. Electron. 4, 452 (2021).

Huang, Y.-S. et al. First demonstration of uniform 4-stacked Ge0.9Sn0.1 nanosheets with record ION =73µA at VOV=VDS= −0.5V and low noise using double Ge0.95Sn0.05 caps, dry etch, low channel doping, and high S/D doping. In Proc. IEEE International Electron Devices Meeting (IEDM) pp. 2.4.1–2.4.4 (IEEE, 2020).

Tu, C.-T. et al. Uniform 4-Stacked Ge0.9Sn0.1 nanosheets using double Ge0.95Sn0.05 caps by highly selective isotropic dry etch. IEEE Trans. Electron Devices 68, 2071–2076 (2021).

Lee, Y.-J. et al. Diamond-shaped Ge and Ge0.9Si0.1 gate-all-around nanowire FETs with four {111} facets by dry etch technology. In Proc. IEEE International Electron Devices Meeting (IEDM) pp. 382–385 (IEEE, 2015).

Wu, H. et al. First demonstration of Ge nanowire CMOS circuits: lowest SS of 64 mV/dec, highest gmax of 1057 μS/μm in Ge nFETs and highest maximum voltage gain of 54 V/V in Ge CMOS inverters. In Proc. IEEE International Electron Devices Meeting (IEDM) pp. 2.1.1–2.1.4 (IEEE, 2015).

Chu, C.-L. et al. Stacked Ge-nanosheet GAAFETs fabricated by Ge/Si multilayer epitaxy. IEEE Electron Device Lett. 39, 1133–1136 (2018).

Ritzenthaler, R. et al. Vertically stacked gate-all-around Si nanowire CMOS transistors with reduced vertical nanowires separation, new work function metal gate solutions, and DC/AC performance optimization. In Proc. IEEE International Electron Devices Meeting (IEDM) pp. 508–511 (IEEE, 2018).

Barraud, S. et al. Tunability of parasitic channel in gate-all-round stacked nanosheets. In Proc. IEEE International Electron Devices Meeting (IEDM) pp. 500–503 (IEEE, 2018).

Mertens, H. et al. Vertically stacked gate-all-around Si nanowire transistors: key process optimizations and ring oscillator demonstration. In Proc. IEEE International Electron Devices Meeting (IEDM) pp. 828–831 (IEEE, 2017).

Huang, C.-Y. et al. 3-D Self-aligned stacked NMOS-on-PMOS nanoribbon transistors for continued Moore’s Law scaling. In Proc. IEEE International Electron Devices Meeting (IEDM) pp. 425–428 (IEEE, 2020).

Arimura, H. et al. A record GmSAT/SSSAT and PBTI reliability in Si-passivated Ge nFinFETs by improved gate stack surface preparation. In Symposium on VLSI Technology Digest of Technical Papers pp. T9-1 92–93 (IEEE, 2019).

Mitard, J. et al. First demonstration of 15nm-WFIN inversion-mode relaxed-germanium n-FinFETs with Si-cap free RMG and NiSiGe source/drain. In Proc. IEEE International Electron Devices Meeting (IEDM) pp. 418–421 (IEEE, 2014).

van Dal, M. J. H. et al. Ge n-channel FinFET with optimized gate stack and contacts. In Proc. IEEE International Electron Devices Meeting (IEDM) pp. 235–238 (IEEE, 2014).

Wu, S.-Y. et al. Demonstration of a sub-0.03 µm2 High Density 6-T SRAM with scaled bulk FinFETs for mobile SOC applications beyond 10nm node. In Symposium on VLSI Technology Digest of Technical Papers pp. T9.1 92–93 (IEEE, 2016).

Rachmady, W. et al. 300mm heterogeneous 3D integration of record performance layer transfer germanium PMOS with silicon NMOS for low power high performance logic applications. In Proc. IEEE International Electron Devices Meeting (IEDM) pp. 697–700 (IEEE, 2019)

Mertens, H. et al. Forksheet FETs for advanced CMOS scaling: forksheet-nanosheet co-integration and dual work function metal gates at 17nm N-P Space. In Symposium on VLSI Technology Digest of Technical Papers pp. T2-1 1–2 (IEEE, 2021).

TCAD Sentaurus Suite, version T-2022.03, Synopsys Inc., Mountain View, CA (2022).

Lin, H.-C. et al. RF performance of stacked Si nanosheet nFETs. IEEE Trans. Electron Devices 68, 5277–5283 (2021).

Yoon, J. et al. Bottom oxide bulk FinFETs without punch-through-stopper for extending toward 5-nm node. IEEE Access 7, 75762–75767 (2019).

Huynh-Bao, T. et al. Statistical timing analysis considering device and interconnect variability for BEOL requirements in the 5-nm node and beyond. IEEE Transaction on Very Large Scale Integration (VLSI) Systems 25 (2017).

Masetti, G. et al. Modeling of carrier mobility against carrier concentration in arsenic-, phosphorus-, and boron-doped silicon. IEEE Trans. Electron Devices 30, 764–769 (1983).

Lin, H.-C. et al. RF performance of stacked Si nanosheets/nanowires. IEEE Electron Device Lett. 43, 1017–1020 (2022).

Acknowledgements

This work was supported in part by the National Science and Technology Council, Taiwan, under Grant NSTC 112-2218-E-002-024-MBK, NSTC 111-2634-F-A49-008-, NSTC 112-2622-8-A49-013 -SB, NSTC 112-2221-E-002-247-MY3, and in part by the Ministry of Education, Taiwan, under Grant NTU-CC-112L890901. The tool support by the Taiwan Semiconductor Research Institute, Taiwan, is also acknowledged.

Author information

Authors and Affiliations

Contributions

Y.-R.C., Y.-C.L., and C.W.L. conceived the study and designed the experiments. Y.-C.L., Y.-R.C., C.-T.T., B.-W.H., and S.-J.C. fabricated the transistors and analysed the data. H.-C.L. and T.C. conducted and discussed the simulations. W.-H.H. analysed the secondary ion mass spectrometry data. Y.-R.C., Y.-C.L., H.-C.L., and C.W.L. wrote the manuscript. All authors contributed to discussing the data and revising the manuscript. All authors have given approval to the final version of the manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Communications Engineering thanks qingzhu zhang and the other, anonymous, reviewers for their contribution to the peer review of this work. Primary Handling Editors: Liwen Sang and Mengying Su, Rosamund Daw.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Chen, YR., Liu, YC., Lin, HC. et al. Fabrication and performance of highly stacked GeSi nanowire field effect transistors. Commun Eng 2, 77 (2023). https://doi.org/10.1038/s44172-023-00126-8

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s44172-023-00126-8