Abstract

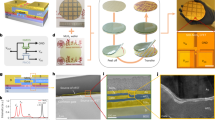

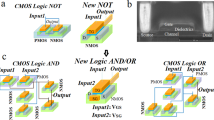

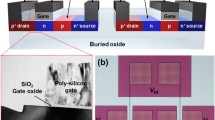

As transistors are scaled to smaller dimensions, their static power increases. Combining two-dimensional (2D) channel materials with complementary metal–oxide–semiconductor (CMOS) logic architectures could be an effective solution to this issue because of the excellent field-effect properties of 2D materials. However, 2D materials have limited polarity control. Here we report a pseudo-CMOS architecture for sub-picowatt logic computing that uses self-biased molybdenum disulfide transistors. The transistors have a gapped channel that forms a tunable barrier—thus circumventing the polarity control of 2D materials—and exhibit a reverse-saturation current below 1 pA with high reliability and endurance. We use the devices to make homojunction-loaded inverters with good rail-to-rail operation at a switching threshold voltage of around 0.5 V, a static power of a few picowatts, a dynamic delay time of around 200 µs, a noise margin of more than 90% and a peak voltage gain of 241. We also fabricate fundamental gate circuits on the basis of this pseudo-CMOS configuration by cascading several devices.

This is a preview of subscription content, access via your institution

Access options

Access Nature and 54 other Nature Portfolio journals

Get Nature+, our best-value online-access subscription

$29.99 / 30 days

cancel any time

Subscribe to this journal

Receive 12 digital issues and online access to articles

$119.00 per year

only $9.92 per issue

Buy this article

- Purchase on Springer Link

- Instant access to full article PDF

Prices may be subject to local taxes which are calculated during checkout

Similar content being viewed by others

Data availability

Source data are provided with this paper. All other data that support the findings of this study are available from the corresponding author on reasonable request.

References

Rupp, K. et al. 42 years of microprocessor trend data. Karl Rupp www.karlrupp.net/2018/02/42-years-of-microprocessor-trend-data/ (2018).

International Roadmap for Devices and Systems (IRDS) 2022 Edition—More Moore (IEEE, 2022); https://irds.ieee.org/images/files/pdf/2022/2022IRDS_MM.pdf

CMOS, the Ideal Logic Family (Fairchild Semiconductor, 1983).

Henzler, S. Power Management of Digital Circuits in Deep Sub-Micron CMOS Technologies (Springer-Verlag, 2006).

Rawat, A., Gupta, A. K. & Rawat, B. Performance projection of 2D material-based CMOS inverters for sub-10-nm channel length. IEEE Trans. Electron Devices 68, 3622–3629 (2021).

Kim, N. S. et al. Leakage current: Moore’s law meets static power. Computer 36, 68–75 (2003).

Radisavljevic, B. et al. Single-layer MoS2 transistors. Nat. Nanotechnol. 6, 147–150 (2011).

Desai, S. B. et al. MoS2 transistors with 1-nanometer gate lengths. Science 354, 99–102 (2016).

Xiao, J. et al. Record-high saturation current in end-bond contacted monolayer MoS2 transistors. Nano Res. 15, 475–481 (2022).

Wu, F. et al. Vertical MoS2 transistors with sub-1-nm gate lengths. Nature 603, 259–264 (2022).

Liu, Y. et al. Promises and prospects of two-dimensional transistors. Nature 591, 43–53 (2021).

Asenov, A. et al. Simulation of intrinsic parameter fluctuations in decananometer and nanometer-scale MOSFETs. IEEE Trans. Electron Devices 50, 1837–1852 (2003).

Liu, C. et al. Two-dimensional materials for next-generation computing technologies. Nat. Nanotechnol. 15, 545–557 (2020).

Kong, L., Chen, Y. & Liu, Y. Recent progresses of NMOS and CMOS logic functions based on two-dimensional semiconductors. Nano Res. 14, 1768–1783 (2021).

Pal, A. et al. Two-dimensional materials enabled next-generation low-energy compute and connectivity. MRS Bull. 46, 1211–1228 (2021).

Zhu, K. et al. The development of integrated circuits based on two-dimensional materials. Nat. Electron. 4, 775–785 (2021).

Kong, L. et al. Doping-free complementary WSe2 circuit via van der Waals metal integration. Nat. Commun. 11, 1866 (2020).

Pan, C. et al. Reconfigurable logic and neuromorphic circuits based on electrically tunable two-dimensional homojunctions. Nat. Electron. 3, 383–390 (2020).

Resta, G. V. et al. Doping-free complementary logic gates enabled by two-dimensional polarity-controllable transistors. ACS Nano 12, 7039–7047 (2018).

Qi, D. et al. Continuously tuning electronic properties of few-layer molybdenum ditelluride with in situ aluminum modification toward ultrahigh gain complementary inverters. ACS Nano 13, 9464–9472 (2019).

Lim, J. Y. et al. Homogeneous 2D MoTe2 p-n Junctions and CMOS inverters formed by atomic-layer-deposition-induced doping. Adv. Mater. 29, 1701798 (2017).

Pezeshki, A. et al. Static and dynamic performance of complementary inverters based on nanosheet alpha-MoTe2 p-channel and MoS2 n-channel transistors. ACS Nano 10, 1118–1125 (2016).

Zhang, H. et al. Complementary logic with voltage zero-loss and nano-watt power via configurable MoS2/WSe2 gate. Adv. Funct. Mater. 28, 1805171 (2018).

Wachter, S. et al. A microprocessor based on a two-dimensional semiconductor. Nat. Commun. 8, 14948 (2017).

Lin, Z. et al. Solution-processable 2D semiconductors for high-performance large-area electronics. Nature 562, 254–258 (2018).

Chen, X. et al. Wafer-scale functional circuits based on two dimensional semiconductors with fabrication optimized by machine learning. Nat. Commun. 12, 5953 (2021).

Mak, K. F. et al. Tightly bound trions in monolayer MoS2. Nat. Mater. 12, 207–211 (2013).

Zhang, X. et al. Near-ideal van der Waals rectifiers based on all-two-dimensional Schottky junctions. Nat. Commun. 12, 1522 (2021).

Jin, Y. et al. A van der Waals homojunction: ideal p-n diode behavior in MoSe2. Adv. Mater. 27, 5534–5540 (2015).

Huang, M. et al. Multifunctional high-performance van der Waals heterostructures. Nat. Nanotechnol. 12, 1148–1154 (2017).

Li, M. Y. et al. Epitaxial growth of a monolayer WSe2-MoS2 lateral p-n junction with an atomically sharp interface. Science 349, 524–528 (2015).

Zhang, X. et al. Poly(4-styrenesulfonate)-induced sulfur vacancy self-healing strategy for monolayer MoS2 homojunction photodiode. Nat. Commun. 8, 15881 (2017).

Baker, R. J. CMOS: Circuit Design, Layout, and Simulation (Wiley, 2019).

Chuang, M.-H. et al. Integrated low-dimensional semiconductors for scalable low-power CMOS logic. Adv. Funct. Mater. 33, 2212722 (2023).

Jeon, P. J. et al. Low power consumption complementary inverters with n-MoS2 and p-WSe2 dichalcogenide nanosheets on glass for logic and light-emitting diode circuits. ACS Appl Mater. Interfaces 7, 22333–22340 (2015).

Wang, X. et al. Pass-transistor logic circuits based on wafer-scale 2D semiconductors. Adv. Mater. 34, 2202472 (2022).

Ding, L. et al. CMOS-based carbon nanotube pass-transistor logic integrated circuits. Nat. Commun. 3, 677 (2012).

Li, N. et al. Large-scale flexible and transparent electronics based on monolayer molybdenum disulfide field-effect transistors. Nat. Electron. 3, 711–717 (2020).

Gao, L. et al. Defect-engineered atomically thin MoS2 homogeneous electronics for logic inverters. Adv. Mater. 32, 1906646 (2020).

Acknowledgements

This work was supported by the National Key Research and Development Program of China under grant nos. 2022YFA1203800 (Z.Z.), 2022YFA1203803 (Z.Z.), 2018YFA0703503 (Y.Z.), 2023YFF1500400 (Y.Z.) and 2023YFF1500401 (X.Z.); the National Natural Science Foundation of China under grant nos. 51991340 (Y.Z.), 51991342 (Y.Z.), 52225206 (Z.Z.), 92163205 (Z.Z.), 52188101 (Y.Z.), 62322402 (X.Z.), 62204012 (X.Z.), 52250398 (X.Z.), 51972022 (Z.Z.), 52303362 (L.G.) and 62304019 (H.Y.); the Frontier Cross Research Project of the Department of Chinese Academy of Sciences under grant no. XK2023JSA001 (Y.Z.); the Beijing Nova Program under grant nos. 20220484145 (X.Z.) and 20230484478 (X.Z.); the Fundamental Research Funds for the Central Universities under grant no. FRF-06500207 (X.Z.); and the State Key Lab for Advanced Metals and Materials under grant no. 2023-Z05 (Z.Z.). We thank Y. Liu at Hunan University and Y. Yu at Southern University of Science and Technology for constructive discussions.

Author information

Authors and Affiliations

Contributions

X.W., Z.Z. and Y.Z. initiated and supervised the project. X.W., X.Z., Z.K. and Z.Z. designed the experiments. X.W. and X.Z. performed device fabrication, data collection and analysis. L.G. and Z.C. assisted in the preparation and characterization of monolayer MoS2 by CVD. H.Y. and M.H. assisted in performing in situ characterization experiments. W.T., L.G. and H.Y. assisted in the device performance measurement and data analysis. X.W., X.Z., Z.K. and Z.Z. cowrote the paper. All authors discussed the results and commented on the paper.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Nature Electronics thanks Michael Waltl, Xiangbin Zeng and the other, anonymous, reviewer(s) for their contribution to the peer review of this work.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Supplementary Information

Supplementary Figs. 1–17, Table 1 and references.

Source data

Source Data Fig. 1

Source data for Fig. 1e.

Source Data Fig. 2

Source data for Fig. 2c–e.

Source Data Fig. 3

Source data for Fig. 3c–h.

Source Data Fig. 4

Source data for Fig. 4c–h.

Source Data Fig. 5

Source data for Fig. 5b–g.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Wei, X., Zhang, X., Yu, H. et al. Homojunction-loaded inverters based on self-biased molybdenum disulfide transistors for sub-picowatt computing. Nat Electron 7, 138–146 (2024). https://doi.org/10.1038/s41928-023-01112-w

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1038/s41928-023-01112-w