Abstract

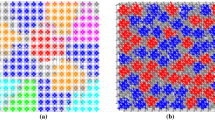

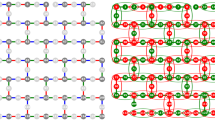

Massively parallel annealing processors are of potential use in a wide range of sampling and optimization problems. A key component dictating the size of these processors is the neuron update circuit, which is ideally implemented using stochastic nanodevices. Here we show that photon statistics observed in single-photon avalanche diodes (SPADs) and temporal filtering can generate stochastic states. The approach can be used to continuously control the computational temperature and to implement the Potts model, an n-state generalization of the two-state Ising model. The use of SPADs also offers a practical advantage since they are readily manufacturable in standard complementary metal–oxide–semiconductor (CMOS) processes. To illustrate the effectiveness of SPAD-based annealing, we design Ising and Potts models driven by an array of discrete SPADs. The hardware replicates ideal distributions and can solve graph-colouring and travelling salesman problems, with the Potts model finding solutions ten times faster than the Ising solver. Compared with other physics-based approaches, such as D-Wave and coherent Ising machines, our approach finds almost all solutions on hard graph instances.

This is a preview of subscription content, access via your institution

Access options

Access Nature and 54 other Nature Portfolio journals

Get Nature+, our best-value online-access subscription

$29.99 / 30 days

cancel any time

Subscribe to this journal

Receive 12 digital issues and online access to articles

$119.00 per year

only $9.92 per issue

Buy this article

- Purchase on Springer Link

- Instant access to full article PDF

Prices may be subject to local taxes which are calculated during checkout

Similar content being viewed by others

Data availability

Data recorded by the 16- and 144-circuit experimental hardware, including the VRSC rate measurements, hyperbolic-tangent and network statistics, and graph-colouring problem and TSP results, are publicly available via GitHub at https://github.com/ucsb-biomimetic/ising-potts-with-SPADs-discrete. Additional plots of the physical circuit measurements are provided in the Supplementary Information. Source data are provided with this paper.

Code availability

Code and other design files, including the design files for both 16- and 144-circuit SPAD annealer implementations, are publicly available via GitHub at https://github.com/ucsb-biomimetic/ising-potts-with-SPADs-discrete. For each implementation, there are KiCad files for the PCBs housing the analogue circuitry, Vivado project or standalone files used to create the FPGA configurations and Python scripts for orchestrating the test routines. Data collection methods may be fully understood by looking at the Python (v3.10) scripts, which record and save the data. All panels in Fig. 6 were generated by the code available in the GitHub repository.

References

Kirkpatrick, S., Gelatt, C. D. & Vecchi, M. P. Optimization by simulated annealing. Science 220, 671–680 (1983).

Rutenbar, R. Simulated annealing algorithms: an overview. IEEE Circuits Devices Mag. 5, 19–26 (1989).

Koulamas, C., Antony, S. & Jaen, R. A survey of simulated annealing applications to operations research problems. Omega 22, 41–56 (1994).

Lucas, A. Ising formulations of many NP problems. Front. Phys. 2, 5 (2014).

Mohseni, N., McMahon, P. L. & Byrnes, T. Ising machines as hardware solvers of combinatorial optimization problems. Nat. Rev. Phys. 4, 363–379 (2022).

Brush, S. G. History of the Lenz-Ising model. Rev. Mod. Phys. 39, 883–893 (1967).

Wu, F. Y. The Potts model. Rev. Mod. Phys. 54, 235–268 (1982).

Camsari, K. Y., Salahuddin, S. & Datta, S. Implementing p-bits with embedded MTJ. IEEE Electron Device Lett. 38, 1767–1770 (2017).

Takemoto, T., Hayashi, M., Yoshimura, C. & Yamaoka, M. A 2 × 30k-spin multi-chip scalable CMOS annealing processor based on a processing-in-memory approach for solving large-scale combinatorial optimization problems. IEEE J. Solid-State Circuits 55, 145–156 (2020).

Su, Y., Kim, H. & Kim, B. CIM-spin: a scalable CMOS annealing processor with digital in-memory spin operators and register spins for combinatorial optimization problems. IEEE J. Solid-State Circuits 57, 2263–2273 (2022).

Aadit, N. A. et al. Massively parallel probabilistic computing with sparse Ising machines. Nat. Electron. 5, 460–468 (2022).

Ueyoshi, K., Marukame, T., Asai, T., Motomura, M. & Schmid, A. FPGA implementation of a scalable and highly parallel architecture for restricted Boltzmann machines. Circuits Syst. 07, 2132–2141 (2016).

Skubiszewski, M. An exact hardware implementation of the Boltzmann machine. In Proc. Fourth IEEE Symposium on Parallel and Distributed Processing 107–110 (IEEE, 1992).

Inaba, K. et al. Potts model solver based on hybrid physical and digital architecture. Commun. Phys. 5, 137 (2022).

Pierangeli, D., Marcucci, G. & Conti, C. Large-scale photonic Ising machine by spatial light modulation. Phys. Rev. Lett. 122, 213902 (2019).

Yan, X. et al. Reconfigurable stochastic neurons based on tin oxide/MoS2 hetero-memristors for simulated annealing and the Boltzmann machine. Nat. Commun. 12, 5710 (2021).

Cai, F. et al. Power-efficient combinatorial optimization using intrinsic noise in memristor Hopfield neural networks. Nat. Electron. 3, 409–418 (2020).

Kiraly, B., Knol, E. J., van Weerdenburg, W. M. J., Kappen, H. J. & Khajetoorians, A. A. An atomic Boltzmann machine capable of self-adaption. Nat. Nanotechnol. 16, 414–420 (2021).

Afoakwa, R., Zhang, Y., Vengalam, U. K. R., Ignjatovic, Z. & Huang, M. BRIM: bistable resistively-coupled Ising machine. In 2021 IEEE International Symposium on High-Performance Computer Architecture (HPCA) 749–760 (IEEE, 2021).

Chou, J., Bramhavar, S., Ghosh, S. & Herzog, W. Analog coupled oscillator based weighted Ising machine. Sci. Rep. 9, 14786 (2019).

Peterson, C. & Söderberg, B. A new method for mapping optimization problems onto neural networks. Int. J. Neural Syst. 01, 3–22 (1989).

Söderberg, B. Optimization with neural networks. In Scientific Applications of Neural Nets (eds Clark, J. W., Lindenau, T. & Ristig, M. L.) 243–256 (Springer, 1999).

Okada, S., Ohzeki, M. & Taguchi, S. Efficient partition of integer optimization problems with one-hot encoding. Sci. Rep. 9, 13036 (2019).

Kanter, I. & Sompolinsky, H. Graph optimisation problems and the Potts glass. J. Phys. A: Math. Gen. 20, L673–L679 (1987).

Okada, S., Ohzeki, M. & Tanaka, K. Efficient quantum and simulated annealing of Potts models using a half-hot constraint. J. Phys. Soc. Jpn 89, 094801 (2020).

Kalinin, K. P. & Berloff, N. G. Simulating ising and n-state planar Potts models and external fields with nonequilibrium condensates. Phys. Rev. Lett. 121, 235302 (2018).

Hollis, P. & Paulos, J. Artificial neural networks using MOS analog multipliers. IEEE J. Solid-State Circuits 25, 849–855 (1990).

Gu, X., Wan, Z. & Iyer, S. S. Charge-trap transistors for CMOS-only analog memory. IEEE Trans. Electron Devices 66, 4183–4187 (2019).

Lazzaro, J., Ryckebusch, S., Mahowald, M. & Mead, C. A. Winner-take-all networks of O(N) complexity. In Advances in Neural Information Processing Systems (ed Touretzky, D.) Vol. 1 (Morgan-Kaufmann, 1988).

Stanco, A. et al. Efficient random number generation techniques for CMOS single-photon avalanche diode array exploiting fast time tagging units. Phys. Rev. Res. 2, 023287 (2020).

Tontini, A., Gasparini, L., Massari, N. & Passerone, R. SPAD-based quantum random number generator with an nth-order rank algorithm on FPGA. IEEE Trans. Circuits Syst., II, Exp. Briefs 66, 2067–2071 (2019).

You, Z., Parmesan, L., Pellegrini, S. & Henderson, R. K. 3µm pitch, 1µm active diameter SPAD arrays in 130nm CMOS imaging technology. In International Image Sensor Workshop 238–241 (IRIS, 2017).

Bruschini, C., Homulle, H., Antolovic, I. M., Burri, S. & Charbon, E. Single-photon avalanche diode imagers in biophotonics: review and outlook. Light Sci. Appl. 8, 87 (2019).

Ceccarelli, F. et al. Recent advances and future perspectives of single-photon avalanche diodes for quantum photonics applications. Adv. Quantum Technol. 4, 2000102 (2021).

Stipčević, M., Wang, D. & Ursin, R. Characterization of a commercially available large area, high detection efficiency single-photon avalanche diode. J. Lightwave Technol. 31, 3591–3596 (2013).

Lu, X. et al. A 4-µm diameter SPAD using less-doped n-well guard ring in baseline 65-nm CMOS. IEEE Trans. Electron Devices 67, 2223–2225 (2020).

de Albuquerque, T. C. et al. Integration of SPAD in 28nm FDSOI CMOS technology. In 2018 48th European Solid-State Device Research Conference (ESSDERC) 82–85 (IEEE, 2018).

López-Martínez, J. M., Vornicu, I., Carmona-Galán, R. & Rodríguez-Vázquez, Á. An experimentally-validated VERILOG-A SPAD model extracted from TCAD simulation. In 2018 25th IEEE International Conference on Electronics, Circuits and Systems (ICECS) 137–140 (IEEE, 2018).

Severini, F. et al. SPAD pixel with sub-ns dead-time for high-count rate applications. IEEE J. Sel. Topics Quantum Electron. 28, 3802808 (2022).

Kwok, J. & Pudenz, K. Graph coloring with quantum annealing. Preprint at https://arxiv.org/abs/2012.04470 (2020).

Tabi, Z. et al. Quantum optimization for the graph coloring problem with space-efficient embedding. In 2020 IEEE International Conference on Quantum Computing and Engineering (QCE) 56–62 (IEEE, 2020).

Morimoto, K. & Charbon, E. A scaling law for SPAD pixel miniaturization. Sensors 21, 3447 (2021).

Rieffel, E. G., Venturelli, D., Do, M., Hen, I. & Frank, J. Parametrized families of hard planning problems from phase transitions. In Proc. Twenty-Eighth AAAI Conference on Artificial Intelligence 2337–2343 (AAAI, 2014).

Acknowledgements

We acknowledge support from the NSF grant 1934288 (W.W. and Z.N.) and the National Institutes of Health grant 1R21EY034291-01 (W.W.). K.Y.C. and L.T. acknowledge the seed grant support from the Institute of Energy Efficiency at University of California, Santa Barbara.

Author information

Authors and Affiliations

Contributions

W.W. and L.T. conceived the idea and planned and designed the experiments. W.W. designed, fabricated and tested the VRSPAD-144 system and was responsible for all the data collection. Z.N. designed the initial 16-VRSPAD system. K.Y.C. provided guidance on the theory of Boltzmann machines and optimization problems. L.T. supervised the overall project. All authors have participated in useful discussions and in writing the manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Nature Electronics thanks David Stoker and the other, anonymous, reviewer(s) for their contribution to the peer review of this work.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Supplementary Information

Supplementary Figs. 1–11, Notes 1–13 and Tables 1 and 2.

Source data

Source Data Figs. 4–6

Voltage and current traces and statistical source data, statistical mean and frequency measurements and statistical source data.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Whitehead, W., Nelson, Z., Camsari, K.Y. et al. CMOS-compatible Ising and Potts annealing using single-photon avalanche diodes. Nat Electron 6, 1009–1019 (2023). https://doi.org/10.1038/s41928-023-01065-0

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1038/s41928-023-01065-0

This article is cited by

-

CMOS plus stochastic nanomagnets enabling heterogeneous computers for probabilistic inference and learning

Nature Communications (2024)