Abstract

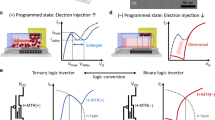

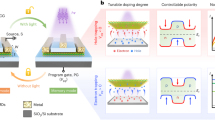

Logic-in-memory architectures could be used to develop efficient computing devices with low power consumption. However, the approach is limited by device performance issues, including reliability and versatility. Here we report a two-dimensional van der Waals heterostructure device that can function as both reconfigurable transistor and reconfigurable non-volatile memory, as well as provide reconfigurable logic-in-memory capabilities. The architecture of the device—termed a partial floating-gate field-effect transistor—offers both charge-trapping and field-regulating units. When operating as a transistor, the device can be switched between the p- and n-type mode, and exhibits a subthreshold swing of 64 mV dec–1 and on/off current ratio approaching 108. When operating as a memory, the device can be switched between the p- and n-type memory, and exhibits an erase/program ratio approaching 108. We use the devices to fabricate complementary metal–oxide–semiconductor circuits, and linear and nonlinear logic gates with in situ storage, as well as device-efficient half-adder circuits.

This is a preview of subscription content, access via your institution

Access options

Access Nature and 54 other Nature Portfolio journals

Get Nature+, our best-value online-access subscription

$29.99 / 30 days

cancel any time

Subscribe to this journal

Receive 12 digital issues and online access to articles

$119.00 per year

only $9.92 per issue

Buy this article

- Purchase on Springer Link

- Instant access to full article PDF

Prices may be subject to local taxes which are calculated during checkout

Similar content being viewed by others

Data availability

The data that support the findings of this study are available from the corresponding authors on reasonable request. Source data are provided with this paper.

References

Mutlu, O., Ghose, S., Gómez-Luna, J. & Ausavarungnirun, R. Processing data where it makes sense: enabling in-memory computation. Microprocess. Microsyst. 67, 28–41 (2019).

Waldrop, M. M. The chips are down for Moore’s law. Nature 530, 144–147 (2016).

Zhang, W. et al. Neuro-inspired computing chips. Nat. Electron. 3, 371–382 (2020).

Zhang, Z. et al. All-in-one two-dimensional retinomorphic hardware device for motion detection and recognition. Nat. Nanotechnol. 17, 27–32 (2022).

Horowitz, M. 1.1 Computing’s energy problem (and what we can do about it). In 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC) 10–14 (IEEE, 2014).

Tong, L. et al. 2D materials–based homogeneous transistor-memory architecture for neuromorphic hardware. Science 373, 1353–1358 (2021).

Chen, H. et al. Logic gates based on neuristors made from two-dimensional materials. Nat. Electron. 4, 399–404 (2021).

Sebastian, A., Le Gallo, M., Khaddam-Aljameh, R. & Eleftheriou, E. Memory devices and applications for in-memory computing. Nat. Nanotechnol. 15, 529–544 (2020).

Shulaker, M. M. et al. Three-dimensional integration of nanotechnologies for computing and data storage on a single chip. Nature 547, 74–78 (2017).

Khoram, S., Zha, Y., Zhang, J. & Li, J. Challenges and opportunities: from near-memory computing to in-memory computing. In Proc. 2017 ACM on International Symposium on Physical Design 43–46 (ACM, 2017).

Pawlowski, J. T. Hybrid memory cube (HMC). In 2011 IEEE Hot Chips 23 Symposium (HCS) 1–24 (IEEE, 2011).

Joonyoung, K. & Younsu, K. HBM: memory solution for bandwidth-hungry processors. In 2014 IEEE Hot Chips 26 Symposium (HCS) 1–24 (IEEE, 2014).

Irisawa, T., Numata, T., Tezuka, T., Sugiyama, N. & Takagi, S. Electron transport properties of ultrathin-body and tri-gate SOI nMOSFETs with biaxial and uniaxial strain. In 2006 International Electron Devices Meeting 1–4 (IEEE, 2006).

Uchida, K. et al. Experimental study on carrier transport mechanism in ultrathin-body SOI nand p-MOSFETs with SOI thickness less than 5 nm. In International Electron Devices Meeting 47–50 (IEEE, 2002).

Liu, Y. et al. Promises and prospects of two-dimensional transistors. Nature 591, 43–53 (2021).

Li, Q. et al. Low voltage and robust InSe memristor using van der Waals electrodes integration. Int. J. Extreme Manuf. 3, 045103 (2021).

Liu, Y., Huang, Y. & Duan, X. Van der Waals integration before and beyond two-dimensional materials. Nature 567, 323–333 (2019).

Liu, C. et al. Small footprint transistor architecture for photoswitching logic and in situ memory. Nat. Nanotechnol. 14, 662–667 (2019).

Sun, Y., Wang, S., Zeng, S., Huang, X. & Zhou, P. Versatile logic and nonvolatile memory based on a van der Waals heterojunction. ACS Appl. Electron. Mater. 3, 3079–3084 (2021).

Chen, P. et al. Approaching the intrinsic exciton physics limit in two-dimensional semiconductor diodes. Nature 599, 404–410 (2021).

Wu, P., Reis, D., Hu, X. S. & Appenzeller, J. Two-dimensional transistors with reconfigurable polarities for secure circuits. Nat. Electron. 4, 45–53 (2021).

Pan, C. et al. Reconfigurable logic and neuromorphic circuits based on electrically tunable two-dimensional homojunctions. Nat. Electron. 3, 383–390 (2020).

Lee, S.-J. et al. Programmable devices based on reversible solid-state doping of two-dimensional semiconductors with superionic silver iodide. Nat. Electron. 3, 630–637 (2020).

Liu, C. et al. Two-dimensional materials for next-generation computing technologies. Nat. Nanotechnol. 15, 545–557 (2020).

Hou, X. et al. A logic-memory transistor with the integration of visible information sensing-memory-processing. Adv. Sci. 7, 2002072 (2020).

Migliato Marega, G. et al. Logic-in-memory based on an atomically thin semiconductor. Nature 587, 72–77 (2020).

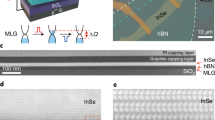

Wu, L. et al. Atomically sharp interface enabled ultrahigh-speed non-volatile memory devices. Nat. Nanotechnol. 16, 882–887 (2021).

Liu, L. et al. Ultrafast non-volatile flash memory based on van der Waals heterostructures. Nat. Nanotechnol. 16, 874–881 (2021).

Li, D. et al. Two-dimensional non-volatile programmable p–n junctions. Nat. Nanotechnol. 12, 901–906 (2017).

Zhu, C. et al. Nonvolatile MoTe2 p–n diodes for optoelectronic logics. ACS Nano 13, 7216–7222 (2019).

Resta, G. V. et al. Doping-free complementary logic gates enabled by two-dimensional polarity-controllable transistors. ACS Nano 12, 7039–7047 (2018).

Yang, Z. et al. A Fermi-level-pinning-free 1D electrical contact at the intrinsic 2D MoS2–metal junction. Adv. Mater. 31, e1808231 (2019).

Xiong, X. et al. Nonvolatile logic and ternary content-addressable memory based on complementary black phosphorus and rhenium disulfide transistors. Adv. Mater. 2021, e2106321 (2021).

Ji, H. G. et al. Chemically tuned p- and n-type WSe2 monolayers with high carrier mobility for advanced electronics. Adv. Mater. 31, e1903613 (2019).

Qi, D. et al. Continuously tuning electronic properties of few-layer molybdenum ditelluride with in situ aluminum modification toward ultrahigh gain complementary inverters. ACS Nano 13, 9464–9472 (2019).

Sun, X. et al. Contact and injection engineering for low SS reconfigurable FETs and high gain complementary inverters. Sci. Bull. 65, 2007–2013 (2020).

Yi, J. et al. Double-gate MoS2 field-effect transistors with full-range tunable threshold voltage for multifunctional logic circuits. Adv. Mater. 33, e2101036 (2021).

Lin, Z. et al. Solution-processable 2D semiconductors for high-performance large-area electronics. Nature 562, 254–258 (2018).

Li, N. et al. Large-scale flexible and transparent electronics based on monolayer molybdenum disulfide field-effect transistors. Nat. Electron. 3, 711–717 (2020).

Chen, X. et al. Wafer-scale functional circuits based on two dimensional semiconductors with fabrication optimized by machine learning. Nat. Commun. 12, 5953 (2021).

Pezeshki, A. et al. Static and dynamic performance of complementary inverters based on nanosheet α-MoTe2 p-channel and MoS2 n-channel transistors. ACS Nano 10, 1118–1125 (2016).

Zhang, H. et al. Complementary logic with voltage zero-loss and nano-watt power via configurable MoS2/WSe2 gate. Adv. Funct. Mater. 28, 1805171 (2018).

Kong, L. et al. Doping-free complementary WSe2 circuit via van der Waals metal integration. Nat. Commun. 11, 1866 (2020).

Acknowledgements

We are grateful to the National Natural Science Foundation of China (nos. 51902098 (D. Li), 52221001, U19A2090 and 62090035 (A.P.), 51972105 (X.Z.), U1930114 (H.D.) and 51991341 (Yuan Liu)) and the Key Program of Science and Technology Department of Hunan Province (nos. 2019XK2001 and 2020XK2001 (A.P.)), the Science and Technology Innovation Program of Hunan Province (nos. 2021RC3061 (D. Li), 2020RC2028 (B.Z.) and 2021RC2042 (H.L.)), the Natural Science Foundation of Hunan Province (nos. 2021JJ20016 (D. Li), 2021JJ30132 (X.Z.)) and the project funded by China Postdoctoral Science Foundation (nos. BX2021094 and 2020M680112 (B.Z.) and 2021M690953 (H.L.)), National Key R&D Program of China (No. 2021YFA1200503 (Yuan Liu)).

Author information

Authors and Affiliations

Contributions

D. Li and A.P. conceived and supervised the experiment. D. Li, X.S., C.Z. and J.Y. designed the devices and circuits. X.S., C.Z., H.L., B.Z. and L.X. performed the device fabrication and property characterization. Yong Liu captured the Raman spectra of the heterojunctions. W.Y. and D. Liang obtained the AFM images and height profiles of the devices. Q.S., W.Z. and C.M. supported the cross-sectional information of the device. X.Z., H.D., L.L., Yuan Liu and D. Li provided assistance with the mechanism analysis and discussion. X.S. and D. Li wrote the manuscript with help from all the authors.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Nature Electronics thanks Dayane Reis, Tania Roy and Hyeon-Jin Shin for their contribution to the peer review of this work.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Extended data

Extended Data Fig. 1 Transport properties of WSe2-based ambipolar FET and memory.

Transport properties of WSe2-based ambipolar FET and memory. Schematic structure of WSe2-based (a) ambipolar FET and (c) ambipolar memory. (b) The corresponding optical image. (d) Transfer curves of WSe2 FET, where graphene is used as the back gate and drain voltage is applied between electrodes E2 and E3. Typical ambipolar conduction behaviour is observed with the minimum current point locating at around 0 V, and the small voltage hysteresis demonstrates little interface charge states. (e) Double sweep transfer characteristic of WSe2-based memory by scanning control gate voltage between -8 and +8 V. (f) Retention performance of channel current after applying voltage pulse of +8 or -8 V on control gate, showing a small erase/program ratio less than 10.

Extended Data Fig. 2 Relationship between pulse width of CG and device performance.

Relationship between pulse width of CG and device performance. (a) Transfer curves of PFGFET in FET mode after different pulse width. (b) Relationship between the pulse width and ION/IOFF. Dynamic switching behaviour between p- and n-type with pulse width of (c) 90 μs and (d) 5 ms.

Extended Data Fig. 3 Switching and retention performance of PFGFET.

Switching and retention performance of PFGFET. (a) Switching and (b) retention performance of reconfigurable memory.

Extended Data Fig. 4 Transport properties of MoTe2-based device (PFGFET #6) with 16.2 nm hBN tunnelling layer.

Transport properties of MoTe2-based device (PFGFET #6) with 16.2 nm hBN tunnelling layer, indicating that ambipolar MoTe2 has similar behaviours with such device architecture. (a) Optical and AFM images of the device. Transfer curves of the PFGFET device acquired at (b) memory mode (VTG = ± 5 V) and (c) field effect transistor mode (VCG-pulse = ±15 V). (d) The reconfigurability of PFGFET at field effect transistor mode. The PFGFET is initially programmed at p-type state with VCG-pulse of -15 V. When an opposite VCG-pulse (+15 V) is introduced, this state will be erased, resulting in n-type state. (e) Switching and (f) retention performance of reconfigurable PFGFET #4. The results indicate that the ambipolar MoTe2 exhibits similar reconfigurable memory and FET capacity, that is, enables the coexistence of memory and logic function in a single unit.

Extended Data Fig. 5 Transport properties of MoS2-based PFGFET (PFGFET #2).

Transport properties of MoS2-based PFGFET (PFGFET #2). Schematic structure of MoS2-based (a) FET and (c) PFGFET. (b) The corresponding optical image of FET and PFGFET. (d) Transfer curve of MoS2 FET, where graphene is used as the back gate and drain voltage is applied between electrodes E1 and E2. Typical n-type depletion conduction behaviour is observed. (f) The n-type transport behaviour with optimized on/off transition is acquired at MoS2-based PFGFET (between E2 and E3 electrons). (e) Subthreshold swing acquired from transfer curves of FET and PFGFET. The SS of PFGFET is extracted to be 66 mV/dec. (g) Double sweep transfer characteristic of MoS2-based memory by scanning control gate voltage between -8 and +8 V. The erase/program ratio for VTG = -2 V and VTG = 2 V are about 1 and 108, indicating the n-type conduction behaviour of MoS2. (h) Switching and (i) retention performance of MoS2-based PFGFET.

Extended Data Fig. 6 Power consumption of the NOR logic gate.

Power consumption of the NOR logic gate. (a) Output waveforms (b) current and (c) power consumption of NOR logic gate with read voltage of 1 V. (d) Output waveforms (e) current and (f) power consumption with read voltage of 100 mV. (g) Output waveforms (h) current and (i) power consumption with read voltage of 10 mV.

Supplementary information

Supplementary Information

Supplementary Sections 1–8, Figs. 1–19, Tables 1–4 and discussion.

Source data

Source Data Fig. 2

Source data for Fig. 2.

Source Data Fig. 3

Source data for Fig. 3.

Source Data Fig. 4

Source data for Fig. 4.

Source Data Fig. 5

Source data for Fig. 5.

Source Data Extended Data Fig. 1

Source data for Extended Data Fig. 1.

Source Data Extended Data Fig. 2

Source data for Extended Data Fig. 2.

Source Data Extended Data Fig. 3

Source data for Extended Data Fig. 3.

Source Data Extended Data Fig. 4

Source data for Extended Data Fig. 4.

Source Data Extended Data Fig. 5

Source data for Extended Data Fig. 5.

Source Data Extended Data Fig. 6

Source data for Extended Data Fig. 6.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Sun, X., Zhu, C., Yi, J. et al. Reconfigurable logic-in-memory architectures based on a two-dimensional van der Waals heterostructure device. Nat Electron 5, 752–760 (2022). https://doi.org/10.1038/s41928-022-00858-z

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1038/s41928-022-00858-z