Abstract

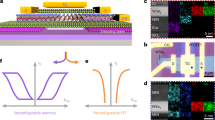

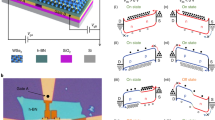

Reconfigurable field-effect transistors (FETs) combine unipolar n- and p-type characteristics in a single programmable device and could be used to reduce the complexity of electronic devices. However, current reconfigurable FETs require a constant voltage supply to achieve polarity conversion, leading to high power consumption. Here we report a reconfigurable FET that is based on a hexagonal boron nitride/rhenium diselenide/hexagonal boron nitride (hBN/ReSe2/hBN) heterostructure and has a nonvolatile and tunable polarity. A photoinduced trapping mechanism is used to drive photoexcited holes or electrons into the interface between the hBN and the silicon dioxide substrate. The reconfigurable FET can switch between a transistor and memory mode, and several FETs can be used to create inverter, AND, OR, NAND, NOR, XOR and XNOR circuits. We also show that, when in memory-mode operation, the devices can be used to emulate synaptic functions for neuromorphic computing systems.

This is a preview of subscription content, access via your institution

Access options

Access Nature and 54 other Nature Portfolio journals

Get Nature+, our best-value online-access subscription

$29.99 / 30 days

cancel any time

Subscribe to this journal

Receive 12 digital issues and online access to articles

$119.00 per year

only $9.92 per issue

Buy this article

- Purchase on Springer Link

- Instant access to full article PDF

Prices may be subject to local taxes which are calculated during checkout

Similar content being viewed by others

Data availability

The data that support the plots within this paper and other findings of this study are available from the corresponding authors on reasonable request.

Code availability

The codes used for simulation and data plotting are available from the corresponding authors on reasonable request.

References

Haensch, W. et al. Silicon CMOS devices beyond scaling. IBM J. Res. Dev. 50, 339–361 (2006).

Thompson, S. E. & Parthasarathy, S. Moore’s law: the future of Si microelectronics. Mater. Today 9, 20–25 (2006).

Waldrop, M. M. The chips are down for Moore’s law. Nature 530, 144–147 (2016).

Yu, B. et al. FinFET scaling to 10-nm gate length. IEDM Tech. Dig. 251–254 (2002).

Yeo, K. H. et al. Gate-all-around (GAA) twin silicon nanowire MOSFET (TSNWFET) with 15-nm length gate and 4-nm radius nanowires. IEDM Tech. Dig. 1–2 (2006).

Si, M. et al. Steep-slope hysteresis-free negative capacitance MoS2 transistors. Nat. Nanotechnol. 13, 24–28 (2018).

Chen, Y. et al. Optoelectronic properties analysis of silicon light-emitting diode monolithically integrated in standard CMOS IC. Chin. Phys. B 28, 107801 (2019).

Khan, A. I., Keshavarzi, A. & Datta, S. The future of ferroelectric field-effect transistor technology. Nat. Electron. 3, 588–597 (2020).

Convertino, C. et al. A hybrid III–V tunnel FET and MOSFET technology platform integrated on silicon. Nat. Electron. 4, 162–170 (2021).

Xu, K. Silicon electro-optic micro-modulator fabricated in standard CMOS technology as components for all silicon monolithic integrated optoelectronic systems. J. Micromech. Microeng. 31, 054001 (2021).

Huang, J.-K. et al. High-κ perovskite membranes as insulators for two-dimensional transistors. Nature 605, 262–267 (2022).

Heinzig, A. et al. Reconfigurable silicon nanowire transistors. Nano Lett. 12, 119–124 (2012).

Groenendijk, D. J. et al. Photovoltaic and photothermoelectric effect in a double-gated WSe2 device. Nano Lett. 14, 5846–5852 (2014).

Appenzeller, J. et al. Band-to-band tunneling in carbon nanotube field-effect transistors. Phys. Rev. Lett. 93, 196805 (2004).

Lin, Y.-M., Appenzeller, J. & Avouris, P. Novel carbon nanotube FET design with tunable polarity. IEDM Tech. Dig. 687–690 (2004).

Colli, A. et al. Top-gated silicon nanowire transistors in a single fabrication step. ACS Nano 3, 1587–1593 (2009).

Mongillo, M. et al. Multifunctional devices and logic gates with undoped silicon nanowires. Nano Lett. 12, 3074–3079 (2012).

Michele, D. M. et al. Polarity control in double-gate, gate-all-around vertically stacked silicon nanowire FETs. IEDM Tech. Dig. 8.4.1–8.4.4 (2012).

Heinzig, A. et al. Reconfigurable silicon nanowire transistor. Nano Lett. 12, 119–124 (2012).

Trommer, J. et al. Elementary aspects for circuit implementation of reconfigurable nanowire transistors. IEEE Electron Device Lett. 35, 141–143 (2013).

Rai, S. et al. Designing efficient circuits based on runtime-reconfigurable field-effect transistors. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 27, 560–572 (2018).

Pospischil, A., Furchi, M. M. & Mueller, T. Solar-energy conversion and light emission in an atomic monolayer p–n diode. Nat. Nanotechnol. 9, 257–261 (2015).

Bie, Y. Q. et al. A MoTe2-based light-emitting diode and photodetector for silicon photonic integrated circuits. Nat. Nanotechnol. 12, 1124–1129 (2017).

Avsar, A. et al. Reconfigurable diodes based on vertical WSe2 transistors with van der Waals bonded contacts. Adv. Mater. 30, 1707200 (2018).

Pan, C. et al. Reconfigurable logic and neuromorphic circuits based on electrically tunable two-dimensional homojunctions. Nat. Electron. 3, 383–390 (2020).

Chen, P. et al. Approaching the intrinsic exciton physics limit in two-dimensional semiconductor diodes. Nature 599, 404–410 (2021).

Wu, P. et al. Two-dimensional transistors with reconfigurable polarities for secure circuits. Nat. Electron. 4, 45–53 (2021).

Ghosh, S. et al. Enhanced responsivity and detectivity of fast WSe2 phototransistor using electrostatically tunable in-plane lateral p–n homojunction. Nat. Commun. 12, 3336 (2021).

Zhou, Y. et al. A reconfigurable two-WSe2-transistor synaptic cell for reinforcement learning. Adv. Mater. 34, 2107754 (2022).

Wu, G. et al. MoTe2 p–n homojunctions defined by ferroelectric polarization. Adv. Mater. 32, 1907937 (2020).

Tong, L. et al. 2D materials-based homogeneous transistor-memory architecture for neuromorphic hardware. Science 373, 1353–1358 (2021).

Luo, Z. D. et al. Dual-ferroelectric-coupling-engineered two-dimensional transistors for multifunctional in-memory computing. ACS Nano 16, 3362–3372 (2022).

Ma, T. P. Why is nonvolatile ferroelectric memory field-effect transisor still elusive? IEEE Electron Device Lett. 23, 386–388 (2002).

Wang, Z. et al. Resistive switching materials for information processing. Nat. Rev. Mater. 5, 173–195 (2020).

Ju, L. et al. Photoinduced doping in heterostructures of graphene and boron nitride. Nat. Nanotechnol. 9, 348–352 (2014).

Wu, E. et al. Photoinduced doping to enable tunable and high-performance anti-ambipolar MoTe2/MoS2 heterotransistors. ACS Nano 13, 5430–5438 (2019).

Wu, E. et al. Dynamically controllable polarity modulation of MoTe2 field-effect transistors through ultraviolet light and electrostatic activation. Sci. Adv. 5, eaav3430 (2019).

Xu, M. et al. Optoelectronic synapses based on photo-induced doping in MoS2/h-BN field-effect transistors. Adv. Opt. Mater. 9, 2100937 (2021).

Li, S. et al. A high-performance in-memory photodetector realized by charge storage in a van der Waals MISFET. Adv. Mater. 34, 2107734 (2022).

Marega, G. M. et al. Logic-in-memory based on an atomically thin semiconductor. Nature 587, 72–77 (2020).

Tran, T. T. et al. Quantum emission from hexagonal boron nitride monolayers. Nat. Nanotechnol. 11, 37–41 (2016).

Liu, X. et al. Manipulating charge and energy transfer between 2D atomic layers via heterostructure engineering. Nano Lett. 20, 5359–5366 (2020).

Lee, K. C. et al. Analog circuit applications based on all‐2D ambipolar ReSe2 field‐effect transistors. Adv. Funct. Mater. 29, 1809011 (2019).

Yang, S. H. et al. Multifunctional full-visible-spectrum optoelectronics based on a van der Waals heterostructure. Nano Energy 66, 104107 (2019).

Fei, W. et al. Emerging reconfigurable electronic devices based on two-dimensional materials: a review. InfoMat 4, e12355 (2022).

Xu, K. Silicon MOS optoelectronic micro-nano structure based on reversed-biased PN junction. Phys. Status Solidi A 216, 1800868 (2019).

Rabaey, J. M. et al. Digital Integrated Circuits 2nd edn (Pearson, 2003).

Arnold, A. J. et al. Mimicking neurotransmitter release in chemical synapses via hysteresis engineering in MoS2 transistors. ACS Nano 11, 3110–3118 (2017).

Yu, S. Neruo-inspired computing with emerging nonvolatile memorys. Proc. IEEE 106, 260–285 (2018).

John, R. A. et al. Synergistic gating of electro-iono-photoactive 2D chalcogenide neuristors: coexistence of Hebbian and homeostatic synaptic metaplasticity. Adv. Mater. 30, 1800220 (2018).

Alcami, P. & Pereda, A. E. Beyond plasticity: the dynamic impact of electrical synapses on neural circuits. Nat. Rev. Neurosci. 20, 253–271 (2019).

Zhang, W. et al. Neuro-inspired computing chips. Nat. Electron. 3, 371–382 (2020).

Ho, C.-H. & Liu, Z.-Z. Complete-series excitonic dipole emissions in few layer ReS2 and ReSe2 observed by polarized photoluminescence spectroscopy. Nano Energy 56, 641–650 (2019).

Acknowledgements

This work was supported by the Taiwan Ministry of Science and Technology (grants nos. MOST 109-2112-M-005-013-MY3, 111-2923-M-005-001-MY3 and 110-2119-M-007-003-MBK). This work was also financially supported by the Center for Semiconductor Technology Research from the Featured Areas Research Center Program within the framework of the Higher Education Sprout Project of the Ministry of Education (MOE) in Taiwan. This study was partly supported by the National Science and Technology Council, Taiwan, under grant no. NSTC 111-2634-F-A49-008. K.W. and T.T. acknowledge support from JSPS KAKENHI (grants nos. 19H05790, 20H00354 and 21H05233). We thank V. Pi-Ho Hu (National Taiwan University) for useful discussions and Jie Dong Co. for facility support.

Author information

Authors and Affiliations

Contributions

Y.-F.L., P.-W.C. and M.-Y.T. conceived and designed the entire experiments. J.-L.W. designed and realized the CNN simulation. M.-Y.T. and C.-T.H. fabricated the devices and conducted the measurements. M.-Y.T. completed the data analysis. The paper was written by Y.-F.L. and M.-Y.T. with contributions from all co-authors. Y.-F.L. and P.-W.C. supervised the research. C.-Y.L. provided some experimental methods. K.W., T.T. and C.-H.H. provided the 2D crystals. M.-P.L., F.-S.Y., M.L., Y.-M.C., W.-W.W. and M.Y. provided suggestions related to the experiments. All the authors discussed the results and commented on the manuscript.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Nature Electronics thanks Wei Chen, Jens Trommer and the other, anonymous, reviewer(s) for their contribution to the peer review of this work.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Supplementary Information

Supplementary Figs. 1–6, Notes 1 and 2 and Table.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Tsai, MY., Huang, CT., Lin, CY. et al. A reconfigurable transistor and memory based on a two-dimensional heterostructure and photoinduced trapping. Nat Electron 6, 755–764 (2023). https://doi.org/10.1038/s41928-023-01034-7

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1038/s41928-023-01034-7