Abstract

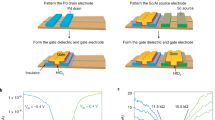

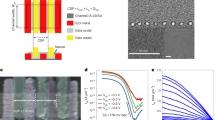

Carbon nanotube field-effect transistors (CNFETs) are a promising nanotechnology for the development of energy-efficient computing. Despite rapid progress, CNFETs have only been fabricated in academic or research laboratories. A critical challenge in transferring this technology to commercial manufacturing facilities is developing a suitable method for depositing nanotubes uniformly over industry-standard large-area substrates. Such a deposition method needs to be manufacturable, compatible with today’s silicon-based technologies, and provide a path to achieving systems with energy efficiency benefits over silicon. Here, we show that a deposition technique in which the substrate is submerged within a nanotube solution can address these challenges and can allow CNFETs to be fabricated within industrial facilities. By elucidating the mechanisms driving nanotube deposition, we develop process modifications to standard solution-based methods that significantly improve throughput, accelerating the deposition process by more than 1,100 times, while simultaneously reducing cost. This allows us to fabricate CNFETs in a commercial silicon manufacturing facility and high-volume semiconductor foundry. We demonstrate uniform and reproducible CNFET fabrication across industry-standard 200 mm wafers, employing the same equipment currently being used to fabricate silicon product wafers.

This is a preview of subscription content, access via your institution

Access options

Access Nature and 54 other Nature Portfolio journals

Get Nature+, our best-value online-access subscription

$29.99 / 30 days

cancel any time

Subscribe to this journal

Receive 12 digital issues and online access to articles

$119.00 per year

only $9.92 per issue

Buy this article

- Purchase on Springer Link

- Instant access to full article PDF

Prices may be subject to local taxes which are calculated during checkout

Similar content being viewed by others

Data availability

The data that support the findings of this study are available from the corresponding author upon reasonable request.

References

Dennard, R. H., Gaensslen, F. H., Rideout, V. L., Bassous, E. & LeBlanc, A. R. Design of ion-implanted MOSFET’s with very small physical dimensions. IEEE J. Solid-State Circuits 9, 256–268 (1974).

Moore, G. Moore’s law. Electronics 38, 114 (1965).

Hahn, P. O. The 300 mm silicon wafer—a cost and technology challenge. Microelectron. Eng. 56, 3–13 (2001).

Hills, G. et al. Understanding energy efficiency benefits of carbon nanotube field-effect transistors for digital VLSI. IEEE Trans. Nanotechnol. 17, 1259–1269 (2018).

Aly, M. M. S. et al. Energy-efficient abundant-data computing: the N3XT 1,000X. Computer 48, 24–33 (2015).

Frank, D. J. et al. Device scaling limits of Si MOSFETs and their application dependencies. Proc. IEEE 89, 259–288 (2001).

Javey, A., Guo, J., Wang, Q., Lundstrom, M. & Dai, H. Ballistic carbon nanotube field-effect transistors. Nature 424, 654–657 (2003).

Zhang, Z. et al. Doping-free fabrication of carbon nanotube based ballistic CMOS devices and circuits. Nano Lett. 7, 3603–3607 (2007).

Hills, G. et al. Rapid co-optimization of processing and circuit design to overcome carbon nanotube variations. IEEE Trans. Comput. Aided Des. 34, 1082–1095 (2015).

Amer, A. G., Ho, R., Hills, G., Chandrakasan, A. P., Shulaker, M. M., SHARC: Self-Healing Analog with RRAM and CNFETs. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC) 470–472 (IEEE, 2019).

Hills, G. et al. Modern microprocessor built from complementary carbon nanotube transistors. Nature 572, 595–602 (2019).

Srimani, T., Hills, G., Lau, C. & Shulaker, M. M. Monolithic three-dimensional imaging system: carbon nanotube computing circuitry integrated directly over silicon imager. In Proceedings of the 2019 Symposium on VLSI Technology (VLSI) 24–25 (IEEE, 2019).

Kanhaiya, P. S., Lau, C., Hills, G., Bishop, M. & Shulaker, M. M. 1 Kbit 6T SRAM arrays in carbon nanotube FET CMOS. In Proceedings of the 2019 Symposium on VLSI Technology (VLSI) 54–55 (IEEE, 2019).

Shulaker, M. M. et al. High-performance carbon nanotube field-effect transistors. In Proceedings of the 2014 IEEE International Electron Devices Meeting (IEDM) 33–36 (IEEE, 2014).

Brady, G. J. et al. Quasi-ballistic carbon nanotube array transistors with current density exceeding Si and GaAs. Science 2, e1601240 (2016).

Kanhaiya, P. S., Lau, C., Hills, G., Bishop, M. D. & Shulaker, M. M. Carbon nanotube-based CMOS SRAM: 1 kbit 6T SRAM arrays and 10T SRAM cells. IEEE Trans. Electron Devices 66, 5375–5380 (2019).

Qiu, C. et al. Scaling carbon nanotube complementary transistors to 5 nm gate lengths. Science 355, 271–276 (2017).

Cao, Q., Tersoff, J., Farmer, D. B., Zhu, Y. & Han, S. J. Carbon nanotube transistors scaled to a 40 nanometer footprint. Science 356, 1369–1372 (2017).

Lau, C., Srimani, T., Bishop, M. D., Hills, G. & Shulaker, M. M. Tunable n-type doping of carbon nanotubes through engineered atomic layer deposition HfOX films. ACS Nano 12, 10924–10931 (2018).

Zhong, D., Xiao, M., Zhang, Z. & Peng, L. M. Solution-processed carbon nanotubes based transistors with current density of 1.7 mA/μm and peak transconductance of 0.8 mS/μm. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM) 5–6 (IEEE, 2017).

Cao, Q. et al. Arrays of single-walled carbon nanotubes with full surface coverage for high-performance electronics. Nat. Nanotechnol. 8, 180–186 (2013).

Ding, J. et al. A hybrid enrichment process combining conjugated polymer extraction and silica gel adsorption for high purity semiconducting single-walled carbon nanotubes. Nanoscale 7, 15741–15747 (2015).

Green, A. A. & Hersam, M. C. Ultracentrifugation of single-walled nanotubes. Mater. Today 10, 59–60 (2007).

Baltzinger, J.-L. & Delahaye, B. In Semiconductor Technologies (ed. Grym, J.) Ch. 4, 57–78 (IntechOpen, 1999).

Srimani, T., Hills, G., Bishop, M. D. & Shulaker, M. M. 30 nm contacted gate pitch back-gate carbon nanotube FETs for sub-3 nm nodes. IEEE Trans. Nanotechnol. 18, 132–138 (2018).

Langmuir, I. The adsorption of gases on plane surfaces of glass, mica and platinum. J. Am. Chem. Soc. 40, 1361–1403 (1918).

Park, J. J. et al. Langmuir adsorption study of the interaction of CdSe/ZnS quantum dots with model substrates: influence of substrate surface chemistry and pH. Langmuir 25, 443–450 (2008).

Schaaf, P. & Talbot, J. Surface exclusion effects in adsorption processes. J. Chem. Phys. 91, 4401–4409 (1989).

Langmuir, I. The constitution and fundamental properties of solids and liquids. Part I. Solids. J. Am. Chem. Soc. 38, 2221–2295 (1916).

Azizian, S. Kinetic models of sorption: a theoretical analysis. J. Colloid Interface Sci. 276, 47–52 (2004).

Ho, Y. S. Review of second-order models for adsorption systems. J. Hazard. Mater. 136, 681–689 (2006).

Foo, K. Y. & Hameed, B. H. Insights into the modeling of adsorption isotherm systems. Chem. Eng. J. 156, 2–10 (2010).

Gorintin, L., Bondavalli, P., Legagneux, P. & Pribat, D. High performances CNTFETs achieved using CNT networks for selective gas sensing. Proc. SPIE 7399, 739909 (2009).

Bardon, M. G. et al. Extreme scaling enabled by 5 tracks cells: holistic design-device co-optimization for FinFETs and lateral nanowires. In Proceedings of the 2016 IEEE International Electron Devices Meeting (IEDM) 22–28 (IEEE, 2016).

Deegan, R. D. et al. Capillary flow as the cause of ring stains from dried liquid drops. Nature 389, 827–829 (1997).

Li, Q., Zhu, Y. T., Kinloch, I. A. & Windle, A. H. Self-organization of carbon nanotubes in evaporating droplets. J. Phys. Chem. B 110, 13926–13930 (2006).

Brady, G., Joo, Y., Wu, M., Shea, M. & Gopalan, P. Polyfluorene-sorted, carbon nanotube array field-effect transistors with increased current density and high on/off ratio. ACS Nano 8, 11614–11621 (2014).

Lee, C.-S., Pop, E., Franklin, A. D., Haensch, W. & Wong, H.-S. A compact virtual-source model for carbon nanotube FETs in the sub-10 nm regime—Part I: intrinsic elements. IEEE Trans. Electron Devices 62, 3061–3069 (2015).

Pitner, G. et al. Low-temperature side contact to carbon nanotube transistors: resistance distributions down to 10 nm contact length. Nano Lett. 19, 1083–1089 (2019).

Acknowledgements

We acknowledge support from Analog Devices Inc. (ADI), SkyWater Technology, the Defense Advanced Research Projects Agency (DARPA) Three-Dimensional System-on-Chip (3DSoC) programme (HR0011-18-3-0006) and the Air Force Research Laboratory for support. We thank S. Feindt and A. Olney from ADI and B. Ferguson from SkyWater for collaboration. We acknowledge J. Daley (MIT) for his guidance concerning helium ion microscopy, as well as the Microsystems Technology Laboratories (MTL, MIT). The views, opinions and/or findings expressed are those of the author and should not be interpreted as representing the official views or policies of the Department of Defense or the US Government.

Author information

Authors and Affiliations

Contributions

M.D.B. led all of the research and was involved in all aspects of the work. G.H. performed the VLSI analysis. T.S., M.D.B., C.L. and M.M.S. led efforts with A.R. and M.N. to develop and transfer technology to SkyWater Foundry, and T.S., M.D.B., C.L. and M.M.S. led efforts with D.M. and S.F. to develop and transfer technology to ADI. J.H., M.D.B. and M.M.S. developed and tested the purified contaminant-free 99.99% semiconducting CNT solution. M.M.S. advised and led on all aspects of the project.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Supplementary Information

Supplementary Figs. 1–10, discussion and Table 1.

Rights and permissions

About this article

Cite this article

Bishop, M.D., Hills, G., Srimani, T. et al. Fabrication of carbon nanotube field-effect transistors in commercial silicon manufacturing facilities. Nat Electron 3, 492–501 (2020). https://doi.org/10.1038/s41928-020-0419-7

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1038/s41928-020-0419-7

This article is cited by

-

Optimizing fault tolerance of RAM cell through MUX based modeling and design using symmetries of QCA cells

Scientific Reports (2024)

-

Design an energy efficient pulse triggered ternary flip flops with Pseudo NCFET logic

Analog Integrated Circuits and Signal Processing (2024)

-

A programmable gain amplifier based on a two-level CNTFET op amp with optimized trans-conductance to drain current ratio

Analog Integrated Circuits and Signal Processing (2024)

-

Chirality-dependent electrical transport properties of carbon nanotubes obtained by experimental measurement

Nature Communications (2023)

-

Chemiresistive sensing with functionalized carbon nanotubes

Nature Reviews Methods Primers (2023)