Abstract

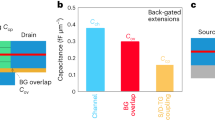

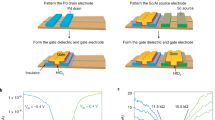

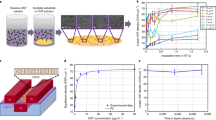

Aligned semiconducting carbon nanotubes are a potential alternative to silicon in the creation of scaled field-effect transistors (FETs) due to their easy miniaturization and high energy efficiency. However, it remains unclear whether aligned nanotube transistors can be fabricated at the same dimensions as low-node silicon technology and maintaining high performance. Here we report aligned carbon nanotube FETs that can be scaled to a size corresponding to the 10 nm silicon technology node. We first fabricate nanotube FETs with a contacted gate pitch of 175 nm (achieved by scaling the gate length and contact length to 85 nm and 80 nm, respectively) that exhibit an on current of 2.24 mA μm–1 and peak transconductance of 1.64 mS μm–1; this is superior to 45 nm silicon technology node transistors in terms of size and electronic performance. Six nanotube FETs are used to create a static random-access memory cell with an area of 0.976 μm2, which is comparable with the 90 nm silicon technology node. A full-contact structure is then introduced between the metal and nanotubes to achieve a low contact resistance of 90 Ω μm and reduce the dependence on the contact length. This is used to create nanotube FETs with a contacted gate pitch of 55 nm—corresponding to the 10 nm node—with carrier mobility and Fermi velocity higher than the 10 nm silicon metal–oxide–semiconductor transistors.

This is a preview of subscription content, access via your institution

Access options

Access Nature and 54 other Nature Portfolio journals

Get Nature+, our best-value online-access subscription

$29.99 / 30 days

cancel any time

Subscribe to this journal

Receive 12 digital issues and online access to articles

$119.00 per year

only $9.92 per issue

Buy this article

- Purchase on Springer Link

- Instant access to full article PDF

Prices may be subject to local taxes which are calculated during checkout

Similar content being viewed by others

Data availability

The data that support the plots within this paper are available from the corresponding authors upon reasonable request.

References

Haensch, W. et al. Silicon CMOS devices beyond scaling. IBM J. Res. Dev. 50, 339–361 (2006).

Liu, C. et al. Two-dimensional materials for next-generation computing technologies. Nat. Nanotechnol. 15, 545–557 (2020).

Leiserson, C. E. et al. There’s plenty of room at the top: what will drive computer performance after Moore’s law? Science 368, eaam9744 (2020).

The International Roadmap for Devices and Systems: 2020 https://irds.ieee.org/Editions/2020 (2020).

Cao, Q. Carbon nanotube transistor technology for more-Moore scaling. Nano Res. 14, 3051–3069 (2021).

Akinwande, D. et al. Graphene and two-dimensional materials for silicon technology. Nature 573, 507–518 (2019).

Liu, L. et al. Uniform nucleation and epitaxy of bilayer molybdenum disulfide on sapphire. Nature 605, 69–75 (2022).

Lin, Y. et al. Enhancement‐mode field‐effect transistors and high‐speed integrated circuits based on aligned carbon nanotube films. Adv. Funct. Mater. 32, 2104539 (2022).

Wu, Z. et al. Large-scale growth of few-layer two-dimensional black phosphorus. Nat. Mater. 20, 1203–1209 (2021).

Shi, H. et al. Radiofrequency transistors based on aligned carbon nanotube arrays. Nat. Electron. 4, 405–415 (2021).

Liu, L. et al. Aligned, high-density semiconducting carbon nanotube arrays for high-performance electronics. Science 368, 850–856 (2020).

Cao, Q., Tersoff, J., Farmer, D. B., Zhu, Y. & Han, S.-J. Carbon nanotube transistors scaled to a 40-nanometer footprint. Science 356, 1369–1372 (2017).

Shulaker, M. M. et al. Carbon nanotube computer. Nature 501, 526–530 (2013).

Franklin, A. D. Nanomaterials in transistors: from high-performance to thin-film applications. Science 349, aab2750 (2015).

Avouris, P., Chen, Z. & Perebeinos, V. Carbon-based electronics. Nat. Nanotechnol. 2, 605–615 (2007).

Qiu, C. et al. Scaling carbon nanotube complementary transistors to 5-nm gate lengths. Science 355, 271–276 (2017).

Zhao, M. et al. DNA-directed nanofabrication of high-performance carbon nanotube field-effect transistors. Science 368, 878–881 (2020).

Geier, M. L. et al. Solution-processed carbon nanotube thin-film complementary static random access memory. Nat. Nanotechnol. 10, 944–948 (2015).

Cao, Q. et al. Arrays of single-walled carbon nanotubes with full surface coverage for high-performance electronics. Nat. Nanotechnol. 8, 180–186 (2013).

Park, H. et al. High-density integration of carbon nanotubes via chemical self-assembly. Nat. Nanotechnol. 7, 787–791 (2012).

Datta, S. Ten nanometre CMOS logic technology. Nat. Electron. 1, 500–501 (2018).

Cao, Q. et al. End-bonded contacts for carbon nanotube transistors with low, size-independent resistance. Science 350, 68–72 (2015).

Shulaker, M. M. et al. Three-dimensional integration of nanotechnologies for computing and data storage on a single chip. Nature 547, 74–78 (2017).

Samavedam, S. et al. Future logic scaling: towards atomic channels and deconstructed chips. In 2020 IEEE International Electron Devices Meeting 1.1.1–1.1.10 (IEEE, 2020).

Zhu, M. G., Zhang, Z. & Peng, L. M. High‐performance and radiation‐hard carbon nanotube complementary static random‐access memory. Adv. Electron. Mater. 5, 1900313 (2019).

Ghani, T. et al. A 90 nm high volume manufacturing logic technology featuring novel 45 nm gate length strained silicon CMOS transistors. In 2003 IEEE International Electron Devices Meeting 11.16.11–11.16.13 (IEEE, 2003).

Kim, W. et al. Electrical contacts to carbon nanotubes down to 1 nm in diameter. Appl. Phys. Lett. 87, 173101 (2005).

Xu, L., Gao, N., Zhang, Z. & Peng, L.-M. Lowering interface state density in carbon nanotube thin film transistors through using stacked Y2O3/HfO2 gate dielectric. Appl. Phys. Lett. 113, 083105 (2018).

Bohr, M. T. et al. A high performance 0.35 μm logic technology for 3.3 V and 2.5 V operation. In 1994 IEEE International Electron Devices Meeting 273–276 (IEEE, 1994).

Brand, A. et al. Intel’s 0.25 micron, 2.0 volts logic process technology. Intel. Technol. J. Q 3, 1998 (1998).

Yang, S. et al. A high performance 180 nm generation logic technology. In 1998 IEEE International Electron Devices Meeting Technical Digest (Cat. No. 98CH36217) 197–200 (IEEE, 1998).

Tyagi, S. et al. A 130 nm generation logic technology featuring 70 nm transistors, dual Vt transistors and 6 layers of Cu interconnects. In 2000 IEEE International Electron Devices Meeting Technical Digest IEDM (Cat. No. 00CH37138) 567–570 (IEEE, 2000).

Mistry, K. et al. A 45 nm logic technology with high-k+metal gate transistors, strained silicon, 9 Cu interconnect layers, 193 nm dry patterning, and 100% Pb-free packaging. In 2007 IEEE International Electron Devices Meeting 247–250 (IEEE, 2007).

Natarajan, S. et al. A 32 nm logic technology featuring 2nd-generation high-k+metal-gate transistors, enhanced channel strain and 0.171 μm2 SRAM cell size in a 291 Mb array. In 2008 IEEE International Electron Devices Meeting 1–3 (IEEE, 2008).

Auth, C. et al. A 22 nm high performance and low-power CMOS technology featuring fully-depleted tri-gate transistors, self-aligned contacts and high density MIM capacitors. In 2012 Symposium on VLSI Technology (VLSIT) 131–132 (IEEE, 2012).

Natarajan, S. et al. A 14 nm logic technology featuring 2nd-generation FinFET, air-gapped interconnects, self-aligned double patterning and a 0.0588 µm2 SRAM cell size. In 2014 IEEE International Electron Devices Meeting 3.7.1–3.7.3 (IEEE, 2014).

Auth, C. et al. A 10 nm high performance and low-power CMOS technology featuring 3rd generation FinFET transistors, self-aligned quad patterning, contact over active gate and cobalt local interconnects. In 2017 IEEE International Electron Devices Meeting 29.21.21–29.21.24 (IEEE, 2017).

Chen, R. et al. Carbon nanotube SRAM in 5-nm technology node design, optimization, and performance evaluation—part I: CNFET transistor optimization. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 30, 432–439 (2022).

Banerjee, S., Chaudhuri, A. & Chakrabarty, K. Analysis of the impact of process variations and manufacturing defects on the performance of carbon-nanotube FETs. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 28, 1513–1526 (2020).

Cao, Q. et al. Origins and characteristics of the threshold voltage variability of quasiballistic single-walled carbon nanotube field-effect transistors. ACS Nano 9, 1936–1944 (2015).

Suriyasena Liyanage, L., Xu, X., Pitner, G., Bao, Z. & Wong, H. S. P. VLSI-compatible carbon nanotube doping technique with low work-function metal oxides. Nano Lett. 14, 1884–1890 (2014).

Zhong, D., Zhao, C., Liu, L., Zhang, Z. & Peng, L.-M. Continuous adjustment of threshold voltage in carbon nanotube field-effect transistors through gate engineering. Appl. Phys. Lett. 112, 153109 (2018).

Wang, X. et al. Pass‐transistor logic circuits based on wafer‐scale 2D semiconductors. Adv. Mater. 34, 2202472 (2022).

Pang, C.-S., Thakuria, N., Gupta, S. K. & Chen, Z. First demonstration of WSe2 based CMOS-SRAM. In 2018 IEEE International Electron Devices Meeting (IEDM) 22.22.21–22.22.24 (IEEE, 2018).

Wang, H. et al. Integrated circuits based on bilayer MoS2 transistors. Nano Lett. 12, 4674–4680 (2012).

Allain, A., Kang, J., Banerjee, K. & Kis, A. Electrical contacts to two-dimensional semiconductors. Nat. Mater. 14, 1195–1205 (2015).

Franklin, A. D. & Chen, Z. Length scaling of carbon nanotube transistors. Nat. Nanotechnol. 5, 858–862 (2010).

Pitner, G. et al. Low-temperature side contact to carbon nanotube transistors: resistance distributions down to 10 nm contact length. Nano Lett. 19, 1083–1089 (2019).

Franklin, A. D., Farmer, D. B. & Haensch, W. Defining and overcoming the contact resistance challenge in scaled carbon nanotube transistors. ACS Nano 8, 7333–7339 (2014).

Kang, J., Sarkar, D., Liu, W., Jena, D. & Banerjee, K. A computational study of metal-contacts to beyond-graphene 2D semiconductor materials. In 2012 International Electron Devices Meeting 17.14.11–17.14.14 (IEEE, 2012).

Nandakumar, M. et al. Shallow trench isolation for advanced ULSI CMOS technologies. In 1998 IEEE International Electron Devices Meeting 133–136 (IEEE, 1998).

Xu, L., Qiu, C., Zhao, C., Zhang, Z. & Peng, L.-M. Insight into ballisticity of room-temperature carrier transport in carbon nanotube field-effect transistors. IEEE Trans. Electron Devices 66, 3535–3540 (2019).

Thompson, S. E. et al. A 90-nm logic technology featuring strained-silicon. In 2004 IEEE International Electron Devices Meeting 51, 1790–1797 (IEEE, 2004).

Del Alamo, J. A. Nanometre-scale electronics with III–V compound semiconductors. Nature 479, 317–323 (2011).

Xu, L., Qiu, C., Peng, L.-M. & Zhang, Z. Suppression of leakage current in carbon nanotube field-effect transistors. Nano Res. 14, 976–981 (2020).

Zhao, C. et al. Strengthened complementary metal–oxide–semiconductor logic for small-band-gap semiconductor-based high-performance and low-power application. ACS Nano 14, 15267–15275 (2020).

Srimani, T. et al. Asymmetric gating for reducing leakage current in carbon nanotube field-effect transistors. Appl. Phys. Lett. 115, 063107 (2019).

Liu, C. et al. Complementary transistors based on aligned semiconducting carbon nanotube arrays. ACS Nano 16, 21482–21490 (2022).

Xiao, M. et al. n‐type Dirac‐source field‐effect transistors based on a graphene/carbon nanotube heterojunction. Adv. Electron. Mater. 6, 2000258 (2020).

Qiu, C. G. et al. Dirac-source field-effect transistors as energy-efficient, high-performance electronic switches. Science 361, 387–391 (2018).

Acknowledgements

This work is supported by the National Key Research & Development Program (grant no. 2022YFB4401601), Natural Science Foundation of China (62225101), Beijing Municipal Science and Technology Commission (grant no. Z191100007019001-3) and Peking Nanofab Laboratory.

Author information

Authors and Affiliations

Contributions

Z.Z. and L.-M.P. proposed and supervised the project. Y.L. and Y.C. fabricated the scaled aligned CNT FETs and 6T SRAM cells. Y.L. and Y.C. characterized the devices and 6T SRAM cells. P.Z. calculated the power consumptions of the per write operation between aligned CNT and Si 6T SRAM cells. L.X. extracted the mobility and injection velocity of the CNTs using the virtual source model. S.D. and C.J. performed the TEM characterizations. C.L. and Q.H. helped characterize the devices. Y.L., Y.C., Z.Z. and L.-M.P. analysed the data and wrote the manuscript. All authors discussed the results and commented on the manuscript.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Nature Electronics thanks Ming Lei and the other, anonymous, reviewer(s) for their contribution to the peer review of this work.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Supplementary Information

Supplementary Figs. 1–14, Discussions 1 and 2 and Tables 1–4.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Lin, Y., Cao, Y., Ding, S. et al. Scaling aligned carbon nanotube transistors to a sub-10 nm node. Nat Electron 6, 506–515 (2023). https://doi.org/10.1038/s41928-023-00983-3

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1038/s41928-023-00983-3

This article is cited by

-

Complementary carbon nanotube metal–oxide–semiconductor field-effect transistors with localized solid-state extension doping

Nature Electronics (2023)

-

Pushing carbon nanotube circuits below the 10-nm node

Nature Electronics (2023)