Abstract

Despite intensive studies on van der Waals heterostructures based on two-dimensional layered materials, isotype vdW heterojunctions, which consist of two different semiconductors with the same majority carrier, have received little attention. We demonstrate an n–n isotype field-effect heterojunction device composed of multilayer moly ditelluride (MoTe2) and tin disulfide (SnS2). The carrier transport flowing through the n-MoTe2/n-SnS2 heterojunction exhibits a clear rectifying behavior exceeding 103, even at a moderate source–drain voltage of 1 V in ambient environment. Owing to the large band offsets between the two materials, a potential barrier exceeding ~1 eV is formed, which is verified by comparing a numerical solution of Poisson’s equation and experimental data. In contrast to the conventional p–n heterostructure operating by diffusion of the minority carrier, we identify the carrier transport is governed by the majority carrier via the thermionic emission and tunneling-mediated process through the potential barrier. Furthermore, the gate voltage can completely turn off the device and even enhance the rectification. A ternary inverter based on the isotype MoTe2/SnS2 heterojunction and a SnS2 channel transistor is demonstrated for potential multivalued logic applications. Our results suggest that the isotype vdW heterojunction will become an able candidate for electronic or optoelectronic devices after suitable band engineering and design optimization.

Similar content being viewed by others

Introduction

Van der Waals (vdW) heterostructures based on two-dimensional (2D) layered materials have been extensively studied owing to its enormous combinations of selectable materials and excellent semiconducting properties. These structures have replaced conventional group IV- or III–V-based materials for applications in electronics and related fields1,2,3,4. Weak vdW interactions between individual layers and the absence of dangling bonds at the interfaces make it possible to fabricate high-performance devices5,6,7,8,9. On the one hand, unisotype vdW heterostructures, namely p–n junction, have only been studied as a building block for diodes or optoelectronic devices with distinct current rectification, gate-tunable polarity behavior, negative differential resistance from the band-to-band tunneling, and photovoltaic effect10,11,12,13,14,15,16,17,18,19,20,21. While there are a variety of choices for n-type vdW materials, there are few natural p-type vdW materials such as black phosphorus10,11,12,13,14,15 and WSe27,16,17,18,19,20,21.

On the other hand, there are few published research works on isotype vdW heterojunction, in which the transport dominated by the same majority carriers in both components. For optoelectronic device, photodetectors made of isotype vdW heterojunctions with WS2 and MoS2 were recently reported22,23. One of the reasons why isotype heterojunction is not considered for electronic devices is that it has a smaller expected rectifying response than p–n heterojunctions. However, the lack of natural p-type vdW materials has shifted the focus of researchers toward isotype vdW heterojunctions, especially n–n type, because there are enormous candidate materials.

In this study, an isotype heterojunction device combined with a multilayer moly ditelluride (MoTe2) and tin disulfide (SnS2) is demonstrated. The transistor is fabricated by exfoliating each material and stacking them by the polydimethylpolysiloxane (PDMS) dry transfer method on a Si/SiO2 (300 nm) substrate (see the details in the Methods section)24. The transport properties of individual SnS2 and MoTe2 channels were measured. It was confirmed that the conductivity of SnS2 is n type, regardless of its thickness, and MoTe2 exhibits n-type behavior for a thick flake. SnS2 has a large electron affinity (~5.2 eV) and bandgap (~2.2 eV) in the bulk phase25, which can form distinct band alignments when combined with other transition metal dichalcogenide (TMD) groups26,27,28. MoTe2, however, has a smaller electron affinity (~3.8 eV) and smaller bandgap (~0.9 eV)27. Therefore, a large band offset and a large built-in potential barrier at the heterojunction between MoTe2 and SnS2 is expected to form. In addition, we measured the Raman spectroscopy of the vdW heterojunction and confirmed the electron transfer from MoTe2 to SnS2 side according to Anderson’s rule.

As a result, the electrical measurement of the MoTe2/SnS2 heterojunction device clearly exhibits rectification. From the systematic analysis of carrier transport, based on a numerical solution of Poisson’s equation and Simmons approximation, we ascribe the rectifying behavior to the large band offsets between the two materials, which creates a large potential barrier at the heterojunction. In addition, we certify the switchable rectification characteristic by varying the gate voltage with a maximum rectification ratio of ~103, at a modestly low source–drain voltage of 1 V and in ambient environment (room temperature of 300 K). This value is comparable with that of other p–n unisotype vdW heterostructure devices from previous reports17,23,29,30. Finally, we demonstrate a ternary inverter using the MoTe2/SnS2 heterojunction and a SnS2 channel transistor. We emphasize that this is the first experimental study reporting a systematical analysis of the MoTe2/SnS2 heterojunction device.

Results

Device structure and Raman spectrum of the heterojunction

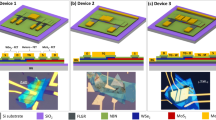

Figure 1a shows the microscopic image of the multilayer MoTe2/SnS2 heterojunction device with four Ti/Au electrodes. Figure 1b is the schematic side view of the fabricated device. The four electrodes are used to compare the individual channel and heterojunction channel in a single device, i.e., the electronic properties of MoTe2, SnS2, and MoTe2/SnS2 heterojunctions can be examined using electrodes E1–E2, E3–E4, and E2–E3, respectively. Figure 1c shows the atomic force microscope (AFM) image for the green dashed box in Fig. 1a. From the topographic image and the respective height profiles (represented by solid black and red lines), the thicknesses of SnS2 and MoTe2 are approximately 30 and 70 nm, respectively.

a The optical image and b the schematic side view of the MoTe2/SnS2 heterojunction device, respectively. The scale bar used is 10 μm. E1 and E2 (E3 and E4) are the electrodes to measure the electrical properties of MoTe2 (SnS2) individual channels and E2–E3 is for the heterojunction channel. c Topographic image for the green dashed box in the optical images, and the respective height profiles. d Raman spectra of the samples at different positions. e Raman shift in the SnS2 A1g peak after heterojunction formation.

The Raman scattering measurement was performed on different channel areas of the fabricated device. The measured areas were marked with the black (MoTe2), red (SnS2). and green dots (heterojunction) in Fig. 1a, and each Raman spectrum is shown in Fig. 1d, respectively. We used a 514-nm green laser as the excitation source. On the MoTe2 region (black line), two peaks appear near 171 and 230 cm−1, corresponding to the respective out-of-plane A1g and in-plane E12g phonon modes. The bulk inactive B12g phonon mode around 290 cm−1 is not observed in our MoTe2 thick flake (Supplementary Fig. 1), which agrees with the previously reported observations31,32,33. The spectrum in the SnS2 region (red line) shows a prominent peak of the A1g mode at ~315 cm−1 and a weaker peak of the Eg mode near 206 cm−1, which are also consistent with previous results34,35. In the heterojunction region (green), the peaks receive contributions from both MoTe2 and SnS2, indicating the existence of two distinct materials. Especially, a significant reduction of the SnS2 Raman peak intensity was observed due to the thick MoTe2 flake (~70 nm) placed on the SnS2 flake. This, in turn, led to the feeble peak of Eg that is indistinguishable in the overlapped region. In addition, we observe a redshift of ~3 cm−1 in the out-of-plane mode (A1g), owing to the phonon softening caused by the electron transfer from MoTe2 to SnS236. The electron affinity rule (Anderson’s rule) accounts for this electron transfer.

Electrical characteristics and the band alignment

Figure 2a, b shows the transfer characteristics of individual MoTe2 and SnS2 channel FET with electrodes E1–E2 and E3–E4, respectively. A back-gate voltage (Vg) was applied to the heavily n-doped (As dopants) Si substrate with a resistivity of ~0.005 Ω cm. All electronic measurements were carried out under ambient conditions (room temperature of 300 K). The observed linear output curves at different gate voltages for both MoTe2 and SnS2 FETs in the inset of Fig. 2a, b suggest the sufficiently low contact resistances between Ti/Au metal electrodes and both materials37,38. At the source–drain voltage (Vds) of 1 V, n-type dominant ambipolar behavior was observed for the bulk MoTe238,39,40,41. We checked the low gate leakage current through SiO2—300-nm thick—in tens of picoampere level for whole gate voltage ranges as shown in Supplementary Fig. 2. Specifically, MoTe2 FET exhibited ambipolar behavior for an intermediate flake and p-type behavior for a thin flake, as shown in Supplementary Fig. 2. This dependence of change in conductivity on the thickness has been reported in previous studies as well42,43. For SnS2, a typical n-type unipolar was observed37,44,45,46. It is noteworthy that we achieved sufficiently high on/off ratios (~105) in both FETs with thick flakes even though they operate in the depletion-mode, i.e., a negative gate voltage for an n-channel transistor is required to turn off the device. Usually, the on/off ratio in a depletion-mode transistor limits the thickness of the channel material, because the gating field weakens gradually, or even entirely lost, as the distance between the gate oxide surface and the channel increases47. In other words, a large leakage current flows through the expanding undepleted parts as the channel thickness increases, leading to a poor on/off ratio. In this respect, the high on/off ratio in our devices implies that the carriers in the channel can be fully depleted under the given gate voltage. Especially, a very high on/off ratio reaching 107 in the SnS2 FET was achieved even with a thick flake (~30 nm), as shown in Fig. 2a. This result can be attributed to the larger bandgap of bulk SnS2 (~2.2 eV) than that of the other TMDs48. The small bandgap of bulk MoTe2 (~0.9 eV) accounts for the relatively high off-state current of MoTe2 FET.

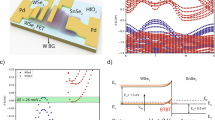

Figure 2c shows the band alignment of the MoTe2/SnS2 heterojunction before and after contact. The conduction band minimum (Ec) and valence band maximum (Ev) values of MoTe2 (SnS2) were previously reported to be 3.8 eV (5.2 eV) and 4.7 eV (7.4 eV), respectively26,27,28. A very large conduction band offset (ΔEc) and valence band offset (ΔEv) of approximately 1.4 and 2.7 eV are achieved between MoTe2 and SnS2, respectively, compared with other combinations of 2D materials. Majority carrier concentrations per unit area for the respective channels (electron for both materials) at Vg = 0 V are estimated by16, \(n_{{\mathrm{MoTe}}_2}\left( {n_{{\mathrm{SnS}}_2}} \right) = \frac{{C_{{\mathrm{ox}}}\left| {V_{{\mathrm{th}}} - V_g} \right|}}{q} = 2.16 \times 10^{12}{\mathrm{(}}3.59 \times 10^{11}{\mathrm{)cm}}^{ - 2}\), where q = 1.6 × 10−19C and Cox = 1.15 × 10−8F/cm2 is the capacitance per unit area of the 300-nm-thick SiO2 gate oxide layer. The threshold voltage (Vth) is extracted based on the extrapolation in the linear region method, which finds the gate-voltage axis intercept of the linear extrapolation of transfer curves at the first maximum point of transconductance49. The values are −30 and −5 V for MoTe2 and SnS2 FET, respectively, as shown in Supplementary Fig. 3. We treated both MoTe2 and SnS2 as nondegenerate semiconductors, to simplify the calculations.

Thus, the Fermi level position was estimated using \(n^ \ast = {\int}_{E_c}^\infty {f(E)N(E)dE \cong N_c{\mathrm{exp}}\left( {\frac{{E_F - E_c}}{{k_{\mathrm{B}}T}}} \right)}\), where n* is the number of electrons per unit volume, Nc is the effective density of states in the conduction band, kB is the Boltzmann constant (1.38 × 10−23 J/K), and T is the temperature (300 K, in this case)50. Note that the channels in our devices were completely depleted under given gate voltages, which means the number of unit volumes can be simply calculated by dividing the carrier concentration obtained above by the material thickness (tMoTe2 = 70 nm, tSnS2 = 30 nm); n*MoTe2 = 3.07 × 1017 cm−3 and n*SnS2 = 1.2 × 1017 cm−3. Nc is equal to \(2\left( {\frac{{2\pi m ^\ast k_BT}}{{h^2}}} \right)^{3/2}\), where m* is the effective mass of the electron (0.55 m0 for MoTe2 and 0.43 m0 for SnS2)51,52,53 and h is the Planck constant (6.63 × 10−34 Js), giving Nc of 1.02 × 1019 and 7.08 × 1018 cm−3 for MoTe2 and SnS2, respectively. Consequently, the difference between the conduction band edge and Fermi level (EF–Ec) were calculated to be 0.09 eV for MoTe2 and 0.1 eV for SnS2. From this, the work functions were 3.89 eV (5.3 eV) for MoTe2 (SnS2).

From these band structures, the predicted band alignments of the heterojunction when these two materials were in contact were schematically described. The smaller work function of MoTe2 allows the electrons in the MoTe2 side to spill over to the SnS2 side until thermal equilibrium is established, forming a depletion region on the MoTe2 side and an accumulation region on the SnS2 side. This phenomenon is consistent with the Raman analysis in Fig. 1e. Thus, band bending occurs at the heterojunction, which yields the built-in potential ϕMo and ϕSn on the MoTe2 and SnS2 sides, respectively. The total built-in potential (Vbi) must be equal to the sum of the potential drops on the two sides (Vbi = ϕMo + ϕSn). It can be calculated from the work function difference between the two materials (~1.41 eV), since the Fermi level is constant and flat throughout the heterojunction at equilibrium. It is worth mentioning that ours is an isotype heterojunction, which is different from the conventional p–n junction heterostructures15,17,22. Therefore, the depletion region width on the MoTe2 side can be calculated by the following equations54:

where Nd,Mo ≈ 3.1 × 1017 cm−3 and Nd,Sn ≈ 1.2 × 1017 cm−3, calculated by Nd,Mo(Sn) = nMo(Sn)/tMo(Sn), from the electron majority carrier concentrations and thicknesses of each material. εMo = 10.1 and εSn = 17.7 are the dielectric constants of MoTe2 and SnS2, respectively55,56. Eqs. (1) and (2) can be solved for ϕSn, ϕMo, and xMo. Consequently, we obtained ϕMo = 1.3 eV, ϕSn = 0.11 eV, and xMo = 68.7 nm, as shown in Fig. 2c. This depletion region width is almost similar with the thickness of MoTe2 (70 nm), implying that the MoTe2 layer may be fully depleted after contact with SnS2 at equilibrium. The barrier height value of 1.31 eV will be used to identify the transport behavior of the junction. We note that the energy band alignment of this device is also similar to that in the previous report, where the band alignment was determined by the combination of X-ray photoemission spectroscopy and ultraviolet photoelectron spectroscopy measurements28.

Transport mechanism through the heterojunction

To examine the carrier transport through the MoTe2/SnS2 heterojunction at Vg = 0 V, a Vds of up to 5 V was applied to the electrode on the MoTe2 side (E2), and the electrode on SnS2 (E3) was grounded. The forward (If) and backward currents (Ib) are defined as arising when the positive and negative voltages are applied to E2, respectively. As shown in Fig. 3a, the backward current increased rapidly up to a few microamperes with Vds, and the forward current increased only up to a few hundreds of nanoamperes even at high Vds, showing a clear rectifying characteristic. We confirmed the same trend with the other devices, which also exhibited good rectification behavior (Supplementary Fig. 4). The rectification ratio with different Vds, defined as Ib/If at the same Vds, is illustrated in Fig. 3b. The ratio behaves significantly differently across Vds = 1.35 V. In the small Vds range represented by region (I), the rectification ratio increases until a maximum value of ~4 × 102. It then decreases in region (II), where Vds is larger than 1.35 V. This transitional behavior implies our device has two different transport mechanisms.

a Output characteristic of the MoTe2/SnS2 heterojunction device. The inset shows the logarithmic scale of the output curve. b Rectification ratio, defined by Ib/If at the same Vds, with the increasing magnitude of Vds. c Fowler–Nordheim plot. d Energy band diagrams of the heterojunction at different Vds.

We further investigated the transport of forward current using the Simmons approximation54 to figure out the rectification behavior and found out two distinctive transport mechanisms can explain our device’s transport property57. Direct tunneling (DT) and Fowler–Nordheim tunneling (FNT) can be expressed by the following relations:

where ϕ is the barrier height, d is the tunneling barrier width, h is the reduced Plank constant, and m* is the effective mass of an electron. With the above equations, we draw the Fowler–Nordheim plot, i.e., ln(I/V2) vs. 1/V plot, as shown in Fig. 3c. This plot clearly shows the transition from a logarithmic regime at small Vds for DT to a linear regime with a negative slope at high Vds for FNT, representing region I (pink) and region II (blue), respectively. The transition voltage (Vtrans) of 1.35 V is consistent with the voltage at which RR begins to decrease, indicating that the increased forward current via FNT gave rise to the decrease of the rectification ratio. Moreover, Vtrans corresponds to ϕ/q, yielding the tunneling barrier height of ~1.35 eV. This value is analogous with the value of ϕMo = 1.3 eV in the previous band diagram analysis. With the slope in the linear regime, \(\frac{{8\pi d\sqrt {2m^ \ast \phi ^3} }}{{3hq}} = 7.9\), where m* = 0.43 m0 is the effective mass of electron in SnS251,52, we obtained d ≈ 1.12 nm.

From these results, the band diagrams of Fig. 3d are used to explain the rectification behavior. Note that only the electron carrier transport is considered because the electron is the majority carrier for both materials. When a negative voltage is applied to the MoTe2 side (Vds < 0 V), the electron is transferred from the MoTe2 to the SnS2 side will face the much lower barrier height or even no barrier at high negative voltages. As a result, the electrons easily contribute to the current by overcoming the potential barrier, even with the small thermal energy via thermionic emission. This results in the rapidly increasing backward current. In contrast, in the range of 0 < Vds < 1.35 V, the electrons in the SnS2 side confront the built-in potential barrier, whose height is determined from the conduction band offset between MoTe2 and SnS2. This barrier blocks the electron transfer from the SnS2 side to the MoTe2 side, so that the current could be achieved purely by direct tunneling through the trapezoidal barrier. This current is lower than the backward current, causing the rectification property. However, for Vds > 1.35 V, the potential barrier becomes narrower, more triangular as shown in Fig. 3d. Consequently, the increased forward current via the FNT reduces the rectification ratio.

Next, we examine the output curves of MoTe2/SnS2 heterojunction at different gate voltages from −80 to 80 V in steps of 20 V, as shown in Fig. 4a. The simple measurement schematic is in the inset of Fig. 4a. The output curves of the heterojunction device illustrate the gate-tunable rectification behavior. The backward current was decreased as Vg was changed toward negative values, so that the rectification property became imperceptible. Indeed, the rectification ratio at Vds = 1 V was less than 10 for Vg < −20 V, as shown in Fig. 4b. Notably, the ratio reached up to ~103 in a positive Vg range. This value is more than twice the value at Vg = 0 V.

a Gate dependence of output characteristics of the MoTe2/SnS2 heterojunction in the range −1 to 1 V. The inset shows the schematic for the electrical measurement on the heterojunction. Vds is applied to E2, which is in contact with MoTe2, and E3, which is in contact with SnS2, is grounded. b Rectification ratio under different gate voltages at Vds = 1 V. The inset represents the band alignment at negative voltages. c Transfer characteristics of the heterojunction at |Vds| = 1 V.

To inspect these gate-tunable rectification properties, the corresponding transfer characteristics of the MoTe2/SnS2 heterojunction device are summarized in Fig. 4c. The transfer curve of the heterojunction on the backward current (green open circle) follows a similar trend with that of SnS2. The curve on the forward current (green closed circle) also follows that of SnS2 for Vg < −20 V. However, the current variation for Vg > −20 V with increasing Vg is negligible, yielding consistent gate-tunable rectification properties. From the transfer curves of the MoTe2 and SnS2 FET, SnS2 channel will turn off for Vg < −20 V, implying that there are no carriers, and the majority carrier in MoTe2 will change from electron to hole in the negative gate-voltage range. The relevant band diagram is illustrated in the inset of Fig. 4b. In this band diagram, when the negative Vds is applied to the MoTe2 side, the current flow of hole carriers from SnS2 to MoTe2 would be very low because the SnS2 channel is depleted. In addition, the majority hole carriers flowing from MoTe2 to SnS2 upon application of positive Vds to MoTe2 face a large potential barrier caused by the large valence band offset (Supplementary Fig. 5). Consequently, both forward and backward currents are very low for Vg < −20 V, suppressing the rectification behavior. In this manner, this device can be viewed as a series connection of MoTe2/SnS2 heterojunction and two resistors of MoTe2 and SnS2, whose resistance values can be adjusted by controlling Vg. Note the MoTe2/SnS2 heterojunction has a lateral configuration. The simple equivalent circuit is shown in the inset of Fig. 4c. The transfer curves of a heterojunction device fabricated with a thin MoTe2 flake was also investigated in Supplementary Fig. 6, indicating the gate dependence was determined by the series connection of the two materials. Based on this analysis, we deduce that the MoTe2/SnS2 heterojunction gives rise to the rectification property only when the resistance values of the parts other than the junction is low enough for the heterojunction to dominate the current flow in the series connection.

Ternary inverter

Finally, we applied the MoTe2/SnS2 heterojunction to a multivalued logic device by fabricating a ternary inverter with only two n-type FETs. As illustrated in Fig. 5a, the driving voltage (Vdd) and input voltage (Vin) were applied to the electrode of the MoTe2 side (E2) and Si back-gate electrode. The end of the electrode of the SnS2 side (E4) was grounded, and then the output voltage (Vout) on the other electrode in contact with the SnS2 side (E3) was measured.

This is the integration of MoTe2/SnS2 heterojunction with SnS2 FETs, which their resistance value can be fully controlled by regulating Vin. Figure 5b depicts the equivalent circuit of the ternary inverter. The plot of Vin vs. Vout in Fig. 5c clearly shows three distinct output voltage regions in the range of 0–60 V at Vdd = 1 V, corresponding to the three logical states. The output voltage (Vout) is a voltage drop across SnS2 FET determined by the fraction of the driving voltages (VDD) that depends on the resistance ratio between SnS2 and heterojunction channel. The input voltage-dependent resistance values of both channels are exhibited in Supplementary Fig. 7. For Vin < 10 V, the SnS2 FET has a smaller current path than that of the MoTe2/SnS2 heterojunction channel because of the MoTe2 channel part, leading to “logic 1.” For 15 < Vin < 25 V, SnS2 and heterojunction channels have a constant resistance ratio as shown in Supplementary Fig. 7. This implies the voltage drop across the SnS2 channel is sustained in this region, resulting in the output “logic 1/2”7,58. At high Vin, SnS2 FET is completely turned on, whereas the current passing through the heterojunction is restricted by the large potential barrier, and thus the state “logic 0” is achieved.

Discussion

We fabricated a multilayer n-MoTe2/n-SnS2 isotype heterojunction device. Raman analysis confirmed the electron transfer from MoTe2 to SnS2 side based on Anderson’s rule. The output characteristics of the MoTe2/SnS2 heterojunction clearly exhibited the rectification behavior. From a systematic analysis based on a numerical solution of Poisson’s equation and Simmons approximation, we ascribed the rectification to a potential barrier exceeding ~1 eV, attributed to the large band offsets between the two materials. Unlike the conventional p–n heterostructure operating by diffusion of minority carrier, we confirmed the transport is determined by the majority carriers via thermionic emission and tunneling process through the potential barrier. Furthermore, we certified the switchable rectification characteristic by varying the gate voltage. While the rectification was turned off for the negative Vg, it was enhanced for the positive Vg up to a maximum rectification ratio of ~103 at a modest source–drain voltage of 1 V in ambient environment. This value is comparable with that of other p–n unisotype vdW heterostructure devices reported by previous studies. Finally, we demonstrate the working of the new device by fabricating a ternary inverter using the MoTe2/SnS2 FET and a SnS2 channel transistor. This is the first experimental study reporting a systematical analysis for a MoTe2/SnS2 heterojunction device. The results can be used as guidelines for the optimization and designing of a variety of heterojunction-based customizable electronic or photonic devices.

Methods

Device fabrication

MoTe2/SnS2 heterostructure devices were fabricated by the dry transfer method. MoTe2 and SnS2 were mechanically exfoliated from their commercial bulk forms (HQ graphene, America) using blue tape on PDMS (Gel-Pak, PF-X4–17 mil.) and a highly n-doped (As doped) substrate with a 300-nm-thick SiO2 layer, respectively. The MoTe2 flakes on PDMS were aligned by a transfer system-mounted microscope, and then transferred on to SnS2 flakes. The electrodes were patterned by the electron-beam lithography process, and Ti/Au (20/50 nm) metals were deposited by a thermal evaporator at high vacuum pressure (~106 Torr).

Device characterization

AFM measurement was performed in ambient environment with tapping mode, to confirm the thickness of the flakes. Raman spectroscopic measurements (Renishaw) were carried out at room temperature using a 514-nm laser as the excitation source with <2 mW power. We used a Keithley-4200SCS parameter analyzer to measure the electrical properties of the MoTe2/SnS2 heterojunction device and the ternary inverter.

Data availability

The authors confirm that the data supporting the findings of this study are available within the article. Related additional data are available on reasonable request from the authors.

References

Geim, A. K. & Grigorieva, I. V. Van der Waals heterostructures. Nature 499, 419–425 (2013).

Novoselov, K. S. et al. 2D materials and van der Waals heterostructures. Science 353, aac9439 (2016).

Wang, X. & Xia, F. Stacked 2D materials shed light. Nat. Mater. 14, 264 (2015).

Liu, Y. et al. Van der Waals integration before and beyond two-dimensional materials. Nature 567, 323–333 (2019).

Qiu, X. & Ji, W. Illuminating interlayer interactions. Nat. Mater. 17, 211–213 (2018).

Jariwala, D. et al. Mixed-dimensional van der Waals heterostructures. Nat. Mater. 16, 170–181 (2017).

Nourbakhsh, A. et al. Transport properties of a MoS2/WSe2 heterojunction transistor and its potential for application. Nano Lett. 16, 1359–1366 (2016).

Zhou, X. et al. Tunneling diode based on WSe2/SnS2 heterostructure incorporating high detectivity and responsivity. Adv. Mater. 30, 1703286 (2018).

Wang, Y. et al. Light induced double ‘on’ state anti-ambipolar behavior and self-driven photoswitching in p-WSe2/n-SnS2 heterostructures. 2D Mater. 4, 025097 (2017).

Huang, M. et al. Multifunctional high-performance van der Waals heterostructures. Nat. Nanotechnol. 12, 1148–1154 (2017).

Shim, J. et al. Phosphorene/rhenium disulfide heterojunction-based negative differential resistance device for multi-valued logic. Nat. Commun. 7, 13413 (2016).

Yan, R. et al. Esaki diodes in van der Waals heterojunctions with broken-gap energy band alignment. Nano Lett. 15, 5791–5798 (2015).

Dastgeer, G. et al. Temperature-dependent and gate-tunable rectification in a black phosphorus/WS2 van der Waals heterojunction diode. ACS Appl. Mater. Interfaces 10, 13150–13157 (2018).

Li, D. et al. Gate-controlled BP–WSe2 heterojunction diode for logic rectifiers and logic optoelectronics. Small 13, 1603726 (2017).

Srivastava, P. K. et al. Van der Waals broken-gap p–n heterojunction tunnel diode based on black phosphorus and rhenium disulfide. ACS Appl. Mater. Interfaces 11, 8266–8275 (2019).

Lee, C.-H. et al. Atomically thin p–n junctions with van der Waals heterointerfaces. Nat. Nanotechnol. 9, 676–681 (2014).

Doan, M.-H. et al. Charge transport in MoS2/WSe2 van der Waals heterostructure with tunable inversion layer. ACS Nano 11, 3832–3840 (2017).

Roy, T. et al. Dual-gated MoS2/WSe2 van der Waals tunnel diodes and transistors. ACS Nano 9, 2071–2079 (2015).

Furchi, M. M. et al. Photovoltaic effect in an electrically tunable van der Waals heterojunction. Nano Lett. 14, 4785–4791 (2014).

Yang, T. et al. Van der Waals epitaxial growth and optoelectronics of large-scale WSe2/SnS2 vertical bilayer p–n junctions. Nat. Commun. 8, 1906 (2017).

Park, C. et al. Photovoltaic effect in a few-layer ReS2/WSe2 heterostructure. Nanoscale 10, 20306–20312 (2018).

Wang, G. et al. Interlayer coupling induced infrared response in WS2/MoS2 heterostructures enhanced by surface plasmon resonance. Adv. Funct. Mater. 28, 1800339 (2018).

Lee, J. et al. Thermodynamically stable synthesis of large-scale and highly crystalline transition metal dichalcogenide monolayers and their unipolar n–n heterojunction devices. Adv. Mater. 29, 1702206 (2017).

Castellanos-Gomez, A. et al. Deterministic transfer of two-dimensional materials by all-dry viscoelastic stamping. 2D Mater. 1, 011002 (2014).

Lokhande, C. D. A chemical method for tin disulphide thin film deposition. J. Phys. D 23, 1703–1705 (1990).

Gong, C. et al. Band alignment of two-dimensional transition metal dichalcogenides: Application in tunnel field effect transistors. Appl. Phys. Lett. 103, 053513 (2013).

Guo, Y. & Robertson, J. Band engineering in transition metal dichalcogenides: stacked versus lateral heterostructures. Appl. Phys. Lett. 108, 233104 (2016).

Schlaf, R. et al. Band lineup of layered semiconductor heterointerfaces prepared by van der Waals epitaxy: charge transfer correction term for the electron affinity rule. J. Appl. Phys. 85, 2732–2753 (1999).

Huo, N. et al. Novel and enhanced optoelectronic performances of multilayer MoS2–WS2 heterostructure transistors. Adv. Funct. Mater. 24, 7025–7031 (2014).

Li, C. et al. WSe2/MoS2 and MoTe2/SnSe2 van der Waals heterostructure transistors with different band alignment. Nanotechnology 28, 415201 (2017).

Lezama, I. G. et al. Indirect-to-direct band gap crossover in few-layer MoTe2. Nano Lett. 15, 2336–2342 (2015).

Ruppert, C. et al. Optical properties and band gap of single- and few-layer MoTe2 crystals. Nano Lett. 14, 6231–6236 (2014).

Yamamoto, M. et al. Strong enhancement of raman scattering from a bulk-inactive vibrational mode in few-layer MoTe2. ACS Nano 8, 3895–3903 (2014).

Smith, A. J. et al. Raman scattering studies of SnS2 and SnSe2. J. Phys. C 10, 1321–1323 (1977).

Huang, Y. et al. Tin disulfide—an emerging layered metal dichalcogenide semiconductor: materials properties and device characteristics. ACS Nano 8, 10743–10755 (2014).

Chakraborty, B. et al. Symmetry-dependent phonon renormalization in monolayer MoS2 transistor. Phys. Rev. B 85, 161403 (2012).

Song, H. S. et al. High-performance top-gated monolayer SnS2 field-effect transistors and their integrated logic circuits. Nanoscale 5, 9666–9670 (2013).

Nakaharai, S. et al. Carrier polarity control in α-MoTe2 Schottky junctions based on weak fermi-level pinning. ACS Appl. Mater. Interfaces 8, 14732–14739 (2016).

Chen, J. et al. Contact engineering of molybdenum ditelluride field effect transistors through rapid thermal annealing. ACS Appl. Mater. Interfaces 9, 30107–30114 (2017).

Lin, Y.-F. et al. Ambipolar MoTe2 transistors and their applications in logic circuits. Adv. Mater. 26, 3263–3269 (2014).

Nakaharai, S. et al. Electrostatically reversible polarity of ambipolar α-MoTe2 transistors. ACS Nano 9, 5976–5983 (2015).

Rani, A. et al. Tuning the polarity of MoTe2 FETs by varying the channel thickness for gas-sensing applications. Sensors 19, 2551 (2019).

Pudasaini, P. R. et al. High-performance multilayer WSe2 field-effect transistors with carrier type control. Nano Res. 11, 722–730 (2018).

Ye, G. et al. Synthesis of large-scale atomic-layer SnS2 through chemical vapor deposition. Nano Res. 10, 2386–2394 (2017).

Yuan, H. T. et al. Liquid-gated electric-double-layer transistor on layered metal dichalcogenide, SnS2. Appl. Phys. Lett. 98, 012102 (2011).

Zschieschang, U. et al. Tin disulfide (SnS2) thin-film field-effect transistors. In Proc. 72nd Device Research Conference 267–268 (2014).

Zhang, Y. et al. Thickness considerations of two-dimensional layered semiconductors for transistor applications. Sci. Rep. 6, 29615 (2016).

De, D. et al. High on/off ratio field effect transistors based on exfoliated crystalline SnS2 nano-membranes. Nanotechnology 24, 025202 (2012).

Ortiz-Conde, A. et al. A review of recent MOSFET threshold voltage extraction methods. Microelectron. Reliab. 42, 583–596 (2002).

Wang, F. et al. Tunable GaTe-MoS2 van der Waals p–n junctions with novel optoelectronic performance. Nano Lett. 15, 7558–7566 (2015).

Sun, B.-Z. et al. Anisotropic thermoelectric properties of layered compounds in SnX2 (X = S, Se): a promising thermoelectric material. Phys. Chem. Chem. Phys. 17, 29844–29853 (2015).

Li, J. et al. Thickness-controlled electronic structure and thermoelectric performance of ultrathin SnS2 nanosheets. Sci. Rep. 7, 8914 (2017).

Das, S. et al. Toward low-power electronics: tunneling phenomena in transition metal dichalcogenides. ACS Nano 8, 1681–1689 (2014).

Sze, S. M. & NG, K. K. In Physics of Semiconductor Devices 77–133 (John Wiley & Sons, Inc., 2006).

Takeda, N. & Parkinson, B. A. Adsorption morphology, light absorption, and sensitization yields for squaraine dyes on SnS2 surfaces. JACS 125, 5559–5571 (2003).

Laturia, A. et al. Dielectric properties of hexagonal boron nitride and transition metal dichalcogenides: from monolayer to bulk. npj 2D Mater. Appl. 2, 6 (2018).

Simmons, J. G. Generalized Formula for the electric tunnel effect between similar electrodes separated by a thin insulating film. J. Appl. Phys. 34, 1793–1803 (1963).

Duong, N. T. et al. Modulating the functions of MoS2/MoTe2 van der Waals heterostructure via thickness variation. ACS Nano 13, 4478–4485 (2019).

Acknowledgements

This research was supported by the Nano Material Technology Development Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Science, ICT and Future Planning (NRF-2016M3A7B4900147 and NRF-2017R1A2B4007219). We would like to thank Dr Suyong Jung, Korea Research Institute of Standards and Science, for carefully reading the manuscript and helpful discussions.

Author information

Authors and Affiliations

Contributions

S.Kim performed the device fabrication and electrical characterization; S.Kim, C.-W.Lee, and S.Seo were involved in writing the manuscript; H.Du, T.Kim, S.Shin, H.Song, H.Kim, and D.Kang contributed to the scientific discussions. All authors have given approval to the final version of the manuscript.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Kim, S., Du, H., Kim, T. et al. Gate-switchable rectification in isotype van der Waals heterostructure of multilayer MoTe2/SnS2 with large band offsets. npj 2D Mater Appl 4, 15 (2020). https://doi.org/10.1038/s41699-020-0149-8

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41699-020-0149-8

This article is cited by

-

Miniaturized spectrometer with intrinsic long-term image memory

Nature Communications (2024)

-

A reconfigurable binary/ternary logic conversion-in-memory based on drain-aligned floating-gate heterojunction transistors

Nature Communications (2023)

-

Controllable potential barrier for multiple negative-differential-transconductance and its application to multi-valued logic computing

npj 2D Materials and Applications (2021)