Abstract

In this paper, a Class-E inverter and a thermal compensation circuit for wireless power transmission in biomedical implants are designed, simulated, and fabricated. In the analysis of the Class-E inverter, the voltage-dependent non-linearities of Cds, Cgd, and RON as well as temperature-dependent non-linearity of RON of the transistor are considered simultaneously. Close agreement of theoretical, simulated and experimental results confirmed the validity of the proposed approach in taking into account these nonlinear effects. The paper investigated the effect of temperature variations on the characteristics of the inverter. Since both the output power and efficiency decrease with increasing temperature, a compensation circuit is proposed to keep them constant within a wide temperature range to enable its application as a reliable power source for medical implants in harsh environments. Simulations were performed and the results confirmed that the compensator enables significant improvements by maintaining the power and efficiency almost constant (8.46 ± 0.14 W and 90.4 ± 0.2%) within the temperature range of − 60 to 100 °C. Measurements performed at 25 °C and 80 °C with and without the compensation circuit were in good agreement with the theoretical and simulation results. The obtained measured output power and efficiency at 25 °C are equal to 7.42 W and 89.9%.

Similar content being viewed by others

Introduction

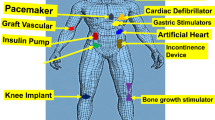

Today, wireless technology plays an important role in the development of Health informatics. The convenience of patients under treatment, diagnosing the disease with the least side effects and the accuracy of test results are important concerns of scientists in this field. Wireless technology is used in biomedical sensors, artificial organs, and remote monitoring of the patients’ condition1,2,3. Figure 1 shows some examples of implants that integrate wireless technology for therapeutic applications. The illustrated implants work at different frequencies and are designed according to their function in different parts of the body4,5,6,7,8,9. Class-E Power Amplifier (PA) or inverter is the main component of WPT11. In design and analysis of Class-E power amplifier, the effects of input voltage waveforms12, duty ratio13, and parasitic linear and nonlinear capacitances14 have been discussed. Also, comprehensive research projects have been conducted to improve the characteristics of PAs in different classes for biomedical industry15 One of the important issues in the manufacture of biomedical implants is availability of reliable wireless power supplies and this paper is focused on this matter specially with regards to operation in harsh environments.

Some of the therapeutic implants which are supplied with WPT10.

The Class-E inverter has been welcomed due to its high efficiency, circuit simplicity, and small size and therefore it has been the main element of practical circuits such as biomedical implants16,17, inverters18,19,20, WPT systems21,22,23,24,25,26, oscillators23,28, and light communication transmitter29. Due to these broad applications, a variety of techniques have also been used to design and optimize class E inverters for different WPT applications. As an example, in Inductive Power Transfer (IPT) WPT, due to the displacement of the transmitter and receiver coils, as well as the displacement of the alignment between them, the values of the output resistance and inductance of the inverter changes. To avoid the effects of these changes, frequency modulated control24 and load independent class E inverter25,26 have been presented. The load-independent Class-E inverter achieves constant output voltage, ZVS, and fixed phase shift between the driving signal and the output voltage at any load resistance without any control24.

Another approach is to merge Class-E PAs with other classes, which results in mixed-mode PAs such as class DEM30 and class EM/Fn31. The robust and efficient wireless power transfer and the floating bulk technique achieved by using a power-efficient Class-E power amplifier have also been investigated32,33. In one research34, a study of the temperature effect on the MOSFET biased in the subthreshold region is presented. In another work two Class-E PAs with transmission line (TL), lumped elements35, and a Class-E PA with two cascaded transistors36 have been studied. The design of the Class-E PA considering the non-linear drain-source and linear gate-drain capacitances have also been studied12,37,38 In a recent work39, the temperature effect on the Class-E PA has been investigated where the effect of temperature has been compensated by DC gate-source voltage, despite its undesired influence on the transistor bias region, also only the drain-source resistor of the transistor is considered as a linear element and the effect of nonlinear capacitors is completely neglected. This is while, the need to consider these capacitors in the analysis has already been thoroughly proven40. Studying the effects of temperature changes on WPT transmitters while also considering the simultaneous effect of nonlinear capacitances and on-state resistance is a missing challenge of research, which is the main aim of this paper. We have then proceeded to propose a compensation circuit which does not adversely affect the bias of the MOSFET and aims to exceed the performance of the previous approach. This is done with the objective of maximizing the operating temperature range of the inverter as defined by its power level and efficiency. In this paper, it is shown that the output power and efficiency decrease with increasing temperature. The change in temperature also changes the drain-source voltage, which it may exceed the maximum withstand voltage of the transistor and as a result, the transistor can be damaged in the circuit. This condition would be worse if we had a MOSFET with a large RON. In medical implants, providing a reliable power source is one of the designers’ issues. A compensation circuit is proposed in this paper to keep output power and efficiency constant within a wide temperature range in order to enable its application as a reliable power source for medical implants in harsh environments.

This paper is categorized as follows; discussion of the design block diagram and design specification, presentation of the proposed analysis for the Class E Inverter considering the voltage-dependent non-linearities of Cds, Cgd, and RON as well as temperature-dependent non-linearity of RON of the transistor and investigating temperature variation effects, introducing the class-E inverter with the proposed thermal compensation circuit, and finally presentation and discussion of the measurement results and a conclusion.

Proposed methodology

Design block diagram and design specification

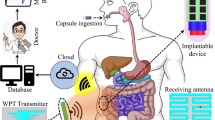

The proposed block diagram of a WPT used in biomedical implants is shown in Fig. 2. Due to the high efficiency of switching inverters, they are used in the wireless power supply system in the power transmitter part. In wireless implants, the transmitter induces the required power into the implant circuit with an inductive couple that transmits the power through the coils. In the receiver part of the body, a rectifier and a regulator are utilized to create the required power. The presented circuit of a WPT is shown in Fig. 3.

Class E inverter is used in many WPTs due to its simplicity of structure and high efficiency at the operating frequency. The important elements of the Class E inverter circuit are the MOSFET, which acts as a switch, a resonant circuit at the desired operating frequency, and an external capacitor. In a class E inverter, the transistor is biased in the cut-off region, with a sufficient gate driving amplitude to make it to operate alternatively between the cut-off and the linear region. Nonlinear elements of the transistor include the drain-source capacitor and the gate-drain capacitor, which have a non-linear voltage dependence. The drain-source on-resistor has a nonlinear temperature dependence. The output series resonance circuit followed by a phase difference inductor is designed to produce the output signal at the operating frequency with the lowest power loss. A choke is used between the drain of the transistor and the power supply to create low-ripple DC current and isolate ac signals from DC. In most designs, the transistor is considered an ideal switch, which is modeled as a short circuit in the ON-state and as an open circuit in the OFF-state, but in the ON-state, the transistor has a resistance that depends on the transistor parameters.

Transistor temperature dependency

All passive and active elements have internal resistance, considering this resistance in the design process causes theoretical and fabricated responses to be in good agreement with each other. The most dependence of the transistor on the temperature is related to this resistance, which is tied to the drain-source. In switching inverters, the transistor operates in the triode region in the ON-state and operates in the cut-off region in the OFF-state. The relation of the transistor current in the triode region is defined as41:

In the deep triode region, VDS ≤ 2(VGS − Vth), it can be obtained:

The relationship of the ON-state drain-source resistance can be presented as41:

where iT is the transistor current, VGS is the gate-source voltage, VDS is the drain-source voltage, \({\mu }_{n}\) is mobility, Vth is the threshold voltage, and \({C}_{ox}\) is the oxide capacitor per unit area. W is 100u and L is 100u for IRF510. In (3), \({\mu }_{n}\) and Vth are temperature-dependent parameters that lead to the temperature dependence of ON-state drain-source resistance. Firstly, the effect of temperature variations on Vth is investigated. Vth is obtained as42:

where \(q\) is the electron charge and \({N}_{a}\) is the acceptor doping density, \({\varepsilon }_{si}\) is the dielectric constant of the semiconductor and \(2{\mathrm{\varnothing }}_{F}\) is twice the bulk potential. Where for the P substrate, the bulk potential is obtained as follows42:

\({V}_{T}\) is the thermal voltage and \({n}_{i}\) is the intrinsic carrier density. The \({V}_{T}\) and \({n}_{i}\) depend on temperature and are described as follows42:

NC is the Effective density of states in the conduction band, Nv is the Effective density of states in the valence band, Eg is the semiconductor Energy bandgap, and K is Boltzmann’s constant. The energy bandgap of a semiconductor is related to temperature and is expressed as follows42:

By substituting (6), (7), and (8) in (5), the \({\mathrm{\varnothing }}_{F}\) is obtained by42:

Mobility is the second parameter that depends on the temperature. Mobility decreases with increasing temperature with coefficient T-2.4 and is defined as below42:

where \({\mu }_{n0}\) varies based on the amount of silicon impurity. By substituting all the parameters in (3), the equation of resistance based on temperature is obtained as:

The constant parameters for silicon in (11) are defined as below42:

Temperature changes are caused by changes in ambient temperature and junction temperature, which causes power dissipation in the transistor. It can be seen from (11), RON is a function of Vth and mobility, which decreases with increasing temperature.

Figure 4 shows the dependence of Vth and mobility as a function of temperature for IRF510 transistor. The change of RON based on temperature variations when VGS = 5.2 V is shown in Fig. 5. RON has an increasing trend with increasing temperature.

Presented analysis for the class E inverter

Figure 6 shows the equivalent of the simple class E (SCE) inverter circuit which consists of:

-

The transistor considers the nonlinear capacitances (Cds and Cgd).

-

RON is the resistance of the transistor ON-state.

-

Cext is the fixed external capacitor.

-

LRFC is used as the ac blocker.

-

RRFC is the resistance of the LRFC.

-

L acts as a phase difference inductor.

-

RL0 is the resistance of L + Lr.

-

Cr + Lr just passes the first harmonic and blocks other harmonics.

The element values and specifications of the class E inverter in − 60 °C ~ 180 °C temperature ranges are obtained by numerical solution according to ZVS and ZVDS conditions including nonlinear RON, Cds, and Cgd. Figure 7 shows a block diagram of the design process and methodology that is used. In the design, the input parameters are operating frequency, peak output current Im, external capacitances Cext, and chock inductance LRFC, which are known. Also, the output parameters are L, Lr, Cr, RL, VDD, efficiency, output power, Vd−ON, Vd−ON , and IDC, which are obtained according to the temperature variation.

A square pulse with a duty cycle of 50% is applied to the gate transistor. When the transistor is OFF (0˂Ɵ < π), the gate-source voltage is zero, leaving only the nonlinear capacitors of the transistor. The following relationship can be presented:

In (12), \({V}_{d-OFF}\) is the drain-source voltage in the OFF-state, IDC is the DC current injected from VDD, and because of LRFC operation, this current has a very little ripple. Imn is the nth harmonic peak of the output current. The nonlinearity of transistor capacitors (Cds and Cgd) are considered for more accuracy in the design and their relationship is as follows38:

where \({V}_{d-OFF}\) is the drain-to-source transistor voltage in the OFF-state, Vbi1 and Vbi2 are the built-in voltage of the pn junction, Cj01 is the drain-to-source capacitance at \({V}_{d-OFF}\), Cj02 is the gate-to-drain capacitance at \({V}_{d-OFF}\), m1 is the grading coefficient for the nonlinear drain-to-source capacitance and m2 is the grading coefficient for the nonlinear gate-to-drain capacitance. By substituting (13) in (12) and integrating from θ we have:

The parameters of IRF510 MOSFET are listed in Table 143.

When the transistor is ON (π˂Ɵ < 2π), the gate-source voltage is high, RON impact is added to the structure. iT is the current passing through the transistor. This current is considered zero when the transistor is in OFF-state due to the high resistance of the transistor. By utilizing the current division in the drain node, the below equation can be obtained:

where ‘Z’ and ‘II’ mean impedance and parallel, respectively.

The ZVS and ZVDS conditions are applied to the transistor voltage to avoid overlap between voltage and current at π. These conditions create minimal consumption in the design. Applying these conditions to Eqs. (12) and (15):

The output resonance circuit of the transistor is designed with high-quality factor, so only the first harmonic is considered in the design and the rest of the harmonics are ignored. Therefore, according to (16) and (17), the amount of phase difference required to meet the conditions of ZVS and ZVDS is equal to \({\varphi }_{n}=\) − 0.567 rad. Figure 8 shows the drain voltage at 25 °C as well as determines the drain voltage peak value in the ON and OFF states. It can be seen that the drain voltage in the ON-state has a significant value, but it has been neglected in previous class E inverter designs.

The drain voltage in the ON-state according to RON can be obtained as below:

where \({i}_{T}\) is the current of the transistor in ON-state, which is presented in (15).

The voltage of the DC power supply according to the drain voltage can be obtained. 0 to π indicates the OFF-state, and π to 2π indicates the ON-state of the transistor, VDD can be calculated as follows:

To have a constant output current with ZVS and ZVDS conditions versus temperature changes, the circuit parameters like VDD, Lr, Cr, L, and RL must be changed. According to (19), VDD versus temperature changes is obtained and shown in Fig. 9.

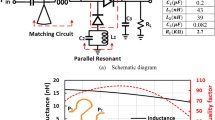

As temperature increases, VDD should be increased to compensate for the drop in drain voltage in the OFF-state. Figure 10a shows the output resonant circuit. At the fundamental harmonic, which is considered to be 1 MHz, the resonant circuit is simplified, as shown in Fig. 10a. By employing KVL in the circuit:

In (20), \({V}_{d-OFF}H1\) is the first harmonic of Vd−OFF, VL is the phase difference inductor voltage, VO is the output voltage, and \({V}_{{R}_{L0}}\) is the RL0 voltage. By substituting the first harmonic of the out current in (20):

By solving (21) we have:

where \(\left|{V}_{d-OFF}H1\right|\) and \({\varphi }_{{V}_{d-OFF}H1}\) are the absolute value and phase of the fundamental harmonic of Vd−OFF, respectively. By solving (22) and (23) the value of output resistance and phase difference inductor are calculated as follows:

By solving (24) and (25), the optimal load resistance values (RL) and L that are suitable for creating ZVS and ZVDS conditions at different temperatures are calculated. The calculated RL and L are shown in Fig. 10b. As the temperature increases, the value of these parameters should be reduced to achieve the conditions of ZVS and ZVDS and have a constant output current.

In this design, the quality factor in the resonant circuit is considered to be 10, so that the output current waveform is close to a pure sinusoid. According to (26) and (27), the value of the inductor and capacitor of the series resonant are obtained based on the temperature, as shown in Fig. 11. As the temperature increases, to access the ZVS and ZVDS conditions and constant output current, the inductor should be decreased and the capacitor should be increased.

In a real Class E inverter, the efficiency is not 100% due to the presence of parasitic elements. The efficiency can be calculated by dividing the power delivered to the load over the total power consumption in the circuit as follows:

The total power consumption of the circuit is expressed as:

where \({P}_{{R}_{RFC}}\),\({P}_{{R}_{L0}}\), and \({P}_{{R}_{on}}\) are the dissipated power in RRFC, RL0, and RON, respectively. The efficiency is calculated as:

In order to have a constant output current and maintain the nominal conditions, the values of the circuit elements change according to the ambient and junction temperature. Figure 12 shows, that the efficiency and output power versus temperature variations when the values of the circuit elements change. As can be seen, the output power and the efficiency in the presented SCE inverter decrease with rising temperature.

Presented design for the class E inverter at 25 °C

In this section, a class E inverter at 25 °C is designed and the elements of the circuit are obtained according to previous analysis as listed in Table 2, then the effect of temperature variations on the specifications are investigated as shown by a block diagram in Fig. 13.

By solving (14) and (15), the dependence of the drain voltage is calculated according to temperature and Ɵ, as shown in Fig. 14a,b. In the ON-state, taking into account the rising RON, the drain voltage rises, as shown in Fig. 14a. Due to the constant VDD, as the temperature increases, the total area under the drain voltage curve from 0 to 2π should also remain constant. Therefore, to compensate for the increase in the drain voltage in the ON state, the peak value of drain voltage in the OFF-state is reduced as shown in Fig. 14b. The drain current is considered zero in the range of 0 to π and the transistor resistance is assumed infinite. One of the important factors in the design is to consider the maximum voltage that can be tolerated for the transistor according to its model. If the drain voltage changes caused by temperature fluctuations are not controlled, they can damage the transistor.

A change in temperature causes a change in resistance, and then the amount of output current and efficiency and output power change. Figure 15a,b show the reduction of these parameters based on temperature increment. As it is clear, these changes are significant and should be considered in the design.

Design of the presented thermal compensation unit

In this section, a thermal compensation unit (TCU) is provided for the SCE. According to (11), RON has inversely related to the gate-source voltage applied to the transistor. RON versus VGS and temperature is shown in Fig. 16.

To achieve a constant RON with temperature variations, the amount of VGS in the circuit should be changed. To generate VGS according to temperature changes, a compensation circuit is designed, as shown in Fig. 17.

The TCU includes:

-

An OP-AMP is formed in a non-inverter state.

-

Three constant resistors (Rfix1, Rfix2, Rfix3).

-

RT is a 10KΩ negative temperature control (NTC) resistor with 3435 part-number.

-

VPDC has applied voltage to the op-amp.

-

TC4427 is used as the driver.

RT has a nonlinear decreasing behavior with increasing temperature. The model of this resistor is 3435. The resistance value versus temperature is shown in Fig. 18.

The block diagram of the TCU design process is shown in Fig. 19. The values of VGS versus temperature that creates constant RON are obtained from Fig. 16 in MATLAB and plotted in Fig. 20 with a continuous-black-line. The elements value of the compensation circuit as shown in Fig. 17 are calculated in MATLAB with respect to VGS and RT (3435 NTC resistor) values. Figure 20 shows the created VGS versus temperature with different values of Rfix1, Rfix2, and Rfix3.

VDCdriver determines the value of the pulse signal applied to the gate and is calculated from the following equation:

Figure 20 shows, VGS versus temperature for constant RON in a continuous black line. The elements of the compensation circuit, which are Rfix1, Rfix2, Rfix3, and VPDC should be adjusted so that the compensation circuit produces this pattern for VGS. The blue dashed lines with Rfix1 = 2.8, Rfix2 = 7, and Rfix3 = 3 KΩ provide the best agreement between − 60 and 100 °C. The SCE is investigated with and without the compensation circuit. When the TCU is in the design, it prevents the effect of temperature variations on the inverter parameters. The changes in efficiency and output power based on the temperature in the SCE and the TCCE inverter are shown in Fig. 21, simultaneously. The compensator enables significant improvements by maintaining the simulation power and efficiency almost constant (8.46 ± 0.14 W and 90.4 ± 0.2%) within the temperature range of − 60 to 100 °C. From the comparison of efficiency and output power in the TCCE inverter and the SCE inverter, it is becoming clear that the TCU provides constant output power and efficiency versus temperature variations, which is very desirable for telecommunication circuits.

Performance analysis result

The presented TCCE inverter is fabricated and shown in Fig. 22. The input signal has a duty ratio of 0.5. The operation frequency is 1 MHz. As can be seen, the negative temperature control resistor is placed next to the IRF510 to sense the ambient and junction temperature simultaneously. The TCU can be isolated from the SCE inverter with a jumper so that it can be tested with and without the compensation circuit. The load resistance is made by ceramic resistors with a tolerance of 10 watts. All capacitors used are able to withstand high power.

Comparison of theoretical, simulation, and experimental results

Table 3 shows the values of the elements used in the TCCE inverter. Table 4 shows the theoretical, simulated, and measured results of the presented TCCE inverter at 25 °C. As can be seen, the simulation and measurement results are very close to the theoretical results. This precision in the results is due to the consideration of all the parasitic elements of the transistor as well as the resistance of the transistor in the ON-state. Figure 23a shows the output driver voltage applied to the gate of the transistor. The value of VGS is 5.2 V. The driver output capacitor causes a slow slope in the measured VGS. In Fig. 23b, the drain voltage for simulation, theoretical and fabrication results are shown. The output current is considered pure sinusoidal in the theoretical analysis, but in the measurement and simulation results, the output current has more harmonics, which increases the drain voltage level for simulation and measurement.

Figure 24c shows the output voltage. The difference between the results is due to the increase of the resistance in the resonance path in the manufacturing process and considering the output current as a pure sinusoid. Figure 24a shows the applied gate voltage for the SCE inverter at 25 °C and 80 °C and also for the TCCE inverter at 80 °C. At a temperature of 80 °C, the value of gate voltage increases due to the operation of the compensating circuit and prevents changes in the drain voltage. As can be seen in Fig. 24b, the drain voltage in the SCE inverter at 25 °C is almost the same as the drain voltage in the TCCE inverter at 80 °C. Due to the operation of the TCU, the peak of the drain voltage remains constant. Figure 24c shows that at 80 °C in the SCE inverter, the output voltage is affected by the decreased in the drain voltage. Table 5 compares the values of the parameters measured with SCE at 25 °C and 80 °C and the parameters measured with TCCE at 80 °C. In the SCE inverter at 80 °C, the output power is 2.7% lower than the SCE inverter at 25 °C. By applying the TCCE inverter, this difference reaches 0.13%, which is very favorable. In the SCE inverter, the efficiency at 25 °C is 89.9%, which decreases to 88.1% when the temperature increases to 80 °C. As the temperature increases in the TCCE inverter, the efficiency remains constant. It is concluded that the TCU has a very positive effect on the inverter parameters. Important parameters of the class E inverter for comparing the TCCE inverter with other references are presented in Table 6. The output power and efficiency of the proposed circuit are 7.42 W and 89.9%. Output power and efficiency are in conflict with each other, in some references, despite high efficiency, they have provided lower output power. Cgd and Cds have a non-linear relationship with the drain-source voltage and their consideration confirms the theoretical answer. None of the references consider these capacitances as nonlinear elements in design process, nor do all references consider the nonlinear effects of RON.

Conclusion

In this paper, a class E inverter with a thermal compensation unit has been presented. In the WPT, the class E inverter is more affected by temperature due to the presence of the active elements. The temperature variation effect has been considered in the class E inverter design including nonlinear Cds, Cgd and RON and it has been compensated to achieve a reliable power source in the biomedical implant. It has been found that temperature changes significantly affect inverter characteristics such as output power and efficiency. Therefore, a compensation circuit was proposed and added to the simple class E inverter. Simulations were performed and the results confirmed that the compensator enables significant improvements by maintaining almost constant power and efficiency (8.46 ± 0.14 W and 90.4 ± 0.2%) in the temperature range of − 60 to 100 °C. The thermal compensation class E inverter has been fabricated, and the simulation and theoretical results are validated with the measured results. The tested circuit results are in good and acceptable agreement with the simulation results. The obtained output power is 7.42 W with an efficiency of 89.9% at 25 °C.

Data availability

The calculated results during the current study are available from the corresponding author on reasonable request.

References

Tian, X. et al. Wireless body sensor networks based on metamaterial textiles. Nat. Electron. 2, 243–251 (2019).

Li, R. et al. A flexible and physically transient electrochemical sensor for real-time wireless nitric oxide monitoring. Nat. Commun. 11, 1–11 (2020).

Tomioka, Y. et al. Wearable, wireless, multi-sensor device for monitoring tissue circulation after free-tissue transplantation: a multicentre clinical trial. Sci. Rep. 12, 1–14 (2022).

Sawigun, C., Ngamkham, W., & Serdijn, W. A. An ultra low-power peak-instant detector for a peak picking cochlear implant processor. In 2010 Biomedical Circuits and Systems Conference (BioCAS), 222–225 (2010).

Meng, M., & Kiani, M. Self-image-guided ultrasonic wireless power transmission to millimeter-sized biomedical implants. In 2019 41st Annual International Conference of the IEEE Engineering in Medicine and Biology Society (EMBC), 364–367 (2019).

Iqbal, A., Sura, P. R., Al-Hasan, M., Mabrouk, I. B. & Denidni, T. A. Wireless power transfer system for deep-implanted biomedical devices. Sci. Rep. 12, 1–13 (2022).

Elliott, M., Momin, S., Fiddes, B., Farooqi, F. & Sohaib, S. A. Pacemaker and defibrillator implantation and programming in patients with deep brain stimulation. Arrhythmia Electrophysiol. Rev. 8, 138 (2019).

Cagnan, H., Denison, T., McIntyre, C. & Brown, P. Emerging technologies for improved deep brain stimulation. Nat. Biotechnol. 37, 1024–1033 (2019).

Yan, B. et al. Battery-free implantable insulin micropump operating at transcutaneously radio frequency-transmittable power. Med. Devices Sens. 2, e10055 (2019).

Massachusetts Institute of Technology http://groups.csail.mit.edu/netmit/IMDShield (2011).

Grebennikov, A., Sokal, N. O. & Franco, M. J. Switchmode RF and Microwave Power Amplifiers (Academic Press, 2012).

Hayati, M., Lotfi, A., Kazimierczuk, M. K. & Sekiya, H. Generalized design considerations and analysis of class-E amplifier for sinusoidal and square input voltage waveforms. IEEE Trans. Ind. Electron. 62, 211–220 (2014).

Hayati, M., Lotfi, A., Kazimierczuk, M. K. & Sekiya, H. Modeling and analysis of class-E amplifier with a shunt inductor at sub-nominal operation for any duty ratio. IEEE Trans. Circuits Syst. I Regul. Pap. 61, 987–1000 (2013).

Hayati, M., Lotfi, A., Kazimierczuk, M. K. & Sekiya, H. Analysis and design of class-E power amplifier with MOSFET parasitic linear and nonlinear capacitances at any duty ratio. IEEE Trans. Power Electron. 28, 5222–5232 (2013).

Sridhar, N., Senthilpari, C., Mardeni, R., Yong, W. H. & Nandhakumar, T. A low power, highly efficient, linear, enhanced wideband Class-J mode power amplifier for 5G applications. Sci. Rep. 12, 1–18 (2022).

Yang, Z., Liu, W. & Basham, E. Inductor modeling in wireless links for implantable electronics. IEEE Trans. Magn. 43, 3851–3860 (2007).

Felic, G. K., Ng, D. & Skafidas, E. Investigation of frequency-dependent effects in inductive coils for implantable electronics. IEEE Trans. Magn. 49, 1353–1360 (2012).

Sensui, T. & Koizumi, H. Load-independent class E zero-voltage-switching parallel resonant inverter. IEEE Trans. Power Electron. 36, 12805–12818 (2021).

Shigeno, A. & Koizumi, H. Voltage-source parallel resonant class E inverter. IEEE Trans. Power Electron. 34, 9768–9778 (2019).

Fu, M., Yin, H., Liu, M., Wang, Y. & Ma, C. A 6.78 MHz multiple-receiver wireless power transfer system with constant output voltage and optimum efficiency. IEEE Trans. Power Electron. 33, 5330–5340 (2017).

Huang, X. et al. Synchronous push–pull class E rectifiers with load-independent operation for megahertz wireless power transfer. IEEE Trans. Power Electron. 36, 6351–6363 (2021).

Dou, Y., Huang, X., Ouyang, Z. & Andersen, M. A. Modelling and compensation design of class-E rectifier for near-resistive impedance in high-frequency power conversion. IEEE Trans. Power Electron. 36, 8812–8823 (2021).

He, L. & Guo, D. A clamped and harmonic injected class-E converter with ZVS and reduced voltage stress over wide range of distance in WPT system. IEEE Trans. Power Electron. 36, 6339–6350 (2020).

Komiyama, Y. et al. Frequency-modulation controlled load-independent class-E inverter. IEEE Access 9, 144600–144613 (2021).

Aldhaher, S., Yates, D. C. & Mitcheson, P. D. Load-independent class E/EF inverters and rectifiers for MHz-switching applications. IEEE Trans. Power Electron. 33, 8270–8287 (2018).

Luo, W., Ogi, Y., Ebihara, F., Wei, X. & Sekiya, H. Design of load-independent class-E inverter with MOSFET gate-to-drain and drain-to-source parasitic capacitances. Nonlinear Theory Appl. IEICE 11, 267–277 (2020).

Ahmadi, M. M. & Pezeshkpour, S. A self-starting class-E power oscillator with an inverting gate driver. IEEE Trans. Ind. Electron. 67, 8344–8354 (2019).

Ahmadi, M. M. & Salehi-Sirzar, M. A self-tuned class-E power oscillator. IEEE Trans. Power Electron. 34, 4434–4449 (2018).

Aller, D. G., Lamar, D. G., Miaja, P. F., Rodriguez, J. & Sebastian, J. Taking advantage of the sum of the light in outphasing technique for visible light communication transmitter. IEEE J. Emerg. Select. Top. Power Electron. 9, 138–145 (2020).

Inaba, T. & Koizumi, H. Class-DE M tuned power amplifier. IEEE Trans. Power Electron. 34, 403–415 (2018).

Mugisho, M. S., Thian, M., Piacibello, A., Camarchia, V. & Quay, R. Harmonic-injection class-E M/F n power amplifier with finite DC-feed inductance and isolation circuit. IEEE Trans. Microw. Theory Tech. 69, 3319–3334 (2021).

Assawaworrarit, S. & Fan, S. Robust and efficient wireless power transfer using a switch-mode implementation of a nonlinear parity–time symmetric circuit. Nat. Electron. 3, 273–279 (2020).

Dehqan, A. R., Toofan, S. & Lotfi, H. Floating bulk cascode class-E power amplifier. IEEE Trans. Circuits Syst. II Express Briefs 66, 537–541 (2018).

Wang, H. & Mercier, P. P. Near-zero-power temperature sensing via tunneling currents through complementary metal-oxide-semiconductor transistors. Sci. Rep. 7, 1–7 (2017).

Mugisho, M. S. et al. Generalized class-E power amplifier with shunt capacitance and shunt filter. IEEE Trans. Microw. Theory Tech. 67, 3464–3474 (2019).

Peña-Eguiluz, R. et al. Stacked class-E amplifier. IEEE Trans. Industr. Electron. 67, 8292–8301 (2019).

Surakitbovorn, K. N. & Rivas-Davila, J. M. On the optimization of a class-E power amplifier with GaN HEMTs at megahertz operation. IEEE Trans. Power Electron. 35, 4009–4023 (2019).

Lotfi, A. et al. Subnominal operation of class-E nonlinear shunt capacitance power amplifier at any duty ratio and grading coefficient. IEEE Trans. Ind. Electron. 65, 7878–7887 (2018).

Liu, C. & Shi, C. J. R. Design of the class-E power amplifier considering the temperature effect of the transistor on-resistance for sensor applications. IEEE Trans. Circuits Syst. II Express Briefs 68, 1705–1709 (2021).

Hayati, M., Abbasi, H., Kazimierczuk, M. K. & Sekiya, H. Analysis and study of the duty ratio effects on the class-E M power amplifier including MOSFET nonlinear gate-to-drain and drain-to-source capacitances. IEEE Trans. Power Electron. 33, 10550–10562 (2018).

Razavi, B. Design of Analog Cmos Integrated Circuits 7th edn. (McGraw-Hill, 2001).

Sze, S. M., Li, Y. & Ng, K. K. Physics of Semiconductor Devices (Wiley, 2021).

Vishay Intertechnology. www.vishay.com (2017).

Author information

Authors and Affiliations

Contributions

Design, analysis, investigation, and writing—original draft preparation M.K., suggestions, writing—review and editing: M.H. and H.A. All authors discussed the results and contributed to the final manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher's note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Khodadoost, M., Hayati, M. & Abbasi, H. Investigation of temperature variations on a Class-E inverter and proposing a compensation circuit to prevent harmful effects on biomedical implants. Sci Rep 13, 4017 (2023). https://doi.org/10.1038/s41598-023-31076-y

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-023-31076-y

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.