Abstract

In this paper, a capacitorless one-transistor dynamic random access memory (1 T-DRAM) based on a polycrystalline silicon (poly-Si) metal-oxide-semiconductor field-effect transistor with the asymmetric dual-gate (ADG) structure is designed and analyzed through a technology computer-aided design (TCAD) simulation. A poly-Si thin film was used within the device due to its low fabrication cost and feasibility in high-density three-dimensional (3-D) memory arrays. We studied the transfer characteristics and memory performances of the single-layer ADG 1 T-DRAMs and the 3-D stacked ADG 1 T-DRAMs and analyze the reliability depending on the location and the number of grain-boundaries (GBs). The relative standard deviation (RSD) of the threshold voltages (Vth) is depending on the location and the number of GBs. The RSDs of the single-layer ADG 1 T-DRAM and the 3-D stacked ADG 1 T-DRAM are 1.58% and 0.68%, respectively. The RSDs of retention time representing the memory performances are 54.7% and 41%, respectively. As a result of the 3-D stacked structure, the averaging effect occurs, which greatly aids in improving the reliability of the memory performances as well as the transfer characteristics of 1 T-DRAMs depending on the influence of GBs. The proposed 3-D stacked ADG 1 T-DRAM helps implement a high-reliability single-cell memory device.

Similar content being viewed by others

Introduction

Recently, due to the complexity of the conventional DRAM’s capacitor fabrication, the 1T-DRAM has attracted great attention as a replacement for the conventional DRAM. The 1T-DRAM operates without the use of external capacitors, instead of relying on the floating body effect. The 1T-DRAM has the advantages of being easy to manufacture and having excellent logic device compatibility1,2,3,4,5. However, the smaller sizes of these devices tend to limit their retention characteristics due to the stronger electric field between the body and the source/drain junction. The stronger electric fields accelerate the recombination/generation process of the excess holes, resulting in shorter RTs in scaling of the 1T-DRAM. Various groups have conducted many studies, and the ADG structure can be a great solution to overcome the RT of 1T-DRAMs5. In addition, the 3-D stacked 1T-DRAM is made of polycrystalline silicon (poly-Si), so high-density 3-D memory arrays can be feasible. Based on their superior advantages in terms of the integrated fabrication technology, the poly-Si-based transistors have been widely used in 3-D memory technology in the past6,7,8.

The thermal budget was one of the significant challenges in implementing 3-D stacked transistors. The second layer and beyond of the device require high-temperature processing, which can threaten existing metallization materials or cause dopant diffusion in the lower layers of the device9. These difficulties in the fabrication can be overcome by using excimer laser crystallization (ELC) and it can implement the 3-D stacked 1T-DRAM. Fabrication steps are outlined in references 4,10 and 11. The key fabrication steps for the proposed 3-D stacked 1T-DRAM are summarized in more detail in the Supplementary Information. ELC can solve the thermal budget issues, however, it cannot solve the random distribution of the GBs. Because they randomly varied depending on the laser irradiation energy density10. The GBs are important in transistors made of poly-Si because they directly affect the transistor’s electrical performances. An analysis of the effect of GBs in a single channel was carried out in reference 5. However, a statistical study on the effect of the GBs in 3-D stacked ADG 1T-DRAM based on MOSFET with poly-Si has not been reported yet.

In this work, the 3-D stacked ADG poly-Si MOSFET based 1T-DRAM with various average grain sizes (Gsizes) cells are investigated. A TCAD simulation is used to demonstrate the superior reliability of 3-D stacked ADG 1T-DRAM to the effects of the GBs11. The proposed 3-D stacked ADG 1T-DRAM cells’ transfer characteristics, as well as memory performances, are analyzed and compared with the single-layer ADG 1T-DRAM. It has been proven to have excellent reliability to the effects of GBs.

Simulation methodology

Device structure

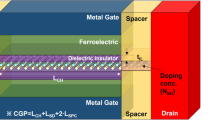

Figure 1 shows the cross-sectional view of the 3-D stacked ADG poly-Si-MOSFET-based 1T-DRAM cell with an ADG structure to implement high-reliability GB-independent electrical characteristics and memory performances. The main gates are used to control the conventional MOSFET operation during the read period and the tunneling operation during the program period. The control gates located below the channel regions are used to operate the tunneling phenomenon during program operation. Additionally, they sweep out holes during the erase period, helping to maintain the stored holes during the hold operation. Each layer’s main gates share a common electrode, likewise the control gates share a common electrode. We refer to the operating bias of 1T-DRAM in reference 5. The work-functions of the main gate (WFMG) and the control gate (WFCG) are 4.85 eV and 5.3 eV, respectively. The main gate length (Lmg), the control gate length (Lcg), the underlap length (Lunderlap), the body thicknesses (Tbody), the gate dielectric (HfO2) thicknesses (Tox) and spacer thicknesses (Tspacer) are 70 nm, 50 nm, 10 nm, 12 nm, 3 nm, and 30 nm, respectively. The spacer is made of silicon oxide (SiO2), a low-κ material that reduces parasitic capacitance and leakage components between channels. The doping concentrations of the source, body, and drain regions are 1 × 1020 cm−3 (n-type), 1 × 1018 cm−3 (p-type) and 1 × 1020 cm−3 (n-type), respectively. The values of the work-functions of the gates, the length of the gate, the underlap length, etc., refer to reference 5. Variations of underlap length in the proposed device are summarized in more detail in the Supplementary Information. Table 1 summarized the device parameters for each of the proposed devices.

Physical models for accurate simulation works

The GB model, where a single GB exists in the channel region, is widely used. Also, most previous studies assumed that the Gsize in the channel of poly-Si MOSFETs is the same when there are two or more than two GB in the channel region5,12,13,14. In this paper, we supposed Gsize and its standard deviation (SD) are assumed to be 30 nm and 10 nm, respectively, to reflect realistic experimental results of Gsize having a Gaussian distribution as shown in reference 13. Figure 2 shows the histogram of the Gsize generated as assumed. As a result, TCAD simulations realistically represent variations in the size and the location of the GB in the transistor. The Box-Muller method, which generates a Gaussian distribution from uniformly distributed numbers, is the method for generating random GBs in the channel region. Furthermore, the trap distribution in the GBs of the poly-Si was calibrated using the experimental data in references 4 and 5 and assuming that all GBs contain the same amount of traps. The calibration results, including the GB trap distribution, are summarized in more detail in the Supplementary Information.

As shown in Fig. 2, the Gsize distribution consists of groups (A), (B), (C), (D), and (E) depending on its size. As shown in Table 2, the Gsizes are set up as 5 nm to 15 nm, 15 nm to 25 nm, 25 nm to 35 nm, 35 nm to 45 nm and 45 nm to 55 nm, and the portions of each of the sizes are 6.2%, 24.5%, 38.6%, 24.5%, and 6.2%, respectively. If the Gaussian distributions for the Gsizes are applied to each channel of the proposed 3-D stacked ADG 1T-DRAMs, the number of samples becomes too large. Therefore, in this paper, the three channels of the proposed 3-D stacked 1T-DRAMs independently have one Gsize among groups (A), (B), (C), (D), and (E) as shown in Table 3. For example, the group (ABC) in Table 3 means that the Gsize of the channel in the bottom layer is 10 nm, the middle layer has a Gsize of 20 nm and the top layer has a Gsize of 30 nm. The probability multiplied by the 4000 samples and rounded-off is the value of the number of samples. To examine the electrical characteristics and the memory performances, the Sentaurus TCAD simulation tool is used11. To maximize the accuracy of the simulation works, various physical models are considered, including the Fermi–Dirac statistical model, the Shockley-Read-Hall (SRH) recombination model, the nonlocal band-to-band tunneling model, the trap-assisted-tunneling model, the Auger recombination model, the doping-dependent and field-dependent mobility models, the bandgap narrowing model, and the quantum confinement model11. The mobility models which are used for simulation are summarized in more detail in the Supplementary Information.

Results and discussion

When the GB is located in the channel of the n-type MOSFET, the acceptor-like trap forms an energy barrier as electrons are trapped as shown in Fig. 3. The GB-induced potential barrier directly suppresses the current flow. As a result, it causes the Vth to rises5. Thus, it is shown that the variations in conduction characteristics are caused mainly by the number of GB located in the channel3. The Vth is defined by the constant-current method, which determines the Vth as the Vg value for Id = 10−7 A/µm15.

Statistical analysis of transfer characteristics

Figure 4 shows the drain current (Id) versus the gate voltage (Vg) curves of 4000 samples each single-layer ADG 1T-DRAMs and 3-D stacked ADG 1T-DRAMs with a Gsize of 30 nm under drain voltage = 0.5 V. Histograms of (a) the Vths (b) the subthreshold swings (SSs) (c) the on-currents (Ions), and (d) the off-currents (Ioffs) obtained from simulations for 4000 samples with the proposed GB model, for proposed single-layer ADG 1T-DRAMs and 3-D stacked ADG 1T-DRAMs are extracted from Fig. 4.

In Fig. 5a, the averages of the extracted Vths of the single-layer ADG 1T-DRAMs and the 3-D stacked ADG 1T-DRAMs are 1.002 V and 0.956 V, respectively. The SDs for the Vths are 15.9 mV and 6.5 mV, respectively. The RSDs are 1.58% and 0.68%, respectively. The RSD is the SD divided by the mean and multiplied by 100. In other words, a large RSD indicates that the SD is large in comparison to the mean and it has a large dispersion. Since the RSD is expressed as a percentage, it is a coefficient of merit that can be used to compare the spread of data sets with different measurement units. The Id are higher in the 3-D stacked ADG 1T-DRAMs due to the multi-layer structure, resulting in lower Vth. The RSDs of the Vths are 1.58% for the single-layer ADG 1T-DRAMs and 0.68% for the 3-D stacked ADG 1T-DRAMs. Since the single-layer ADG 1T-DRAMs’ RSD is about two times than the 3-D stacked ADG 1T-DRAMs’ RSD. Therefore, the 3-D structure has better reliability for the Vth variations due to the GBs.

Figure 5b shows the distribution of SSs. The average of SSs of the single-layer ADG 1T-DRAMs and the 3-D stacked ADG 1T-DRAMs have similar values, 115.0 mv/dec and 114.2 mv/dec, respectively. The single-layer ADG 1T-DRAMs have the SSs ranging from 110 mv/dec to 140 mv/dec, as can be seen. However, in the case of the 3-D stacked ADG 1T-DRAMs, it can be seen that most of the SSs are distributed between 112 mv/dec and 117 mv/dec, respectively. This phenomenon occurs because they have 3-D stacked structures that complement the fluctuation in current characteristics caused by the GBs. This phenomenon is called the averaging effect. In the case of the single-layer ADG 1T-DRAM, it is significantly affected by the GBs of a channel region. However, even if one layer is significantly affected by the GBs, the performance variation in current and memory due to the GBs is small in the 3-D stacked ADG 1T-DRAM because the performance degradation is shared with the other two layers. This is a similar phenomenon that the decrease in work-function variation as the metal gate granularity decreases16,17. Consequently, the RSD of SSs of the 3-D stacked ADG 1T-DRAMs is more than 9 times smaller than the single-layer ADG 1T-DRAMs, which can be said to be excellent in the reliability of transfer characteristics.

Figure 5c shows the distribution of the Ions. The average Ions of the single-layer ADG 1T-DRAMs and the 3-D stacked ADG 1T-DRAMs are 1.87 × 10-4 A/µm and 5.74 × 10−4 A/µm, respectively. The average Ions of the 3-D stacked ADG 1T-DRAMs, which are multi-channel structures, is about three times larger than the single-layer ADG 1T-DRAMs’. A low Ion is a long-standing weakness of poly-Si transistors, but it can be solved using a 3-D stacked structure. In addition, the SDs of Ions are 1.45 × 10−5 A/µm and 2.49 × 10−5 A/µm, respectively. In respect to the SD, the dispersion of the 3-D stacked ADG 1T-DRAMs seems larger, but in the case of the RSD, which reflects the real dispersion, the single-layer ADG 1T-DRAMs’ RSD is 7.75% and the 3-D stacked ADG 1T-DRAMs’ RSD is 4.34%, respectively. In conclusion, the 3-D stacked 1T-DRAM has excellent transfer characteristics, such as a larger Ion and more minor variation.

Figure 5d shows the distribution of the Ioff s. The average of Ioff s of the 3-D stacked ADG 1T-DRAMs is 1.6 times larger than the single-layer ADG 1T-DRAMs’. The Ioff s are the parameter with the most pronounced averaging effect. As aforementioned, thanks to the averaging effect, the RSD of the Ioff of the 3-D stacked ADG 1T-DRAM is 3% owing to the 3-D structure. On the other hand, the transfer curves of the single-layer ADG 1T-DRAMs show large variances, which results in the RSD of 130.7% as shown in Fig. 4. The figure of merits (FOMs) of the transfer characteristics and the memory performances are summarized in Table 4.

Statistical analysis of memory performances

Histograms of (a) the sensing margins (SMs) and (b) RTs from 4000 samples simulations with the proposed GB model, for the proposed single-layer ADG 1T-DRAMs and the 3-D stacked ADG 1T-DRAMs, are shown in Fig. 6a. In Fig. 6a, the averages of SMs of the single-layer ADG 1T-DRAM and the 3-D stacked ADG 1T-DRAM are 5.72 µA/µm and 17.4 µA/µm, the SDs are 1.44 µA/µm and 2.54 µA/µm and the RSDs are 25.2% and 14.6%, respectively. The SD of the SMs in the 3-D stacked ADG 1T-DRAMs is larger than the single-layers’, but the RSD is the opposite. Additionally, in the case of the single-layer ADG 1T-DRAMs, depending on the distribution of the GBs, some samples get poor SMs that are less than 3 µA/µm which is the reference value18. On the other hand, all samples of the 3-D stacked ADG 1T-DRAMs have superior to the SM of 3 µA/µm.

As shown in Fig. 6b, the average RTs of the single-layer ADG 1T-DRAMs and the 3-D stacked ADG 1T-DRAMs are 212 ms and 200 ms, respectively, showing similar values. However, as shown in Fig. 6b, the SDs of RTs are 116 ms and 82 ms and the RSDs of RTs are 54.7% and 41%. This indicates that the 3-D stacked ADG 1T-DRAMs have smaller RT deviations. In addition, in the single-layer ADG 1T-DRAMs, 6.2% of the samples are insufficient for RT to meet 64 ms which is the memory criteria of the international roadmap for devices and systems (IRDS) (>64 ms)19. However, in the case of the 3-D stacked ADG 1T-DRAMs, all the samples have longer RT than 60 ms as shown in Fig. 6b. In terms of the RT, the 3-D stacked ADG 1T-DRAMs are more reliable than the single-layer ADG 1T-DRAMs. The FOM of the memory performances is summarized in Table 4.

Consequently, when considering the SDs, and the RSDs of transfer characteristics and memory performances, the 3-D stacked ADG 1T-DRAMs showed excellent performance not only transfer characteristics but also memory performances. Moreover, they also show high immunity to the impact of GBs, especially on retention in the part of memory performances. Thus, our proposed 3-D stacked ADG 1T-DRAMs can be excellent devices in terms of reliability. Performance comparison of the conventional 1T-1C DRAMs, the capacitorless DRAMs, and the 3-D stacked asymmetric dual-gate 1T-DRAM are summarized in more detail in the Supplementary Information.

Conclusion

In this work, a novel structure of 1 T-DRAM based on a poly-Si MOSFET transistor with the 3-D stacked ADG structure is designed and analyzed through a TCAD simulation. The optimized geometric parameters of the single-layer ADG 1 T-DRAM are used to perform the 3-D stacked ADG 1 T-DRAM5. The single-layer ADG 1 T-DRAM and the 3-D stacked ADG 1 T-DRAM are studied for their transfer characteristics and memory performances. Also, we statistically analyzed the reliability depending on the location and number of GBs. In the case of the single-layer ADG 1 T-DRAM, the RSDs of the Vth, SS, Ion, and Ioff are 1.58%, 5.18%, 7.75%, and 130.7%, respectively. On the other hand, the RSDs of the Vth, Ion, Ioff, and SS of the 3-D stacked ADG 1 T-DRAMs are 0.68%, 0.55%, 4.43%, and 3.0%, respectively. The RSDs of the SM and RT of the single-layer ADG 1 T-DRAM are 25.2% and 54.7%, respectively. On the other hand, the RSDs of the SM and RT of the 3-D stacked ADG 1 T-DRAMs are 14.6% and 41%, respectively. The averaging effect occurs thanks to the 3-D stacked structure, which greatly helps to improve the reliability of the memory performances as well as the transfer characteristics of the 3-D stacked ADG 1 T-DRAM depending on the influence of GBs. As a result, when compared to the single-layer ADG 1 T-DRAM, the proposed novel 3-D stacked ADG 1 T-DRAM can implement a high reliable single memory cell.

Data availability

The datasets used and/or analysed during the current study available from the corresponding author on reasonable request.

References

Okhonin, S., Nagoga, M., Sallese, J.-M. & Fazan, P. A capacitor-less 1t-dram cell. IEEE Electron Device Lett. 23, 85–87 (2002).

Hu, C., King, T.-J. & Hu, C. A capacitorless double-gate dram cell. IEEE Electron Device Lett. 23, 345–347 (2002).

Yoon, Y. J., Seo, J. H., Cho, S., Lee, J.-H. & Kang, I. M. A polycrystalline-silicon dual-gate mosfet-based 1t-dram using grain boundary-induced variable resistance. Appl. Phys. Lett. 114, 183503 (2019).

Seo, J. H. et al. Fabrication and characterization of a thin-body poly-si 1t dram with charge-trap effect. IEEE Electron Device Lett. 40, 566–569 (2019).

Lee, S. H. et al. Polycrystalline-silicon-mosfet-based capacitorless dram with grain boundaries and its performances. IEEE Access 9, 50281–50290 (2021).

Shirota, R. 3d-nand flash memory and technology. In Advances in Non-Volatile Memory and Storage Technology, 283–319 (Elsevier, 2019).

Chou, Y.-L. et al. Investigation of vth distribution tails of ground-select-line cells and edge dummy cells in a 3-d nand flash memory. IEEE Trans. Electron Devices 68, 2260–2264 (2021).

Lin, P.-J., Chiu, Y.-Y., Chen, F. & Shirota, R. Simulation study of the instability induced by the variation of grain boundary width and trap density in gate-all-around polysilicon transistor. IEEE Trans. Electron Devices 68, 1969–1974 (2021).

Chan, V. W., Chan, P. C. & Chan, M. Three-dimensional cmos soi integrated circuit using high-temperature metal-induced lateral crystallization. IEEE Trans. Electron Devices 48, 1394–1399 (2001).

Lee, I.-C. et al. High-performance vertically stacked bottom-gate and top-gate polycrystalline silicon thin-film transistors for three-dimensional integrated circuits. Solid-State Electron. 77, 26–30 (2012).

Guide, S. D. U. & Version, L. Synopsys tcad sentaurus. San Jose, CA, USA (2016).

Cho, M. S. et al. Simulation of capacitorless dynamic random access memory based on junctionless finfets using grain boundary of polycrystalline silicon. Appl. Phys. A 126, 1–10 (2020).

Kim, H. et al. Analysis of the sensing margin of silicon and poly-si 1t-dram. Micromachines 11, 228 (2020).

Yoo, S., Sun, W. & Shin, H. Analysis of a lateral grain boundary for reducing performance variations in poly-si 1t-dram. Micromachines 11, 952 (2020).

Saadat, A., Van De Put, M. L., Edwards, H. & Vandenberghe, W. G. Channel length optimization for planar ldmos field-effect transistors for low-voltage power applications. IEEE J. Electron Devices Soc. 8, 711–715 (2020).

Nam, H., Lee, Y., Park, J.-D. & Shin, C. Study of work-function variation in high-k/metal-gate gate-all-around nanowire mosfet. IEEE Trans. Electron Devices 63, 3338–3341 (2016).

Dadgour, H. F., Endo, K., De, V. K. & Banerjee, K. Grain-orientation induced work function variation in nanoscale metal-gate transistors—part i: Modeling, analysis, and experimental validation. IEEE Trans. Electron Devices 57, 2504–2514 (2010).

Jeong, H. et al. A new capacitorless 1t dram cell: Surrounding gate mosfet with vertical channel (sgvc cell). IEEE Trans. Nanotechnol. 6, 352–357 (2007).

IRDS. International roadmap for devices and systems, 2020 edition. IEEE (2020).

Acknowledgements

This work was supported by the National Research Foundation of Korea (NRF) grant funded by the Korea government (MSIT) (No. NRF-2020R1A2C1005087). This study was supported by the BK21 FOUR project funded by the Ministry of Education, Korea (4199990113966). This research was supported by Basic Science Research Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Education (NRF-2021R1A6A3A13039927). This research was supported by National R&D Program through the National Research Foundation of Korea (NRF) funded by Ministry of Science and ICT (2021M3F3A2A03017764). This research was supported by National R&D Program through the National Research Foundation of Korea (NRF) funded by Ministry of Science and ICT (2022M3I7A1078936). This investigation was financially supported by Semiconductor Industry Collaborative Project between Kyungpook National University and Samsung Electronics Co. Ltd. The EDA tool was supported by the IC Design Education Center (IDEC), Korea.

Author information

Authors and Affiliations

Contributions

S.H.L. conceived the idea and verified and investigated. J.P., S.R.M., G.U.K., J.J., J.-H.B., S.-H.L., and I.M.K. provided the experimental advices and supports. S.H.L. analyzed the results and wrote the manuscript and I.M.K. supervised the research. All authors edited the manuscript and have given approval to the final version of the manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher's note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Lee, S.H., Park, J., Min, S.R. et al. 3-D stacked polycrystalline-silicon-MOSFET-based capacitorless DRAM with superior immunity to grain-boundary’s influence. Sci Rep 12, 14455 (2022). https://doi.org/10.1038/s41598-022-18682-y

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-022-18682-y

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.