Abstract

In this study, we applied ferroelectrics to the gate stack of Field Effect Transistors (FETs) with a 2D transition-metal dichalcogenide (TMDC) channel, actively researching for sub-2nm technology node implementation. Subsequently, we analyzed the circuit characteristics of Logic-in-Memory (LiM) operation and utilized LiM features after applying ferroelectrics to achieve a single-device configuration. Based on well-calibrated simulations, we performed compact modeling in a circuit simulator to depict the temperature-dependent electrical characteristics of ferroelectric FETs with a double gate structure and 2D channel (DG 2D-FeFET) in sub-2nm dimensions. Through this, we have confirmed that the 2D FeFET-based LiM technology, designed for the 2 nm technology node, exhibits superior characteristics in terms of delay, power/energy consumption, and circuit area under all temperature conditions, compared to the conventional CMOS technology based on 2D FETs. This verification serves as proof of the future technological potential of 2D-FeFET in extremely scaled-down technology nodes.

Similar content being viewed by others

Introduction

CMOS technology scaling down continues, and recent advancements indicate a sustained miniaturization trend with the introduction of 2D transition-metal dichalcogenide (TMDC) materials in the sub-2nm technology node1. This trend is anticipated due to the thin TMDC’s inherent advantages, such as immunity to short-channel effects, minimal interface trap formation owing to van der Waals bonds and the absence of dangling bonds, excellent mobility characteristics, and superior interface properties compared to silicon2. Numerous studies on large-area integration processes and contact technology development for mass production have been reported to facilitate practical implementation3,4,5. Recently, both the IMEC and IRDS CMOS logic technology roadmaps, along with various papers, have provided insights into the feasibility of TMDC in scaled technology nodes6,7,8.

Meanwhile, with the increasing prominence of applied research in Artificial Intelligence (AI) and the Internet of Things (IoT), the development of memory-intensive application devices has become crucial. The Von Neumann architecture consists of a Central Processing Unit (CPU), memory unit, and input/output device. The CPU and memory unit exchange data through the system bus. The traditional Von Neumann architecture faces challenges in meeting the requirements of memory-intensive application devices due to the increasing speed difference in data processing between the fast-evolving CPU and memory unit, as well as the unnecessary power consumption escalation in the bus, leading to the Von Neumann bottleneck problem9,10,11,12,13. To address such issues, Logic-in-Memory (LiM) research, placing the memory unit and computing core in close proximity, has recently gained momentum14,15. LiM can be categorized based on the proximity of the memory unit and computing unit16. In-memory computing, processing in memory, and coarse-grain LiM involve Non-Volatile (NV) memory arranged in a matrix array close to the computing core. Fine-grain LiM integrates NV memory tightly with the logic unit within the computing circuit. Recently, circuits such as Full Adder (FA) and Ternary Content Addressable Memory (TCAM) using fine-grain LiM transistors have been reported to exhibit improved circuit area and energy consumption characteristics compared to conventional CMOS FETs17,18,19,20. FeFETs utilizing the strong ferroelectricity manifested when doping impurities like silicon and zirconium into the hafnium oxide (HfO2) primarily used as the FET gate insulator have gained significant attention as fine-grain LiM devices. This is attributed to their high compatibility with existing silicon-based integration processes. Global Foundries has demonstrated FeFET devices based on 28 nm CMOS and 22 nm FDSOI CMOS as baseline FETs, along with various application circuit results21.

In previous studies, the resistance and capacitance of FETs with a channel made of TMDC material were segmented, and an analysis based on the number of channel layers was conducted2,22. However, there is currently a lack of preliminary research on analyzing the characteristics of devices by depositing a strong ferroelectric on 2D materials. In this paper, we modeled a DG FeFET by integrating one of the representative 2D TMDC materials, tungsten disulfide (WS2) channel, with a ferroelectric, 10 nm HSO, in the sub-2nm dimension. We predicted the device and LiM circuit characteristics. To achieve this, we extracted the electrical characteristics of DG FeFET devices by utilizing the electrical properties of WS2 channels in DG FETs, calculated through atomic-level simulations by Ahmed et al., and the electrical characteristics of a Silicon-doped hafnium oxide (HSO) ferroelectric layer reported from fabrication devices by Zhou et al.23,24. We developed a compact model that describes this process and benchmarked power, performance, and area characteristics in various FA and TCAM circuits through circuit simulations. In this process, we utilized a conventional FA circuit (1 type) and TCAM circuit (1 type) composed of DG FETs, along with two previously published FeFET-based FA circuits (2 types) and TCAM circuits (2 types), and a proposed FeFET-based FA circuit (1 type) in this paper. Additionally, we confirmed robust circuit operation characteristics in nano-scale nodes through circuit characteristic verification under various temperature conditions. The structure of this paper is as follows. In Chapter 2, we describe the circuit modeling method, including the electrical characteristics of the WS2 channel and ferroelectric layer used in the DG FeFET in this study, as well as temperature variations. In Chapter 3, we perform various FA and TCAM circuit analyses and benchmarks using the developed DG FeFET’s LiM characteristics. In particular, we evaluate circuit layout area comparisons and circuit robustness against temperature changes. Finally, in Chapter 4, we conclude the paper.

Results

Characteristics of DG FeFET with Mono-layer WS2 channel and HSO ferroelectric layer

Figure 1 illustrates the double-gate structure of a 2D-channel FeFET with a monolayer WS2 channel and a ferroelectric gate dielectrics, as employed in this study. Table 1 outlines the key dimensions applied to the 2D-channel DG FeFET structure in this research, corresponding to sub-2nm technology node dimensions6. In particular, the thickness of the ferroelectrics and dielectrics is an important factor in the capacitance characteristics (CFE/CDE) that determine the memory window (MW). 2D-based FET exhibits advantages over Si-based FET in scaling aspects in the latest processes, and it is evident that they possess superior electrical properties.

Compact modeling of DG FeFET with Mono-layer WS2 channel and HSO ferroelectric layer

In Fig. 2, the summarized development process of the overall FeFET compact model library for LiM-based FA and TCAM circuit analysis is presented. As illustrated in Fig. 3, this study employs a Metal-Ferroelectric-Insulator-Semiconductor (MFIS) structure FeFET, integrating a ferroelectric layer into the gate stack of the baseline FET. This integration was implemented using the principles of charge conservation and voltage distribution. In the absence of metal between ferroelectrics and dielectrics, polarization coupling occurs, exerting a slight influence on the overall capacitance28. However, simulations were conducted under the assumption of no polarization coupling, representing an ideal scenario. The self-developed ferroelectric device model, implemented in Verilog-A, was integrated into the baseline FET using BSIM-IMG, and the electrical characteristics of the FeFET were simulated through Synopsys’ HSPICE. The obtained Memory Window with applied Program/Erase voltage, as determined by the FeFET compact model, is summarized in Fig. 3.

The development process of a compact model library for WS2-based FET used as the baseline FET is included in Fig. 2, steps ①-②. In this study, results based on atomic-level simulations of WS2 channels, deemed capable of achieving sub-2nm, were utilized. To verify the dynamic characteristics of the circuit, I–V calibration was performed using the standard TCAD software, Synopsys’s Sentaurus, followed by obtaining C-V characteristics. We used the thin layer model for WS2-FET with a channel thickness of a few nm, and included the IALmob model to describe surface and phonon scattering, and the RCS model to represent remote coulomb scattering due to high-k gate dielectrics. Subsequently, for the development of the compact model library for the baseline WS2-based FET, the industry-standard BSIM-IMG model suitable for Double Gate structures was utilized. Initially, process variables were utilized as the physical parameter set. Parameters describing electrical characteristics such as I–V and C–V at T = 300 K were extracted, while temperature-dependent parameters were extracted at T = 230 K and 360 K, respectively. In the circuit simulation netlist, the parasitic components (CEXT, CMOL, REXT, RMOL) and contact resistance (RCNT) that affect the AC condition were connected to the WS2-FET as shown in Fig. 4a to analyze the circuit performance. CEXT, CMOL, REXT, RMOL were obtained from well-calibrated TCAD, while RCNT at 300 K (=1.8 kΩ µm) was reported from experiments23, and RCNT at 230 K and 360 K were taken from experimental values in Li et al.29. Subsequently, Ioff targeting and centering were performed to meet the speed and power requirements of the sub-2nm node as per the industry standards.

a Capacitances, resistances of MOL, extension, b Intrinsic I–V graph of DG WS2-FET with high voltage (Vds = 0.6 V), low voltage (Vds = 0.01 V), c Intrinsic gate capacitance graph for high voltage22.

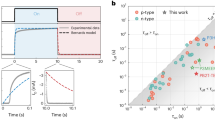

Figure 5 outlines the compact modeling process for the characteristics of the 10 nm ferroelectric layer used in this study. It is a model that integrates formulas that describe various physical characteristics of various ferroelectric layers in previous studies into one24,30,31. Verilog-A is used to output polarization characteristics by voltage values input over time on circuit simulators. Equation 1 describes the saturation loop of the ferroelectric layer, while Equations 2–4 depict the nonsaturated inner loop characteristics. Equation 5 represents the total polarization, including dielectric characteristics, and Equations 6–8 describe the temperature-dependent properties. In Equation 6, the temperature dependence of the saturation polarization of the ferroelectric capacitor is assumed to follow Landau theory. Equation 7 utilizes the approximation that the coercive field is considered when the temperature (T) is lower than the Curie’s temperature (TC)32. Energy barriers (WB), Boltzmann constant (kb), potential barrier height (v0), Critical Volume (V*), Saturation Polarization (PS), and the time taken for Coercive field (EC) is a known constant, so EC and Temperature (T) have a linear relationship. This led to the derivation of Equation 8 applying Vopsaroiu’s model. Here, VC represents the coercive voltage, P↑↓(VEFF) represents the polarization of the inner loop, εFE is the dielectric constant of the ferroelectric material, ε0 is the dielectric constant in the air, tFE is the thickness of the ferroelectric material, PS,0K is the saturation polarization at absolute temperature, TEFF is the absolute temperature of the current state, and A and B are fitting parameters for determining EC concerning temperature. The model, considering hysteresis and the non-saturated inner loop, is expressed using Verilog-A following the flowchart in Fig. 5 to implement ferroelectric spontaneous electric polarization. Figure 5 provides a detailed explanation of step 2 in Fig. 2. The Verilog-A describing the ferroelectric capacitor is divided into sections for the temperature impact and the part related to ferroelectric hysteresis. First, εFE, tFE, which are ferroelectric material information, PS, a, and VC of Equation 1 are set for polarization according to temperature conditions. After that, if it is not room temperature, PS and VC are corrected for the current temperature through Equation 6-8. Ferroelectric hysteresis is described after PS, VC calibration. When in the saturation loop, m = 1 and b = 0 in Equation 2, and in the non-saturated inner loop, Equation 3 and 4 are used to calculate m and b in Equation 2. The equivalent circuit of the ferroelectric layer (FeCAP) modeled based on Equations 1–8 consists of RFE, CFE, and C0, as shown in Fig. 6c, enabling the description of dynamic response. The charge density (Q) of FeCAP arises from spontaneous polarization (P) and induced displacement due to the permittivity of the ferroelectric layer (εFEε0) (Equation 5). The variation of P with applied voltage is modeled by CFE, while the linear displacement component is modeled by C0. Here, RFE is introduced to delay the charging of CFE, describing the RC delay (τFE = RFECFE) in polarization switching.

a WS2-FET temperature-dependent Id–Vg curve considering contact resistance, b Ferroelectrics temperature-dependent polarization-electric field hysteresis curve, c Ferroelectric model connected in series with RFE and in parallel with linear capacitor, d Temperature dependent measured Id–Vg curve of WS2-FeFET. Note that the Memory Window of 1.4 V is obtained through Program (PG) and Erase (ER) states at 300 K, including contact resistance characteristics. This has a great advantage in terms of Memory operation.

FA and TCAM design based on FeFET and circuit analysis

The Power Performance Area characteristics of fully WS2-FET-based FA and TCAM, as well as partially WS2-FeFET-utilized FA and TCAM, were benchmarked. In all operations, the Program/Erase voltage is set to 2 V, and the input voltage is set to 0.5 V. The transistor count for FA varies, with the 28 T FA having the highest count at 28 transistors, the 3 FeFETs FA having the lowest count at 19 transistors, and the 6 FeFETs FA having 21 transistors. The FeFET TCAM include a 2 T 2FeFETs TCAM with four transistors and a 2FeFETs TCAM with 2 transistors. FeFETs TCAM replace 6 T SRAM in the 16 T TCAM with NV memories. Both FeFET-based FA and TCAM use fewer transistors than conventional FA and TCAM, providing an advantage in terms of spatial efficiency. Supplementary Table 1 presents the input waveform conditions and transistor counts for the 28 T, 3 FeFETs, 6 FeFETs FA, and 16 T, 2 T 2FeFETs, 2FeFETs TCAM.

In Supplementary Fig. 1, the design of the 28 T FA takes advantage of the complementary connection of nMOS and pMOS. The serial connection of nMOS is convertible to the parallel connection of pMOS, and vice versa. Unlike 28 T FA, the 3FeFETs FA proposed by Yin et al. using FeFET does not work complementarily with nMOS and pMOS, and consists of nMOS except for clock transistor and inverter transistor19.

As seen in Fig. 6c, in the Polarization up (P-up) state, the output is 1, and in the Polarization down (P-down) state, the output is either 1 or 0. The 6FeFETs FA is a designed structure based on the array structure proposed by Breyer et al.33. In Breyer et al.‘s study, an FA using FeFETs requires an FeFET I–V curve that outputs 1 or 0 when P-up and 0 when P-down. Therefore, the curve needs to be shifted to the right, which poses challenges such as delay time issues when using the different type of I–V curve. In order to use the curve in the form of Fig. 6c without moving, 6FeFETs FA was designed in this paper. Unlike the 3FeFETs FA, Sum and COUT operate independently. Sum is obtained through XOR gates, and COUT is calculated using AND gates. The structure is arranged in a NOR memory array format, which does not interfere with FeFET switching, making write operations easy. It can be applied to various array structures, such as memristor-crossbar memory arrays. The incorporation of nonvolatile devices’ write operations in existing logic FA can lead to abrupt voltage/current drops. By integrating non-volatile characteristics into volatile circuit structures, a stable LiM structure with nonvolatility is achievable. Two clock transistors and four inverter transistors are connected to the bit line.

The Id–Vg curves for 3 FeFETs, 6 FeFETs FA at 230 K, 300 K, and 360 K can be observed through Fig. 6c. The read voltage for both 3 FeFETs and 6 FeFETs FA is set to 0.5 V. As shown in Supplementary Fig. 1e-h, applying 2 V stores 1 in the FeFET, and it continues to operate with the value 1. When −2 V is applied, 0 is stored in the FeFET. The 28 T, 3FeFETs, and 6FeFETs FA operate similarly at 230 K and 360 K.

In the analysis of circuit characteristics such as Delay time, Dynamic Power, Standby Power, and Power Delay Product (PDP) for circuits based on 28 T, 3FeFETs, and 6FeFETs FA at different temperatures, the results were summarized in Supplementary Table 2 and Fig. 7. In all aspects, the 6FeFETs FA outperformed others. When compared to the 28 T FA for Delay time, the 3FeFETs FA improved by 12.7%, and the 6FeFETs FA improved by 16.8%. In the WS2-FET Id–Vg curve of the 28 T FA, the Ion/Ioff was lower than that of the 3FeFETs FA, leading to an improvement in Delay time for the 3FeFETs FA over the 28 T FA. Unlike the 28 T FA, which passes through three transistors from input to output, the 6FeFETs FA passes through approximately two WS2-FETs, resulting in the smallest Delay time characteristic. Dynamic Power improved by 29.1% for the 3FeFETs FA and 57.7% for the 6FeFETs FA. The 28 T FA utilizes all 28 transistors during operation, while the 3FeFETs FA uses all 19 transistors as the output of !COUT is used as an input for Sum operation. Additionally, FeFET has a high Ion/Ioff19. Therefore, the Dynamic Power of the 3FeFETs FA is lower than that of the 28 T FA. In contrast to the 3FeFETs FA, which operates with complex interactions between Sum and COUT, the proposed 6FeFETs FA operates in array form where Sum and COUT operate independently. When CIN is 1, 13 transistors operate, and when CIN is 0, 14 transistors operate. The 6FeFETs FA, with the fewest operating transistors, has the lowest Dynamic Power, followed sequentially by the 3FeFETs FA and the 28 T FA. Supplementary Fig. 2a, b illustrates the proportion of power taken by FeFET and WS2-FET in the Total Dynamic Power of 3FeFETs and 6FeFETs FA. Looking at the Dynamic Power per transistor, in the 3FeFETs FA, FeFET accounts for 0.4%, and WS2-FET accounts for 6.2%. In the case of the 6FeFETs FA, FeFET accounts for 0.9%, and WS2-FET accounts for 6.3%. This indicates that the Power consumed by FeFET is significantly small, and there is an advantage in Power as the number of FeFETs increases. Standby Power improves by 5.5% for the 3FeFETs FA and 19.0% for the 6FeFETs FA. The 28 T FA has the highest Standby Power because it has more transistors than the 3FeFETs and 6FeFETs FA. 6FeFETs FA has more transistor counts than 3FeFETs FA, but 6FeFETs FA has the lowest Standby Power because the circuit of 6FeFETs FA has more parallel structures than 3FeFETs FA. PDP improves by 38.1% for the 3FeFETs FA and 64.8% for the 6FeFETs FA. Ultimately, the 6FeFETs FA, with the smallest Delay time and lowest Dynamic Power, exhibits the best PDP characteristics.

a, e Delay time, b, f Dynamic Power, c, g Standby Power, d, h PDP of FA. The values in (a–d) are taken from 300 K in Supplementary Table 2.

Figure 7e–h depicts circuit characteristics at temperatures of 230 K, 300 K, and 360 K. Delay time improves as the temperature decreases. For Dynamic Power, it increases as the temperature decreases. In Fig. 6a, the Ion of the 2D-channel DG FET used as the Baseline FET increases in the order of 230 K, 300 K, and 360 K. Therefore, Delay time is directly proportional to temperature, while Dynamic Power is inversely proportional to temperature. Standby Power improves as the temperature decreases. Since Ioff increases in the order of 360 K, 300 K, and 230 K, Standby Power is directly proportional to temperature. At all temperatures, the Delay time of the 6FeFETs FA is the shortest compared to the 28 T FA, and Dynamic Power and Standby Power also decrease the most in the 6FeFETs FA. Consequently, the Delay time, Dynamic/Standby Power, and PDP characteristics of the 6FeFETs FA are the most superior.

As shown in Supplementary Fig. 3, Supplementary Table 3, to compare the circuit layout area of FA, we designed the Layout Versus Schematic (LVS) process directly. For layouts targeting sub-2nm technology nodes, a 42 nm CGP and a 16 nm MP were employed. The circuit area of the 3FeFETs FA, considering metal wiring, improved by 22.9% compared to the 28 T FA. The circuit area of the 6FeFETs FA decreased by 13.1% compared to the 28 T FA. The 3FeFETs FA, with the fewest transistor counts, has the smallest area. Therefore, the use of FeFETs results in area improvement.

The circuit diagrams and operation principles of 2 T 2FeFETs, 2FeFETs TCAM are as follows. In the 2 T 2FeFETs TCAM, a negative voltage of −2 V is applied to the Bit Line (BL) node to polarize it to High-Vth for writing “1”, while a voltage of 2 V is applied to the Bit Line Bar (BLB) node to polarize it to low-Vth for writing “0”. When searching for “0”, the Match Line (ML) node is discharged, and vice versa when writing “0” and searching for “1”. Additionally, when writing “X” and searching for “0” or “1”, the ML node is not discharged, and it operates as a match (Supplementary Fig. 4a–c).

In contrast, the 2FeFETs TCAM performs both search and polarization using Search Line (SL) & Search Line Bar (SLB) (Supplementary Fig. 4d–f). Due to this, when the device is in a low-Vth state and the read voltage is below the threshold voltage, the FeFET should be turned off. Therefore, a I–V hysteresis curve shifted to the right not existing I–V hysteresis curve, achieved through gate work function engineering (Fig. 8a), is needed. In the high-Vth and low-Vth states, the FeFET operates as off when the operating voltage is below the threshold voltage, and in the low-Vth state, it operates as on when the read voltage is above the threshold voltage.

2FeFETs TCAM has one pull-down transistor, while 2 T 2FeFETs TCAM has two, showing multi-bit mismatch characteristics unlike other TCAM schemes34. Figure 8b shows the variation in ML node discharge rate based on the number of mismatch bits in a 64×64 array. The 2FeFETs TCAM, despite its drawback of slower delay, has the advantage of being able to determine the number of mismatch based on the discharge rate.

We investigate and compare the circuit characteristics (Search Delay, Search Energy, and Energy Delay Product) of 16 T, 2 T 2FeFETs, and 2FeFETs TCAM. Additionally, we examine the temperature-dependent characteristics of the 2 T 2FeFETs TCAM. To observe trends in performance gaps, we conduct a comparative analysis based on the increase in TCAM array size up to 64×6435,36,37.

For comparison between various TCAM schemes, Search Delay, Search Energy, and Energy Delay Product (EDP) are measured in all mismatch states with the highest ML discharge rate of 2FeFETs TCAM. Unlike 1 mismatch, in the case of all mismatches, the number of nodes discharged in the pull-down network increases, leading to a decrease in Delay as the array size increases (Fig. 9a). At room temperature, compared to the 64 × 64 size 16 T TCAM, the 2 T 2FeFETs TCAM is 3.0% faster, while the 2FeFETs TCAM is 26.4% slower (Fig. 9d). The 2 T 2FeFETs TCAM, with two pull-down transistors, exhibits the fastest Delay, followed by the 16 T and 2FeFETs TCAM. For Search Energy, as the transistor count decreases to 1/4 for 2T 2FeFETs TCAM and 1/8 for 2FeFETs TCAM compared to 16 T TCAM, the difference between them increases with the increasing array size (Fig. 9b). Compared to 16 T TCAM, the energy consumption of 2 T 2FeFETs TCAM improved by 35.9%, and for 2FeFETs TCAM, it improved by 53.7% (Fig. 9e). To assess the impact of the trade-off between Delay and Energy, we examined the EDP. In the case of a 64 × 64 size at 300 K, the EDP for 2 T 2FeFETs TCAM is 37.8% lower compared to 16 T TCAM, and 2FeFETs TCAM shows a 41.4% reduction (Fig. 9c, f).

Since the delay of 2 T 2FeFETs TCAM has the largest Ion/Ioff at low temperatures where the on current of FeFET is large and the off current is small, the lower the temperature, the higher the performance. Conversely, Energy consumption has an advantage at higher temperatures when the on current is low.

As a result, 2 T 2FeFETs, 2FeFETs TCAM using FeFETs have an advantage in terms of EDP compared to the 16 T TCAM. This is primarily due to significant energy consumption. In the case of 16 T TCAM, volatile LiM continuously consumes energy in SRAM, while in the 2 T 2FeFETs TCAM, SRAM is replaced by FeFET, reducing energy consumption (Supplementary Fig. 5a). In the 2FeFETs TCAM, the comparator is combined with FeFET, achieving even greater energy savings (Supplementary Fig. 5c).

The 16 T, 2 T 2FeFETs, 2FeFETs TCAM require one Sense Amplifier (SA) per Match line, and each SA consists of three transistors. A 2×2 TCAM cells with SA in the 16 T TCAM have a total of 70 transistors. The 2 T 2FeFETs TCAM has 8 FeFETs and 14 transistors, while the 2FeFETs TCAM has only 8 FeFETs and 6 transistors. Supplementary Figure 3, Supplementary Table 3 compared the layout and area of a 2 × 2 TCAM cell, including SA, for 16 T, 2 T 2FeFETs, 2FeFETs TCAM. The 2 T 2FeFETs TCAM occupies 20.8% less area than the 16 T TCAM, while the 2FeFETs TCAM has a 14% smaller footprint.

Discussion

In this paper, two different types of FA and TCAM were designed through FeFET incorporating ferroelectric materials into 2D-channel DGFETs using monolayer WS2 channels to confirm the potential for next-generation LiM applications. To achieve this, we examined the structure and characteristics of FeFET and implemented a FeFET compact model. We analyzed the Delay time, Dynamic Power, Standby Power, and Power Delay Product (PDP) for a 28 T FA and 3 FeFETs FA, as well as a 6 FeFETs FA. Additionally, we conducted a circuit layout area comparison through LVS processes applying sub-2nm technology nodes. The same process was carried out for Search Delay, Search Energy, and Energy Delay Product (EDP) aspects in 16 T TCAM, 2 T 2FeFETs TCAM, and 2FeFETs TCAM.

To verify the operational characteristics of the LiM circuit, a FeFET hysteresis curve is essential. If the appropriate Program/Erase voltage is not applied to the gate, a hysteresis loop will not form, leading to operational errors. We optimized the Program/Erase voltage conditions for polarization characteristics, confirming the normal operation of FeFET-based FA and TCAM under various temperature conditions (230 K, 300 K, 360 K).

The PDP of FA improves as the number of utilized FeFETs increases. Compared to 28 T FA, 3FeFETs FA shows a 38.1% improvement, and 6FeFETs FA demonstrates a 64.8% enhancement. The designed 6 FeFETs FA outperforms in terms of Delay time, Dynamic/Standby Power, and PDP under all temperature conditions, with a 13.1% reduction in circuit area compared to 28 T FA, enhancing the feasibility of LiM application circuits. For TCAM, as the array size increases, Search Delay decreases, and the 2 T 2FeFETs TCAM with two pull-down transistors proves to be the fastest. In terms of Search Energy, the 2FeFETs TCAM, with the fewest number of devices among NV TCAM, exhibits significantly the lowest energy consumption. Moreover, examining the temperature characteristics of the 2 T 2FeFETs TCAM reveals that it achieves the fastest delay at the lowest temperature with the highest Ion/Ioff, while energy consumption is most improved at the highest temperature with the smallest Ion. Ultimately, at room temperature, the EDP of 2 T 2FeFETs TCAM is 37.8% better than that of 16 T TCAM, and 2FeFETs TCAM is 41.4% better. Therefore, the EDP of 2FeFETs TCAM is the most superior, with only a 14.0% reduction in area compared to 16 T TCAM.

Methods

Device analysis and circuit modeling of 2D-channel DG FeFET

The temperature characteristics of WS2 were derived from measurements reported by Ovchinnikov et al.38, with additional details provided in our research group’s previous paper22. Ion decreases with temperature, while Ioff increases proportionally to temperature. 2D materials exhibit Metal-Insulator Transition (MIT) characteristics due to the formation of disorder and interactions between metal and insulator, influenced by the relative strength of each mechanism39. In monolayer WS2 DG FETs, MIT occurs at a gate voltage of ~0.3 V, and as the temperature increases, the Sub-threshold Swing becomes higher. When the gate voltage is lower than the MIT point, the influence of the insulating state dominates, resulting in an increase in Ioff with temperature. Conversely, when the gate voltage is higher than the MIT point, the influence of the metallic state becomes more pronounced, leading to a decrease in Ion with increasing temperature38.

The polarization–electric field (P–E) characteristics of the ferroelectric material used in this study were based on a 10 nm HSO Metal-Ferroelectric-Metal structure measured through PUND tests, with experimental values taken from Ni et al.30. Temperature variations were applied based on experimental data reported by Zhou et al.24. An increase in the thickness (tFE) of ferroelectrics leads to an enlargement of the MW. However, it also results in an increase in the required voltage for hysteresis, negatively impacting energy efficiency. Moreover, beyond a certain thickness, a monoclinic phase dominates, characterized by minimal remnant polarization and low permittivity, leading to the loss of ferroelectricity40. With an increase in temperature, both the MW and Remanent Polarization (Pr) decrease, while the absolute value of Saturation Polarization (PS) is comparatively small. This is attributed to the phase change in the ferroelectric material; as the temperature of the ferroelectric material increases, the impact of the tetragonal phase with nonpolar characteristics becomes more significant than that of the orthorhombic phase with polar characteristics, resulting in changes in the P–E curve41.

Data availability

The authors declare that the data supporting the findings of this work are available within the paper and its supplementary information. The corresponding authors can also provide data upon reasonable request.

References

Liu, Y. et al. Promises and prospects of two-dimensional transistors. Nature 591, 43–53 (2021).

Park, J. et al. Investigation of optimal architecture of MoS2 channel field-effect transistors on a Sub-2 nm process node. ACS Appl. Electron. Mater. 5, 2239–2248 (2023).

Shen, P.-C. et al. Ultralow contact resistance between semimetal and monolayer semiconductors. Nature 593, 211–217 (2021).

Dorow, C. et al. Advancing monolayer 2-D nMOS and pMOS transistor integration from growth to van der Waals interface engineering for ultimate CMOS scaling. IEEE Trans. Electron Devices 68, 6592–6598 (2021).

Wu, F. et al. Vertical MoS2 transistors with sub-1-nm gate lengths. Nature 603, 259–264 (2022).

International Roadmap for Devices and Systems (IRDS™) https://irds.ieee.org/editions/2022 (2022). (2017-2022)Available online(accessed on 5 Oct).

International Technology Roadmap for Semiconductors (ITRS). (2001−2013). Available online: http://www.itrs2.net/ (accessed on 5 October 2013).

Samavedam, S. et al. In Proc. IEEE International Electron Devices Meeting (IEDM). 1.1. 1-1.1. 10 (IEEE, 2020).

Huang, X., Liu, C., Jiang, Y.-G. & Zhou, P. In-memory computing to break the memory wall. Chin. Phys. B 29, 078504 (2020).

Jaiswal, A., Chakraborty, I., Agrawal, A. & Roy, K. 8T SRAM cell as a multibit dot-product engine for beyond von Neumann computing. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 27, 2556–2567 (2019).

Mutlu, O., Ghose, S., Gómez-Luna, J. & Ausavarungnirun, R. Processing data where it makes sense: enabling in-memory computation. Microprocessors Microsyst. 67, 28–41 (2019).

Eigenmann, R. & Lilja, D. J. Von neumann computers. Wiley Encycl. Electr. Electron. Eng. 23, 387–400 (1998).

Arikpo, I., Ogban, F. & Eteng, I. Von neumann architecture and modern computers. Glob. J. Math. Sci. 6, 97–103 (2007).

Sebastian, A., Le, Gallo, M., Khaddam-Aljameh, R. & Eleftheriou, E. Memory devices and applications for in-memory computing. Nat. Nanotechnol. 15, 529–544 (2020).

Stone, H. S. A logic-in-memory computer. IEEE Trans. Comput. 100, 73–78 (1970).

O’Connor, I. et al. In Proc. IFIP/IEEE International Conference on Very Large Scale Integration (VLSI-SoC). 180-183 (IEEE, 2018).

Marchand, C. et al. In Proc. 16th International Conference on Design & Technology of Integrated Systems in Nanoscale Era (DTIS). 1-6 (IEEE, 2021).

Zanotti, T., Puglisi, F. M. & Pavan, P. Smart logic-in-memory architecture for low-power non-von neumann computing. IEEE J. Electron Devices Soc. 8, 757–764 (2020).

Yin, X. et al. In Proc. IEEE/ACM International Conference on Computer-Aided Design (ICCAD). 1–8 (IEEE, 2016).

Barla, P., Joshi, V. K. & Bhat, S. Design and evaluation of a self write-terminated hybrid MTJ/CMOS full adder based on LIM structure. J. Circuits, Syst. Comput. 31, 2250146 (2022).

Wang, P. et al. Drain-erase scheme in ferroelectric field effect transistor—Part II: 3-D-NAND architecture for in-memory computing. IEEE Trans. Electron Devices 67, 962–967 (2020).

Park, J., Ra, C., Lim, J. & Jeon, J. Device and circuit analysis of double gate field effect transistor with mono-layer WS2-channel at Sub-2 nm technology node. Nanomaterials 12, 2299 (2022).

Ahmed, Z. et al. In Proc. IEEE International Electron Devices Meeting (IEDM). 22.25. 21–22.25. 24 (IEEE, 2020).

Zhou, D. et al. Electric field and temperature scaling of polarization reversal in silicon doped hafnium oxide ferroelectric thin films. Acta Mater. 99, 240–246 (2015).

Yakimets, D. et al. In Proc. IEEE International Electron Devices Meeting (IEDM). 20.24. 21-20.24. 24 (IEEE, 2017).

Loubet, N. et al. In Proc. Symposium on VLSI Technology. T230-T231 (IEEE, 2017).

Sicard, E. & Trojman, L. Introducing 3-nm Nano-Sheet FET technology in Microwind. (2021).

Liu, Z., Bhuiyan, M. & Ma, T. In Proc. IEEE International Electron Devices Meeting (IEDM). 31.32. 31-31.32. 34 (IEEE, 2018).

Li, W. et al. Approaching the quantum limit in two-dimensional semiconductor contacts. Nature 613, 274–279 (2023).

Ni, K., Jerry, M., Smith, J. A. & Datta, S. In Proc. IEEE symposium on VLSI technology. 131-132 (IEEE, 2018).

Schultz, I., Goebel, H. & Ullmann, M. Modelling polarisation of ferroelectric SBT capacitors including temperature dependence. Electron. Lett. 37, 1 (2001).

Vopsaroiu, M., Blackburn, J., Cain, M. G. & Weaver, P. M. Thermally activated switching kinetics in second-order phase transition ferroelectrics. Phys. Rev. B 82, 024109 (2010).

Breyer, E. T. et al. Compact FeFET circuit building blocks for fast and efficient nonvolatile logic-in-memory. IEEE J. Electron Devices Soc. 8, 748–756 (2020).

Ni, K. et al. Ferroelectric ternary content-addressable memory for one-shot learning. Nat. Electron. 2, 521–529 (2019).

Yin, X., Niemier, M. & Hu, X. S. in Design, Automation & Test in Europe Conference & Exhibition (DATE), 2017. 1444–1449 (IEEE).

Chao, H. J. & Liu, B. High-Performance Switches and Routers. (John Wiley & Sons, 2007).

Huang, P.-T. & Hwang, W. A 65 nm 0.165 fJ/Bit/Search 256$\,\times\, $144 TCAM macro design for IPv6 lookup tables. IEEE J. Solid-State Circuits 46, 507–519 (2010).

Ovchinnikov, D., Allain, A., Huang, Y.-S., Dumcenco, D. & Kis, A. Electrical transport properties of single-layer WS2. ACS Nano 8, 8174–8181 (2014).

Moon, B. H. Metal-insulator transition in two-dimensional transition metal dichalcogenides. Emergent Mater. 4, 989–998 (2021).

Lyu, J., Song, T., Fina, I. & Sánchez, F. High polarization, endurance and retention in sub-5 nm Hf0.5Zr0.5 O2 films. Nanoscale 12, 11280–11287 (2020).

Materlik, R., Künneth, C. & Kersch, A. The origin of ferroelectricity in Hf1− xZrxO2: a computational investigation and a surface energy model. J. App. Phys. 117 (2015).

Acknowledgements

This research was funded and conducted under the Competency Development Program for Industry Specialists of the Korean Ministry of Trade, Industry and Energy (MOTIE), operated by Korea Institute for Advancement of Technology (KIAT). (No. P0023704, Semiconductor-Track Graduate School (SKKU)), and partly by National Foundation of Korea (NRF) grant funded by the Korean government (MSIT) (No.2022M3F3A2A01072215).

Author information

Authors and Affiliations

Contributions

H.K. and J.P. contributed equally to the main idea, analyzing the data, and wrote the initial draft of the manuscript. H.J. performed transistor modeling for simulation. J.J. and C.R. planned this research, executed under the supervision, and finalized the manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Kim, H., Park, J., Jung, H. et al. Logic-in-memory application of ferroelectric-based WS2-channel field-effect transistors for improved area and energy efficiency. npj 2D Mater Appl 8, 29 (2024). https://doi.org/10.1038/s41699-024-00466-9

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41699-024-00466-9