Abstract

Biosensors based on liquid-gated carbon nanotubes field-effect transistors (LG-CNTFETs) have attracted considerable attention, as they offer high sensitivity and selectivity; quick response and label-free detection. However, their practical applications are limited due to the numerous fabrication challenges including resist-based lithography, in which after the lithography process, the resist leaves trace level contaminations over the CNTs that affect the performance of the fabricated biosensors. Here, we report the realization of LG-CNTFET devices using silicon shadow mask-based chemical-free lithography process on a 3-in. silicon wafer, yielding 21 sensor chips. Each sensor chip consists of 3 × 3 array of LG-CNTFET devices. Field emission scanning electron microscope (FESEM) and Raman mapping confirm the isolation of devices within the array chip having 9 individual devices. A reference electrode (Ag/AgCl) is used to demonstrate the uniformity of sensing performances among the fabricated LG-CNTFET devices in an array using different KCl molar solutions. The average threshold voltage (Vth) for all 9 devices varies from 0.46 to 0.19 V for 0.1 mM to 1 M KCl concentration range. This developed chemical-free process of LG-CNTFET array fabrication is simple, inexpensive, rapid having a commercial scope and thus opens a new realm of scalable realization of various biosensors.

Similar content being viewed by others

Introduction

Carbon nanotubes (CNTs) have attracted most attention due to the unique combination of their electrical, optical, mechanical and thermal properties1,2, which make them suitable for incorporation in platforms such as chemiresistors3,4, field-effect transistors (FETs)5,6, supercapacitors7, and other biosensing devices8. For comprehensive use of the biosensing capabilities of CNTs, the approach of their integration into different electrical platforms is one of the important aspects. As-synthesized single-walled CNTs (SWNTs) consist of a mixture of semiconducting (s-) and metallic (m-) nanotubes. The use of this mixture will yield to the variations in device-to-device performance and particularly m-SWNTs degrade the performance of the electronic devices. The s-SWNTs are preferred for thin-film based sensor platforms due to its outstanding charge transport quality and small size (compatible to biomolecules), which make them extremely sensitive to small changes in the surroundings whether it is a gaseous or a liquid environment9,10. The behaviour of SWNTs-based FET devices for chemical/biochemical sensing have been explored with single SWNT11 and multiple SWNTs random network12,13 between source-drain electrodes, integrated by growth or by deposition techniques with back-gated14, top-gated11 biasing, and with or without liquid environment. The deposition of SWNTs random network for the fabrication of the individual device is simple and suitable; however, it is challenging to develop the process for realizing the uniform array of devices, reproducible for commercial production13.

For the fabrication of a uniform array of devices, there are many solution process-based ex situ CNTs deposition techniques which mainly includes inkjet printing15,16, photolithographic patterning17,18, drop-casting19, dip-coating20, electrophoretic deposition21, spin-coating22, and spray-coating3,23. Low-cost inkjet printers have lower resolution, control of drop size and spacing between the line features; whereas commercial inkjet printers are expensive24. Sometimes, few additional steps such as substrate modification15, dispersant removal24 etc. are also required in inkjet printing technique, which results in poor electrical conductivity of the CNTs as well as increased device fabrication cost. In the case of CNTs-based sensing platforms, fabricated by a photolithography process, it has been observed that after photoresist removal, their traces are the sources for signal noise which results in the deterioration in their electrical performance25. Apart from this, electrophoretic deposition techniques of the CNTs have adhesion issues on semiconducting and metal surfaces21. The spin-coating process is not suitable in case of large-size substrates, due to the difficulty in spinning them at high speed, which results in large thickness variation in CNTs film26. In the drop-casting method also, arbitrarily thick films of CNTs results in degradation of FET electrostatic control27,28. From a commercial point-of-view, though the spray-coating process can deposit uniform layers, nevertheless further investigations are required specifically to use this technique to pattern CNTs with large area uniformity over various kinds of solid/flexible substrates such as silicon, glass, polydimethylsiloxane (PDMS), poly(methyl methacrylate) (PMMA), polyether ether ketone (PEEK) etc29.

In this paper, we report direct patterning of a uniform thin film of s-SWNTs using chemical-free shadow mask lithography instead of conventional photolithography. A silicon shadow mask with openings is fabricated using silicon bulk-micromachining and then successfully aligned with the predefined source-drain electrode structures followed by optimized spray coating process to fabricate an array of LG-CNTFET devices. This process is chemical-free, economic, rapid, ease in use and scalable for commercial production of LG-CNTFET device array as a chemical/biochemical sensing platform. The measured resistances between source and drain assure uniformity among the fabricated array of devices. The sensing performance of the fabricated LG-CNTFET biosensing platform with 0.1 mM to 1 M range of KCl concentrations confirms the consistency and uniformity among the complete array of devices.

Materials and methods

Materials

Tetramethylammonium hydroxide (TMAH) (25% solution in water) was purchased from Merck. 1,2-Dichlorobenzene (DCB) (Anhydrous, 99%,) and reference electrode (Ag/AgCl) were purchased from Sigma-Aldrich. Pristine s-SWNTs (IsoNanotubes-S) was purchased from Nanointegris. Sylgard 184 silicone elastomer was purchased from Dow Corning.

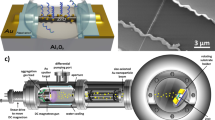

Silicon shadow mask fabrication

The method of silicon shadow mask fabrication was adopted with minor modifications from our earlier work as shown in Fig. 130. First silicon dioxide (SiO2) of ~ 1 μm thickness was grown over 350 μm thick silicon wafer using thermal oxidation and windows of 400 μm × 400 μm size were patterned using photolithography. TMAH solution was used for bulk micromachining of silicon at 80 °C, having an etch rate of ∼ 24 μm/h. For a single LG-CNTFET chip, 9 windows were opened in a silicon shadow mask to realize an array of 3 × 3 devices.

Spray coating optimization

In-house developed spray coating set-up was used to prepare a thin film of s-SWNTs over 3-in. (diameter) silicon wafer30. The setup comprises of ultrasonic atomizer probe, motorized X–Y stage, a hot plate for in situ solvent evaporation, syringe pump for precise flow control of s-SWNTs suspension, and an exhaust fan. The suspension was prepared using pristine s-SWNTs in DCB with a concentration of 0.1 mg/ml31. Uniform s-SWNTs thin film was achieved first on bare silicon substrates through optimization of spray coating parameters namely substrate temperature, substrate-spray nozzle distance, solution concentration, and flow rate. A four-probe sheet resistance measurement (QuadPro, Signatone) was used to map the sheet resistance of these s-SWNTs coated bare silicon substrates. The optimized value of uniform sheet resistance was ~ 0.9 to 1.4 kΩ/square.

LG-CNTFET array fabrication

To fabricate the array of devices, silicon wafer <100> , p-type, 3-in. diameter with resistivity 1–20 Ω-cm was RCA cleaned and (Fig. 2a) and thermal oxide was grown at 1100 °C to achieve silicon dioxide of 1 µm thickness (Fig. 2b). The metal contacts were patterned via photolithography of Cr/Au (300 Å/2500 Å), which were deposited using DC sputtering (Fig. 2c). After wet etching of Cr/Au (Fig. 2d), plasma-enhanced chemical vapour deposition (PECVD) was used to deposit oxide/nitride layers of thickness 1000 Å/4000 Å for passivation purpose (Fig. 2e). Second photolithography was carried out to open only source-drain windows and contact pads in the passivation layer for connections with the s-SWNTs network (Fig. 2f). The patterned substrate with an array of source-drain electrodes pairs was ready for introducing the s-SWNTs as channel elements. This wafer was first aligned with the fabricated reusable silicon shadow mask with the help of in-house developed shadow mask aligner32. After alignment, the assembly was ready for spray coating process (Fig. 2g). As discussed in the previous section, the optimized s-SWNTs spray coating process was adopted to fabricate the actual device array over the wafer, of which temperature was maintained ~ 180 °C. This wafer has 189 devices and distributed over 21 individual sensor chips. After spray coating, the device wafer was separated from the shadow mask and diced into 21 chips of 12.7 mm × 12.7 mm size. The individual chip consists of 3 × 3 array of devices (Fig. 2h) followed by fixing the PDMS well (Fig. 2i). The individual chip with source-drain electrodes of an actual fabricated array of s-SWNTs devices before and after s-SWNTs spray is shown in Fig. 3a,b, respectively. The third electrode corresponding to each device (Fig. 3a) is designed for exploring the possibility of integration of on-chip Ag/AgCl electrodes in future.

After dicing the wafer, the snapshot of an individual chip is shown in Fig. 4a. To accommodate and confine different testing fluids over the devices; PDMS wells of 6 mm diameter and 15 mm height were fabricated using Sylgard 184 silicone elastomer base and curing agent in the ratio of 10:133. The PDMS mixture was stirred manually and poured in stainless steel (SS) mould (Fig. 4b). It is then kept in a vacuum desiccator to remove trapped air bubbles. The mixture was cured at 80 °C for 30 min followed by separation of wells by dicing using SS blade. The individual wells (Fig. 4c) were treated with oxygen plasma for 30 s followed by their fixing over the chip (Fig. 4d).

Results and discussion

Device uniformity

First, the resistances of all 189 devices in 21 chips have been measured to assess the uniformity of spray-coated s-SWNTs on the 3-in. substrate. Figure 5a shows the photograph of a complete 3-in. wafer with multiple sensor chips. The single-chip consists of an array of 3 × 3 devices, in which the distance between two adjacent s-SWNTs spray portions of the individual devices is ~ 1.6 mm. Figure 5b, shows the bar-chart of 21 array chips having an average value of source-drain resistances nearly 3 kΩ, which confirms the uniformity across the wafer. One of these chips was chosen for all further electrical measurements by using different KCl molar concentrations. This chip has the majority of devices (7 out of 9 devices), with source-drain resistance in the range of 1–3 kΩ, while remaining two devices has resistances 3.5 kΩ and 6.9 kΩ, respectively.

To confirm the isolation among the fabricated devices, the resistances were measured between various pads and found open circuit except for the resistance between the two pads of the corresponding device in an array.

Raman and FESEM characterization

The spray-coated chip was characterized using FESEM (Quanta FEG 250, FEI) and Raman (InVia, Renishaw) to confirm the presence of s-SWNTs network between the source-drain as well as to ensure isolation of devices in a chip. FESEM image (Fig. 6a) shows the isotropic spray of s-SWNTs over the prefabricated source-drain structure in a circular area of ~ 750 μm diameter larger than the shadow mask opening i.e. 400 μm. There is always a gap between the shadow mask and the source-drain substrate due to inherent bow in the wafers, the s-SWNTs deposited through windows diffuse beyond the shadow mask opening area (Fig. 3b) and there is a progressive reduction of the thickness of deposited s-SWNTs (Fig. 6b), and eventually, their complete closure, as shown in Fig. 6c34. The zoomed areas in Fig. 6b and further in 6c confirms, how the s-SWNTs density decreases as we move away from the spray-coated zone of a single device in a chip, and this separation helps to isolate the devices from each other.

source-drain) for individual devices (b) the enlarged portion (green box) in (a) shows the blurring effect, and (c) the enlarged portion (blue box) in (b) i.e. the outermost portion of the single device confirms the discontinuity in s-SWNTs film.

FESEM images (a) show the confined network of s-SWNTs between the electrodes (

Raman spectra of the channel region were acquired using 532 nm laser with 1 mW power as shown in Fig. 7a. Radial breathing mode (RBM) peak at 169 cm−1 confirms the presence of SWNTs, while two distinguishable peaks, G1 at 1575 cm−1 and G2 at 1589 cm−1, indicates that the SWNTs are semiconducting35. To confirm the isolation between the adjacent sprayed s-SWNTs region, the Raman mapping was carried out for a single device of an array using pointwise data collection with the spacing of 20 µm in 1.6 mm × 1.6 mm area (Fig. 7b). In the mapping spectra the contour corresponding to RBM peak range 168–172 cm−1, also ensures confinement of sprayed s-SWNTs patterns, therefore it will not interfere with the nearby devices/sensors.

Electrical measurements

Fabricated LG-CNTFETs array platform was electrically tested using 2-channel source-measure unit (SMU) (B2902A, Keysight) with different KCl solution of the concentrations ranging from 0.1 mM to 1 M. For each electrical measurement, 300 µl KCl solution of required molarity was filled in the capped PDMS well over the device and Ag/AgCl reference electrodes, dipped in the filled KCl solution were used as top-gate for FET measurements36.

The output characteristics for the individual device were acquired with drain-source voltage (Vds) of 0–0.2 V at different gate voltages (Vgs) ranging from − 0.1 to 0 V and transfer characteristics were taken for Vgs of − 0.4 to 0.8 V at constant Vds bias of 0.1 V. After each experiment with varying the molar concentration of KCl solution, the chip was thoroughly cleaned with deionized (DI) water and dried with the nitrogen (N2) for the next set of experiments.

Figure 8a shows the output characteristics of the single device from the array (3 × 3 devices) for different KCl concentrations with liquid gate bias applied from − 0.1 to 0 V with 0.05 V incremental steps. In the transfer curve (Fig. 8b) the higher conductance of the device at more negative gate bias (Vgs) indicates the p-type conduction in the s-SWNTs. The low current in off-state is due to m-SWNTs between the electrodes. The results shown in Fig. 8b reflect the significant modulation of conductance in the s-SWNTs network. The linear behaviour (due to diffusion of carriers) in output characteristics at low bias voltage shows that the overall resistances are dominated by significant contributions of SWNT-SWNT junctions in the random network than that of electrode metal-SWNTs contact junctions. This happens mainly due to the relatively larger channel length (~ 200 µm)37.

Electrical characteristics of a single device on the chip array (3 × 3) (a) Output characteristics for different applied gate voltages for different concentrations of KCl, (b) transfer characteristics for different concentrations of KCl at constant voltage Vds ~ 0.1 V, and decrease in Vth for the increase in KCl concentrations are shown by fitting (dashed line) the linear region of the corresponding transfer curve for different concentrations and (c) Vshift for KCl concentrations is plotted while the value for 1 M KCl is taken as reference.

Transfer curve in the Fig. 8b shows that device turned off at Vgs ~ 0.8 V for 0.1 mM KCl concentration and this value decreases with increase in electrolytic concentration from 0.1 mM to 1 M. This reflects the dependence of conductance on ionic strength of the liquid. To determine sensitivity in electrolytic medium, there are different responsible mechanism, which includes majorly Schottky-barrier effect, electrolytic gating effect, capacitive modulation and mobility38,39,40. Device mobility is almost independent for the channel length of ≥ 2 µm9. As in our case, the channel length is ~ 200 µm; therefore, electrostatic gating will dominate over mobility effects. Here shifting of the transfer curve corresponding to different concentrations with a small change in the transconductance (slope of the linear region: dIds/dVgs) shows the electrostatic gating effect38. In LG-CNTFET, the channel SWNTs adhere to the substrate surface, which is negatively charged under physiological conditions41. These negative charges are screened by the positive ions in electrical double layer (EDL) and positive charges (holes) in the SWNTs. Most of these negative charges are screened by the EDL because of its higher capacitance than the quantum capacitance of SWNTs. In other words, the SWNTs experienced reduced liquid gate potential by the potential drop across EDL in the solution.

For higher electrolyte concentration, the thickness of EDL reduces i.e. Debye screening length shortens; this results in higher EDL capacitance, which in-turns reduce the surface potential. Therefore, the more negative voltage is necessary to compensate for this change and the Ids-Vgs curve shifts towards more negative gate voltages41.

The drain current (Ids) in the linear region is given by the following relation42

where Ceff is the effective gate capacitance, which is mainly given by the in-series capacitances of the SWNTs/electrolyte (EDL capacitance) and the electrolyte/gate-electrode, µ is the carrier mobility, W and L are the gate width and length, respectively, Vgs and Vds are the gate-source and drain-source voltages, respectively, and Vth is the threshold voltage. The transconductance gm is expressed as:

For extraction of Vth, the extrapolation in the linear region (ELR) (also called as linear extraction (LE)) method was used43,44. The method is based on finding the gate-voltage axis intercept (i.e., Ids = 0) of the linear extrapolation of the Ids–Vgs curve at its maximum first derivative (slope) point (i.e. the point of maximum transconductance (Fig. 8b)45,46.

For lowest KCl concentration (0.1 mM), the Vth value is highest (i.e. ~ 0.39 V) and as the concentration is increased to 1 M, the Vth is reduced to 0.17 V (Fig. 8b). To quantify the electrostatic gating effect, the shift in threshold voltage (Vshift) vs KCl concentration for a single device of the array is plotted in Fig. 8c, where Vth of 1 M KCl is taken as reference for other KCl concentrations. As the KCl concentration decreases, the devices become more p-doped and correspondingly the increased Vshift. The Vshift by 0.22 V towards more positive gate voltage, in a range of 5 decades of KCl concentration can be seen in Fig. 8c14. For the same LG-CNTFET device, the gate leakage current (Igs) of LG-CNTFET was measured for 0.1 mM to 1 M KCl concentration range under Vgs varying from − 0.4 to 0.8 V and constant Vds ~ 0.1 V (see Fig. S1 in Supplementary Information). It was observed that the measured value of Igs was in the range of ± 50 nA for all the KCl concentrations.

The comparison of electrical measurements of multiple devices over a single chip (3 × 3 array) is essential to validate the uniformity among the devices. As explained in Fig. 5, the silicon shadow mask-based process results in good uniformity of source-drain resistances among the fabricated devices as well as chips covering the whole wafer area. In Fig. 9a, the output characteristics of all 9 devices of a chip (3 × 3 array) at a constant Vgs ~ − 0.2 V and 10 mM KCl concentration are plotted, where the characteristics of maximum devices from the array (7 out of 9) are similar except D3 and D7. The transfer curve as shown in Fig. 9b also confirms the uniformity among the devices. Using ELR method, the calculated Vth of 7 similar devices for 10 mM KCl concentration at constant Vds ~ 0.1 V is 0.35 ± 0.06 V (Fig. 9b). The average value of threshold voltage for all 9 devices of a chip vs KCl concentrations is plotted in the form of an error bar by taking standard deviation as a source of error (Fig. 9c). As concentration increases, the average threshold voltage also shows a linear decrease for the array of devices, similar to the case of the individual device as explained for Fig. 8c. For these 3 × 3 array of LG-CNTFET devices, measured Igs was within ± 50 nA for 0.1 mM to 1 M KCl concentrations under constant Vds ~ 0.1 V for varying Vgs from − 0.4 to 0.8 V (see Fig. S2 in Supplementary Information).

Electrical characteristics of 3 × 3 array of devices (a) Output characteristics for different devices at constant Vgs ~ − 0.2 V for 10 mM KCl concentration (b) transfer characteristics for different devices at constant voltage Vds ~ 0.1 V and 10 mM KCl concentration, and similarity in Vth for different devices for fixed 10 mM KCl concentration is shown by fitting (dashed line) the linear region of the corresponding transfer curve and (c) plot of an average value of Vth for 9 devices of a chip for KCl concentrations along with error bar representation, while standard deviation as a

Conventionally, the fabrication process of LG-CNTFETs involves thin film preparation of CNTs over a large size substrate/wafer, followed by their patterning using photolithography and removal/etching of CNTs from the undesired area using oxygen plasma23,47,48,49,50.

In Table 1, we compare our shadow mask-based s-SWNTs patterning approach with the reported fabrication methods for the realization of similar LG-CNTFET array of devices49,51,52,53,54,55. In most of the cases, for such semiconductor device array fabrication, the use of mixture (s-/m-) SWNTs results in variation in device-to-device characteristics and degradation of device performance especially due to m-SWNTs. In our fabricated devices, s-SWNTs were used for the LG-CNTFET fabrication, which results in uniform electrical performance of devices in an array (Fig. 9). The competitive advantage of our developed shadow-mask based chemical-free process for the fabrication of LG-CNTFET is the minimization of the intermediate steps namely photolithography, etching and photoresist removal, which makes the device manufacturing simpler and economic.

Conclusions

In conclusion, chemical-free shadow mask lithography along with spray coating has been successfully used for patterning the s-SWNTs to fabricate a uniform array of LG-CNTFET devices. For demonstration, the array of LG-CNTFET platform devices was electrically tested with 0.1 mM to 1 M KCl concentrations using Ag/AgCl gate electrode, immersed in fabricated PDMS well. The applied Vds and Vgs voltage ranges were 0–0.2 V and − 0.4 to 0.8 V, respectively for acquiring output and transfer characteristics of the device array. Majority of devices in a single chip have resistances in the range of 1–3 kΩ, which results in their uniform electrical performance. For example, Vth of similar 7 devices for 10 mM KCl concentration at constant Vds ~ 0.1 V is 0.35 ± 0.06 V. The average value of measured Vth for complete device array decreases from 0.46 to 0.19 V with increased KCl concentration from 0.1 mM to 1 M. The developed process is contamination-free, rapid and would be economical to fabricate a uniform array of s-SWNTs-based highly sensitive LG-CNTFET devices for a variety of applications in biochemical sensors.

References

Ajayan, P. M. Nanotubes from carbon. Chem. Rev. 99, 1787–1799 (1999).

Dresselhaus, M. S., Dresselhaus, G. & Eklund, P. C. Science of Fullerenes and Carbon Nanotubes (Elsevier, New York, 1996).

Abdellah, A., Abdelhalim, A., Horn, M., Scarpa, G. & Lugli, P. Scalable spray deposition process for high-performance carbon nanotube gas sensors. IEEE Trans. Nanotechnol. 12, 174–181 (2013).

Agarwal, P. B., Pawar, S., Reddy, S. M., Mishra, P. & Agarwal, A. Reusable silicon shadow mask with sub-5 μm gap for low cost patterning. Sens. Actuators A Phys. 242, 67–72 (2016).

Bondavalli, P., Legagneux, P. & Pribat, D. Carbon nanotubes based transistors as gas sensors: State of the art and critical review. Sens. Actuators B Chem. 140, 304–318 (2009).

Joshi, S. et al. Ambient processed, water-stable, aqueous-gated sub 1 V n-type carbon nanotube field effect transistor. Sci. Rep. 8, 11386 (2018).

Cheng, Q. et al. Graphene and nanostructured MnO2 composite electrodes for supercapacitors. Carbon 49, 2917–2925 (2011).

Gallardo, V. & Amanda, R. Biosensors Based on Carbon Nanotube Field Effect Transistors (CNTFETs) for Detecting Pathogenic Microorganisms (Universitat Rovira i Virgili, Virgili, 2009).

Dürkop, T., Getty, S. A., Cobas, E. & Fuhrer, M. S. Extraordinary mobility in semiconducting carbon nanotubes. Nano Lett. 4, 35–39 (2004).

Agarwal, P. B. et al. Silicon shadow mask technology for aligning and in situ sorting of semiconducting SWNTs for sensitivity enhancement: A case study of NO2 gas sensor. ACS Appl. Mater. Interfaces 12, 40901–40909 (2020).

Rosenblatt, S. et al. High performance electrolyte gated carbon nanotube transistors. Nano Lett. 2, 869–872 (2002).

Yoon, J. et al. Determination of individual contact interfaces in carbon nanotube network-based transistors. Sci. Rep. 7, 1–9 (2017).

Cao, Q. & Rogers, J. A. Random networks and aligned arrays of single-walled carbon nanotubes for electronic device applications. Nano Res. 1, 259–272 (2008).

Munzer, A. M. et al. Back-gated spray-deposited carbon nanotube thin film transistors operated in electrolytic solutions: An assessment towards future biosensing applications. J. Mater. Chem. B 1, 3797–3802 (2013).

Takagi, Y. et al. Inkjet printing of aligned single-walled carbon-nanotube thin films. Appl. Phys. Lett. 102, 20 (2013).

Grubb, P. M., Subbaraman, H., Park, S., Akinwande, D. & Chen, R. T. Inkjet printing of high performance transistors with micron order chemically set gaps. Sci. Rep. 7, 1202 (2017).

Cho, Y.-R. et al. Photolithography-based carbon nanotubes patterning for field emission displays. Mater. Sci. Eng. B 79, 128–132 (2001).

Tang, J. et al. Flexible CMOS integrated circuits based on carbon nanotubes with sub-10 ns stage delays. Nat. Electron. 1, 191–196 (2018).

Bardecker, J. A. et al. Directed assembly of single-walled carbon nanotubes via drop-casting onto a UV-patterned photosensitive monolayer. J. Am. Chem. Soc. 130, 7226–7227 (2008).

Li, B. et al. Ultrathin SWNT films with tunable, anisotropic transport properties. Adv. Funct. Mater. 21, 1810–1815 (2011).

Boccaccini, A. R. et al. Electrophoretic deposition of carbon nanotubes. Carbon 44, 3149–3160 (2006).

Jo, J. W., Jung, J. W., Lee, J. U. & Jo, W. H. Fabrication of highly conductive and transparent thin films from single-walled carbon nanotubes using a new non-ionic surfactant via spin coating. ACS Nano 4, 5382–5388 (2010).

Pillai, S. K. R. & Chan-Park, M. B. High-performance printed carbon nanotube thin-film transistors array fabricated by a nonlithography technique using hafnium oxide passivation layer and mask. ACS Appl. Mater. Interfaces 4, 7047–7054 (2012).

Tortorich, R. & Choi, J.-W. Inkjet printing of carbon nanotubes. Nanomaterials 3, 453–468 (2013).

Sharf, T., Kevek, J. W., DeBorde, T., Wardini, J. L. & Minot, E. D. Origins of charge noise in carbon nanotube field-effect transistor biosensors. Nano Lett. 12, 6380–6384 (2012).

Fu, L. & Yu, A. M. Carbon nanotubes based thin films: Fabrication, characterization and applications. Rev. Adv. Mater. Sci. 36, 40–61 (2014).

Cao, Q. et al. Arrays of single-walled carbon nanotubes with full surface coverage for high-performance electronics. Nat. Nanotechnol. 8, 180–186 (2013).

Gorintin, L., Bondavalli, P., Legagneux, P. & Pribat, D. High performances CNTFETs achieved using CNT networks for selective gas sensing. Proc. SPIE 7399, 739909 (2009).

Ramasamy, E., Lee, W. J., Lee, D. Y. & Song, J. S. Spray coated multi-wall carbon nanotube counter electrode for tri-iodide (I3-) reduction in dye-sensitized solar cells. Electrochem. commun. 10, 1087–1089 (2008).

Agarwal, P. B., Nambiar, A. S., Thakur, N. K. & Sharma, R. CNTs patterning using silicon shadow mask as template for chemical free and cost-effective fabrication of device array. In 6th Nano Today Conference (ed. Ying, J. Y.) 3 (Elsevier, 2019).

Bahr, J. L., Mickelson, E. T., Bronikowski, M. J., Smalley, R. E. & Tour, J. M. Dissolution of small diameter single-wall carbon nanotubes in organic solvents?. Chem. Commun. https://doi.org/10.1039/b008042j (2001).

Agarwal, P. B., Panwar, D. K., Kumar, B. & Agarwal, A. A novel shadow mask aligner based on three points levelling for wedge error compensation. Eng. Res. Express 2, 015034 (2020).

Zhou, K., Zhu, X. G., Li, Y. & Liu, J. Fabrication of PDMS micro through-holes using micromolding in open capillaries. RSC Adv. 4, 31988 (2014).

Vazquez-Mena, O. et al. Reliable and improved nanoscale stencil lithography by membrane stabilization, blurring, and clogging corrections. IEEE Trans. Nanotechnol. 10, 352–357 (2011).

Zhang, L., Liao, V. & Yu, Z. Raman spectroelectrochemistry of a single-wall carbon nanotube bundle. Carbon 48, 2582–2589 (2010).

Minot, E. D. et al. Carbon nanotube biosensors: The critical role of the reference electrode. Appl. Phys. Lett. 91, 093507 (2007).

Ishikawa, F. N. et al. Importance of controlling nanotube density for highly sensitive and reliable biosensors functional in physiological conditions. ACS Nano 4, 6914–6922 (2010).

Heller, I. et al. Influence of electrolyte composition on liquid-gated carbon nanotube and graphene transistors. J. Am. Chem. Soc. 132, 17149–17156 (2010).

Tey, J. N., Wijaya, I. P. M., Wei, J., Rodriguez, I. & Mhaisalkar, S. G. Nanotubes-/nanowires-based, microfluidic-integrated transistors for detecting biomolecules. Microfluid. Nanofluid. 9, 1185–1214 (2010).

Kauffman, D. R. & Star, A. Electronically monitoring biological interactions with carbon nanotube field-effect transistors. Chem. Soc. Rev. 37, 1197–1206 (2008).

Artyukhin, A. B. et al. Controlled electrostatic gating of carbon nanotube FET devices. Nano Lett. 6, 2080–2085 (2006).

Myodo, M. et al. Large-current-controllable carbon nanotube field-effect transistor in electrolyte solution. Appl. Phys. Lett. 106, 20 (2015).

Zhong, D., Zhao, C., Liu, L., Zhang, Z. & Peng, L. M. Continuous adjustment of threshold voltage in carbon nanotube field-effect transistors through gate engineering. Appl. Phys. Lett. 112, 20 (2018).

Melzer, K. et al. Selective ion-sensing with membrane-functionalized electrolyte-gated carbon nanotube field-effect transistors. Analyst 139, 4947–4954 (2014).

Terada, K., Nishiyama, K. & Hatanaka, K.-I. Comparison of MOSFET-threshold-voltage extraction methods. Solid. State. Electron. 45, 35–40 (2001).

Ortiz-Conde, A. et al. A review of recent MOSFET threshold voltage extraction methods. Microelectron. Reliab. 42, 583–596 (2002).

Zhang, X. et al. Fabrication of hundreds of field effect transistors on a single carbon nanotube for basic studies and molecular devices. J. Vac. Sci. Technol. B, Nanotechnol. Microelectron. Mater. Process. Meas. Phenom. 31, 06 (2013).

Bishop, M. D. et al. Fabrication of carbon nanotube field-effect transistors in commercial silicon manufacturing facilities. Nat. Electron. 3, 492–501 (2020).

Pandana, H. et al. A versatile biomolecular charge-based sensor using oxide-gated carbon nanotube transistor arrays. IEEE Sens. J. 8, 655–660 (2008).

Lu, S. & Panchapakesan, B. Nanotube micro-optomechanical actuators. Appl. Phys. Lett. 88, 253107 (2006).

Lee, Y. et al. Electrically controllable single-point covalent functionalization of spin-cast carbon-nanotube field-effect transistor arrays. ACS Nano 12, 9922–9930 (2018).

Dudina, A. et al. Monolithic CMOS sensor platform featuring an array of 9’216 carbon-nanotube-sensor elements and low-noise, wide-bandwidth and wide-dynamic-range readout circuitry. Sens. Actuators B Chem. 279, 255–266 (2019).

Seichepine, F., Rothe, J., Dudina, A., Hierlemann, A. & Frey, U. Dielectrophoresis-assisted integration of 1024 carbon nanotube sensors into a CMOS microsystem. Adv. Mater. 29, 1606852 (2017).

Tung, N. T. et al. Peptide aptamer-modified single-walled carbon nanotube-based transistors for high-performance biosensors. Sci. Rep. 7, 1–9 (2017).

Aschenbach, K. H. Development of Carbon Nanotube Field-Effect Transistor Arrays for Detection of HER2 Overexpression in Breast Cancer (University of Maryland, College Park, 2011).

Acknowledgements

The authors wish to thank Director, CSIR-CEERI, and Dr Ajay Agarwal, CSIR-CEERI for their keen interest and encouragement. Authors thank all scientific and technical members of the facilities management group for their help and support. Financial support from the Council of Scientific and Industrial Research (CSIR), Government of India under the CSIR mission mode project (HCP0012) is duly acknowledged.

Author information

Authors and Affiliations

Contributions

P.B.A. and R.S. conceived the idea, designed the experiments, and N.K.T. and Parul performed the fabrication. P.B.A., N.K.T. and R.S. wrote the main manuscript text and analyzed the FESEM and RAMAN data. J.J., and C.T. did the analysis and interpretation of electrolyte testing data. All authors reviewed the manuscript. The manuscript was written through the contributions of all authors. All authors have approved the final version of the manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher's note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary Information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Agarwal, P.B., Thakur, N.K., Sharma, R. et al. Chemical-free and scalable process for the fabrication of a uniform array of liquid-gated CNTFET, evaluated by KCl electrolyte. Sci Rep 11, 3979 (2021). https://doi.org/10.1038/s41598-021-83451-2

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-021-83451-2

This article is cited by

-

The design and performance of different nanoelectronic binary multipliers

Journal of Computational Electronics (2022)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.