Abstract

The characteristics of traps between the Al0.25Ga0.75N barrier and the GaN channel layer in a high-electron-mobility-transistors (HEMTs) were investigated. The interface traps at the Al0.25Ga0.75N/GaN interface as well as the border traps were experimentally analyzed because the Al0.25Ga0.75N barrier layer functions as a dielectric owing to its high dielectric constant. The interface trap density Dit and border trap density Nbt were extracted from a long-channel field-effect transistor (FET), conventionally known as a FATFET structure, via frequency-dependent capacitance–voltage (C–V) and conductance–voltage (G–V) measurements. The minimum Dit value extracted by the conventional conductance method was 2.5 × 1012 cm−2·eV−1, which agreed well with the actual transistor subthreshold swing of around 142 mV·dec−1. The border trap density Nbt was also extracted from the frequency-dependent C–V characteristics using the distributed circuit model, and the extracted value was 1.5 × 1019 cm−3·eV−1. Low-frequency (1/f) noise measurement provided a clearer picture of the trapping–detrapping phenomena in the Al0.25Ga0.75N layer. The value of the border trap density extracted using the carrier-number-fluctuation (CNF) model was 1.3 × 1019 cm−3·eV−1, which is of a similar level to the extracted value from the distributed circuit model.

Similar content being viewed by others

Introduction

Recently, GaN-based high-electron-mobility-transistors (HEMTs) have gained considerable attention because of their outstanding material properties and device performance, including power and RF applications up to the sub-terahertz regime1,2,3. These advantageous properties and performance are attributable mainly to the high quality of the epitaxial layer comprising the AlxGa1−xN barrier and the GaN channel layer, which causes the formation of two-dimensional electron gas (2DEG) on top of Si, Sapphire, and SiC substrates4,5. The quality of the AlxGa1−xN/GaN interface is crucial to the improvement of the carrier transport in the channel during device operation6,7. In addition to the performance of AlGaN/GaN HEMTs, their reliability is an ongoing topic of research that requires examination of a variety of factors. Most of the reliability issues are related to the AlGaN layer, which is the surface layer in the gate-to-drain access region and contains deep-level traps8. These issues become more critical in deeply scaled transistors for high-frequency applications. Most previous research on the reliability of AlGaN/GaN HEMTs focused mainly on the surface traps in the access region and on their passivation using dielectric materials9,10. Plasma treatment was also utilized to decrease these deep-level traps in the AlGaN barrier layer11. Characterization of interface traps and deep-level border traps is important for improving the 2DEG carrier concentration and reducing interface roughness scattering to enhance mobility, with the eventual aim of improving device reliability and performance. Previous studies focused on the characterization of traps formed at the insulator/AlGaN interface in a metal–oxide–semiconductor field-effect transistor (MOSFET) structure via frequency-dependent capacitance–voltage (C–V) and conductance–voltage (G–V) measurements9,10. Some studies even discussed the interface trap states in AlGaN/GaN Schottky-HEMT as well as MOS-HEMT but their results conclude that the trap states are mainly located at the surface interface within the dielectric or the passivation layer12,13. However, from a device point of view, characterization of the AlGaN/GaN interface would be more beneficial because this interface is directly related to carrier transport.

In this study, we tried to include all types of AlGaN/GaN interfacial trapping analysis for a better understanding. We extracted the interface trap density (Dit) between AlGaN and GaN and the deep-level/border trap density Nbt in the AlGaN barrier layer in a long-channel AlGaN/GaN HEMT fabricated on a SiC substrate. We mainly focused on the trap states inside the AlGaN layer, located at the interface and near the interface of the AlGaN/GaN, and tried to eliminate other probable interfacial trap contributing factors such as dielectric layers for passivation. We used the conventional frequency-dependent C–V and G–V characteristics to understand the interactions of the interface traps14,15. Along with these characteristics, we also investigated the deep-level/border trap behavior in the accumulation region by examining split C–V characteristics, which are typically observed in the conventional Si MOS structure16,17. Although some researchers have discussed border/bulk trap extraction with threshold voltage shift profiling, discharging-based trap energy profile technique, etc., the frequency-dependent CV method for border trap density extraction for AlGaN/GaN heterostructure is not present18,19,20. We further performed low-frequency (1/f) noise measurements as they are a highly powerful tool for analyzing the defects and impurities in semiconductor devices and because they aid in the estimation of the efficiency and reliability of these devices21.

Experimental details

Figure 1a illustrates the cross-sectional schematic and the transmission electron microscopy (TEM) image of the HEMT device used in this study. Epitaxial layers were grown on a semi-insulating 330 µm SiC substrate by metal–organic-chemical-vapor-deposition (MOCVD). Layers were deposited from bottom to top in the following order: an AlN nucleation layer, a 2.6 µm high-resistance GaN layer, a 150 nm GaN channel, and a 28 nm Al0.25Ga0.75N barrier layer. Hall measurements revealed the mobility (µn_Hall) and the sheet charge density (2DEG) to be 2200 cm2·V−1·s−1 and 9 × 1012 cm−2, respectively. Mesa isolation was carried out with Cl2 based inductively-coupled-plasma (ICP) etching to isolate the devices. Before ohmic metal deposition, the substrate was diluted with a mixture of HCl and deionized water (1:5) for 30 s to remove any kind of formed native oxide. To facilitate ohmic contact formation, a Si/Ti/Al/Ni/Au (1/25/160/40/100 nm) alloy was deposited on source and drain area using an electron beam (e-beam) evaporator and rapid thermal annealing at 830 °C was subsequently performed in N2 ambient for 30 s. The contact resistance (RC) and sheet resistance (RSH) were extracted by transmission-line-method (TLM) measurements to be 1.2 Ω·mm and 320 Ω/□ respectively. A Ti/Au (20/300 nm) padding layer was deposited using the E-beam evaporator to achieve strong probe contact. Finally, gate metal consisting of Ni/Au (20/400 nm) was also deposited using e-beam evaporator. The gate length (Lg), gate width (Wg), and source-to-drain distance (Lsd) of the fabricated devices were 14, 50, and 18 µm, respectively. All the devices had the same source-to-gate (Lsg) distance and gate-to-source distance (Lgd) of 2 µm. From the high-resolution TEM image shown in Fig. 1a, the well deposited Al0.25GaN0.75N/GaN interface can be observed. The thickness of Al0.25GaN0.75N was well around 28 nm (27.8 nm) and formed a good interface with the GaN channel layer.

Extraction model

Interface trap model

In conventional Si MOSFET devices, the conductance method is one of the most popular methods for determining the interface trap density (Dit)14,22. Typically, the interface between the dielectric and the semiconductor is analyzed for trap extraction. In our study, we applied the conductance method to our device structure. Because the Al0.25Ga0.75N barrier layer has a wide band gap (~ 4 eV) and a high dielectric constant (~ 9.4), it can act as an insulator and perform comparably to a dielectric material. The conductance method relies on the extraction of the equivalent parallel conductance (GP) from the measured frequency-dependent C–V and G–V characteristics. Figure 1b shows the equivalent circuit of a MOSFET in the depletion region, where Cit, CS and RS represents the interface trap capacitance, the semiconductor capacitance, and series resistance, respectively. The interface trap capacitance can be expressed as Cit = qDit (where q denotes the elemental charge). GP can be determined by the following equation:

Here, Cins is the insulator capacitance; ω is the angular frequency; and Cc and Gc are, respectively, the corrected measured capacitance and conductance corresponding to the series resistance RS.

Using the normalized (GP/ω)max value, we can determine the value of Dit as follows23:

Here, A denotes the device area.

The trap response of the interface states can be determined from the Shockley–Read–Hall statistics of capture and emission24:

Here, ΔE denotes the difference of energy between the conduction band EC and trap energy level ET. KB and T are the Boltzmann constant and temperature. σ, vth and Ddos represent the cross–section of traps, the average thermal velocity, and the effective density of states, respectively.

Border trap model

The distributed circuit model shown in Fig. 1c was used for the extraction of border traps16,17. It can provide information on the border trap states inside the insulator bulk with frequency-dependent C-V measurement. This model can be represented by the following first-order differential equation:

This equation has a boundary condition of x = 0, Y = jωCS, while Y being the total admittance. Nbt in the above equation denotes the density of border traps in the insulator layer.

Usually, the carriers in the channel region and the border traps in the insulator layer can exchange charge through tunneling16. The average time (τ) required for an empty trap to capture electron can be calculated as25

Here, τo denotes the time constant of the capture and emission of a trap. x denotes the distance between the interface and the trap. m* and k denote the effective mass of the Al0.25Ga0.75N layer and the attenuation coefficient respectively. The barrier height between the Al0.25Ga0.75N and the GaN channel conduction band is denoted by Eb and the reduced Plank’s constant by ħ.

τo can be characterized as

where ns, vth and σ are the electron density of the channel surface, the average thermal velocity of the electron, and the border trap cross-section area of capture/emission, respectively.

Equation 4, can be simplified into the following equation for the total capacitance, Ctot26,

Using Nbt and τo as fitting parameters, the best-fitted curve of Ctot with respect to frequency can be generated for the measured capacitance which will be discussed more in the results and discussion section.

The probing distance (Xp) of a border trap with a fixed frequency (f) while, ωτ = 1, can be described as27

Results and discussion

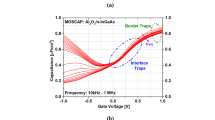

Figure 2a shows the results of the frequency-dependent C–V measurements of the Al0.25GaN0.75N/GaN HEMT where frequency dispersion is evident. Frequency dispersion can be caused by various reasons. Some of the main causes of frequency dispersion during C–V measurement are parasitic effect, lossy interfacial layer, surface roughness, and quantum mechanical confinement etc28. Among them, the most influential reason is the lossy interfacial layer of AlGaN/GaN. The trap states in the AlGaN layer are mostly the reason behind the dispersion. The frequency dispersion in the depletion region indicates that this region is the dominant region for interface traps, whereas the dispersion in the accumulation region indicates the dominant region of the border traps. We used the Nextnano simulation tool (one-dimensional Poisson–Schrodinger solver) to compare the measured and simulated capacitance with respect to a constant gate overdrive (VGS − VT), as shown in Fig. 2b. It is evident that both the measured and the simulated C–V curves are similar which indicates lower leakage current effect on the measured data. Thus, the AlGaN layer can be treated as an insulator owing to its high dielectric constant, similar to the MIS/MOS structure. Figure 2c, d show the band diagrams (determined via simulation) in the depletion and accumulation regions, respectively. In the depletion region, the interface traps above the Fermi level EF are mostly active; this causes the capture and emission of the carriers in the channel region. In the accumulation region, where EF penetrates the conduction band EC, the electrons on the surface are captured and emitted by the border traps via tunneling.

A Keysight B1500A semiconductor device analyzer and an Agilent 4384A precision LCR meter were used for all DC measurements. 1/f measurements were performed using a setup comprising battery operated SRS SR570 low-noise current preamplifier, HP 35670A dynamic signal analyzer, and a 1 Hz filter unit.

The insulator capacitance was determined by the following equation:

Here, εo is the permittivity of free space and εins is the relative permittivity of the Al0.25Ga0.75N layer. As it is known from the literature, the value of εins as calculated from ε = − 0.5x + 9.5—where x denotes the Al content of the AlxGa1−xN layer—for x = 25% is around 9.37529,30. The tensor components of AlN and GaN’s {0001} relative permittivity are linearly interpolated to obtain the relation. The parallel equivalent conductance Gp was calculated using Eq. 1 with correction of the measured capacitance and conductance for the series resistance. Figure 3b shows a plot of the parallel conductance Gp/ω versus the angular frequency ω. Dit was measured from the (Gp/ω)max peak, using Eq. 2; The extracted value of Dit using the conductance method was in the range of 2.5 × 1012 cm−2·eV−1 to 7.1 × 1012 cm−2·eV−1 which is well within the range of 1011–1014 cm−2 eV−1 for S-HEMT and MOS-HEMT from literature10,12,31. Figure 3a shows the active Dit with respect to the trap energy (ΔE), which was determined from Eq. 3. For this calculation, the frequency corresponding to (Gp/ω)max was considered. At room temperature (300 K), the average thermal velocity vth and the effective density of states (Ddos) of the GaN material were considered to be 2.6 × 107 cm·s−1 and 1.2 × 1018 cm−3, respectively31. The value of the capture cross-section σ was assumed to be 3.4 × 10−15 cm2 from the literature32. The reliability of the extracted value of Dit was determined via a theoretical calculation of the subthreshold swing (SS) using the following equation33:

The value of the SS calculated from the lowest extracted Dit was around 143 mV·dec−1, whereas the value determined by the basic I–V measurement was found to be 142 mV·dec−1 (Fig. 3c). This similarity of the measured and calculated values confirms the reliability of the extracted value of Dit.

We used the parameters in Table 1 to extract the border trap density Nbt. For the calculation of the attenuation coefficient, the effective mass of Al0.25Ga0.75N was considered to be 0.19mo (where mo denotes the electron mass at rest)34. The semiconductor capacitance CS was estimated via Nextnano simulation at an accumulation gate bias of − 3.5 V, which was the primary Nbt extraction voltage considered in this study. From Eq. 4, the best-fitted capacitance curves were obtained at − 3.5 V under consideration of Nbt and τo as variable fitting parameters. The best-fitted curve was obtained at Nbt = 1.5 × 1019 cm−3·eV−1 and τo = 1 × 10−12 s, as shown in Fig. 4a. Here, CM denotes the capacitances measured at various applied frequencies at − 3.5 V and Ctot represents the fitted curve. The spatial distribution of Nbt as a function of both the applied VGS and the probing distance into the Al0.25Ga0.75N layer from the Al0.25Ga0.75N/GaN interface is shown in Fig. 4b. The Nbt values were extracted at various applied voltages at a particular applied frequency. The probing depth into the Al0.25Ga0.75N layer from the interface was calculated by Eq. 10 using different τo values associated with the Nbt values. Because the border traps exhibit more dominant characteristics at lower frequencies, we employed a low frequency of 10 kHz to extract the probing depth. With an increase in VGS, the Fermi level EF tended to penetrate to a greater depth into the conduction band EC. As a result, more electrons tended to tunnel into the deep-level traps. As all parameters except τo were fixed, τo showed an inverse relation with the probing depth.

1/f noise measurements were performed by varying the gate voltage VGS and fixing the drain bias VDS at 0.5 V. Figure 5a shows the normalized SID/ID2 (drain current noise spectral density) with respect to frequency up to 104 Hz under varying VGS from the linear region. It is evident that as VGS increased, and the device transitioned from weak inversion to strong inversion, noise level (SID/ID2) decreases. Plotting of the normalized SID/ID2 as a function of ID (drain current) provided results that were more explanatory. Figure 5b shows a plot of the normalized SID/ID2 (blue spheres) as a function of ID at a frequency of 10 Hz. The channel carrier trapping phenomenon of the gate dielectric can be explained using the carrier number fluctuation (CNF) model by the following equations21,35,36:

Here, SVfb denotes the flatband voltage power spectral density; kT, the thermal energy; WL, the channel area; Cd, the dielectric capacitance; f, the frequency; and Nt, the bulk/border trap density. λ denotes the tunneling attenuation distance of the dielectric, which is expressed as λ = [4π(2 m*ФB)1/2/h]−1, where ФB is the dielectric barrier height37. According to the CNF model, the terms SID/ID2 and (gm/ID)2 vary in similar ranges with the drain current or gate voltage. From Fig. 5b, it is evident that both SID/ID2 (blue spheres) and (gm/ID)2 (red line) vary similarly over several decades under varying ID. The SVfb value was calculated to be 10−10 V2·Hz−1 from Eq. 13. Using Eq. 14, we then calculated the border trap density Nt to be around 1.3 × 1019 cm−3·eV−1; this value is of a similar level to the values of the border trap density Nbt extracted from the distributed circuit model and well comparable to the data from literature of 1018–1022 cm−3 eV−120,36,38.

Conclusion

Unlike previous studies, which focused mainly on the insulator/AlGaN interface for trap extraction, the present study attempted to investigate the AlGaN/GaN interface for this purpose. We used modified versions of conventional MOS trap extraction methods to extract the interface trap density Dit and border trap density Nbt of the Al0.25Ga0.75N/GaN interface. We performed the extractions by considering the Al0.25Ga0.75N layer to be comparable to the insulator of the MOS structure on account of the relatively high dielectric constant of the former. The Dit value extracted by the conductance method was in the range of 2.5 × 1012 cm−2·eV−1 to 7.1 × 1012 cm−2·eV−1, and the Nbt value extracted using the distributed circuit model was 1.5 × 1019 cm−3·eV−1 with τo of 1 × 10−12 s. The border trap density Nt extracted using the CNF model via 1/f noise measurements was 1.3 × 1019 cm−3·eV−1 (same level as the extracted value of Nbt), which confirmed the validity and reliability of our trap extraction method.

Data availability

The datasets generated during and/or analysed during the current study are available from the corresponding author on reasonable request.

Change history

02 December 2021

A Correction to this paper has been published: https://doi.org/10.1038/s41598-021-02854-3

References

Sheppard, S. T. et al. High-power microwave GaN/AlGaN HEMT’s on semi-insulating silicon carbide substrates. IEEE Electron Device Lett. 20, 161–163 (1999).

Brown, D. F. et al. W-band power performance of AlGaN/GaN DHFETs with regrown n+ GaN ohmic contacts by MBE. Tech. Dig.—Int. Electron Devices Meet. IEDM https://doi.org/10.1109/IEDM.2011.6131584 (2011).

Algan, G. et al. 60-nm GaN/AlGaN DH-HEMTs with 1.0 Ω·mm Ron, 2.0 A/mm Idmax, and 153 GHz fT 6–7.

Shi, J., Eastman, L. F., Xin, X. & Pophristic, M. High performance AlGaN/GaN power switch with HfO2 insulation. Appl. Phys. Lett. 95, 7–10 (2009).

Liu, Z. H. et al. Improved linearity for low-noise applications in 0.25-μm GaN MISHEMTs using ALD Al2O3 as gate dielectric. IEEE Electron Device Lett. 31, 803–805 (2010).

Mimila-Arroyo, J., Jomard, F. & Chevallier, J. Improvement of AlGaN/GaN/Si high electron mobility heterostructure performance by hydrogenation. Appl. Phys. Lett. 102, 092104 (2013).

Parish, G. et al. AlGaN/AlN/GaN high electron mobility transistors with improved carrier transport. Conf. Optoelectron. Microelectron. Mater. Devices, Proc., COMMAD https://doi.org/10.1109/COMMAD.2004.1577484 (2005).

Rossetto, I. et al. Evidence of hot-electron effects during hard switching of AlGaN/GaN HEMTs. IEEE Trans. Electron Devices 64, 3734–3739 (2017).

Lu, X., Yu, K., Jiang, H., Zhang, A. & Lau, K. M. Study of interface traps in AlGaN/GaN MISHEMTs using LPCVD SiNx as gate dielectric. IEEE Trans. Electron Devices 64, 824–831 (2017).

Ma, X. H. et al. Quantitative characterization of interface traps in Al2O3/AlGaN/GaN metal-oxide-semiconductor high-electron-mobility transistors by dynamic capacitance dispersion technique. Appl. Phys. Lett. 103, 2012–2015 (2013).

Asubar, J. T. et al. Impact of oxygen plasma treatment on the dynamic on-resistance of AlGaN/GaN high-electron-mobility transistors. Appl. Phys. Express 8, 111001 (2015).

Liu, W. L., Chen, Y. L., Balandin, A. A. & Wang, K. L. Capacitance–voltage spectroscopy of trapping states in GaN/AlGaN heterostructure field-effect transistors. J. Nanoelectron. Optoelectron. https://doi.org/10.1166/jno.2006.212 (2006).

Zhu, J., Ma, X., Hou, B., Chen, W. & Hao, Y. Investigation of trap states in high Al content AlGaN/GaN high electron mobility transistors by frequency dependent capacitance and conductance analysis. AIP Adv. 037108, 15–17 (2014).

Engel-Herbert, R., Hwang, Y. & Stemmer, S. Comparison of methods to quantify interface trap densities at dielectric/III-V semiconductor interfaces. J. Appl. Phys. 108, 124101 (2010).

Amir, W., Kim, D. H. & Kim, T. W. Comprehensive analysis of quantum mechanical effects of interface trap and border trap densities of high-k Al2O3/In0.53Ga0.47As on a 300-mm Si substrate. IEEE Access 8, 211464–211473 (2020).

Yuan, Y. et al. A distributed model for border traps in Al2O3-InGaAs MOS devices. IEEE Electron Device Lett. 32, 485–487 (2011).

Chen, H. P. et al. Interface-state modeling of Al2O3–InGaAs MOS from depletion to inversion. IEEE Trans. Electron Devices 59, 2383–2389 (2012).

Gao, R. U. I. et al. A fast extraction method of energy distribution of border traps in AlGaN/GaN MIS-HEMT. IEEE J. Electron Devices Soc. 8, 905–910 (2020).

Zhu, J. et al. Threshold voltage shift and interface/border trapping mechanism in Al2O3/AlGaN/GaN MOS-HEMTs 8–11 (2018).

Im, K.-S., Lee, J.-H., Choi, Y. J. & An, S. J. Effects of GaN buffer resistance on the device performances of AlGaN/GaN HEMTs. MDPI Cryst. 10, 1–7 (2020).

Ghibaudo, G., Roux, O., Nguyen-Duc, C., Balestra, F. & Brini, J. Improved analysis of low frequency noise in field-effect MOS transistors. Phys. Status Solidi 124, 571–581 (1991).

Lin, H. C., Wang, W. E., Brammertz, G., Meuris, M. & Heyns, M. Electrical study of sulfur passivated In0.53Ga0.47As MOS capacitor and transistor with ALD Al2O3 as gate insulator. Microelectron. Eng. 86, 1554–1557 (2009).

Nicollian, E. H. & Brews, J. R. MOS (Metal Oxide Semiconductor) Physics and Technology (Wiley, 1982).

Shockley, W. & Read, W. T. Statistics of the recombinations of holes and electrons. Phys. Rev. 87, 835–842 (1952).

Heiman, F. P. & Warfield, G. The effects of oxide traps on the MOS capacitance. IEEE Trans. Electron Devices ED-12, 167–178 (1965).

Vais, A. et al. An analytical model of MOS admittance for border trap density extraction in high-k dielectrics of III–V MOS devices. IEEE Trans. Electron Devices 63, 4707–4713 (2016).

Rahman, M. M., Kim, J. G., Kim, D. H. & Kim, T. W. Border trap extraction with capacitance-equivalent thickness to reflect the quantum mechanical effect on atomic layer deposition high-k/In0.53Ga0.47As on 300-mm Si substrate. Sci. Rep. 9, 1–12 (2019).

Zhao, C., Zhao, C. Z., Werner, M., Taylor, S. & Chalker, P. Dielectric relaxation of high-k oxides. Nanoscale Res. Lett. 8, 1 (2013).

Zhao, J. Z. et al. Determination of the relative permittivity of the AlGaN barrier layer in strained AlGaN/GaN heterostructures. Chin. Phys. B 18, 3980–3984 (2009).

Li, L. et al. On the hole injection for III-nitride based deep ultraviolet light-emitting diodes. Materials (Basel) 10, 1221 (2017).

Kordoš, P., Stoklas, R., Gregušová, D. & Novák, J. Characterization of AlGaN/GaN metal-oxide-semiconductor field-effect transistors by frequency dependent conductance analysis. Appl. Phys. Lett. 94, 1–4 (2009).

Zhang, K. et al. Trap states in InAlN/AlN/GaN-based double-channel high electron mobility transistors. J. Appl. Phys. 113, 10–25 (2013).

Lyu, J.-S. A new method for extracting interface trap density in short-channel MOSFETs from substrate-bias-dependent subthreshold slopes. ETRI J. 15, 10–25 (1993).

Kurakin, A. M. et al. Quantum confinement effect on the effective mass in two-dimensional electron gas of AlGaN/GaN heterostructures. J. Appl. Phys. 105, 073703 (2009).

Nanowire, G., Bae, Y., Ghibaudo, G. & Cristoloveanu, S. 1/f-noise in AlGaN/GaN nanowire omega-FinFETs. IEEE Electron Device Lett. 38, 252–254 (2017).

Vodapally, S. et al. Comparison for 1/f noise characteristics of AlGaN/GaN FinFET and planar MISHFET. IEEE Trans. Electron Devices 64, 3634–3638 (2017).

Yin, R. et al. Correlation between border traps and exposed surface properties in gate recessed normally-off Al2O3/GaN MOSFET. Appl. Phys. Lett. 112, 2–7 (2018).

Jeon, D. Y. et al. Effects of series resistance and interface properties on the operation of AlGaN/GaN high electron mobility transistors. Microelectron. Eng. 199, 40–44 (2018).

Acknowledgements

This work was supported by a National Research Foundation of Korea (NRF) grant funded by the Korean government (MSIP; Ministry of Science, ICT and Future Planning, NRF- 2019R1A2C1009816 and NRF-2019M3F5A1A01076973).

Author information

Authors and Affiliations

Contributions

W.A. conducted most of the characterizations and wrote the manuscript including the figures. J.-W.S. and K.-Y.S. helped in device fabrication. J.-M.K., C.-Y.C. and K.-H.P. helped in the wafer growth processing. T.H., T.T., H.S., and H.M. provided epi structure and helped in overall quality check and review of the paper. T.-W.K. initiated the work and supervised the entire process. All authors analysed and discussed the results.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher's note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

The original online version of this Article was revised: The original version of this Article contained an error in the Acknowledgments section. “This work was supported by the National Research Foundation of Korea (NRF) grant funded by the Korean government (MSIP; Ministry of Science, ICT and Future Planning, NRF- 2019R1A2C1009816 and NRF- 2019M3F5A1A01076973) and Nano Material Technology Development Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Science, ICT and Future Planning (2009-0082580).” now reads: “This work was supported by a National Research Foundation of Korea (NRF) grant funded by the Korean government (MSIP; Ministry of Science, ICT and Future Planning, NRF- 2019R1A2C1009816 and NRF-2019M3F5A1A01076973).”

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Amir, W., Shin, JW., Shin, KY. et al. A quantitative approach for trap analysis between Al0.25Ga0.75N and GaN in high electron mobility transistors. Sci Rep 11, 22401 (2021). https://doi.org/10.1038/s41598-021-01768-4

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-021-01768-4

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.