Abstract

We successfully demonstrated a detailed and systematic enhancement of organic field effect transistors (OFETs) performance using dithienothiophene (DTT) and furan-flanked diketopyrrolopyrrole based donor–acceptor conjugated polymer semiconductor namely PDPPF-DTT as an active semiconductor. The self-assembled monolayers (SAMs) treatments at interface junctions of the semiconductor–dielectric and at the semiconductor–metal electrodes has been implemented using bottom gate bottom contact device geometry. Due to SAM treatment at the interface using tailored approach, the significant reduction of threshold voltage (Vth) from − 15.42 to + 5.74 V has been observed. In addition to tuning effect of Vth, simultaneously charge carrier mobility (µFET) has been also enhanced the from 9.94 × 10−4 cm2/Vs to 0.18 cm2/Vs. In order to calculate the trap density in each OFET device, the hysteresis in transfer characteristics has been studied in detail for bare and SAM treated devices. Higher trap density in Penta-fluoro-benzene-thiol (PFBT) treated OFET devices enhances the gate field, which in turn controls the charge carrier density in the channel, and hence gives lower Vth = + 5.74 V. Also, PFBT treatment enhances the trapped interface electrons, which helps to enhance the mobility in this OFET architecture. The overall effect has led to possibility of reduction in the Vth with simultaneous enhancements of µFET in OFETs, following systematic device engineering methodology.

Similar content being viewed by others

Introduction

A very low cost, low powered and flexible integrated circuits are some of the important basic requirement for the future advanced technologies including internet of things (IoT), robotics, wearable electronics, and fourth industrial revolution. In order to realize the real world applications such as actuators and sensors in robots1,2, wearable bio electronics and healthcare3, the overall performance of OFETs should be higher. With future applicability in such high-end applications, and for OFETs overall effective diffusion, there has been an increasing necessity of understanding the possible reasons for the enhancement of mobility values and controlled reduction of Vth simultaneously, upon following device engineering methodology. Once the low powered OFET devices, with enhanced speed of operation are achieved, the reasons for such a change in phenomenon needs to be analysed for better standardizations. This can be more effectively possible, when a similar class of co-polymer is chosen, and the behavioural change is re-proven with systematic study. Additionally, the physics behind of phenomenon for such change must be understood for more clarity and utilization. Accordingly, in our previous work we have shown the methodology, which showcases that effective SAM treatment at interfaces can lead to enhanced mobility, and reduced threshold voltage4. In this work, we highlight that achievement of similar behaviour upon surface treatment is repeatable with a different copolymer. Along with that, the reasoning for the such a change in device behaviours, due to varied extent of trap states upon surface treatment in discussed.

The essential surge, in the performance of the OFETs can be modulated via thin film interface engineering using chosen organic semiconductor material5. Accordingly, there are various ways to enhance the overall OFETs performance, including the development of new organic donor–acceptor semiconductors6,7,8,9,10, relevant semiconductor doping11, implant doping12, use of high dielectric constant materials13,14, various material deposition processes15,16, and use of self-assembled monolayers (SAM) treatments4,5,17,18. In most of the above-mentioned strategies, it has been highlighted that charge carrier transport in polymer thin films is largely influenced by the structural and energetic disorders. These are generally introduced into the films and/or device interfaces19. Mainly, the interaction between the dielectric layer and the semiconductor thin films has a direct impact on the orientation of the molecular segments in the channel region of the OFETs and thereby such interaction should be feasible to support efficient charge transport across channel13. Accordingly, the interaction between dielectric and semiconductor layer is widely addressed through the appropriate choices of the SAM material, and its effective treatment on the dielectric surface before the semiconductor material is deposited on top of dielectric surface20. Among many possible silanes based SAM treatments on the SiO2 surface, octyl trichlorosilane (OTS) is one of the most widely used21,22,23 due to its appropriate alkyl chain length which enhances alkyl–alkyl interdigitation between the SAM alkyl chain and alkyl chain substituted on the conjugated backbone motifs.

The interface engineering to optimize the charge injecting contacts becomes important to realize high performing OFETs. SAM treatments like PFBT on the surface of the source and drain metal electrodes have an impact on the charge injection possibilities, because of their polar nature. PFBT tend to shift the position of the work-function based on the terminating group present in its backbone4. This will make the charge injection from the respective electrode adjustable based on the band gap of the respective organic semiconductor material24. Adjusting the work function of an electrode is critical to modulate the charge transport and electrical performance because the threshold voltage (Vth) shifts in OFETs is influenced by the intrinsic electric field produced by the permanent dipole of the SAM layers and by the electrochemical reaction between surface functional groups and the semiconductor molecules25. Basically, both such modifications can variably influence the crystallization process of the active layer, in terms of molecular packing and grain boundary sizes independently. Thereby, the study of their combined effect with proper reasoning about the underlying physics, on some of those high performing organic semiconductor based OFETs has become essential24,25,26,27.

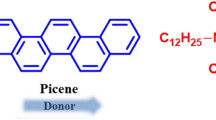

In our previous report, we have demonstrated that by introducing long-branched alkyl groups to the donor–acceptor (D–A) polymers, their solution processability can be improved and the molecular packing in the film state can be reduced21. This design, which has been intensively studied, leads to a significant enhancement of hole mobility approaching level of (12 cm2 V−1 s−1)28and even exceeding (20 cm2 V−1 s−1)29. Among reported various donor–acceptor (D–A) based copolymers, recently diketopyrrolopyrrole (DPP) dye incorporated molecular and polymeric D–A materials have illustrated outstanding performance in transistor based various organic electronic devices including stretchable transistors, ambipolar transistors, phototransistors, chemical sensors and so on30. The lower cost, easy synthesis, solution processability, ink forming capability ample scope for chemical structural modification, enhancing π–π stacking due to aromatic fused lactam structure makes DPP building block as a star conjugated moiety. The energy levels consisting of both the highest occupied molecular orbital (HOMO) and lowest unoccupied molecular orbital (LUMO) and its subsequent band gap can be systematically tuned either by varying flanking groups attached to the DPP core or by incorporating comonomers (which are either strong/weak electron donor or acceptor) in the main conjugated backbones. Either holes or electrons can be injected into their respective HOMO or LUMO determines their nature either as p-type or n-type materials for transistor. If the both holes and electrons are getting injected simultaneously into their HOMO and LUMO’s due to lower band gap nature, then they can be potential materials for ambipolar transistors since their energy levels are close to the work function of metal electrode. There are numerous numbers of flanking groups such as furan31, thiophene32, selenophene33, pyridine34,35 thiazole36, thienothiophene35 and naphthalene have been used in the literature for the polymer synthesis. Among the reported DPP molecular and polymer semiconductors, thiophene flanked DPP is one of the most widely studied building block37. Taking benefits of biodegradability of furan and its higher solubility upon combining with large extended conjugated comonomer blocks, recently, furan flanked DPP (DPPF) materials have attracted great deal of attention for designing solution processable organic semiconductor materials with high performances38,39.

Compared to DPPT39,40, DPPF has smaller oxygen heteroatom present in the furan ring and shorter due to this, the C = O bond may lead to less steric hindrance between the DPP unit and the neighbouring aryl group and might allow more co-planar structure41. Herein, a D–A polymer based on DPPF as acceptor and DTT as a donor was synthesized and investigated as active channel semiconductor for OFETs devices.

In our current work, we study the effects altered trap density upon the surface modifications on the PDPPF-DTT based OFETs. To understand the reasoning of enhancement in mobility after OTS treatment, we summarize its correlation with the observation from the thin film Atomic Force Microscopy (AFM), and thin film X-Ray Diffraction (XRD) analyses. The correlation of enhancement of mobility and reduction of Vth upon these surface treatments is explained through the energy level band diagram. XRD analysis confirms that, after OTS treatment, the morphology of the semiconducting layer improved which help to increase the mobility. Then we showcase that the interface traps mainly affect the gate field, which in turn control Vth of the OFET device. This effect leads to the mobility governance by both the fields, and the morphology control by SAM treatment, on this type of polymers based OFETs.

Results and discussion

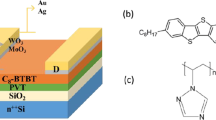

Figure 1a shows molecular structures PDPPF-DTT polymer whereas Fig. 1b,c shows the molecular structures of OTS and PFBT SAMs materials used for SiO2 and S/D contact treatment, respectively. The systematic devices structures are planned based on the lines of those discussed in our previous work, using PDPPT-DTT4 polymer. In this study, we utilise the PDPPF-DTT version of the polymer. The OFET device structure are categorized into three types. Firstly, as in Fig. 1d, we fixed the bare (untreated) SiO2 and untreated S/D OFETs as the reference (Ref.) device type. Secondly, we consider Fig. 1d. (1) as the OFETs device type whose SiO2 was treated with OTS leading to a hydrophobic surface with a contact angle of 106º, on this device type there is not any PFBT treatment done. Lastly, we consider Fig. 1d. (2) as the OFETs device type wherein, along with the OTS treatment on SiO2, there is additional PFBT treatment of gold (Au) S/D electrode.

The chemical structures of (a) PDPPF-DTT, (b) OTS, (c) PFBT, and (d) the device structures of OFETs analysed. (Ref) is a considered reference device, wherein, there is not any kind of SAM treatment applied to SiO2 and Au source–drain (S/D) contacts. Device mentioned as (1) is with OTS treated SiO2, and device mentioned (2) is the one with both PFBT and OTS treatment at Au and SiO2 surface respectively. Finally (e) and (f) describe average µFET and Vth on different device types respectively.

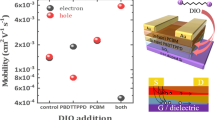

Figure S1(a), Fig. S1(b), and Fig. S1(c) shows the 3-dimensional chemical structures of PDPPF-DTT polymer, along with that of OTS, PFBT respectively. Figure 1e,f describes the variation in mobility and threshold voltages in all three device architectures. Which clearly depicts that upon OTS and PFBT treatment, PDPPF-DTT polymer based OFET device performance is better both in terms of µFET enhancement and lowered Vth.

We characterize the bare (untreated) SiO2 and OTS treated SiO2 surfaces in terms of hydrophilicity and morphology of the deposited active semiconductor thin film. Fig. S8(a) and Fig. S8(b) shows the contact angle measurement for bare and OTS treated SiO2 surface, respectively. The contact angle, as discussed increases from 28° to 106° after OTS treatment, this clearly indicates the formation of hydrophobic surface after OTS treatment. This aids in the process of reduction of hysteresis in transfer characteristics and lowered trap density in OTS treated surfaces and discussed in the further section below. AFM images of PDPPF-DTT thin film grown over bare surface is illustrated in Fig. 2a, Fig. S6, and Fig. S8(c). The one on OTS treated SiO2 surface is illustrated in Fig. 2b, Fig. S7, and Fig. S8(d). The film is annealed at 150 °C for 30 min in both the cases directly on the top of the hot plate in an N2 environment. Images captured in tapping mode by scanning the 5 µm × 5 µm surface area. The RMS average nominal height of the film grown over bare SiO2 surface is 3.68 nm and is 4.42 nm for the film grown over OTS treated surfaces. Such an mild increased film height on average, in conjunction with increased contact angel on OTS treated SiO2 provides a better interface between the polymer and the dielectric interface42, promoting the molecular ordering of the overlaid channel semiconductor43. Thus, leading to enhanced field-effect mobilities after OTS treatment in PDPPF-DTT based OFETs.

After the systematic characterization of the bare and OTS treated SiO2 surfaces in terms of its hydrophobic nature and thin film morphology, we performed Grazing Incident Diffraction (GID) for PDPPF-DTT film grown on bear and OTS treated SiO2 surfaces, after annealed at 150 °C for 30 min to remove the solvent residues. Figure 3 shows the GID patterns of 2θ ranges between 1 to 40°. The relative broad diffraction peaks represent the nano-crystalline nature of the formed phase. Fig. S9 shows the diffraction peaks in GID on untreated Si/SiO2 substrate, without any polymer deposited is at around 53°. Thereby, the peaks at 4° and 22° are emerging from the PDPPF-DTT polymer. For the same polymer, the hump around 22° is discussed38. For further clarity the diffraction peaks around 4° and 22° on both patterns were fitted using Pseudo-Voigt44 type peaks phase in DIFFRAC.TOPAS v6 software45. The refined peak positions and full width half maxima (FWHM) are summarised in Table S1. The FWHM of the first peak between 3.1 to 5.5° 2θ are reduced from 0.81 to 0.70° 2θ upon OTS treatment; the FWHM of the second peak between 13 to 31° 2θ are reduced from 8.18 to 6.35° 2θ upon OTS treatment. Particularly in DPP class of polymers such a FWHM narrowing of the peaks generally implies that the lamellar structures have become considerably more uniform, which leads to a more uniform distribution of the d-spacing46. D-spacing can be calculated from peak positions following the Bragg’s law: d = λ/(2 Sinθ), where ‘d’ stands for the interplane spacing, ‘λ’ represents the radiation wavelength 1.54059 Å in our experiment, ‘θ’ represents the half of the peak position 2θ in the XRD measurement. Following OTS treatment, d-spacing values of these two peaks increased from 20.26 to 20.58 Å, and from 3.95 to 4.01 Å, respectively, indicating a larger unit cell. Hence, comparatively after OTS treatment, larger crystallite packing structure was formed, with increased nano-crystal size. This in turn leads to the enhancement of the increased mobility values from 9.49 × 10−4 to 3.77 × 10−2 cm2/Vs.

OFET performance evaluation of PDPPF-DTT

After thin film characterization of the PDPPF-DTT semiconducting film grown over bare and OTS treated SiO2 surface, we fabricated the complete OFET structure and the electrical characteristics taken out as output (IDS − VDS) and transfer curves (IDS − VGS). Figure 4a,c shows the transfer and output characteristics for OFETs fabricated bare SiO2 surfaces (Ref devices), while Fig. 4b,d shows the transfer and output characteristics for OFETs fabricated on OTS treated SiO2 surfaces (Type 1 devices). Log IDS versus VGS plots of PDPPF-DTT based OFETs on Ref and device type 1 are shown in Fig. S2(a) and Fig. S2(b), and that device of type 2 are shown in Fig. S3.

The basic equations explaining operation of OFETs in the linear, and in the saturation region is shown in the supplementary information, as per equation S1, and S2 respectively. The µFET can be extracted from the transfer characteristics of (IDS vs. VGS), as in equation (S3) by plotting the square root of the saturation current as a function of VGS. Further the parameter SS narrates the important turn-on characteristics of the devices. This parameter is defined as the rate at which IDS varies (in terms of decades) with VGS, while the device is operating at the subthreshold region. Thereby, it is extracted by fitting a line to the steepest portion of the subthreshold region, followed by taking inverse of obtained value, as narrated in equation (S4). All the device parameters for both cases are summarized in Table 1. This table showcases the significant enhancement in the mobility values of this polymer increases from 9.49 × 10−4 to 3.77 × 10−2 cm2/Vs, after OTS treatment. The obtained mobility values are slightly lower then PDPPT-DTT4, due to changes in the flanking group. The increased performance after the OTS Treatment can be attributed to enhanced crystallinity upon OTS treatment, confirmed by X-ray diffractogram and due increase in thin film surface roughness of the PDPPF-DTT from 3.68 nm on bare SiO2, to 4.42 nm after OTS treated SiO2.

Next, the Vth changes from − 15.42 to − 15.80 V after OTS treatment. The extent of change in Vth is larger than that observed in PDPPT-DTT4. Table 1. showcases the onset threshold voltage values and the average of three different OFET devices fabricated in a single substrate under similar conditions. To investigate the reasons, change in Vth, we measured hysteresis in transfer characteristics for both, bare and OTS treated SiO2 surfaces. Hysteresis decrease after OTS treatment. This is measured by calculating the change in Vth in two cycles of the hysteresis. We calculated the trap density (\(N_{Trap}\)) in each case by using the following equation:47

wherein \(C_{i}\) is dielectric capacitance and \(q\) is an electronic charge. We obtained the trap density for bare and OTS treated OFET devices are 2.73 × 1011 cm−2 and 2.23 × 1011 cm−2, respectively. This reduced trap density confirms the good quality dielectric/semiconductor interface formation. But, on the other hand, the field due to trapped electron charges play an important role to control the net charge density in the OFET channel. Singh et. al studied the role of electron traps and their control over Vth in PVP/TIPS-pentacene based solution-processed OFETs. The field which arises due to electron traps at dielectric/semiconductor interface enhance the gate field, and hence leading to the reduction Vth47,48,49. Field due to electron traps and their dynamics at dielectric–semiconductor interface is discussed by drain current transient measurements in48,49 and is schematically demonstrated in Fig. S5.

Further, we used the PFBT treatment of Au S/D electrodes over OTS treated SiO2 surfaces just before the deposition of PDPPF-DTT semiconductor film. We measured the work-function of Au by Photo-Electron Spectroscopy in Air (PESA). Riken AC-3 was used as the measuring system as showcased in Fig. S4. It was found the work function changes from 4.76 to 5.49 eV after PFBT treatment. Thereby, reducing the injection barrier between the electrode and semiconductor interface. In our case, the reduction in barrier height takes place from earlier ∆H1 = 0.59 eV to ∆H2 = 0.14 eV as show in Fig. 6a without PFBT treated Au, and in Fig. 6b with PFBT treated Au, respectively. This is consistent with previous OFET studies24,27,50,51.

Figure 5a,b shows the transfer and output characteristics for OFETs fabricated on PFBT and OTS treated SiO2 surfaces (Type 2 devices). After PFBT treatment, mobility increases up to 0.182 cm2/Vs and Vth decreases to + 5.74 V. Both, mobility and Vth significantly change after PFBT treatment in comparison to bare and only OTS treated SiO2 surfaces. The obtained highest charge carrier mobility of 0.182 cm2/Vs for PDDPF-DTT upon OTS and PFBT dual treatment is slightly lower than earlier reported value and it could be attributed with different device geometry and interface effect. In our earlier report, we used top contact bottom gate devices but herein first time we used bottom gate bottom contact devices. Batch to batch variation in molecular weight and polydispersity of synthesized polymer may hamper on the performance and this is one of the major drawbacks of polymers compared to well defined small molecules or oligomers which has single molecular weight. In OFET devices, it has been reported that the charge carrier densities and the channel conductance could be strongly affected by the charge carrier injection barrier.

The tuning from negative Vth towards positive has been also observed in other types of organic semiconductor where PFBT was used as an interfacial layer with Au as source and drain electrode27. The significant increase in mobility in these type 2 devices (PFBT over OTS treated SiO2 surface) is expected to reduce the contact resistance after PFBT treatment. Few research groups52,53 reported the effect of contact resistance on charge carrier mobility for the bottom and top contact OFET geometry, lower contact resistance aids in to increased mobility.

Upon PFBT treatment average Vth reduces from − 15.42 to 5.74 V due reduced barrier height simultaneously increasing the mobility values. This reduction in Vth is significantly lower in comparison to bare and only OTS treated SiO2 surfaces. Our study points to significance of introducing traps in a selective manner that takes advantage of the presence of dipoles and the attendant electric field produced by them that can improve dissociation of both singlet and charge transfer excitons in organic devices54,55,56. Which is most recently debated by an in depth study by Abdu-Aguye et al.57. Thereby, we studied hysteresis in transfer characteristic for these type 2 devices as shown in Fig. 5a. The large counter—clockwise hysteresis has been observed. We calculated the trap density using Eq. (1). We achieve the trap density for these type 2 devices 6.62 × 1011 cm−2, which is very high in comparison to Ref. device, type 1 having values 2.73 × 1011 cm−2, and 2.23 × 1011 cm−2 respectively. The field occurred due to trapped interface electrons, aid in the process of enhancing the gate field, thereby causes charge accumulation at lower voltage (5.74 V in this case). This in turn thereby decreases Ion/Ioff ratio upon PFBT treatment (Fig. 6)12.

Conclusions

In summary, following our work in4, we have optimised PDPPF-DTT polymer based p-type BGBC OFETs. SAM treatment was effectively done at dielectric layer– semiconductor and metal–semiconductor interfaces. Firstly, OTS treatment tuned the dielectric interface and enhanced crystallinity of the semiconducting thin film due to which highest obtained mobility increased by around two order of magnitude. Secondly, the injection barrier between Au S/D electrode and HOMO of the PDPPF-DTT polymer reduced by PFBT treatment, which further aided to enhance the highest obtained mobility of up to 0.18 cm2/Vs. At the same time, PFBT treatment increase the hysteresis in transfer characteristics, and estimated in terms of high electron trap density (6.62 × 1011 cm−2), which reduce Vth by controlling the field in channel from − 15.42 to 5.74 V. The positive shift in case of PDPPT-DTT4 was only up to 1 V, but in case of PDPPF-DTT it up to 5.74 V. Thereby, enhancing the performance further toward more positive value. Thereby we demonstrate a systematic possibility of reduction of the Vth with simultaneous enhancement in the mobility by effectively controlling the interface interaction phenomenon for the case of PDPPF-DTT.

Experimental section

The BGBC devices were-fabricated on p++ highly doped silicon substrate with SiO2 as the dielectric layer with thickness of 200 nm, which was thoroughly cleaned by placing the substrates in Piranha solution, and heat at 80 °C for 10 min. Remove the Piranha solution and rinse the substrates with deionized (DI) water for three times. Sonicated with DI water, toluene, and isopropyl alcohol (IPA) for 10 min each in that order. Bake at 100 °C for 1 h. Exposure of the Si–SiO2 substrates to ethanol vapour at 150 °C. UV-Ozone (UV/O3) treatment for 10 min58. OTS treatment was performed by placing the cleaned Si–SiO2 substrates in OTS-chloroform 1:10 (500 µl/5 ml) solution for 6 h, after which the substrates were rinsed with the chloroform solvent, the obtained contact angle was (106° ± 2°). Bottom contact S/D Au metal of 70 nm-thick was deposited using the thermal vacuum deposition chamber. The channel length and channel width were 100 µm and 1.5 mm respectively, their deposited values was measured using laser microscope imaging, and the values obtained where used during measurement and further analysed4.

For devices requiring PFBT treatment, prior to spin coating of the organic semiconductor layer, the Au based source and drain electrode surfaces were modified accordingly. This PFBT Au modification was done by immersing the substrates in a 30 mM solution of PFBT in isopropanol for 5 min. Post which they were properly rinsed with pure isopropanol59. Au source–drain work function changes after PFBT treatment, was measured by Photo-Electron Spectroscopy in Air (PESA). For this measurement Riken AC-3 equipment was utilized.

During solution preparation PDPPF-DTT was used a solute in chloroform at ratio of 7 mg/ml and solution was prepared. During the same it was the magnetically stirred at 300 rpm for 20 min. Post which the formed solution was spin coated on the cleaned and appropriately treated substrates at 1000 rpm for 60 s, which was immediately followed by annealing them at 150 °C for 30 min. Then in the in the nitrogen environment, all the fabricated devices were characterized using Keithley 4200-SCS semiconductor parameter analyser. For thin film thickness measurement, the Dektak thickness profilometer was used. Bruker AFM analyser was the equipment used for thin film surface AFM analysis. Thin film XRD were measured in Rigaku SmartLab (CuKα Long Fine Focus Tube working at 40 kV 40 mA) in Grazing Incident Diffraction (GID) geometry. The 0.1 mm thick parallel beam grazing incident into thin film surface at 0.3°, taking surface information only. A 0.228° equatorial soller was used on the secondary side to allow only parallel beam go into a Hypix3000 detector working in 0D mode. 5° axial soller slit was used on the primary side. The data was scanned from 1° to 90° − 2θ, at 0.02° step size at scan speed 2° per minutes, by just scanning the detector in 2θ mode. Further, the electrical characteristics of the fabricated OFET were measured using a semiconductor parameter analyser in the N2 Glove Box Environment.

References

Zang, Y., Zhang, F., Huang, D., Di, C.-A. & Zhu, D. Sensitive flexible magnetic sensors using organic transistors with magnetic-functionalized suspended gate electrodes. Adv. Mater. 27, 7979–7985 (2015).

Xie, M. et al. Flexible multifunctional sensors for wearable and robotic applications. Adv. Mater. Technol. 4, 1800626 (2019).

Surya, S. G. et al. Organic field effect transistors (OFETs) in environmental sensing and health monitoring: a review. TrAC Trends Anal. Chem. 111, 27–36 (2019).

Patil, B. B. et al. Reduced threshold voltages and enhanced mobilities in diketopyrrolopyrrole-dithienothiophene polymer based organic transistor by interface engineering. n/a.

Kim, C.-H. et al. Decoupling the effects of self-assembled monolayers on gold, silver, and copper organic transistor contacts. Adv. Mater. Interfaces. 2, 1400384 (2015).

Cho, M. J. et al. A high-mobility terselenophene and diketopyrrolopyrrole containing copolymer in solution-processed thin film transistors. Chem. Commun. (Camb.). 49, 7132–7134 (2013).

Huang, J. et al. Diazaisoindigo-based polymers with high-performance charge-transport properties: from computational screening to experimental characterization. Chem. Mater. 28, 2209–2218 (2016).

Mei, J., Diao, Y., Appleton, A. L., Fang, L. & Bao, Z. Integrated materials design of organic semiconductors for field-effect transistors. J. Am. Chem. Soc. 135, 6724–6746 (2013).

Allard, S., Forster, M., Souharce, B., Thiem, H. & Scherf, U. Organic semiconductors for solution-processable field-effect transistors (OFETs). Angew. Chem. Int. Ed. 47, 4070–4098 (2008).

Turkoglu, G., Cinar, M. E. & Ozturk, T. in Sulfur Chemistry (ed Xuefeng Jiang) 79–123 (Springer International Publishing, 2019).

Lan, S. et al. Improving device performance of n-type organic field-effect transistors via doping with a p-type organic semiconductor. J. Mater. Chem. C 7, 4543–4550 (2019).

Kim, Y. et al. Enhanced charge injection properties of organic field-effect transistor by molecular implantation doping. Adv. Mater. 31, 1806697 (2019).

Lin, H. et al. Critical impact of gate dielectric interfaces on the trap states and cumulative charge of high-performance organic thin field transistors. Mater. Sci. Semicond. Process. 91, 275–280 (2019).

Nketia-Yawson, B. & Noh, Y.-Y. Recent progress on high-capacitance polymer gate dielectrics for flexible low-voltage transistors. Adv. Funct. Mater. 28, 1802201 (2018).

Yuan, Y. et al. Ultra-high mobility transparent organic thin film transistors grown by an off-centre spin-coating method. Nat. Commun. 5, 3005 (2014).

Nawaz, A. et al. Experimental and modeling study of low-voltage field-effect transistors fabricated with molecularly aligned copolymer floating films. Flex. Print. Electron. 3, 015006 (2018).

Liu, C., Xu, Y. & Noh, Y.-Y. Contact engineering in organic field-effect transistors. Mater. Today 18, 79–96 (2015).

Lenz, T., Schmaltz, T., Novak, M. & Halik, M. Self-assembled monolayer exchange reactions as a tool for channel interface engineering in low-voltage organic thin-film transistors. Langmuir 28, 13900–13904 (2012).

Tanaka, H. et al. Microscopic observation of efficient charge transport processes across domain boundaries in donor–acceptor-type conjugated polymers. Commun. Phys. 2, 1–10 (2019).

Li, Y., Sonar, P., Murphy, L. & Hong, W. High mobility diketopyrrolopyrrole (DPP)-based organic semiconductor materials for organic thin film transistors and photovoltaics. Energy Environ. Sci. 6, 1684–1710 (2013).

Li, Y., Singh, S. P. & Sonar, P. A high mobility P-type DPP-thieno[3,2-b]thiophene copolymer for organic thin-film transistors. Adv. Mater. 22, 4862–4866 (2010).

Mohammadi, E. et al. Dynamic-template-directed multiscale assembly for large-area coating of highly-aligned conjugated polymer thin films. Nat. Commun. 8, 16070 (2017).

Yang, S. F. et al. Diketopyrrolopyrrole-based conjugated polymer entailing triethylene glycols as side chains with high thin-film charge mobility without post-treatments. Adv. Sci. (Weinh.) 4, 1700048 (2017).

Mei, Y. et al. Interface engineering to enhance charge injection and transport in solution-deposited organic transistors. Org. Electron. 50, 100–105 (2017).

Rockson, T. K. et al. Engineering asymmetric charge injection/extraction to optimize organic transistor performances. ACS Appl. Mater Interfaces 11, 10108–10117 (2019).

Paterson, A. F. et al. On the role of contact resistance and electrode modification in organic electrochemical transistors. Adv. Mater. 31, 1902291 (2019).

Roh, J. et al. Injection-modulated polarity conversion by charge carrier density control via a self-assembled monolayer for all-solution-processed organic field-effect transistors. Sci. Rep. 7, 46365 (2017).

Kang, I., Yun, H. J., Chung, D. S., Kwon, S. K. & Kim, Y. H. Record high hole mobility in polymer semiconductors via side-chain engineering. J. Am. Chem. Soc. 135, 14896–14899 (2013).

Paterson, A. F. et al. On the role of contact resistance and electrode modification in organic electrochemical transistors. Adv. Mater. 31, e1902291 (2019).

Liu, Q., Bottle, S. E. & Sonar, P. Developments of diketopyrrolopyrrole-dye-based organic semiconductors for a wide range of applications in electronics. Adv. Mater. 32, e1903882 (2020).

Sonar, P. et al. Furan containing diketopyrrolopyrrole copolymers: synthesis, characterization, organic field effect transistor performance and photovoltaic properties. J. Mater. Chem. 22, 4425–4435 (2012).

Zhu, Y., Zhang, K. & Tieke, B. Electrochemical polymerization of bis(3,4-ethylenedioxythiophene)-substituted 1,4-diketo-3,6-diphenyl-pyrrolo[3,4-c]pyrrole (DPP) derivative. Macromol. Chem. Phys. 210, 431–439 (2009).

He, X. & Baumgartner, T. Conjugated main-group polymers for optoelectronics. RSC Adv. 3, 11334–11350 (2013).

Jung, J. W., Liu, F., Russell, T. P. & Jo, W. H. Synthesis of pyridine-capped diketopyrrolopyrrole and its use as a building block of low band-gap polymers for efficient polymer solar cells. Chem. Commun. 49, 8495–8497 (2013).

Osaka, I., Abe, T., Shimawaki, M., Koganezawa, T. & Takimiya, K. Naphthodithiophene-based donor–acceptor polymers: versatile semiconductors for OFETs and OPVs. ACS Macro Lett. 1, 437–440 (2012).

Subramaniyan, S., Kim, F. S., Ren, G., Li, H. & Jenekhe, S. A. High mobility thiazole–diketopyrrolopyrrole copolymer semiconductors for high performance field-effect transistors and photovoltaic devices. Macromolecules 45, 9029–9037 (2012).

Sonar, P., Chang, J., Shi, Z., Wu, J. & Li, J. Thiophene–tetrafluorophenyl–thiophene: a promising building block for ambipolar organic field effect transistors. J. Mater. Chem. C 3, 2080–2085 (2015).

Sonar, P. et al. Hole mobility of 3.56 cm2 V−1 s−1 accomplished using more extended dithienothiophene with furan flanked diketopyrrolopyrrole polymer. J. Mater. Chem. C 3, 9299–9305 (2015).

Ha, T.-J., Sonar, P. & Dodabalapur, A. Improved performance in diketopyrrolopyrrole-based transistors with bilayer gate dielectrics. ACS Appl. Mater. Interfaces 6, 3170–3175 (2014).

Li, Y., Sonar, P., Singh, S. P., Zeng, W. & Soh, M. S. 3,6-Di(furan-2-yl)pyrrolo[3,4-c]pyrrole-1,4(2H,5H)-dione and bithiophene copolymer with rather disordered chain orientation showing high mobility in organic thin film transistors. J. Mater. Chem. 21, 10829–10835 (2011).

Yi, Z., Wang, S. & Liu, Y. Design of high-mobility diketopyrrolopyrrole-based pi-conjugated copolymers for organic thin-film transistors. Adv. Mater. 27, 3589–3606 (2015).

Sista, P. et al. Enhancement of OFET performance of semiconducting polymers containing benzodithiophene upon surface treatment with organic silanes. J. Polym. Sci. Part A Polym. Chem. 49, 2292–2302 (2011).

Lei, Y., Wu, B., Chan, W.-K.E., Zhu, F. & Ong, B. S. Engineering gate dielectric surface properties for enhanced polymer field-effect transistor performance. J. Mater. Chem. C 3, 12267–12272 (2015).

Dinnebier, R. E. & Billinge, S. J. L. in Powder Diffraction 1–19 (2008).

Coelho, A. A. TOPAS and TOPAS-academic: an optimization program integrating computer algebra and crystallographic objects written in C++. J. Appl. Crystallogr. 51, 210–218 (2018).

Um, H. A., Shin, J., Lee, T. W., Cho, M. J. & Choi, D. H. Modulation of carrier mobility of diketopyrrolopyrrole and quaterthiophene containing copolymer with self-assembled monolayers on gate dielectrics of thin film transistors. Synth. Met. 184, 61–67 (2013).

Singh, S. & Mohapatra, Y. N. Bias stress effect in solution-processed organic thin-film transistors: evidence of field-induced emission from interfacial ions. Org. Electron. 51, 128–136 (2017).

Singh, S. & Mohapatra, Y. N. Persistent photocurrent (PPC) in solution-processed organic thin film transistors: mechanisms of gate voltage control. J. Appl. Phys. 120, 045501 (2016).

Singh, S. & Mohapatra, Y. N. Trap kinetics in solution-processed organic thin-film transistors. IEEE Electron. Devices Lett. 37, 35–38 (2016).

Li, S., Guérin, D. & Lmimouni, K. Improving performance of OFET by tuning occurrence of charge transport based on pentacene interaction with SAM functionalized contacts. Microelectron. Eng. 195, 62–67 (2018).

Choi, S. et al. A study on reducing contact resistance in solution-processed organic field-effect transistors. ACS Appl. Mater. Interfaces 8, 24744–24752 (2016).

Borchert, J. W. et al. Small contact resistance and high-frequency operation of flexible low-voltage inverted coplanar organic transistors. Nat. Commun. 10, 1119 (2019).

Gruber, M., Schürrer, F. & Zojer, K. Relation between injection barrier and contact resistance in top-contact organic thin-film transistors. Org. Electron. 13, 1887–1899 (2012).

Behrends, J. et al. Bipolaron formation in organic solar cells observed by pulsed electrically detected magnetic resonance. Phys. Rev. Lett. 105, 176601 (2010).

Yuan, Y. et al. Efficiency enhancement in organic solar cells with ferroelectric polymers. Nat. Mater. 10, 296–302 (2011).

Braz, T., Mendonça, A. L., Di Paolo, R. E. & Morgado, J. Effect of a ferroelectric polymer on the photophysical properties of a polyfluorene: exciton quenching by local electric fields. J. Lumin. 178, 457–462 (2016).

Abdu-Aguye, M. et al. Can ferroelectricity improve organic solar cells?. Macromol. Rapid Commun. 41, e2000124 (2020).

Umeda, T., Tokito, S. & Kumaki, D. High-mobility and air-stable organic thin-film transistors with highly ordered semiconducting polymer films. J. Appl. Phys. 101, 054517 (2007).

Takeda, Y. et al. Fabrication of ultra-thin printed organic TFT CMOS logic circuits optimized for low-voltage wearable sensor applications. Sci. Rep. 6, 25714 (2016).

Acknowledgements

B. B. Patil and T.T. Do, A.S are thankful to QUT for offering scholarship to conduct the research work. We are thankful to CRC for Polymers, Central Analytical Research Facility (CARF), and Institute of Future Environments, Queensland University of Technology (QUT) for providing equipment support. P. Sonar is thankful to QUT for the financial support from the Australian Research Council (ARC) for the Future Fellowship (FT130101337) and QUT core funding (QUT/322120-0301/07). A. K. Pandey acknowledges funding from AISRF (Project 53820).

Author information

Authors and Affiliations

Contributions

B.B.P., Y.T., S.T., S.P. A.K.P., P.S. designed the collaborative research. B.B.P., Y.T. performed the device fabrication, and related experimental work. B.B.P., and S.S. performed the data analysis, and wrote the manuscript, incorporating the comments from all the authors. B.B.P., A.S., and T.. Wang conducted the surface analysis. T.T.D., P.S. provided the polymer, and description of the material. All authors have given approval to the final version of the manuscript.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher's note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Patil, B.B., Takeda, Y., Singh, S. et al. Electrode and dielectric layer interface device engineering study using furan flanked diketopyrrolopyrrole–dithienothiophene polymer based organic transistors. Sci Rep 10, 19989 (2020). https://doi.org/10.1038/s41598-020-76962-x

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-020-76962-x

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.