Abstract

Memristors have demonstrated immense potential as building blocks in future adaptive neuromorphic architectures. Recently, there has been focus on emulating specific synaptic functions of the mammalian nervous system by either tailoring the functional oxides or engineering the external programming hardware. However, high device-to-device variability in memristors induced by the electroforming process and complicated programming hardware are among the key challenges that hinder achieving biomimetic neuromorphic networks. Here, a simple hybrid complementary metal oxide semiconductor (CMOS)-memristor approach is reported to implement different synaptic learning rules by utilizing a CMOS-compatible memristor based on oxygen-deficient SrTiO3-x (STOx). The potential of such hybrid CMOS-memristor approach is demonstrated by successfully imitating time-dependent (pair and triplet spike-time-dependent-plasticity) and rate-dependent (Bienenstosk-Cooper-Munro) synaptic learning rules. Experimental results are benchmarked against in-vitro measurements from hippocampal and visual cortices with good agreement. The scalability of synaptic devices and their programming through a CMOS drive circuitry elaborates the potential of such an approach in realizing adaptive neuromorphic computation and networks.

Similar content being viewed by others

Introduction

The functionality of a brain is attributed to the activity-dependent synaptic weight change, enabling principal cognitive functions1. Although the underlying precise biological mechanism of the synaptic functionality is still under debate2, it is well established that in vivo neurons follow the anti-Hebbian synaptic learning through spike-time-dependent-plasticity (STDP)3,4,5,6,7. In order to mimic the biological synaptic learning, conventional CMOS circuits have been employed8,9, but their limited scalability poses challenge to achieve the efficiency10 and density (~1011 neurons and ~1015 synapses compact in volume of ~1130-1260 cm3)11 of the human brain.

Nanoscale memristors have attracted attention as potential artificial synapses due to their similar activity-dependent nonlinear conductance modulation12,13,14,15. However, memristors require integration with the driving CMOS subsystems to successfully execute the memory/computation operations and emulate synaptic functions. To date, several hybrid CMOS-memristor architectures have been reported to achieve high density memory systems and neuromorphic computing paradigm16,17,18. But CMOS circuitry specifically designed for a particular memristor type, inexorable electroforming process causing a high device-to-device variability and associated stochastic nature of resistive switching are hampering the realization of efficient neuromorphic networks15,16,19. A hybrid architecture implementing a simple dynamic CMOS circuitry to comply with any type of memristors and an electroforming-free memristor would enable the imitation of versatile neuromorphic functions.

In this study, we exploit characteristics of STOx memristors20,21,22,23 and flexible design of a CMOS drive circuit to imitate different time and rate dependent synaptic functions. Over the recent few years, a variety of synaptic functions including short- and long-term memory, paired-pulse facilitation and pair-based STDP (p-STDP) have been implemented on different types of memories11,24,25,26,27,28. However, experimental demonstrations of higher order time-dependent plasticity such as triple-STDP (t-STDP) and quadruplet-STDP (q-STDP), and Bienenstock-Cooper-Munro (BCM) synaptic modifications (well known to exist in biological synapses)29,30,31 are not extensively explored in artificial synaptic devices. Though the classical p-STDP models helped to establish a fundamental understanding of the Hebbian synaptic plasticity in several neural systems but it is not sufficient to accurately model all biological experimental results produced by multiple (triplet and quadruplet) spikes29,32. This can be associated with deficiencies in the classical p-STDP model, such as excluding non-linear integration of spike pairs and their repetition frequency to quantify the synaptic modification30,32. This infers that the classical p-STDP model cannot elicit the BCM synaptic learning rule, which is regarded as a possible explanation of experience-dependent synaptic plasticity30. On the other hand, the t-STDP model is believed to be comprehensive enough to explain the experimental results produced by multiple spikes in biological neural systems. As such, the implementation of the t-STDP rule on STOx synaptic devices can highlight the capability of these artificial synapses to mimic the biological synaptic functionalities. We acknowledge that a few memristive models and circuits have recently been proposed to reproduce these synaptic learning rules33,34,35. However, an experimental emulation of these essential biological learning rules will signify the potential of memristors for future neuromorphic computation.

Furthermore, the available literature reports either extensive peripheral circuitry to generate suitable pre- and post-synaptic spike shapes (similar to the biological action potentials) or special circuits designed for a specific type of memristive system16,36. Additionally, the direct interfacing between CMOS drive circuitry and memristive devices/array can expose them to CMOS circuit non-ideality37. Herein, we utilize a well-established CMOS circuit, called forward body biasing38,39,40,41, in combination with a time-to-digital converter to implement not only time-dependent synaptic rules but also demonstrate the potential of implementing a wide variety of synaptic learning rules.

Results and Discussion

Switching characteristics of STOx synaptic devices

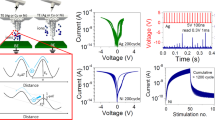

The metal-insulator-metal (MIM) configuration of the synaptic devices is assessed by the cross-sectional scanning transmission electron microscope (STEM, Fig. 1a) and energy-dispersive X-ray spectroscopic (EDS) elemental maps (Fig. 1b–e). The stoichiometric analysis of STOx thin films shows that the sputtered films are oxygen-deficient which indicates presences of oxygen vacancies in the as-grown STOx switching layer (Supplementary Information, Fig. S1). Figure 1f shows a clockwise bipolar switching behavior of the STOx synaptic devices. A negative quasi-static voltage sweep with amplitude of -1 V (as VSET) switches the MIM device from its high resistance state (HRS) to a low resistance state (LRS). While an opposite polarity quasi-static voltage sweep with an amplitude of + 1.3 V (as VRESET) switches the device to its HRS. This behavior i.e., RESET on positive bias and SET on negative bias is typical for STO-based memristors21,22,23,42. The as-fabricated MIM devices are in their high resistive state (HRS) as the measured pristine resistances are close to the normal variance of HRS achieved during subsequent cyclic switching (Supplementary Information, Fig. S2). However, the pristine state resistances are cell-area dependent. Furthermore, the statistical analysis of the as-fabricated devices shows that the average SET and RESET voltages during the first I–V sweeps are also area dependent (Supplementary Information, Fig. S2). The top Ti layer at Ti/STOx interface plays an important role in defining the switching characteristics of STOx resistive memories. In as-fabricated devices under zero bias condition, Ti layer partially oxidizes to sub-stoichiometric oxide (such as Ti2O3)43,44 due to the interfacial oxygen diffusion and Ti‒O bonding between Ti and STOx oxygen ions, at the vicinity of underlying STOx (discussed in cross-sectional analysis below). This introduces an additional switching layer at the top interface (i.e., Ti/Ti2O3/STOx) which is electrochemically different to oxygen deficient STOx and causes a change in mobility and formation energies of oxygen-vacancies in Ti2O3/STOx heterostructure. As such, the STOx synaptic devices do not require explicit electroforming and exhibit resistive switching after a low conditioning voltage sweep (close to the subsequent SET voltage sweeps). This can be associated with (i) the presence of as-grown oxygen vacancies in STOx thin films45,46 (revealed by X-ray photoelectron spectroscopy and photoluminescence spectra, Section S1 of Supplementary Information) and (ii) it is possible that during the first SET sweep Joule heating may induce additional oxygen vacancies in the MIM structure, according to oxygen exchange reaction47. As such, the increasing concentration of oxygen vacancies reduces their migration distance and consequently the electrical energy required to form a conductive filamentary path. Further evidence and cross-sectional characterization of the filamentary path is given in the following sections.

The STOx synaptic devices. (a) The cross-sectional scanning transmission electron microscope micrograph of a pristine STOx synaptic device. Scale bar 50 nm. (b) The energy-dispersive X-ray spectroscopic elemental maps of (b) Pt, (c) Ti, (d) Sr and (e) O. (f) The I–V characteristic sweep of a 10 × 10 µm2 STOx MIM device. (g) The retention time vs. 1/kT plot to evaluate the state stability of the STOx devices. The inset shows retention of LRS and HRS at different elevated temperatures ranging from 150 to 250 °C. (h) Endurance of the devices, where VRESET of −1.6 V, VSET of +1.4 V and VREAD of +0.1 V are applied as a train of short pulses. (i) The dependence of HRS and LRS on the active cell area.

To evaluate the reliability of the STOx MIM devices, the resistive states are measured at elevated temperatures ranging from 150 to 250 °C, as shown in the inset of Fig. 1g. The retention of HRS measured for 30 hours at 250 °C shows no failure, indicating high stability of HRS. However, retention characteristics of LRS are temperature-sensitive. This high temperature LRS retention failure can be associated with the thermally-assisted reduction in the concentration of oxygen vacancies in the nano-filament and eventually leading its rupture48. The LRS retention failure time at different temperatures (where resistance jumps higher than the HRS) is plotted in an Arrhenius plot, as shown in Fig. 1g, to calculate the oxygen vacancy migration activation energy and estimate the retention characteristics of the STOx memristors. The extrapolation of the fitting line in Fig. 1g estimates the retention time of ca. 7.6 years at room temperature. Even though, this retention is suitable for memory and neuromorphic applications, it may be further improved by preventing the re-oxidation of STOx oxide layer through inserting a thin film exhibiting slow oxygen diffusion coefficient, such as Al2O349. On the other hand, activation energy of ca. 0.29 eV is extracted from the linear fitting of the experimental data. Such a low LRS activation energy, as compared to the other oxide systems48,50,51 (e.g., 1.0–1.6 eV reported for amorphous Al2O3, amorphous Ta2O5, amorphous Nb2O5, and TiO2), suggests a hopping conduction mechanism in our STOx MIM devices52. This hopping conduction refers to the electronic transport through localized states, where these states are provided by the oxygen vacancies in the nano-filament.

To evaluate the switching repeatability of the STOx MIM devices (Fig. 1h), short pulses of 1 μs duration and amplitude of −1.4 V and +1.6 V are applied for SET and RESET operations, respectively. READ pulses with amplitude of +0.1 V and duration of 200 ns are used to measure the SET/RESET currents. The effect of pulse width on the switching performance is also evaluated (Supplementary Information, Fig. S4). The endurance characteristics for more than 104 switching cycles (Fig. 1h) indicate that the synaptic devices exhibit repeatable bipolar switching behaviour. Typically in transition metal oxides, the bipolar resistive switching behavior is attributed to the inhomogeneous conduction mechanisms through the localized filamentary pathways and associated redox processes47,53,54,55. As such, the resistance states (i.e., HRS and LRS) are expected to be independent of the lateral dimensions of the MIM devices. Figure 1i reveals no appreciable area-dependency in our STOx devices for either resistance state. This further supports our earlier statement regarding the formation of conductive filamentary pathway in the MIM devices.

Visualising filamentary switching in resistive states

The physical structure of the STOx synaptic devices and their compositional analysis is characterized by cross-sectional transmission electron microscopy (TEM). Electron energy loss spectroscopy (EELS) is used to assess the distribution of oxygen content in the MIM devices. The cross-sectional micrograph and corresponding EELS spectra of a pristine MIM device reveal an amorphous microstructure of the STOx layer and a partial oxidation of the top Ti layer at the Ti/STOx interface (Supplementary Information, Fig. S5). The amorphous and oxygen-deficient structure of STOx layer is attributed to the room temperature sputtering in a pure argon environment. Also, the partial oxidation of the top Ti layer to sub-oxide at Ti/STOx interface can be associated with the interfacial oxygen diffusion and Ti‒O bonding between Ti and STOx oxygen ions44,56,57. Fig. 2a,b shows scanning TEM (STEM) images of the switching STOx memristive devices in their LRS and HRS, respectively. High contrast regions are observed in the STOx layers and along the top Ti/STOx interfaces which indicate the applied electric field induced compositional changes in the STOx layers. To analyse the state-dependent composition of the STOx layers, region of interests (ROIs) are selected across the lamellae, highlighted in Fig. 2a,b. The EELS O–K edge area maps (Fig. 2c,d) show the relative distribution of oxygen content in ROIs where the area maps are generated by taking the O–K edge intensities of the collected spectra (at each pixel) after pre-edge background subtraction. The O–K edge area map of the device in LRS (Fig. 2c) reveals the presence of an extending oxygen-deficient region between top and bottom Pt electrodes. This indicates a localized accumulation of oxygen vacancies and formation of conductive filamentary path across the MIM structure42. On the other hand, the O–K edge area map of the device in HRS (Fig. 2d) shows higher concentration of oxygen vacancies at the vicinity of bottom Pt electrode which indicates a ruptured filamentary path.

Microstructural and compositional analyses of the STOx synaptic devices. (a) STEM cross-section of a switching device in its LRS. Scale bar 20 nm. (b) STEM cross-section of a switching device in its HRS. Scale bar 20 nm. (c) The EELS O–K edge area map of the enclosed region of interest in (a). The colour bar shows the relative oxygen content. (d) The EELS O–K edge area map of the enclosed region of interest in (b). The colour bar shows the relative oxygen content. (e) The EELS Ti–L2,3 edge profiles along a line scan across the ROI in (a). (f) The EELS Ti–L2,3 edge profiles along a line scan across the ROI in (b).

The formation of each oxygen vacancy in STO introduces two electrons into the Ti 3d orbital, and the resulting change in the Ti valence can be observed in the EELS Ti–L2,3 edge profile58,59. Figure 2e,f show the background corrected Ti–L2,3 spectra acquired along the EELS cross-sectional line scans passing over the ROIs indicated in Fig. 2a,b, respectively. The Ti–L2,3 fine structures gradually evolve in their intensity and position (from top Pt/Ti interface to the bottom Pt electrode) as clearly observed in both LRS and HRS. Due to resolution limitation, we evaluate the Ti–L2,3 edge profiles to qualitatively analyse the electronic structure of the ROIs. The broad and relatively low intensity peaks at top Pt/Ti interface indicate the presence of mixed Ti2+ and Ti3+ oxidation states which further highlights the oxidation of Ti layer44,56,58,60. At Ti/STOx interfacial region and in the STOx layer, the crystal-field splitting of Ti–L3 and Ti–L2 peaks (into t2g and eg peaks) and their shift can be attributed to the presence of Ti3+ and Ti4+ oxidation states61,62,63. It is well known that in transition metal oxide based resistive memories the resistive switching is attributed to the redox reactions and associated valence change in the transition metal cations, such as Ti in STO47,64. As such, the cross-sectional TEM analysis shows that the bipolar resistive switching in our STOx MIM devices is of filamentary nature where formation and rupture of extended oxygen-deficient regions and associated change in Ti valance result in LRS and HRS, respectively.

Implementation of synaptic functions

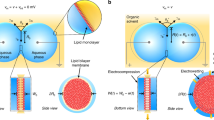

A typical biological synapse consists of a pre-synaptic neuron and a post-synaptic neuron connected through a synaptic cleft, as schematically illustrated in Fig. 3a. In a memristor-based artificial synapse, the bottom and top electrodes work as neurons and the switching layer acts as a synaptic connection. The electrical conductivity of the device interprets the synaptic weight, while its increase or decrease translates to potentiation or depression, respectively, in response to the applied voltage spikes. Figure 3b shows an experimental implementation of simplified t-STDP learning rules using our STOx memristive devices (cross-point and 7 × 7 array of devices). The protocols to implement these learning rules are adopted from ref. 29,30. Synaptic weight changes reported here (denoted by Δw in Fig. 3b) are extracted by applying voltage pulses of different amplitude but fixed pulse width (100 µs). A proposed programming time-to-digital-to-voltage circuitry (discussed in Section 2.4 below) is simulated to generate the amplitude of voltage pulses corresponding to different spike-timing information (Δt1 and Δt2). The capability of this scheme to implement a wide range of learning rules, including p-STDP and t-STDP, is verified by applying a series of 100 pulses for each voltage amplitude that is chosen by the programming circuitry. The amplitude of applied voltage pulses for the corresponding spike-timing is listed in Table S1 (see Supplementary Information). These experiments demonstrate a simple analog time-multiplexing implementation of the artificial memristive synapses with shared peripheral circuitry.

Triplet-based STDP implemented on STOx synaptic devices. (a) An illustration of two biological neurons connecting via synapses. (b) Artificial implementation of STDP learning rules using STOx synaptic devices. Each data point and its deviation from mean (represented by bars) are collected by applying 100 cycles of identical pulses, where each cycle contains a RESET (for potentiation experiments) or SET (for depression experiments) pulse.

A simplified t-STDP learning rule can be presented as30

where Δt1(=tpost - tpre) and Δt1(=tpost1 - tpost2) are time differences. \({A}_{1}^{-}\,\)and \({A}_{2}^{+}\) are constant amplitudes of each exponential term in potentiation (Δw+) and depression (Δw−) equations. The values of these amplitudes extracted from curve fitting (in Fig. 3b) are \({A}_{1}^{-}=-\,0.70\) and \({A}_{2}^{+}=0.60\). Also, τ+ and τ− are time constants of Δw+ and Δw−, respectively, and obtained from the fitting parameters as τ+ = 8.2 ms and τ− = 2.5ms. While the time constant τy indicates the exponential correlation between Δw+ and Δt2, and extracted as τy = 80ms. To reproduce the t-STDP window, the values of Δt2 are fixed at 10, 80 and 160 ms during the experiments (as shown in Fig. 3b).

The simplified t-STDP learning rule29,30, suggests that synaptic depression is produced by spiking pair with time interval of Δt1 (as in classical p-STDP rule), while synaptic potentiation takes a triplet of spikes into account. It is worth mentioning that ref.27 utilizes two sets of spikes. First set of spikes consists of two presynaptic spikes and one postsynaptic spike with Δt1 and Δt2 representing the time differences between the postsynaptic spike and the first and second presynaptic spikes, respectively. Second set of spikes includes two postsynaptic spikes and one presynaptic spike. On the other hand, in ref.28 the synaptic depression is response to a pre- and postsynaptic pair, while synaptic potentiation is induced with a set of triple spikes which consists of two postsynaptic spikes and one presynaptic spike. In our case, we consider ‘post–pre–post’ configuration of the triplet spikes for synaptic potentiation, all details can be similarly applied for a ‘pre–post–pre’ configuration. Also, a pair of pre- and post-synaptic spikes for synaptic depression.

In order to demonstrate that our STOx synaptic devices are capable of imitating biological synaptic plasticity, we implement the t-STDP model (Eq. 1) by following the experimental protocols reported by Pfister and Gerstner29. We compare the results with the electrophysiological experiments performed in hippocampal culture65 and visual cortex31 (Fig. 4). Two different triplet spiking patterns, namely ‘post–pre–post’ (i.e., 1-pre–2-post) and ‘pre–post–pre’ (i.e., 2-pre–1-post), are used in hippocampal culture experiments65. Each spiking pattern consists of 60 triplet of spikes and are repeated at a rate of 1 Hz. The weight change as a function of timing difference between pre- and post-synaptic spikes in both triplet patterns is graphically presented in Fig. 4a,b. The best fit is calculated by a normalized mean-square error function (E) represented as29,

where P, \({\Delta }{W}_{i}^{exp}\), \(\varDelta {W}_{i}^{mem}\) and σi are the number of data points in a dataset, mean weight change (in electrophysiological and a-STOx memristor experiments) and the standard error mean (SEM) of \(\varDelta {W}_{i}^{exp}\) for a given data point i, respectively. In the hippocampal culture, 13 data points are used, which includes 2 pairing and 3 quadruplet data points. To compare our experimental results with hippocampal culture, we use only 8 triplet data points, 4 for 2-pre–1-post and 4 for 1-pre–2-post triplet spiking patterns. Also, we minimize the function E (given in Eq. 2) which represents the error between our memristor experimental results and hippocampal culture (Fig. 4a,b). Conventionally, parameters of the CMOS drive circuit are tuned to achieve the best match between the mathematical t-STDP and hippocampal culture data33,34. However, we minimize the error via one-to-one mapping of the weight changes (Δw) to the appropriate voltage levels applied to the artificial synapses (STOx memristors). Furthermore, this mapping is carried out by extracting timing information using a time-to-digital and then digital-to-voltage conversion in the CMOS drive circuitry (discussed in Section 2.4 below and Section S5 in Supplementary Information). As such, the error is minimized by creating and changing a digital look-up table that maps incoming spike-timing information to a 6-bit digital code. The weight change corresponding to the both triplet pairing configurations is listed in Table S2 (see Supplementary Information). There is <10% error between our memristor data and hippocampal culture data which is comparatively smaller than previously achieved (35%) by mathematical t-STDP models33,34.

Figure 4c shows the implementation of BCM learning rule where the synaptic weight changes as a function of the given frequency, ρ. The comparison of our experimental results with the visual cortex data set (Fig. 4c) shows that STOx memristors closely follow the BCM behavior for ρ ≤ 30 Hz, while for high frequencies our experimental results are within the variation limits of visual cortex data set. As observed in the I–V characteristics of the STOx memristors, SET process exhibits a digital-like behavior while RESET is an analog-like switching behavior offering comparatively more intermediate stable-states. As such, achieving a high dynamic range of weight change for Δw+ is more challenging than Δw−, also observed in Fig. 3b,c. The values of synaptic weight change corresponding to different frequencies are listed in Table S3 (see Supplementary Information). This indicates that similar to time-dependent learning rules (i.e., p-STDP and t-STDP); rate dependent learning rules such as BCM rule can also be implemented by our STOx synaptic devices.

CMOS drive circuitry

Generally, to implement STDP with memristors an approach where pre- and post-spikes are superposed to induce synaptic weight change in memristors is adopted. In such approaches input voltage signals (spikes) are directly applied to the devices which can expose them to CMOS circuit non-idealities35,66. Since the memristive devices response to shape and frequency of an incoming spikes, time-modulated amplitude of superposed spikes or similar techniques are also adopted66,67. However, in this work the relative weight change is achieved by a fully digital spike processing unit (time-to-digital-to-voltage circuit, discussed below) which offers a higher level of multiplexing and lower complexity of the overall drive circuitry. Furthermore, through a fully digital spike processing module (time-to-digital-to-voltage) we distinguish from the conventional approaches of placing memristors in the pathway of signals.

Figure 5a shows a schematic of the proposed CMOS drive circuit which is a modification of the body-bias generator39,40, and converts differences in input spike-timing to voltage amplitudes. The time-to-digital (T2D) module is responsible for the pre- and post-synaptic event digitization and includes a timing control unit and a decoder (see Section S5 in Supplementary Information). The timing control unit is a fully digital unit that receives pre- and post-spikes and generates a binary code according to the timing intervals and works based on a number of counters that are triggered and stopped with spikes. It can be configured to implement multiple protocols and Δt detections38.

The CMOS drive circuitry. (a) A schematic of the proposed CMOS drive circuit which converts difference in input spike-timing into voltage amplitudes to modify the synaptic weight of a target memristor in the array. (b) Simulated resolution of the DAC circuitry to generate the weight changing voltage, i.e., Vw.

As depicted in Fig. 5a, a finely tuned voltage (Vw) is generated to modify the weight of a memristor and is connected to a memristor array via a voltage follower (VF) and an array of transmission gates (TGs) that are connected to the top-electrodes (TEs) and bottom-electrodes (BEs) of the memristor array. It is worth mentioning that we focus on the design of peripheral circuitry for memristive artificial synapses, while modifications in the neuron designs may also be necessary to consider for online-learning aspects of the synaptic rules. Each device in the array is individually accessible via an addressable top-electrode (TE) and bottom-electrode (BE) connections. Selections are mandated externally and partially include some internal data. These selection signals are represented with two digital vectors for rows (R) and columns (C), i.e., SelR and SelC respectively, in Fig. 5a. Note that Iref is a constant reference current that is supplied through a digital to analog converter (DAC), while VDDA and VSSA represent analog voltage supply and ground of the drive circuit, respectively. The proposed drive circuitry disconnects timing scales from the voltage level generation. Also, the T2D module is fully programmable and can map any spike-timing to any binary code which can be translated to the corresponding voltage amplitude, via the DAC. It is worth mentioning that addressing an individual device within an array requires additional devices (such as selectors) to protect each device from random programming through parasitic current paths. Also, we are using STOx memristors as a multi-state memory device, as reported in our previous work22. Therefore, unless an initialization is required, there is no one hard switching to HRS or LRS. However, considering the initial status of the memory array, initial weight pattern could be random.

Near exponential relationship exists between the programming voltage amplitude (Vw) and synaptic weight change (Δw), also revealed in Fig. 3b. This implies that a small variation in Vw can cause a significant deviation in Δw. Therefore, it is essential to estimate the programming efficiency of the proposed CMOS drive circuit. Figure 5b shows the Cadence simulation of the DAC circuitry using 90 nm CMOS technology. A 15.6 mV resolution of the VDAC for a total 1 V supply is achieved. Figure 5b and Table S1 (Supplementary Information) show overall mapping of spike-timing to DAC code and then to an equivalent voltage (Vw in this case). It has been reported that variation in Vw is less than 5 mV39,40. Although a 15.6 mV increase in applied voltage magnitudes even higher than the VREAD (i.e., 0.5 V) may not necessarily switch the device, but it is observed that such an increase causes a significant statistical change in Δw.

Conclusion

In summary, we have presented a CMOS-compatible memristor based on STOx exhibiting bipolar resistive switching behavior. First, through electrical and cross-sectional characterizations we have shown that reliable resistive switching in the STOx based memristors is attributed to the redox reactions and electronic transport through the localized conductive nano-filamentary pathway. In addition to the exonerated electroforming characteristics, the STOx memristors have also shown their scalability potential for future high-density memory applications. Secondly, we have demonstrated a hybrid CMOS-memristor approach to successfully mimic time-dependent, such as p- and t-STDP, and rate-dependent such as BCM synaptic learning rules. As such, this study is a step towards the realization of an adaptive neuromorphic network by utilizing high order (triplet and quadruplet) learning rules.

Methods

Device fabrication

The STOx synaptic devices are fabricated as cross-point devices and array in metal-insulator-metal (MIM) configuration with the stack of Pt/Ti/STOx/Pt/Ti/SiO2/Si. Several devices with active areas of 2×2 µm2, 4×4 µm2, 10×10 µm2, 20×20 µm2, 40×40 µm2, 80×80 µm2 and 100×100 µm2 are patterned by following standard photolithography and thin film deposition processes. The bottom Pt (15 nm)/Ti (7 nm) electrodes are patterned onto a SiO2 (300 nm)/Si substrate by electron beam (e-beam) evaporation. As a switching layer, 25 nm thin film of oxygen-deficient STO is deposited by using radio frequency sputtering (with 100 W power) from a commercial ceramic STO target in a pure argon environment under a pressure of 0.46 Pa and at room temperature. In order to complete the MIM structure, top Pt (30 nm)/Ti (5 nm) electrodes are evaporated by the e-beam evaporation at a base pressure of <6×10−5 Pa.

Electrical characterization

The electrical characterization of the STOx synaptic devices is performed under ambient conditions by using a Keysight 2912 A source measure unit and Keithley 4200SCS equipped with remote preamplifiers and 4225 pulse modulation units connected to a micro-probe station. For the resistive switching of STOx synaptic devices, bias is applied on the bottom Pt electrodes while keeping the top Pt electrodes grounded. High temperature electrical measurements are performed by using an environmentally isolated Linkum chamber connected with Agilent 2912 A source meter.

X-ray photoelectron spectroscopy

X-ray photoelectron spectroscopy (XPS) analysis is conducted by using a Thermo Scientific K-Alpha instrument utilizing an aluminum Kα radiation source (1486.6 eV). The XPS spectra are collected from bare STO oxide thin films, sputtered on SiO2/Si substrates. Also, a stoichiometric crystalline STO substrate is used as reference. All spectra are resolved by using the standard Gaussian-Lorentzian function followed by the Shirley background correction.

Photoluminescence spectroscopy

The photoluminescence (PL) emission spectra are obtained using a Horiba Scientific FluoroMax-4 spectrofluorometer. All spectra are collected at room temperature from as-deposited bare STOx thin films sputtered on SiO2/Si substrates. A laser source with 325 nm of wavelength is used to excite the sputtered thin films.

Transmission electron spectroscopy

The transmission electron microscopy (TEM), energy-dispersive X-ray spectroscopy (EDS) and electron energy loss spectroscopic (EELS) analyses are performed on pristine and switching STOx MIM devices (at least for 50 cycles and subjected to constant bias stresses) using a JEOL 2100 F scanning transmission electron microscope (STEM) with attached Tridium Gatan image filter with an aperture of 5 mm. The TEM samples are prepared by focused ion beam cuts through the MIM structure by using a FEI Scios DualBeamTM system. Cross-sectional STEM micrographs and EELS spectra are collected using a <1.5 nm beam spot. EELS spectra are collected with a dispersion of 0.3 eV per pixel which allowed simultaneous recording of the titanium L2,3 (Ti–L2,3) edge and oxygen K (O–K) edge in the regions of interest and across the MIM cross-sections. A power law fit is adopted for the pre-edge background correction while the influence of nearby peaks and plural scattering are reduced by narrow signal windows.

Data availability

All data needed to evaluate the conclusions in the paper are present in the paper and/or Supplementary Materials. Additional data related to this paper may be requested from the authors.

References

Royer, S. & Pare, D. Conservation of total synaptic weight through balanced synaptic depression and potentiation. Nature 422, 518–522 (2003).

Kavalali, E. T. The mechanisms and functions of spontaneous neurotransmitter release. Nat. Rev. Neurosci. 16, 5–16 (2015).

Feldman, D. E. The spike timing dependence of plasticity. Neuron 75, 556–571 (2012).

Sen, S., Miller, K. D. & Abbott, L. F. Competitive Hebbian learning through spike-timing-dependent synaptic plasticity. Nat. Neurosci. 3, 919–926 (2000).

Caporale, N. & Dan, Y. Spike timing–dependent plasticity: A Hebbian learning rule. Annu. Rev. Neurosci. 31, 25–46 (2008).

van Rossum, M. C. W., Bi, G. Q. & Turrigiano, G. G. Stable hebbian learning from spike timing-dependent plasticity. J. Neurosci. 20, 8812–8821 (2000).

Abbott, L. F. & Nelson, S. B. Synaptic plasticity: Taming the beast. Nat. Neurosci. 3, 1178–1183 (2000).

Türel, Ö., Lee, J. H., Ma, X. & Likharev, K. K. Neuromorphic architectures for nanoelectronic circuits. Int. J. Circ. Theor. App. 32, 277–302 (2004).

Indiveri, G. et al. Neuromorphic silicon neuron circuits. Front. Neurosci. 5, 73, https://doi.org/10.3389/fnins.2011.00073 (2011).

Hutchby, J. A., Bourianoff, G. I., Zhirnov, V. V. & Brewer, J. E. Extending the road beyond CMOS. IEEE Circuits Devices Mag. 18, 28–41 (2002).

Wang, Z. et al. Nanoionics-enabled memristive devices: Strategies and materials for neuromorphic applications. Adv. Electron. Mater. 1600510 (2017).

Jo, S. H. et al. Nanoscale memristor device as synapse in neuromorphic systems. Nano. Lett. 10, 1297–1301 (2010).

Zamarreno-Ramos, C. et al. On spike-timing-dependent-plasticity, memristive devices, and building a self-learning visual cortex. Front. Neurosci. 5, 26 (2011).

Serrano-Gotarredona, T., Masquelier, T., Prodromakis, T., Indiveri, G. & Linares-Barranco, B. STDP and STDP variations with memristors for spiking neuromorphic learning systems. Front. Neurosci. 7, 1–15 (2013).

Yang, J. J., Strukov, D. B. & Stewart, D. R. Memristive devices for computing. Nat. Nanotechnol. 8, 13–24 (2013).

Chakrabarti, B. et al. A multiply-add engine with monolithically integrated 3D memristor crossbar/CMOS hybrid circuit. Sci. Rep. 7, 42429 (2017).

Kim, K. H. et al. A functional hybrid memristor crossbar-array/CMOS system for data storage and neuromorphic applications. Nano Lett. 12, 389–395 (2012).

Prezioso, M. et al. Training and operation of an integrated neuromorphic network based on metal-oxide memristors. Nature 521, 61–64, https://doi.org/10.1038/nature14441 (2015).

Yang, Y. & Lu, W. Nanoscale resistive switching devices: mechanisms and modeling. Nanoscale 5, 10076–10092 (2013).

Rahman, M. A., Ahmed, T., Walia, S., Sriram, S. & Bhaskaran, M. Oxygen-deficient strontium titanate based stretchable resistive memories. Appl. Mater. Today 13, 126–134 (2018).

Ahmed, T. et al. Transparent amorphous strontium titanate resistive memories with transient photo-response. Nanoscale 9, 14690–14702 (2017).

Nili, H. et al. Donor-induced performance tuning of amorphous SrTiO3 memristive nanodevices: Multistate resistive switching and mechanical tunability. Adv. Func. Mater. 25, 3172–3182 (2015).

Nili, H. et al. Nanoscale resistive switching in amorphous perovskite oxide (a-SrTiO3) memristors. Adv. Func. Mater. 24, 6741–6750 (2014).

Wang, Z. et al. Memristors with diffusive dynamics as synaptic emulators for neuromorphic computing. Nat. Mater. 16, 101–108 (2017).

Yan, X. et al. Memristor with Ag-cluster-doped TiO2 films as artificial synapse for neuroinspired computing. Adv. Funct. Mater. 28, 1705320 (2018).

Zhu, X. & Lu, W. D. Optogenetics-inspired tunable synaptic functions in memristors. ACS Nano 12, 1242–1249, https://doi.org/10.1021/acsnano.7b07317 (2018).

Ahmed, T. et al. Optically stimulated artificial synapse based on layered black phosphorus. Small 15, 1900966 (2019).

Ahmed, T. et al. Multifunctional optoelectronics via harnessing defects in layered black phosphorus. Adv. Func. Mater. 1901991 (2019).

Pfister, J. P. & Gerstner, W. Triplets of spikes in a model of spike timing-dependent plasticity. J. Neurosci. 26, 9673–9682 (2006).

Gjorgjieva, J., Clopath, C., Audet, J. & Pfister, J. P. A triplet spike-timing-dependent plasticity model generalizes the Bienenstock-Cooper-Munro rule to higher-order spatiotemporal correlations. Proc. Natl. Acad. Sci. USA 108, 19383–19388 (2011).

Sjöström, P. J., Turrigiano, G. G. & Nelson, S. B. Rate, timing, and cooperativity jointly determine cortical synaptic plasticity. Neuron 32, 1149–1164 (2001).

Bi, G.-Q. & Wang, H.-X. Temporal asymmetry in spike timing-dependent synaptic plasticity. Physiol. Behav. 77, 551–555 (2002).

Azghadi, M. R., Linares-Barranco, B., Abbott, D. & Leong, P. H. W. A hybrid CMOS-memristor neuromorphic synapse. IEEE Trans. Biomed. Circuits Syst. 11, 434–445 (2017).

Aghnout, S., Karimi, G. & Azghadi, M. R. Modeling triplet spike-timing-dependent plasticity using memristive devices. J. Comput. Electron. 16, 401–410 (2017).

Cai, W., Ellinger, F. & Tetzlaff, R. Neuronal synapse as a memristor: Modeling pair- and triplet-based STDP rule. IEEE Trans. Biomed. Circuits Syst. 9, 87–95 (2015).

Chu, M. et al. Neuromorphic hardware system for visual pattern recognition with memristor array and CMOS neuron. IEEE Trans. Ind. Electron. 62, 2410–2419 (2015).

Xinyu, W., Saxena, V. & Kehan, Z. In 2015 International Joint Conference on Neural Networks (IJCNN). 1–6.

Friedmann, S. et al. Demonstrating hybrid learning in a flexible neuromorphic hardware system. IEEE Trans. Biomed. Circuits Syst. 11, 128–142 (2017).

Blagojević, M. et al. In 2016 IEEE Symposium on VLSI Circuits Digest of Technical Papers. 1–2 (Widerkehr and Associates).

Meijer, M. & Gyvez, J. P. D. Body-bias-driven design strategy for area- and performance-efficient CMOS circuits. IEEE Trans. VLSI Syst. 20, 42–51 (2012).

Meijer, M. et al. In Proceedings of 2010 IEEE International Symposium on Circuits and Systems. 2482–2485.

Nili, H. et al. Microstructure and dynamics of vacancy-induced nanofilamentary switching network in donor doped SrTiO3−x memristors. Nanotechnology 27, 505210 (2016).

Ahmed, T. et al. Data related to the nanoscale structural and compositional evolution in resistance change memories. Data in Brief 21, 18–24, https://doi.org/10.1016/j.dib.2018.09.087 (2018).

Ahmed, T. et al. Inducing tunable switching behavior in a single memristor. Appl. Mater. Today 11, 280–290 (2018).

Joshua Yang, J. et al. The mechanism of electroforming of metal oxide memristive switches. Nanotechnology 20, 215201 (2009).

Gao, S. et al. Forming-free and self-rectifying resistive switching of the simple Pt/TaOx/n-Si structure for access device-free high-density memory application. Nanoscale 7, 6031–6038, https://doi.org/10.1039/c4nr06406b (2015).

Waser, R., Dittmann, R., Staikov, G. & Szot, K. Redox-based resistive switching memories – nanoionic mechanisms, prospects, and challenges. Adv. Mater. 21, 2632–2663 (2009).

Choi, S., Lee, J., Kim, S. & Lu, W. D. Retention failure analysis of metal-oxide based resistive memory. Appl. Phys. Lett. 105, 113510 (2014).

Baeumer, C. et al. Verification of redox-processes as switching and retention failure mechanisms in Nb:SrTiO3/metal devices. Nanoscale 8, 13967–13975 (2016).

Miao, F., Joshua Yang, J., Borghetti, J., Medeiros-Ribeiro, G. & Stanley Williams, R. Observation of two resistance switching modes in TiO2 memristive devices electroformed at low current. Nanotechnology 22, 254007 (2011).

Nakamura, R. et al. Diffusion of oxygen in amorphous Al2O3, Ta2O5, and Nb2O5. J. Appl. Phys. 116, 033504 (2014).

Phan, B. T., Choi, T., Romanenko, A. & Lee, J. Hopping and trap controlled conduction in Cr-doped SrTiO3 thin films. Solid State Electron. 75, 43–47 (2012).

Dittmann, R. et al. Scaling potential of local redox processes in memristive SrTiO3 thin-film devices. Proc. IEEE 100, 1979–1990 (2012).

Lee, E., Gwon, M., Kim, D.-W. & Kim, H. Resistance state-dependent barrier inhomogeneity and transport mechanisms in resistive-switching Pt/SrTiO3 junctions. Appl. Phys. Lett. 98, 132905 (2011).

Kim, H., Park, C., Lee, S. & Kim, D.-W. Inhomogeneous barrier and hysteretic transport properties of Pt/SrTiO3 junctions. J. Phys. D: Appl. Phys. 42, 055306 (2009).

Li, Y. et al. Nanoscale chemical and valence evolution at the metal/oxide interface: A case study of Ti/SrTiO3. Adv. Mater. Interf. 3, 1600201 (2016).

Hill, D. M., Meyer, H. M. & Weaver, J. H. Y, Ba, Cu, and Ti interface reactions with SrTiO3 (100) surfaces. J. Appl. Phys. 65, 4943–4950 (1989).

Sanchez-Santolino, G. et al. Characterization of surface metallic states in SrTiO3 by means of aberration corrected electron microscopy. Ultramicroscopy 127, 109–113 (2013).

Muller, D. A., Nakagawa, N., Ohtomo, A., Grazul, J. L. & Hwang, H. Y. Atomic-scale imaging of nanoengineered oxygen vacancy profiles in SrTiO3. Nature 430, 657–661 (2004).

Stoyanov, E., Langenhorst, F. & Steinle-Neumann, G. The effect of valence state and site geometry on Ti L 3,2 and O K electron energy-loss spectra of TixOy phases. Am. Mineral. 92, 577–586 (2007).

Cooper, D. et al. Anomalous resistance hysteresis in oxide ReRAM: Oxygen evolution and reincorporation revealed by in situ TEM. Adv. Mater. 29, 17002121–17002128 (2017).

Du, H. et al. Atomic structure and chemistry of dislocation cores at low-angle tilt grain boundary in SrTiO3 bicrystals. Acta Mater. 89, 344–351 (2015).

Rho, J. et al. Observation of room temperature photoluminescence in proton irradiated SrTiO3 single crystal. J. Lumin. 130, 1784–1786 (2010).

Menzel, S., Böttger, U., Wimmer, M. & Salinga, M. Physics of the switching kinetics in resistive memories. Adv. Func. Mater. 25, 6306–6325 (2015).

Wang, H.-X., Gerkin, R. C., Nauen, D. W. & Bi, G.-Q. Coactivation and timing-dependent integration of synaptic potentiation and depression. Nat. Neurosci. 8, 187–193 (2005).

Zhao, L., Hong, Q. & Wang, X. Novel designs of spiking neuron circuit and STDP learning circuit based on memristor. Neurocomputing 314, 207–214 (2018).

Xiong, J. et al. Bienenstock, Cooper, and Munro learning rules realized in second-order memristors with tunable forgetting rate. Adv. Func. Mater. 29, 1807316, https://doi.org/10.1002/adfm.201807316 (2019).

Acknowledgements

The authors acknowledge support from the Australian Research Council (ARC) for personnel and project support via DP130100062 (S.S.), DE160100023 (M.B.), and FT140101285 (V.B.) and equipment funding through LE0882246, LE0989615, LE110100223, and LE150100001. The authors would like to acknowledge the technical assistance of the Micro Nano Research Facility (MNRF) and the RMIT Microscopy and Microanalysis Research Facility (RMMF).

Author information

Authors and Affiliations

Contributions

T.A., S.W., M.B., S.S. and O.K. conceptualized this work. T.A. undertook device fabrication and characterization presented in this manuscript with O.K. contributing to data analysis. T.A., R.R., and V.B. performed XPS and PL characterisations. T.A. and E.L.H.M. prepared FIB-based specimen and performed TEM characterisation. T.A. and S.W. prepared the first version of the manuscript with all authors contributing to the final version.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Ahmed, T., Walia, S., Mayes, E.L.H. et al. Time and rate dependent synaptic learning in neuro-mimicking resistive memories. Sci Rep 9, 15404 (2019). https://doi.org/10.1038/s41598-019-51700-0

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-019-51700-0

This article is cited by

-

Planar CBRAM devices using non-cleanroom techniques as RF switches

Applied Physics A (2023)

-

Run-off election-based decision method for the training and inference process in an artificial neural network

Scientific Reports (2021)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.