Abstract

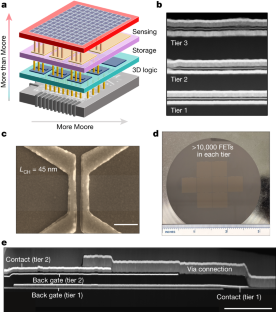

In the field of semiconductors, three-dimensional (3D) integration not only enables packaging of more devices per unit area, referred to as ‘More Moore’1 but also introduces multifunctionalities for ‘More than Moore’2 technologies. Although silicon-based 3D integrated circuits are commercially available3,4,5, there is limited effort on 3D integration of emerging nanomaterials6,7 such as two-dimensional (2D) materials despite their unique functionalities7,8,9,10. Here we demonstrate (1) wafer-scale and monolithic two-tier 3D integration based on MoS2 with more than 10,000 field-effect transistors (FETs) in each tier; (2) three-tier 3D integration based on both MoS2 and WSe2 with about 500 FETs in each tier; and (3) two-tier 3D integration based on 200 scaled MoS2 FETs (channel length, LCH = 45 nm) in each tier. We also realize a 3D circuit and demonstrate multifunctional capabilities, including sensing and storage. We believe that our demonstrations will serve as the foundation for more sophisticated, highly dense and functionally divergent integrated circuits with a larger number of tiers integrated monolithically in the third dimension.

This is a preview of subscription content, access via your institution

Access options

Access Nature and 54 other Nature Portfolio journals

Get Nature+, our best-value online-access subscription

$29.99 / 30 days

cancel any time

Subscribe to this journal

Receive 51 print issues and online access

$199.00 per year

only $3.90 per issue

Buy this article

- Purchase on Springer Link

- Instant access to full article PDF

Prices may be subject to local taxes which are calculated during checkout

Similar content being viewed by others

Data availability

Data on samples produced in the 2DCC-MIP facility are available at https://doi.org/10.26207/khwb-rr73. These include growth recipes and characterization data. Additional datasets generated and/or analysed during this study are available from the corresponding authors on reasonable request.

Code availability

The codes used for plotting the data are available from the corresponding authors.

References

Radosavljevic, M. & Kavalieros, J. 3D-stacked CMOS takes Moore’s law to new heights. IEEE Spectrum https://spectrum.ieee.org/3d-cmos (2022).

Akinwande, D. et al. Graphene and two-dimensional materials for silicon technology. Nature 573, 507–518 (2019).

Ingerly, D. B. et al. Foveros: 3D integration and the use of face-to-face chip stacking for logic devices. In 2019 IEEE International Electron Devices Meeting (IEDM) 19.6.1–19.6.4 (IEEE, 2019).

Yu, D. TSMC packaging technologies for chiplets and 3D. In Proc. 2021 IEEE Hot Chips Vol. 33, 1–47 (TMSC, 2021).

Agarwal, R. et al. 3D packaging for heterogeneous integration. In 2022 IEEE 72nd Electronic Components and Technology Conference (ECTC) 1103–1107 (IEEE, 2022).

Cao, W. et al. The future transistors. Nature 620, 501–515 (2023).

Das, S. et al. Transistors based on two-dimensional materials for future integrated circuits. Nat. Electron. 4, 786–799 (2021).

Zhu, K. et al. Hybrid 2D–CMOS microchips for memristive applications. Nature 618, 57–62 (2023).

Zhou, F. & Chai, Y. Near-sensor and in-sensor computing. Nat. Electron. 3, 664–671 (2020).

Ning, H. et al. An in-memory computing architecture based on a duplex two-dimensional material structure for in situ machine learning. Nat. Nanotechnol. 18, 493–500 (2023).

Shukla, P., Coskun, A. K., Pavlidis, V. F. & Salman, E. An overview of thermal challenges and opportunities for monolithic 3D ICs. In Proc. 2019 on Great Lakes Symposium on VLSI 439–444 (ACM, 2019).

Collaert, N. High Mobility Materials for CMOS Applications (Elsevier, 2018).

Jacob, A. P. et al. Scaling challenges for advanced CMOS devices. Int. J. High Speed Electron. Syst. 26, 1740001 (2017).

Liu, Y. et al. Promises and prospects of two-dimensional transistors. Nature 591, 43–53 (2021).

Liu, L. et al. Uniform nucleation and epitaxy of bilayer molybdenum disulfide on sapphire. Nature 605, 69–75 (2022).

Kim, K. S. et al. Non-epitaxial single-crystal 2D material growth by geometric confinement. Nature 614, 88–94 (2023).

Yang, P. et al. Batch production of 6-inch uniform monolayer molybdenum disulfide catalyzed by sodium in glass. Nat. Commun. 9, 979 (2018).

Zhu, H. et al. Step engineering for nucleation and domain orientation control in WSe2 epitaxy on c-plane sapphire. Nat. Nanotechnol. https://doi.org/10.1038/s41565-023-01456-6 (2023).

Shen, P.-C. et al. Ultralow contact resistance between semimetal and monolayer semiconductors. Nature 593, 211–217 (2021).

Li, W. et al. Approaching the quantum limit in two-dimensional semiconductor contacts. Nature 613, 274–279 (2023).

Smets, Q. et al. Ultra-scaled MOCVD MoS2 MOSFETs with 42 nm contact pitch and 250 µA/µm drain current. In 2019 IEEE International Electron Devices Meeting (IEDM) 23.2.1–23.2.4 https://doi.org/10.1109/IEDM19573.2019.8993650 (2019).

Jiang, J., Xu, L., Qiu, C. & Peng, L,-M. Ballistic two-dimensional InSe transistors. Nature 616, 470–475 (2023).

Mannix, A. J. et al. Robotic four-dimensional pixel assembly of van der Waals solids. Nat. Nanotechnol. 17, 361–366 (2022).

Wachter, S., Polyushkin, D. K., Bethge, O. & Mueller, T. A microprocessor based on a two-dimensional semiconductor. Nat. Commun. 8, 14948 (2017).

Pendurthi, R. et al. Heterogeneous integration of atomically thin semiconductors for non-von Neumann CMOS. Small 18, 2202590 (2022).

Zhu, K. et al. The development of integrated circuits based on two-dimensional materials. Nat. Electron. 4, 775–785 (2021).

Zhu, J. et al. Low-thermal-budget synthesis of monolayer molybdenum disulfide for silicon back-end-of-line integration on a 200 mm platform. Nat. Nanotechnol. 18, 456–463 (2023).

Dodda, A. et al. Active pixel sensor matrix based on monolayer MoS2 phototransistor array. Nat. Mater. 21, 1379–1387 (2022).

Sebastian, A., Pendurthi, R., Choudhury, T. H., Redwing, J. M. & Das, S. Benchmarking monolayer MoS2 and WS2 field-effect transistors. Nat. Commun. 12, 693 (2021).

Zheng, Y., Gao, J., Han, C. & Chen, W. Ohmic contact engineering for two-dimensional materials. Cell Rep. Phys. Sci. 2, 100298 (2021).

Arutchelvan, G. et al. Impact of device scaling on the electrical properties of MoS2 field-effect transistors. Sci. Rep. 11, 6610 (2021).

Jayachandran, D. et al. A low-power biomimetic collision detector based on an in-memory molybdenum disulfide photodetector. Nat. Electron. 3, 646–655 (2020).

Radhakrishnan, S. S. et al. A sparse and spike-timing-based adaptive photoencoder for augmenting machine vision for spiking neural networks. Adv. Mater. 34, 2202535 (2022).

Li, J. et al. A non-volatile AND gate based on Al2O3/HfO2/Al2O3 charge-trap stack for in-situ storage applications. Sci. Bull. 64, 1518–1524 (2019).

Zhang, E. et al. Tunable charge-trap memory based on few-layer MoS2. ACS Nano 9, 612–619 (2015).

Hoang, A. T. et al. Low-temperature growth of MoS2 on polymer and thin glass substrates for flexible electronics. Nat. Nanotechnol. https://doi.org/10.1038/s41565-023-01460-w (2023).

Illarionov, Y. Y. et al. Insulators for 2D nanoelectronics: the gap to bridge. Nat. Commun. 11, 3385 (2020).

Waltl, M. et al. Perspective of 2D integrated electronic circuits: scientific pipe dream or disruptive technology? Adv. Mater. 34, 2201082 (2022).

Lee, D., Das, S., Doppa, J. R., Pande, P. P. & Chakrabarty, K. Impact of Electrostatic Coupling on Monolithic 3D-enabled Network on Chip. ACM Transact. Des. Autom. Electron. Syst. 24, 62 (2019).

Jiang, J., Parto, K., Cao, W. & Banerjee, K. Ultimate monolithic-3D integration with 2D materials: Rationale, prospects, and challenges. IEEE J. Electron Devices Soc. 7, 878–887 (2019).

S.-C. Lin and K. Banerjee, in Wafer Level 3-D ICs Process Technology (eds C. S. Tan et al.) 1–26 (Springer, 2008).

Fu, Y. et al. Graphene related materials for thermal management. 2D Mater. 7, 012001 (2020).

Xuan, Y. et al. Multi-scale modeling of gas-phase reactions in metal-organic chemical vapor deposition growth of WSe2. J. Cryst. Growth 527, 125247 (2019).

Zhang, X. et al. Diffusion-controlled epitaxy of large area coalesced WSe2 monolayers on sapphire. Nano Lett. 18, 1049–1056 (2018).

Schranghamer, T. F. et al. Ultrascaled contacts to monolayer MoS2 field effect transistors. Nano Lett. 23, 3426–3434 (2023).

Acknowledgements

We thank M. Labella and T. F. Schranghamer for developing the scaled lift-off process, and all staff of the Nanofabrication Lab at the Pennsylvania State University for their assistance. The MOCVD samples were grown in the 2D Crystal Consortium Materials Innovation Platform (2DCC-MIP) facility at the Pennsylvania State University, which is supported by the National Science Foundation under cooperative agreement DMR-2039351. This work was supported by the Army Research Office (ARO) through Contract Number W911NF1810268 and National Science Foundation (NSF) through CAREER Award under Grant Number ECCS-2042154. T.V.M. and J.M.R. acknowledge the support of the U.S. Air Force Office of Scientific Research and Clarkson Aerospace Corp. under Award no. FA9550-21-0460.

Author information

Authors and Affiliations

Contributions

S.D., R.P. and D.J. conceived the idea and designed the experiments. D.J., R.P., N.U.S. and M.U.K.S. fabricated all the 3D chips. S.D., D.J., R.P., N.U.S., M.U.K.S. and A.P. performed the experiments, analysed the data, discussed the results and agreed on their implications. N.T., C.C. and T.V.M. grew and characterized the 2D materials under the supervision of J.M.R. S.K. performed the 2-inch MoS2 transfer and characterized the 2D materials under the supervision of J.M.R. Y.Y. and Y.H. performed the FIB and TEM for the 3D chip. All authors contributed to the preparation of the paper.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Nature thanks Tania Roy and the other, anonymous, reviewer(s) for their contribution to the peer review of this work.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Extended data figures and tables

Extended Data Fig. 1 Device Schematic of the 2D FET.

Schematic of the 2D FET device consisting of a 9 nm Al2O3/3 nm HfO2/3 nm Al2O3 floating gate-like stack, the 2D channel (either MoS2 or WSe2), and the source/drain contacts, consisting of 20 nm Ni/10 nm Au for MoS2, or 20 nm Pd/10 nm Au for WSe2.

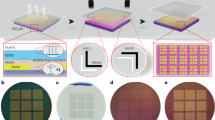

Extended Data Fig. 2 Fabrication flow for 3D Integration of 2D FETs.

a) Fabrication flow to realize 2 tier and 3 tier 3D integrated chips based on 2D FETs. Note that any nonconductive carrier substrate can be used to realize a 3D integrated chip. b) Table showing the number of unique fabrication steps required to realize each tier.

Extended Data Fig. 3 2-tier and 3-tier integrated 3D chips based on 2D FETs.

a) Optical image of a 2-tier chip based on MoS2 FETs. Each cell within the array contains 4 FETs, with two devices in each tier that are stacked vertically. b) Optical image of a 3-tier chip based on MoS2 FETs. Each cell contains 5 FETs with two devices in tier 1, two devices in tier 2, and one device in tier 3, with three devices stacked vertically. Note that the limitation in integrating more devices in each cell is due to geometric constraints in contact pad placement for subsequent measurements.

Extended Data Fig. 4 Electrical characteristics of the 2-tier wafer scale MoS2 devices.

Transfer characteristics and corresponding histograms of SS, ION, and VTH from devices in (a) die 1, (b) die 2, (c) die 3, (d) die 4, (e) die 5 of tier 1, and those in (f) die 1, (g) die 2, (h) die 3, (i) die 4, (j) die 5 of tier 2 is given.

Extended Data Fig. 5 TEM and EDS analysis of the vertically stacked 3-tier MoS2.

a) Zoomed in HAADF-STEM image of each tier shows the thin MoS2 layer between gate dielectric and contact pads. b) Corresponding EDS elemental mapping shows the presence of Mo and S in each tier.

Extended Data Fig. 6 Electrical characteristics of 3-Tier stack of MoS2 and WSe2 FETs.

Transfer characteristics of a) 500 tier 1, b) 500 tier 2, and c) 250 MoS2 FETs with \({L}_{{\rm{CH}}}\) = 300 nm. Transfer characteristics of d) 300 tier 1, e) 300 tier 2, and f) 200 tier 3 MoS2 FETs with \({L}_{{\rm{CH}}}\) = 1000 nm. Transfer characteristics of g) 500 tier 1, h) 500 tier 2, and i) 250 WSe2 FETs with \({L}_{{\rm{CH}}}\) = 300 nm and j) 300 tier 1, k) 300 tier 2, and l) 200 tier 3 WSe2 FETs with \({L}_{{\rm{CH}}}\) = 1000 nm. Note that the WSe2 FETs demonstrate ambipolar transport, with dominant p-type conduction, which is complementary to the n-type conduction observed in MoS2 FETs. 20 nm Ni/10 nm Au stack was used as source/drain contact electrodes for MoS2 FETs and 20 nm Pd/10 nm Au stack was used as source/drain contact electrodes for WSe2 FETs. All transfer characteristics were measured using \({V}_{{\rm{DS}}}\) = 1 V. (*Note that the limitation in the number of devices in tier 3 is due to less contact pad space available, after the fabrication of both tier 1 and tier 2.).

Extended Data Fig. 7 Extracted device parameters for the 3-tier 3D integrated MoS2 and WSe2 FETs.

Distribution of \(SS\), \({I}_{{\rm{ON}}}\), and \({V}_{{\rm{TH}}}\) of 200 MoS2 FETs for a) tier 1, b) tier 2, and c) tier 3, corresponding to the transfer characteristics given in Fig. 3d-f. Distribution of \(SS\), \({I}_{{\rm{ON}}}\), and \({V}_{{\rm{TH}}}\) of 200 WSe2 FETs for d) tier 1, e) tier 2, and f) tier 3 corresponding to the transfer characteristics given in Fig. 3g-i.

Extended Data Fig. 8 Impact of 3D topography on 2D FETs.

AFM scan of a 2-tier MoS2 chip. a) without and b) with an underlying MoS2 device. AFM line scan across the devices show c) 30 nm step height between the channel and the contact for 2nd tier devices and d) 60 nm step height between the channel to the contact for the 3rd tier devices. This is also highlighted in the schematics showing the surface topography prior to the fabrication of e) 2-tier and f) 3-tier devices. Clearly, with increasing number of tiers, the surface topography becomes increasingly complex, which can lead to strain and other mechanical challenges for the transferred 2D films.

Extended Data Fig. 9 Multifunctional 2D FETs.

a) Schematic of a 2-tier MoS2 chip with a via connection between the two tiers, enabling the realization of a 3D integrated inverter. b) Characteristics of the inverter consisting of tier 1 and tier 2 MoS2 FETs. The memory capabilities exhibited by the MoS2 FETs are shown with c) transfer characteristics for ten devices that are programmed in a low conduction state (LCS), and a high conduction state (HCS), d) retention of HCS and LCS for 300 s, and e) endurance taken for 1000 read/write cycles for a \({V}_{{\rm{Program}}}\)= −5 V, \({V}_{{\rm{Program}}}\)= 4 V, and a \({V}_{{\rm{Read}}}\)= −0.5 V for a pulse time of 1 ms. Finally, the photo-sensing capabilities of MoS2 FETs are shown with f) transfer characteristics from 50 devices measured under dark and illuminated conditions (white light, \({P}_{{\rm{IN}}}\) = 15 Wm−2). The extracted g) responsivity (\(R\)) and h) specific detectivity (\({D}^{* }\)).

Supplementary information

Supplementary Information

This file contains Supplementary Information sections 1–9, including Supplementary Figs. 1 and 2, and additional references.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Jayachandran, D., Pendurthi, R., Sadaf, M.U.K. et al. Three-dimensional integration of two-dimensional field-effect transistors. Nature 625, 276–281 (2024). https://doi.org/10.1038/s41586-023-06860-5

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1038/s41586-023-06860-5

This article is cited by

-

A 2D route to 3D computer chips

Nature (2024)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.