Abstract

With the development of wearable devices and hafnium-based ferroelectrics (FE), there is an increasing demand for high-performance flexible ferroelectric memories. However, developing ferroelectric memories that simultaneously exhibit good flexibility and significant performance has proven challenging. Here, we developed a high-performance flexible field-effect transistor (FeFET) device with a thermal budget of less than 400 °C by integrating Zr-doped HfO2 (HZO) and ultra-thin indium tin oxide (ITO). The proposed FeFET has a large memory window (MW) of 2.78 V, a high current on/off ratio (ION/IOFF) of over 108, and high endurance up to 2×107 cycles. In addition, the FeFETs under different bending conditions exhibit excellent neuromorphic properties. The device exhibits excellent bending reliability over 5×105 pulse cycles at a bending radius of 5 mm. The efficient integration of hafnium-based ferroelectric materials with promising ultrathin channel materials (ITO) offers unique opportunities to enable high-performance back-end-of-line (BEOL) compatible wearable FeFETs for edge intelligence applications.

Similar content being viewed by others

Introduction

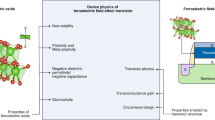

The discovery of hafnium-based ferroelectrics (FE) promoted the development of ferroelectric field-effect transistors (FeFETs), which have ultra-low power consumption, fast erasing speed and strong scalability, making them occupy a place in the field of non-volatile memory (NVM)1,2,3,4,5. The channel conductance of the transistor is controlled by polarization switching of the gate ferroelectric barrier, thereby achieving fast read/write operations of the device6,7. Since the preparation process of FeFETs requires high temperature, it is difficult to be compatible with flexible substrates, which limits its application in the wearable field. Until now, FeFETs based on rigid substrates have exhibited superior performance. Although ferroelectric devices fabricated on flexible substrates, such as systems based on polyvinylidene fluoride (PVDF) and its copolymer polyvinylidene fluoride-trifluoroethylene (PVDF-TrFE), have also demonstrated excellent capabilities, proven to exceed 108 cycles of endurance8,9,10, they are confronted with limitations of film thickness and driving voltage11,12,13,14. Moreover, the requirements for the use scenarios are strict, and the performance in the bending state is difficult to be guaranteed, which limits their practical applications.

And with the scaling of transistor sizes, there is a higher demand for ultra-thin channel materials. For example, two-dimensional van der Waals materials have received more attention15,16. However, these materials usually have high contact resistance with metal electrodes and are easy to form interface traps. More importantly, their preparation processes are not compatible with CMOS17. Studies have shown that oxide semiconductors commonly used as transparent contact layers such as amorphous indium gallium zinc oxide (IGZO) and indium tin oxide (ITO) have become promising candidates for ultra-thin channels18,19,20. They can achieve monolithic 3-D integration, have high carrier mobility, high uniformity wafer-level deposition film formation, excellent flexibility, and their low process temperature overcomes the back-end-of-line (BEOL) low thermal budget process limitations21,22. According to previous reports, the carrier density controllability of the ITO channel can be effectively enhanced through thickness scaling and ferroelectric gating19,22,23. P(VDF-TrFE) is cost-effective, easy to fabricate via sol-gel processing, and requires a low processing temperature, making it a promising ferroelectric material for FeFETs and synaptic devices11,24,25,26. However, P(VDF-TrFE) films are typically thick (over 100 nm) and necessitate higher driving voltages for polarization switching and saturation11,12,13,14. In contrast, thin Zr-doped HfO2 (HZO) exhibits excellent ferroelectric performance at low driving voltages even at a thickness of merely 5nm27,28,29, which is crucial for scalable integrated circuits incorporating ultra-thin oxide semiconductors. Currently, whether it is two-terminal devices like FRAM or three-terminal transistors integrated with IGZO channels, the annealing temperature of HZO has been shown to be compatible with BEOL conditions19,30,31,32. In addition, FeFETs based on HZO have demonstrated synaptic characteristics33. On the other hand, the ferroelectric properties of HZO films fabricated on flexible mica substrates have continued to exhibit exceptional performance34. Nonetheless, achieving high-performance HZO-based ferroelectric memories on flexible substrates remains challenging. Since ferroelectric materials such as Zr-doped HfO2 (HZO) have good switchable polarization, when used as gate ferroelectric dielectrics, they can effectively modulate carriers in the ITO channel, resulting in excellent performance3,35,36.

In this work, we report a BEOL-compatible high-performance FeFET memory device based on HZO and ultrathin ITO channels on a flexible MICA substrate, which outperforms rigid substrates. The proposed FeFET has a minimum subthreshold swing (S.S.) of 33 mV/decade, a current on/off ratio (ION/IOFF) ratio of over 108, and a very large and stable memory window (~2.78 V). FeFET has high endurance of over 107 cycles and good retention characteristics estimated to be over ten years. Under different bending conditions, the conductance modulation of the device has high stability and reliability. In addition, FeFET has excellent pulse cycles endurance (>5 × 105) at a small bending radius (R = 5 mm). Additionally, we demonstrate the application of this device in neuromorphic computing. The excellent performance of flexible FeFET has greatly broadened the application of devices in the wearable field.

Results

Flexible ITO FeFET device structure

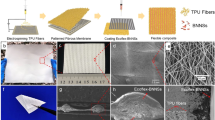

The device structure of the FeFETs is characterized. The optical microscope image of the ITO ferroelectric memory prepared on the flexible MICA substrate in the bent state is shown in Fig. 1a. The device is highly transparent and bendable. Figure 1b is an enlarged structural diagram of a single ITO FeFET. W/Ti and Ni are used as the bottom and top electrodes respectively, where the bottom electrode is prepared in the Al2O3 dielectric layer through a buried gate process. The specific preparation process of the device is shown in Fig. 1c. The thermal budget of the entire preparation process is within 400 °C BEOL compatibility. The micrograph of the device is shown in Supplementary Fig. 1, displaying the shape of gate and source/drain with ITO channel. The channel length and width are 5 μm and 50 μm, respectively.

a Photograph of the device array in a bent state. The device is highly transparent and flexible. b Schematic diagram of BEOL-compatible flexible ITO FeFET memory devices. c The key experimental method flow of HZO-based FeFET fabrication process. The FE HZO is deposited at 250 °C with a cycle ratio of 1:1. d HRTEM image of the Ni/ITO/HZO/W/Ti/Al2O3 gate stack. HRTEM shows clear crystallization of the HZO material and an ultra-thin 3.4 nm ITO channel. e Cross-sectional elemental analysis from EDX spectroscopy of ITO FeFETs. It can be clearly seen that the content of each element corresponds to the depth. The XPS spectra for O 1 s region of the f HZO film and g ITO channel. Oxygen vacancies account for 14.96% and 17.84% of all oxygen-related chemical bonds, respectively. h Atomic force microscope (AFM) image of the surface morphology of ITO film.

Figure 1d, e shows the High-resolution transmission electron microscope (HRTEM) and Energy dispersive x-ray spectroscopy (EDX) images of flexible ITO FeFETs capturing Ni/ ITO/ HZO/ W/ Ti/ Al2O3 stack. HRTEM shows clear crystallization of the HZO material and an ultra-thin 3.4 nm ITO channel. The cross-sectional TEM image of the FeFET and the EDS elemental map of each layer are shown in Supplementary Fig. 2. Figure 1f, g illustrates the X-ray photoelectron spectroscopy (XPS) for O 1s region of the HZO and ITO films respectively. Oxygen vacancies account for 14.96% and 17.84% of all oxygen-related chemical bonds, respectively. The calculation method for oxygen vacancies is presented in Supplementary Fig. 3. The concentration of oxygen vacancies can be controllably altered by adjusting process parameters23,37. An appropriate concentration of oxygen vacancies is crucial for both ITO and HZO. The XPS spectra of ultra-thin 3.4 nm ITO fully shows that it is an excellent semiconductor23. The full XPS spectra of ITO film and HZO film are shown in Supplementary Fig. 4. Atomic force microscopy (AFM) was used to analyze the surface morphology of the ultra-thin ITO film. As can be seen from Fig. 1h, the root-mean-square (RMS) roughness of the ITO film is only 0.51 nm, which proves that through physical vapor deposition (PVD) can obtain a higher quality ITO channel and ensure the performance of the device. The AFM surface analysis of the HZO film is shown in Supplementary Fig. 5, and the RMS is only 1.27 nm.

Device performance of flexible ITO FeFETs

The P-V loops in different voltage of metal/insulator/metal (MIM) capacitors with the structures (a) W/11.4 nm HZO/Ni and (b) W/11.4 nm HZO/3.4 nm ITO/ Ni are shown in Fig. 2a, b. The similar P-V characteristics suggest that the interface of FE and channel is excellent. Different annealing temperatures and electrodes have a significant impact on the ferroelectric properties of HZO. Low-temperature annealing leads to a decline in ferroelectric performance38, while excessively high annealing temperatures result in larger leakage currents39. Since TiN is wet-etched easily and can endow the ferroelectric thin films with larger remnant polarization (Pr) and lower leakage current40, TiN was chosen as the electrode for HZO annealing. Figure 2c displays the measured ID-VG of ITO FeFETs which exhibits a near-ideal S.S. value, high ION/IOFF ratio of 108, and sub-pA gate/substrate leakage. Magnified images of the transistor gate current and the leakage current of the HZO gate stack at different applied voltages are shown in Supplementary Fig. 6. The low level of leakage current ensures the reliability and stability of the device. Figure 2d shows the ID-VD curves, showing high ION of 105 μA/μm at VG = 3 V and VD = 0.1 V. In the small VD range of 0–0.5 V, ID and VG exhibit linearity, demonstrating a good ohmic contact between S/D and channel (Supplementary Fig. 7). The S.S. distribution suggests a good ferroelectric switch in Fig. 2e. At room temperature, S.S. (33 mV/decade) of sub-60 was obtained.

P-V loops of representative capacitors with a W/11.4 nm HZO /Ni and b W/11.4 nm HZO/3.4 nm ITO/Ni. The similar P-V characteristics suggest that the interface of FE and channel is excellent. c Measured ID-VG of ITO FeFETs exhibiting near-ideal S.S. value, high ION/IOFF ratio of 108, and sub-pA. gate/substrate leakage. d Measured ID-VD curve, showing high Ion of 105 μA/μm at VG = 3 V & VD = 0.1 V. e The S.S. distribution of ITO FeFETs devices, showing minimum S.S. of 33 mV/decade. f ID-VG curves for ITO FeFETs. A stable FE type hysteresis with MW up to 2.78 V is available. g Memory window (MW) versus VG, MAX of ITO FeFETs at VD = 0.1 V. MW is calculated as ΔVth in f. Record-high MW of 2.78 V at VG, MAX = 5 V. h Threshold voltages after erase and program versus VG Sweep range of ITO FeFETs at VD = 0.1 V. i Benchmarking of MW and ION/IOFF performance of FeFETs reported in this work (shown as a five-pointed star) versus recently reported FeFETs (shown as other symbols), where the MW is normalized with respect to the ferroelectric layer thickness.

Figure 2f demonstrates the ID-VG curves at different VG sweep ranges for ITO FeFETs with a stable FE type hysteresis. Memory window (MW) versus VG ranges is shown in Fig. 2g, and at VG, MAX = 5 V and VD = 0.1 V, a record-high MW of 2.78 V is available. Figure 2h shows the threshold voltages (Vth) after erase and program versus VG, ± 2 V is enough to program and erase with a large MW. The distribution of key performance indicators (KPIs) for 30 devices is presented in Supplementary Fig. 8, including critical performance information such as the on/off ratio, S.S., MW, and ION. The overall performance of the devices is favorable, which can be attributed to mature device fabrication processes and stable experimental conditions. Figure 2i benchmarks the MW and ION/IOFF performance of the FeFET reported in this work (shown as a five-pointed star) against those reported in the last three years (shown as other symbols), with the MW is normalized relative to the ferroelectric layer thickness19,41,42,43,44,45,46,47,48,49,50,51,52,53,54,55,56,57. Supplementary Table 1 summarizes the key parameters of the flexible ITO FeFET in this study compared with the control group. This device successfully implements ultra-thin ITO channel high-performance BEOL-compatible ferroelectric memory on a flexible substrate, and has obvious advantages over other FeFETs, including S.S. as small as 33 mV/decade and ION/IOFF ratio exceeding 108 and record high normalized MW of 0.24 V/nm.

The operational mechanism of FeFET is shown in Fig. 3a. Ferroelectric polarization switches can modulate the Vth of the device by reversing the polarity of the polarization-bound charges, thereby achieving a counterclockwise ID-VG curve. When a positive gate voltage is applied, the ferroelectric polarization is oriented upwards, resulting in the accumulation of charges in the channel, corresponding to the programming state. Conversely, when a negative gate voltage is applied, the ferroelectric polarization is reversed, leading to depletion of charge carriers in the channel, corresponding to the erasing state. Figure 3b, c shows pulse sequence for endurance and retention test. For endurance measurement, the pulse width of erase and program processes are VP (+3.8 V,100 μs) and VE (−2 V,100 μs). For retention measurement, the pulse width of both erase and program processes are 500 μs with amplitude of 3.8 V. Figure 3d shows the retention characteristics of the ITO FeFETs. Optimized retention extrapolated as >10 years at VD = 0.1 V. Figure 3e displays the great performance of the ITO FeFETs endurance property and a high endurance exceeding 2 × 107 cycles is achieved. Figure 3f benchmarks the retention and endurance performance of FeFETs reported in this work (shown as five-pointed stars) against those reported in the past three years (shown as other symbols)19,41,47,48,51,52,53,54,55,56,57,58,59. A more detailed parameter comparison is shown in Supplementary Table 2. Compared with other FeFETs, the flexible ultrathin ITO channel ferroelectric memory has longer data retention time and better endurance characteristics.

a The charge distribution and polarization states of the ultra-thin ITO channel FeFET in programming mode (above) and erasing mode (below). b Pulse sequence for endurance test used. Pulse width of erase and program processes are VP (3.8 V, 100 μs) and VE (−2 V, 100 μs). c Pulse sequence for retention test used. Pulse width of both erase and program processes are 500 μs with amplitude of 3.8 V. d Retention characterization of the ITO FeFETs. Optimized retention extrapolated as >10 years. at VD = 0.1 V. e Performance of the endurance property for the ITO FeFETs. High endurance exceeding 2 × 107 cycles. f Benchmarking the retention and endurance performance of FeFETs reported in this work (shown as five-pointed stars) against recently reported FeFETs (shown as other symbols).

Experimental characterization of synaptic properties of flexible ITO FeFETs

The neuromorphic computing properties of the ITO FeFETs under different bending test conditions are studied. Figure 4a is a schematic diagram of the test of a flexible device under a certain bending radius. The highly transparent and flexible devices are bent on the surface of a cylindrical with different radii (R = 7 mm or R = 5 mm). The real-time test photos of the FeFETs on the ultrathin MICA being characterized under the folded state in Supplementary Fig. 9. The information transfer of biological synapses and corresponding artificial synaptic devices is shown in Fig. 4b. Excitatory or inhibitory stimuli are transmitted from the presynaptic neuron to the postsynaptic neuron across the synaptic cleft. In artificial synapse device, the gate and source/drain electrodes correspond to presynaptic and postsynaptic neurons, respectively. Synaptic plasticity corresponds to the postsynaptic current (PSC), the conductance level of the device.

a Schematic diagram of device flexibility testing. b The information transmission at biological synapses and corresponding artificial synaptic devices. c PPF under different bending cycles caused by paired pulses with a time interval of 500 ms. The inset is the PPF index extracted from the curve, constant at 141%. The transition from STM to LTM is achieved by changing the applied d pulse frequency and e pulse amplitude. f High-pass filtering characteristics of ITO FeFETs. g Learning behavior of ITO FeFETs. After 130 s of forgetting process, the FeFETs can reach the initial current level after only 27 same pulses revealing excellent memory retention. h The learning-forgetting process of ITO FeFETs under different bending radii of 5 mm and 7 mm. The inset presents the dependence of relaxation time on radius. i Relaxation time constant (τ) as a function of applied pulse parameters.

Paired pulse facilitation (PPF) is an important manifestation of short-term synaptic plasticity. Triggered by pulses (3 V, 200 μs) with a time interval of 500 ms, paired-pulse facilitation (PPF) under different bending cycles of R = 7 mm is displayed in Fig. 4c. The inset is the PPF index (A2/A1) extracted from the curve, constant at 141% which illustrates that it maintains good state after bending 1000 cycles. In addition to short-term synaptic plasticity, long-term synaptic plasticity is crucial for organisms’ behaviors such as learning and memory60,61. The transition from short-term memory (STM) to long-term memory (LTM) can be achieved in ITO artificial synaptic devices by changing the applied pulse parameters. When the parameters of a single applied pulse are fixed (1 V, 50 μs), as the applied pulse frequency increases from 0.2 Hz to 4 Hz in Fig. 4d, the level of PSC gradually increases and acquires a slower decay rate. Similarly, when applying 20 consecutive pulses with a fixed time interval of 1 s and a pulse width of 50 μs, as the pulse amplitude increases from 0.8 V to 2 V, the promotion of memory level is achieved. (Fig. 4e).

In biological nervous systems, synapses with low neurotransmitter release probability can function as high-pass filters, which is crucial for organisms to process redundant information62. Figure 4f shows the simulation of high-pass filtering characteristics. 20 continuous pulses (1 V, 50 μs) are applied to the ITO FeFET at different frequencies. If the cut-off current (blue dotted line) is set to 80 nA, only the frequency is higher than 1 Hz signals can be transmitted. In addition, we simulated the learning behavior of organisms, and the results are shown in Fig. 4g. First, 47 pulses (3 v, 200 μs) are applied to bring the organism’s memory to a higher level. After 130 s of forgetting process, the ITO FeFETs can reach the initial current level after only 27 same pulses, which proves its excellent memory retention ability.

In addition, ITO FeFETs under different bending radii were used to simulate the learning-forgetting behavior of organisms (Fig. 4h). First, 50 consecutive pulses (3 V, 200 μs) are applied to devices with different bending radii (flat, R = 7 mm, R = 5 mm) to make the PSC reach a high level, followed by a natural forgetting process of up to 200 s. Memory retention was further quantified using the Kohlrausch equation63,64:

where Ie is the current at the final steady state, t is time, and τ is the relaxation time constant. The τ obtained by the Kohlrausch equation is shown in the inset of Fig. 4h. Under three bending radii, the conductance level of the device is continuously and stably modulated, and the τ is similar. When the number of pulses (N = 30/50) increases and the pulse parameters (2 V, 100 μs or 3 V, 200 μs) increase, the τ increases exponentially, which also corresponds to the improvement of memory level and the formation of LTM (Fig. 4i).

Bending reliability of flexible ITO FeFETs

Next-generation flexible and wearable neuromorphic computing devices must be able to maintain stable synaptic properties under small bending radii and have continuous and uniform conductance switching behavior. Figure 5a demonstrates the used pulse sequence for potentiation-depression cycling stress tests and one cycle consists of 100 potentiating pulses and the subsequent 100 depressing pulses. All the currents are measured with an applied bias of −0.1 V on the postsynaptic neuron. The repetitive long-term potentiation/depression (LTP/LTD) operations in the folded devices during 5 × 105 spikes of presynaptic pulses (±2 V, 100 μs) are measured in Fig. 5b. The initial and last 5 cycles LTP and LTD operations reveal the pulse cycling robustness of the FeFETs under bending conditions (Fig. 5c, d). Additionally, we have investigated the impact of different bending radii and bending cycles on the response of the HZO gate stack and the ION/IOFF ratio, endurance, and other performances of FeFETs, as shown in Supplementary Figs. 10 and 11. The device performance remains stable under different application scenarios.

a Pulse sequence for Potentiation-depression cycling stress tests used. One cycle was 100 potentiating pulses and the subsequent 100 depressing pulses. All the currents were measured with an applied bias of −0.1 V on the postsynaptic neuron. b Repetitive LTP and LTD operations in the folded FeFETs during 50 K spikes of presynaptic pulses. c, d Show the LTP and LTD during the initial and final 5 cycles, respectively. e MNIST pattern recognition accuracy was evaluated by backpropagation (BP) algorithm. A high recognition accuracy close to the ideal was obtained in ITO FeFETs after applying 600 pulses and 48 K pulses. f Schematic diagram of the device’s bending strain. g–i Stress variation of the device during the bending process. The stress distribution on different functional layers was obtained through FEA simulation as the bending radius changed.

Artificial neural networks based on ITO FeFET synaptic devices

We constructed an artificial neural network (ANN) using ITO FeFETs to recognize handwritten digits in the MNIST database (Supplementary Fig. 12). The network consists of an input layer (784 neurons), a hidden layer (64 neurons), and an output layer (10 neurons)65. The process of training and recognizing digital images using ANN65,66, including signal forward propagation and error backpropagation, is depicted in Supplementary Fig. 13. The relationship between network recognition accuracy and factors such as the number of neurons in the hidden layer and the initial values of weights V and W, which significantly influence the accuracy and efficiency of ANN classification, is shown in Supplementary Fig. 14. The correlation between recognition accuracy and the proportion of noise pixels is demonstrated in Supplementary Fig. 15, illustrating the robust fault tolerance of the constructed ANN. The device conductance levels after 600 and 48,000 pulse operations were extracted for network training. The average confusion matrix change during the pattern training epochs is shown in Supplementary Fig. 16. As the training process proceeds, the inferred output becomes consistent with the desired output. After 1000 iterations of training based on the backpropagation (BP) algorithm, the recognition rates of the two groups of flexible ferroelectric neural networks reached 91.8% and 90.8%, respectively (Fig. 5e). This negligible difference is crucial for wearable platforms to be used for more complex neural processing to realize truly wearable smart electronics.

In order to comprehend the impact of stress distribution on the degradation of device performance, finite element analysis (FEA) was conducted using ABAQUS software. Figure 5f illustrates the schematic of bending strain for the two-point bending operation, where stress is applied from both sides of the device. A two-dimensional model for the device structure was established, as depicted in Supplementary Fig. 17, with the material parameters outlined in Supplementary Table 3. The model assumes perfect bonding at the interfaces between different layers. In the simulation, the folding process was simulated by incrementally increasing the displacement loading (DL). In the initial state (Fig. 5g), no apparent structural defects were observed in the device. As shown in Fig. 5h, with the gradual reduction of the bending radius, the internal stress of the device increased, leading to the formation of stress concentration points. With the continued application of external pressure, the stress concentration in the device readily induced crack formation and propagation within the device, ultimately resulting in a deterioration of device performance or even device failure (Fig. 5i). Analyzing the impact of displacement loading on the device’s lifespan contributes to understanding stress propagation paths and exploring device failure mechanisms. This, in turn, facilitates the enhancement of the reliability of flexible devices subjected to bending stress.

Discussion

In summary, addressing the challenges of achieving high-performance ferroelectric memory on flexible substrates, based on ultra-thin (3.4 nm) ITO channel and ferroelectric material HZO, a BEOL-compatible high-performance ITO FeFET was prepared on a flexible MICA substrate with a thermal budget below 400 °C. Since the PVD ITO channel exhibits a low thermal budget of 200 °C, highly controllable thickness, wafer-level uniformity and conformality, and ultra-high electron mobility, the prepared FeFET has a minimum S.S. of 33 mv/decade, an ION/IOFF ratio exceeding 108, and an excellent large MW of 2.78 V. In terms of memory characteristics, the endurance of ITO FeFETs >2 × 107 cycles, and the data retention >10 years. The above parameters are at the leading level among reported FeFETs. In addition, the prepared ITO FeFET is transparent and bendable. The device successfully simulates a variety of biological synaptic behaviors under different bending radii, and its performance remains stable after multiple bending cycles. The most important is that when 5 × 105 pulses are continuously applied to the device with a bending radius of 5 mm, the conductance modulation behavior of the device is uniform and stable. This demonstrates the device’s bending reliability and excellent high pulse cycle durability. We believe that continuous efforts in this innovative approach are expected to pave the way for future electronic devices, promoting the application of ferroelectric memories in wearable, foldable electronics.

Methods

Device fabrication

Figure 1c illustrates the key experimental process. After solvent clean of the MICA substrate, 100 nm Al2O3 was grown at 250 °C by atom layer deposition (ALD) using (CH3)3Al (TMA) and H2O as precursors. Gate isolation was performed by dry etching by BCl3/Ar. Then the bottom electrode was patterned by lithography and deposited 10 nm Ti/ 80 nm W by sputtering. The FE 11.4 nm HZO was grown by ALD at 250 °C with a cycle ratio of 1:1. 80 nm TiN was sputtered as a sacrificial capping layer (SCL) and rapid thermal annealing (RTA) at 400 °C for 30 s in N2. The TiN SCL was removed by a mixture of ammonia, hydrogen peroxide, and water (NH3: H2O2: H2O = 1:1:5). The 3.4 nm ITO was deposited by sputtering at 200 °C under an oxygen ratio of 15% ([O]/[O]+[Ar] = 15%). The top electrode 70 nm sputtered Ni was patterned by bi-layer photoresist lithography as Source/ Drain (S/D). Channel area was defined by BCl3/Ar dry etching. The channel length and width were 5 and 50 μm. The thermal budget of the entire fabrication process is below 400 °C, so the device performance is expected to remain unchanged under back-end-of-line (BEOL) conditions.

Device characterization

The basic electrical characteristics and synaptic characteristics of ITO FeFETs were tested under dark conditions and room temperature by Agilent B1500A semiconductor parameter analyzer. Pulse signals with different parameters (amplitude, width) are applied to the device through an arbitrary function generator (KEYSIGHT B1525A). The ferroelectric polarization hysteresis loop of the device was measured with a precision LC analyzer (Radiant Technologies Inc.). In the cross-sectional TEM test of the device, FIB precision sample preparation (FEI Helios) was first performed, followed by TEM analysis (FEI Talos F200X). X-ray photoelectron spectroscopy (XPS) was obtained using a Thermo ESCALAB 250Xi XPS system. Atomic force microscopy (AFM; Dimension Edge, Bruker) was used to analyze the surface morphology of ITO and HZO films.

Data availability

The source data that support the findings of this study are available in figshare with the identifier [https://doi.org/10.6084/m9.figshare.25374901].

Code availability

Code from this study is available from the corresponding author upon request.

References

Khan, A. I., Keshavarzi, A. & Datta, S. The future of ferroelectric field-effect transistor technology. Nat. Electron. 3, 588–597 (2020).

Yurchuk, E. et al. Charge-trapping phenomena in HfO 2-based FeFET-type nonvolatile memories. IEEE Trans. Electron Devices 63, 3501–3507 (2016).

Liang, Z. et al. A novel high-endurance FeFET memory device based on ZrO 2 anti-ferroelectric and IGZO channel. 2021 IEEE International Electron Devices Meeting (IEDM) (IEEE, 2021).

Wang, X. et al. Van der Waals engineering of ferroelectric heterostructures for long-retention memory. Nat. Commun. 12, 1109 (2021).

Toprasertpong, K., Takenaka, M. & Takagi, S. Direct observation of interface charge behaviors in FeFET by quasi-static split CV and Hall techniques: Revealing FeFET operation. 2019 IEEE International Electron Devices Meeting (IEDM) (IEEE, 2019).

Miller, S. & McWhorter, P. Physics of the ferroelectric nonvolatile memory field effect transistor. J. Appl. Phys. 72, 5999–6010 (1992).

Kim, J. Y., Choi, M.-J. & Jang, H. W. Ferroelectric field effect transistors: Progress and perspective. APL Mater. 9, 021102 (2021).

Majumdar, S. Back‐end CMOS compatible and flexible ferroelectric memories for neuromorphic computing and adaptive sensing. Adv. Intell. Syst. 4, 2100175 (2022).

Li, Q.-X. et al. Ferroelectric artificial synapse for neuromorphic computing and flexible applications. Fundamental Res. 3, 960–966 (2023).

Dang, Z., Guo, F., Wu, Z., Jin, K. & Hao, J. Interface Engineering and Device Applications of 2D Ultrathin Film/Ferroelectric Copolymer P (VDF‐TrFE). Advanced Physics. Research 2, 2200038 (2023).

Dang, Z. et al. Black Phosphorus/Ferroelectric P (VDF-TrFE) Field-Effect Transistors with High Mobility for Energy-Efficient Artificial Synapse in High-Accuracy Neuromorphic Computing. Nano Lett. 23, 6752–6759 (2023).

Rahi, S., Raghuwanshi, V., Konwar, G. & Tiwari, S. P. High-Performance Flexible Solution-Processed Organic Nonvolatile Memory Transistors. IEEE Trans. Electron Devices 70, 4338–4344 (2023).

Lee, K. H. et al. High‐mobility nonvolatile memory thin‐film transistors with a ferroelectric polymer interfacing ZnO and pentacene channels. Adv. Mater. 21, 4287–4291 (2009).

Lee, K.-J., Yang, T.-Y., Chou, D.-W. & Wang, Y.-H. Hybrid Ferroelectric P (VDF-TrFE)/BZT Insulators for Pentacene-Based Nonvolatile Memory Applications. IEEE Electron Device Lett. 43, 1463–1466 (2022).

Wu, F. et al. Vertical MoS2 transistors with sub-1-nm gate lengths. Nature 603, 259–264 (2022).

Liu, X. et al. Post-CMOS compatible aluminum scandium nitride/2D channel ferroelectric field-effect-transistor memory. Nano Lett. 21, 3753–3761 (2021).

Kim, M.-K., Kim, I.-J. & Lee, J.-S. CMOS-compatible ferroelectric NAND flash memory for high-density, low-power, and high-speed three-dimensional memory. Sci. Adv. 7, eabe1341 (2021).

Chand, U. et al. 2-kbit array of 3-D monolithically-stacked IGZO FETs with low SS-64mV/dec, ultra-low-leakage, competitive μ-57 cm 2/Vs performance and novel nMOS-only circuit demonstration. 2021 Symposium on VLSI Technology. 1–2 (IEEE, 2021).

Sun, C. et al. Temperature-dependent operation of InGaZnO ferroelectric thin-film transistors with a metal-ferroelectric-metal-insulator-semiconductor structure. IEEE Electron Device Lett. 42, 1786–1789 (2021).

Ishizu, T. et al. An Energy-Efficient Normally Off Microcontroller With 880-nW Standby Power, 1 Clock System Backup, and 4.69-us Wakeup Featuring 60-nm CAAC-IGZO FETs. IEEE Solid State Circ. Lett. 2, 293–296 (2019)..

Nomura, K. et al. Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors. Nature 432, 488–492 (2004).

Si, M. et al. BEOL compatible indium-tin-oxide transistors: Switching of ultrahigh-density 2-D electron gas over 0.8× 10 14/cm 2 at oxide/oxide interface by the change of ferroelectric polarization. IEEE Trans. Electron Devices 68, 3195–3199 (2021).

Li, S. et al. Nanometre-thin indium tin oxide for advanced high-performance electronics. Nat. Mater. 18, 1091–1097 (2019).

Shen, C.-K., Chaurasiya, R., Chen, K.-T. & Chen, J.-S. Synaptic Emulation via Ferroelectric P (VDF-TrFE) Reinforced Charge Trapping/Detrapping in Zinc–Tin Oxide Transistor. ACS Appl. Mater. Interfaces 14, 16939–16948 (2022).

Lee, Y. T. et al. Nonvolatile ferroelectric memory circuit using black phosphorus nanosheet-based field-effect transistors with P (VDF-TrFE) polymer. ACS Nano 9, 10394–10401 (2015).

Chu, F. J., Chen, Y. C., Shih, L. C., Mao, S. C. & Chen, J. S. Reconfigurable Physical Reservoir Enabled by Polarization of Ferroelectric Polymer P (VDF–TrFE) and Interface Charge‐Trapping/Detrapping in Dual‐Gate IGZO Transistor. Adv. Funct. Mater., 34, 2310951 (2023).

Ali, T. et al. A multilevel FeFET memory device based on laminated HSO and HZO ferroelectric layers for high-density storage. 2019 IEEE Annual International Electron Devices Meeting (IEDM) (IEEE, 2019).

Kim, S. J. et al. Low-voltage operation and high endurance of 5-nm ferroelectric Hf0. 5Zr0. 5O2 capacitors. Appl. Phys. Lett. 113, 182903 (2018).

Lyu, X. Polarization and Switching Dynamics Study of Ferroelectric Hafnium Zirconium Oxide for Feram and Fefet Applications. (Purdue University, 2023).

Luo, Q. et al. A highly CMOS compatible hafnia-based ferroelectric diode. Nat. Commun. 11 1391 (2020).

Du, Y. et al. Monolithic 3D Integration of FeFET, Hybrid CMOS Logic and Analog RRAM Array for Energy-Efficient Reconfigurable Computing-In-Memory Architecture. 2023 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits). 1−2 (IEEE, 2023).

Zheng, Z. et al. BEOL-Compatible MFMIS Ferroelectric/Anti-Ferroelectric FETs-Part I: Experimental Results With Boosted Memory Window. In IEEE Transactions on Electron Devices (IEEE, 2023).

Sun, C. et al. Novel a-IGZO anti-ferroelectric FET LIF neuron with co-integrated ferroelectric FET synapse for spiking neural networks. 2022 International Electron Devices Meeting (IEDM) (IEEE, 2022).

Xiao, W. et al. Thermally stable and radiation hard ferroelectric Hf0. 5Zr0. 5O2 thin films on muscovite mica for flexible nonvolatile memory applications. ACS Appl. Electron. Mater. 1, 919–927 (2019).

Sun, C. et al. Highly scaled InGaZnO ferroelectric field-effect transistors and ternary content-addressable memory. IEEE Trans. Electron Devices 69, 5262–5269 (2022).

Lu, T., Liang, R., Zhao, R., Yang, Y. & Ren, T.-L. Fabrication and characterization of ferroelectric HfZrO-based synaptic transistors with multi-state plasticity. 2020 IEEE Electron Devices Technology & Manufacturing Conference (EDTM). 1–4 (IEEE, 2020).

Li, Z. et al. Understanding the Effect of Oxygen Content on Ferroelectric Properties of Al-Doped HfO Thin Films. IEEE Electron Device Lett. 44, 56–59 (2022).

Shibayama, S., Nishimura, T., Migita, S. & Toriumi, A. Thermodynamic control of ferroelectric-phase formation in HfxZr1− xO2 and ZrO2. J. Appl. Phys. 124, 184101 (2018).

Jeon, S., Das, D. & Gaddam, V. Effect of high pressure annealing temperature on the ferroelectric properties of TiN/Hf 0.25 Zr 0.75 O 2/TiN capacitors. 2020 4th IEEE Electron Devices Technology & Manufacturing Conference (EDTM). 1–3 (IEEE, 2020).

Cao, R. et al. Effects of capping electrode on ferroelectric properties of Hf 0.5 Zr 0.5 O 2 thin films. IEEE Electron Device Lett. 39, 1207–1210 (2018).

Saitoh, M. et al. HfO 2-based FeFET and FTJ for ferroelectric-memory centric 3D LSI towards low-power and high-density storage and AI applications. 2020 IEEE International Electron Devices Meeting (IEDM) (IEEE, 2020).

Mo, F. et al. Low-voltage operating ferroelectric FET with ultrathin IGZO channel for high-density memory application. IEEE J. Electron Devices Soc. 8, 717–723 (2020).

Yang, J. Y., Yeom, M. J., Park, Y., Heo, J. & Yoo, G. Ferroelectric α‐In2Se3 Wrapped‐Gate β‐Ga2O3 Field‐Effect Transistors for Dynamic Threshold Voltage Control. Adv. Electron. Mater. 7, 2100306 (2021).

Kim, M.-K., Kim, I.-J. & Lee, J.-S. Oxide semiconductor-based ferroelectric thin-film transistors for advanced neuromorphic computing. Appl. Phys. Lett. 118, 032902 (2021).

Aabrar, K. A. et al. BEOL compatible superlattice FerroFET-based high precision analog weight cell with superior linearity and symmetry. 2021 IEEE International Electron Devices Meeting (IEDM) (IEEE, 2021).

Lin, Z. et al. High-Peformance BEOL-Compatible Atomic-Layer-Deposited In 2 O 3 Fe-FETs Enabled by Channel Length Scaling down to 7 nm: Achieving Performance Enhancement with Large Memory Window of 2.2 V, Long Retention> 10 years and High Endurance> 10 8 Cycles. 2021 IEEE International Electron Devices Meeting (IEDM) (IEEE, 2021).

Li, Z. et al. A 3D vertical-channel ferroelectric/anti-ferroelectric FET with indium oxide. IEEE Electron Device Lett. 43, 1227–1230 (2022).

Persson, A. E., Zhu, Z., Athle, R. & Wernersson, L.-E. Integration of ferroelectric Hf x Zr 1-x O 2 on vertical III-V nanowire gate-all-around FETs on silicon. IEEE Electron Device Lett. 43, 854–857 (2022).

Hasan, M. M. et al. Improvement of Amorphous InGaZnO Thin-Film Transistor With Ferroelectric ZrO x/HfZrO Gate Insulator by 2 Step Sequential Ar/O 2 Treatment. IEEE Electron Device Lett. 43, 725–728 (2022).

Aabrar, K. A. et al. BEOL-compatible superlattice FEFET analog synapse with improved linearity and symmetry of weight update. IEEE Trans. Electron Devices 69, 2094–2100 (2022).

Chen, C.-K. et al. First demonstration of ultra-low D it top-gated ferroelectric oxide-semiconductor memtransistor with record performance by channel defect self-compensation effect for BEOL-compatible non-volatile logic switch. 2022 International Electron Devices Meeting (IEDM). (IEEE, 2022).

Chen, C.-K. et al. High-Performance Top-Gated and Double-Gated Oxide–Semiconductor Ferroelectric Field-Effect Transistor Enabled by Channel Defect Self-Compensation Effect. IEEE Trans. Electron Devices 70, 2098–2105 (2023).

Jeong, S. et al. All-Sputter-Deposited Hf 0.5 Zr 0.5 O 2 Double-Gate Ferroelectric Thin-Film Transistor with Amorphous Indium–Gallium–Zinc Oxide Channel. IEEE Electron Device Lett. 44, 749–752 (2023).

Liao, J. et al. Van der Waals Ferroelectric Semiconductor Field Effect Transistor for In-Memory Computing. ACS nano 17, 6095–6102 (2023).

Kim, I.-J., Kim, M.-K. & Lee, J.-S. Design Strategy to Improve Memory Window in Ferroelectric Transistors With Oxide Semiconductor Channel. IEEE Electron Device Lett. 44, 249–252 (2022).

Luo, C. et al. Ferroelectric Hf0. 5Zr0. 5O2-gated synaptic transistors with large conductance dynamic range and multilevel states. Sci. China Mater. 66, 2372–2382 (2023).

Kim, K.-H. et al. Scalable CMOS back-end-of-line-compatible AlScN/two-dimensional channel ferroelectric field-effect transistors. Nat. Nanotechnol. 18, 1044–1050 (2023).

Choi, S.-N., Moon, S.-E. & Yoon, S.-M. Impact of oxide gate electrode for ferroelectric field-effect transistors with metal-ferroelectric-metal-insulator-semiconductor gate stack using undoped HfO2 thin films prepared by atomic layer deposition. Nanotechnology 32, 085709 (2020).

Mondal, S. et al. ScAlN-Based ITO Channel Ferroelectric Field-Effect Transistors With Large Memory Window. In IEEE Transactions on Electron Devices (IEEE, 2023).

Celikel, T., Szostak, V. A. & Feldman, D. E. Modulation of spike timing by sensory deprivation during induction of cortical map plasticity. Nat. Neurosci. 7, 534–541 (2004).

Li, Q. et al. Ultralow power wearable organic ferroelectric device for optoelectronic neuromorphic computing. Nano Lett. 22, 6435–6443 (2022).

Huang, W. et al. Zero-power optoelectronic synaptic devices. Nano Energy 73, 104790 (2020).

Wang, Z. et al. Nanoionics‐enabled memristive devices: strategies and materials for neuromorphic applications. Adv. Electron. Mater. 3, 1600510 (2017).

Li, Q.-X. et al. Flexible organic field-effect transistor arrays for wearable neuromorphic device applications. Nanoscale 12, 23150–23158 (2020).

Li, Q. et al. Organic optoelectronic synaptic devices for energy-efficient neuromorphic computing. IEEE Electron Device Lett. 43, 1089–1092 (2022).

Cao, Y. et al. An Efficient Training Methodology of Hardware Neural Network Based on Wafer-Scale MoS2 Synaptic Array. Adv. Electronic Mater. 8, 2200909 (2022).

Acknowledgements

This work was supported by the National Key R&D Program of China (Grant 2021YFA1202600), the NSFC (Grants 92064009, 22175042), Science and Technology Commission of Shanghai Municipality (22501100900), China Postdoctoral Science Foundation (Grant 2022TQ0068, BX2021070, 2021M700026), and the Zhejiang Lab’s International Talent Fund for Young Professionals.

Author information

Authors and Affiliations

Contributions

Q.L., S.W., and L.C. initiated the research. Q.L., S.W., and J.Y. prepared and characterized the ITO and HZO. Q.L. and X.H. designed the ferroelectric transistors. Q.L. and S.W. fabricated the ferroelectric synaptic transistor. Q.L., Q.S., and Y.Y. conducted the electrical measurements. Q.L. and Z.L. conducts flexible measurement and FEA simulation. Q.L., Q.S., L.C., and D.W.Z. analyzed the data. Q.L. and D.W.Z. wrote the manuscript with input from all the other authors. T.W., Y.L., and J.M. provided support during the manuscript revision process. All authors discussed the results and commented on the manuscript.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Nature Communications thanks Sayani Majumdar, Thomas Kämpfe and the other, anonymous, reviewer(s) for their contribution to the peer review of this work. A peer review file is available.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Li, Q., Wang, S., Li, Z. et al. High-performance ferroelectric field-effect transistors with ultra-thin indium tin oxide channels for flexible and transparent electronics. Nat Commun 15, 2686 (2024). https://doi.org/10.1038/s41467-024-46878-5

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41467-024-46878-5

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.