Abstract

Layered transition metal dichalcogenides have shown tremendous potential for photodetection due to their non-zero direct bandgaps, high light absorption coefficients and carrier mobilities, and ability to form atomically sharp and defect-free heterointerfaces. A critical and fundamental bottleneck in the realization of high performance detectors is their trap-dependent photoresponse that trades off responsivity with speed. This work demonstrates a facile method of attenuating this trade-off by nearly 2x through integration of a lateral, in-plane, electrostatically tunable p-n homojunction with a conventional WSe2 phototransistor. The tunable p-n junction allows modulation of the photocarrier population and width of the conducting channel independently from the phototransistor. Increased illumination current with the lateral p-n junction helps achieve responsivity enhancement upto 2.4x at nearly the same switching speed (14–16 µs) over a wide range of laser power (300 pW–33 nW). The added benefit of reduced dark current enhances specific detectivity (D*) by nearly 25x to yield a maximum measured flicker noise-limited D* of 1.1×1012 Jones. High responsivity of 170 A/W at 300 pW laser power along with the ability to detect sub-1 pW laser switching are demonstrated.

Similar content being viewed by others

Introduction

Photodetectors play a significant role in modern society due to diverse applications across the electromagnetic spectrum, such as in short- and long-range communication, visible and infrared camera sensors, and biomedical imaging. Commercially available high responsivity, high detectivity, and fast photodetectors are based on silicon and group III–V semiconductors. Recently, two-dimensional layered van der Waals (vdW) materials, especially transition metal dichalcogenides (TMDs), have emerged as promising optoelectronic candidates due to their (i) large optical absorption, (ii) broad spectral response ranging from deep ultraviolet to infrared, and (iii) excellent tensile strength for flexible device applications. Among the TMDs, WSe2 has been studied in great detail owing to its (i) sizeable bandgap (~1.2 eV for few-layer and bulk), (ii) relatively high carrier mobility (hole mobility of ~118 cm2/Vs)1, (iii) high absorption coefficient (> 105 cm−1 at 532 nm)2, and (iv) ambient air stability3 unlike other popular vdW materials such as black phosphorus4,5 and InSe6,7.

There exists a strong trade-off between the two key performance metrics of TMD photodetectors, viz. responsivity (R) and speed8. R is directly proportional to the photoconductive gain (G) of a phototransistor, where G depends on the channel mobility and photogenerated carrier lifetime. Most studies have observed that high carrier lifetime leads to large gain, and consequently enhanced photoresponsivity8,9. On the other hand, the speed of a phototransistor decreases with increasing carrier lifetimes. For example, Lopez-Sanchez et al. have reported a monolayer (ML) MoS2 phototransistor with a high responsivity of 880 A/W but a response time > 4 s limits its speed10. Similarly, a WSe2-based phototransistor has been reported with ultrafast rise and fall switching times < 8 μs but with a responsivity of 0.6 A/W11. Hence, ways of attenuating the trade-off between responsivity and speed can truly enable high-performance photodetectors that simultaneously exhibit fast switching and high responsivity. Furthermore, photodetector’s specific detectivity (D*) quantifies its ability to detect low incident laser power such that a large D* value is desirable for highly sensitive photodetection. Typically, D* is limited by the dark current of the detector, and hence, a low dark current is essential to achieve high D*12,13.

In this work, we demonstrate a phototransistor architecture wherein a conventional WSe2 phototransistor has been integrated with an in-plane, lateral, p–n diode in the direction transverse to the source-drain direction. The p–n homojunction diode is electrostatically tunable through gate electrodes. Chemical doping has been employed to enhance the photoresponsivity on layered semiconductors till date14,15. This work relies on electrostatic doping due to its ease of tunability, reversibility, and area selectivity16,17,18. We show substantial attenuation (2x) of the responsivity-speed trade-off through electrostatic modulation of the lateral p–n junction using comprehensive steady-state and temporal photoresponse measurements under a 532 nm laser. As a result, the lateral p–n diode action enables responsivity enhancement by 1.1x –2.4x at nearly the same switching speed (14–16 µs) over a wide range of laser power (300 pW–33 nW). High responsivity (94 A/W), and speed (14 µs) are demonstrated for 1 nW incident power, reaching peak values of 170 A/W at 300 pW. Along with this, a flicker noise-limited maximum measured D* value of 1.1 × 1012 Jones, enhanced by 4.2x –25x due to dark current reduction by the lateral p–n junction, makes this one of the fastest high-responsivity and high-detectivity WSe2 phototransistors till date.

Results

Phototransistor architecture and fabrication

Three interdigitated bottom metal gates (Fig. 1a) were fabricated adjacent to each other on a 285 nm SiO2/Si substrate using e-beam lithography and metal sputtering. The two side gates (SGs) that sandwich the middle gate (MG) were electrically shorted by connecting them with an additional metal line during fabrication. The bottom gates were metallized using a Cr (2 nm)/Au (30 nm) stack. Next, an hBN flake was transferred selectively on top of the three bottom gates, followed by a thin WSe2 flake on top of the hBN. Here hBN serves as the bottom gate dielectric and WSe2 as the channel material. The flake transfers were followed by e-beam patterning of source/drain (S/D) contacts on WSe2 at both ends of the MG, perpendicular to the SG–MG–SG direction and overlapping with the MG. Cr (2 nm)/Pt (30 nm)/Au (80 nm) stack was deposited by sputtering to form S/D contacts. Finally, the as-fabricated device was annealed in ambient at 150 °C for 1 h. The anneal helps in Pt d-orbital hybridization with WSe2, thereby lowering the S/D contact resistance for improved p-type conduction15. This completes the formation of a field-effect transistor (FET) with a WSe2 conduction channel over the MG along with adjacent (side) WSe2 regions over the SGs. The fabrication process flow has been described in detail in Supplementary Fig. 1. Although mechanically exfoliated flakes from bulk crystals have been employed in this work, the use of CVD-grown large area flakes/layers of hBN19 and WSe220 can enable wafer-scale fabrication of a large array of devices. A 3D schematic of the device and an optical microscope image in Fig. 1a, b show the complete device architecture with bottom gates and top S/D contacts. The thickness of the hBN and WSe2 flakes was determined to be ~15 and ~7 nm (around 10 layers) respectively, using atomic force microscopy scans as shown in Fig. 1c. Each of the three gates controls the local carrier density in the WSe2 region above it through electrostatic doping. Besides controlling the carrier density (doping) in the WSe2 side regions, the SGs also control the potential barriers between the WSe2 side regions and the middle channel. Hence, by choosing appropriate MG and SG voltages, it is possible to selectively attain pS–nM–pS or nS–pM–nS band configurations along the SG–MG–SG direction (in-plane and perpendicular to the S/D channel). As a result, the SGs can influence the middle FET action in dark and under illumination. Device simulations with a representative three-gate structure on a thin Si/SiO2 system demonstrate the effect of MG- and SG-induced electrostatic doping on the channel width under dark and the photocarrier population under illumination for varying VSG as shown in Supplementary note 2.

a 3D schematic of the WSe2 phototransistor with middle (MG) and side gates (SG). The transparent blue layer is hBN on top of metal back gates on SiO2/Si and underneath WSe2 (channel material). The top layer in the green (‘Se’ atom) and black (‘W’ atom) ball-stick structure represents WSe2. b Optical microscope image of the device with MG and SGs defined at the bottom and S/D contacts on the top. c AFM scans indicate that the WSe2 channel is 7 nm thick and the hBN gate dielectric is 15 nm thick.

Dark characteristics and photoresponsivity

The formation of lateral p–n junctions at the two SG–MG interfaces, along the sides of the middle channel between S/D, is critical to the demonstration of SG modulation of the photoresponse. To demonstrate electrostatic doping and p–n diode action along the lateral MG–SG direction (diodes are in-plane and perpendicular to the direction of S/D conduction), side contacts (CSG), one on each side of the WSe2 flake over each SG, were fabricated on a separate device having the same architecture of the back gates and S/D contacts. The device schematic is shown in Supplementary Fig. 3a along with a schematic representation of the p–n diode in Fig. 2b inset. The current–voltage (IV) characteristics shown in Supplementary Fig. 3b along with the lateral MG (S contact)-to-SG (CSG) contact change from that of a resistor (n–n) to that of a diode (p–n) with a rectification ratio of ~104, when the SG is kept at a fixed bias (VSG = 2 V) and the MG is tuned from 2 to −2 V. With VSG fixed at 2 V, the WSe2 region over the SG becomes n doped while the doping in the WSe2 region over the MG changes from n to p type when VMG is changed from 2 to −2 V. This clearly shows the formation of a gate tunable lateral p–n junction along the side of the S/D channel. Electron energy band diagrams corresponding to the IV characteristics are shown in Supplementary Fig. 3c. They depict the change from n–n to p–n with appropriate bias voltages at MG and SG.

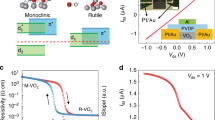

a The transfer characteristic (IDVMG) of FET in dark condition shows an on/off current ratio close to 105 when VSG is not applied. The inset shows the output characteristics (IDVD) without VSG. b Transfer characteristics (IDVMG) for VSG varying from −2 (p+S–pM–p+S) to 2 V (nS–pM–nS), for fixed VD = 1 V, under dark condition. ID decreases, going from p+S–pM–p+S to nS–pM–nS configuration. The inset shows the FET measurement configuration, where MG is the only gate controlling S/D conduction. c Energy band diagrams across the SG–MG–SG direction illustrating the transition from p+S–pM–p+S to nS–pM–nS as VSG changes from −2 to 2 V for fixed VMG = 0 V (sub-threshold region). The semi-transparent box in pink shows the effective source-to-drain channel width under p–p+ and p–n depletion from both sides of the channel. d Normalized change in ID vs source-to-drain channel carrier concentration (\({\mathrm{p}}_{{\mathrm{WSe}}_{2}}\)), showing much higher change at lower concentrations in the sub-threshold region.

Figure 2a shows p-type WSe2 FET transfer characteristics (IDVMG) at VD = 1 V where the source terminal is grounded, under dark, when VSG is not applied. An on/off current ratio of ∼105 and a hole mobility of 5 cm2/Vs indicate good MG control and hole transport respectively. The output characteristics (IDVD) in the inset indicate Schottky barrier-dominated transport across the S/D contacts to the WSe2 channel over the MG. High drain on-current (in nA) for positive voltage bias at the metal source contact to the WSe2 channel, and low off-current (∼pA) confirm the formation of a p-type Schottky contact between Pt and WSe2 that is favourable for hole injection. Dark IDVMG characteristics in Fig. 2b show a monotonous decrease in drain current as VSG changes from −2 to 2 V. This is due to increasing depletion of the hole concentration, resulting in the formation of a lateral pM–nS junction across the MG and SG WSe2 regions, with increasing (more positive) VSG. Hence the width of the conducting S/D channel decreases, leading to a reduction in current. For VMG = 0 V, when VSG is not applied, a pS–pM–pS configuration is formed in WSe2 along the lateral SG–MG–SG direction, as shown in Fig. 2c. Under this condition, since the S/D contacts are patterned with an overlap with only the MG, the S/D conduction channel width is defined by the physical width of the MG (2 µm).

The band diagram shown in Fig. 2c is considered to be flat under No-VSG condition, for a simple understanding of the device operation. On the other hand, when VSG = 2 V is applied for VMG = 0 V, the band configuration changes from pS–pM–pS to nS–pM–nS, as VSG = 2 V induces electrons in both SG WSe2 regions making them n-type. Therefore, with pM–nS configuration between the MG and both SGs, as the space charge region (depletion) encroaches the MG area, it effectively decreases the conduction channel width to < 2 µm. Hence, the absolute S/D current (Idark) decreases in the dark state with positive VSG. Based on this reasoning, band alignment for different VSG conditions for a fixed VMG = 0 V is depicted in Fig. 2c to further understand the trend in Idark when VSG is tuned from −2 to No-VSG to 2 V. Figure 2d shows the relative change in dark current with respect to the channel carrier concentration (\({\mathrm{p}}_{{\mathrm{WSe}}_{2}}\)). It can be seen that SG modulation of the channel current is higher for lower \({\mathrm{p}}_{{\mathrm{WSe}}_{2}}\) in the range of 1013 to 1015 cm−3 (sub-threshold region), as it is easier to deplete at lower S/D channel doping density. The calculation of \({\mathrm{p}}_{{\mathrm{WSe}}_{2}}\) is shown in Supplementary note 4.

Photoresponse of the WSe2 transistor was obtained under 532 nm laser illumination. The light was incident on the entire device area to ensure photogeneration of electron-hole (e-h) pairs in WSe2 over the MG as well as the adjacent SG regions. From the total current upon illumination (Ilight), the photocurrent is obtained as Iph = Ilight − Idark. The Iph vs VMG plot in Fig. 3a shows a monotonous increase in Iph with VSG increasing from −2 to 2 V in the ON state. This trend in Iph with VSG is explained through band diagrams in Fig. 3b. When VMG = 0 V and VSG = 2 V (nS–pM–nS configuration) electric fields (from SG to MG) in the lateral depletion regions drive electrons photogenerated near and in the MG depletion region of WSe2 out towards the SG regions. Similarly, holes photogenerated near and in the SG depletion regions of WSe2 are driven towards the MG channel. These additional holes provide increased photocurrent in the nS–pM–nS configuration. Even a single SG will show a similar but smaller increase in photocurrent through the nS–pM configuration under the ON state. Detailed advantages of using a three-gate structure as compared to the conventional single-gate FET are given in Supplementary note 5. On the other hand, the pS–pM–pS configuration (VMG = 0 V, No-VSG) has a relatively flatter band alignment in the SG–MG–SG direction, while the p+S–pM–p+S configuration (VMG = 0 V, VSG = −2 V) has depletion electric fields directed from the MG towards the SG regions that drive photogenerated holes out from the MG channel towards the SG regions. Consequently, Iph decreases progressively with decreasing VSG. The photoresponsivity (R) in Fig. 3c is calculated using the relation

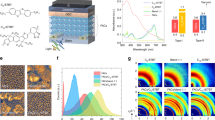

a Iph under light (532 nm laser) vs VMG, with VSG changing from −2 to 2 V. An increase in Iph is observed due to charge separation at the lateral p–n junction leading to an inflow of holes into the MG channel. b Band diagrams across SG-MG-SG showing efficient (holes towards the channel and electrons towards the SG regions) photogenerated e-h separation at the diode depletion regions, going from p+S–pM–p+S to nS–pM–nS configuration. c Responsivity calculated from Iph shows a 24x increase (for fixed VMG = −0.5 V and VD = 1 V) in going from p+S–pM–p+S to nS–pM–nS configuration along the SG-MG-SG direction. d Iph against input optical power shows a sublinear dependency for VSG = −2 and 2 V and without VSG indicating the presence of trap states in the WSe2 channel.

where Pin is the input optical power. Since R is directly proportional to Iph, for a fixed Pin = 33 nW, R can be modulated by nearly 24x from 1 A/W at VSG = −2 V to a high value of 24 A/W at VSG = 2 V, as the band configuration changes from p+S–pM–p+S to nS–pM–nS. Also, R is higher by 2.4x for VSG = 2 V in comparison to the conventional No-VSG configuration. This significant increase in R can be attributed to a two-fold enhancement in Iph as discussed earlier, (a) a decrease in Idark and (b) an increase in Ilight for the same change in VSG that changes the band configuration in SG–MG–SG direction from pS–pM–pS to nS–pM–nS. It is also interesting to note that while VSG modulation of the dark current is maximum in the sub-threshold region, both R and Iph show maximum modulation and maximum or minimum values depending on VSG being positive or negative, when the channel is on (VMG = −0.5 V). This indicates that VSG modulation of Ilight dominates the photoresponse at high hole concentrations in the channel.

Figure 3d shows the dependence of Iph on Pin for fixed VMG = −0.5 V and VSG varying from −2 to 2 V. The power exponent (α) increases from 0.48 to 0.61 as VSG goes from −2 to 2 V and α = 0.52 for No-VSG. \(\alpha\) < 1 indicates the presence of traps in the S/D channel8, which could lead to significant recombination of the photogenerated e-h pairs in the channel before they reach the S/D contacts. The larger the value of α, the lesser is the number of trap states participating in current conduction8,9. Along with a decrease in channel width, an opposite and stronger reverse bias internal electric field builds up as VSG increases from −2 to 2 V. This helps in sweeping out electrons from the conduction band over MG to the SG regions and accumulating holes from the SG regions into the MG channel for VSG = 2 V. On the other hand, for VSG = −2 V, the electrons and holes flow in opposite directions, causing the accumulation of electrons and depletion of holes in the MG area. This leads to more pronounced e-h pair recombination in the case of VSG = −2 V. Hence a smaller number of photogenerated carriers reach the contacts. This is consistent with a lower value of α for VSG = −2 V indicating a higher effective trap density (higher recombination rate) and is one of the factors behind the lower responsivity and photoconductive gain at VSG = −2 V.

Temporal photoresponsivity and detectivity

Next, temporal measurements were carried out to extract the switching speed and analyse the responsivity-speed trade-off under varying VSG conditions. Further, the temporal measurements also enable the extraction of carrier lifetime (τlife), photoconductive gain (G), and external quantum efficiency (EQE) values. Representative photoswitching characteristics obtained under 33 nW incident power at 5 kHz are shown in Supplementary Fig. 9a.

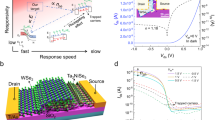

We first present and analyse the data under varying VSG, fixed VMG conditions as shown in Fig. 4a, b, c. Figure 4a shows R and fall time (τf) data for varying VSG at fixed VMG = −0.5 V (maximum R and Iph point in the IphVMG transfer curves of Fig. 3a). R increases from 5.5 to 17 A/W with VSG increasing from 0 to 2 V and, as expected from the R-τf trade-off, τf increases from 14.6 to 15.8 µs. These trends are explained through Fig. 4b which depicts two cases- (1) pS–pM–pS (VSG = VMG = −0.5 V) and (2) nS–pM–nS (VSG = 2 V, VMG = −0.5 V). In case (2), lateral nS–pM and pM–nS band bendings across the SG–MG–SG direction form reverse-biased p–n junctions between MG and the SG WSe2 regions. Hence, as explained in detail in the Supplementary Information (note 8), the equilibrium minority electron concentration in dark condition for case (2), n2, is less than in case (1), n1 (as explained in Fig. 4c), due to a depletion of electrons near the depletion edge in the MG region under reverse bias. Under illumination, these band bendings cause excess photogenerated holes to flow into the S/D channel (opposite for electrons) from both sides and give rise to (i) a very high density of photogenerated holes, and (ii) a large difference in electron and hole concentrations in the S/D channel. These factors decrease the e-h recombination rate (RSRH in Fig. 4c) in case (2) when the laser is turned off, leading to high responsivity but slower speed. In case (1), lateral injection of holes and ejection of electrons is not possible due to a lack of band bending. Hence, compared to case (2), the transistor switches faster but with lower responsivity. Figure 4b plots R vs τf trade-off indicating a slope of 9.8 A/Ws.

For fixed VMG = −0.5 V and varying VSG (a) Responsivity (R) and fall time (τf) data. b R vs τf trade-off indicating a slope of 9.8 A/Ws. c Schematic band diagrams depicting recombination rate (RSRH) dependence on carrier concentrations for (1) pS–pM–pS (VSG = VMG = −0.5 V) and (2) nS–pM–nS (VSG = 2 V, VMG = −0.5 V) configurations. More charge (e-h) separation under nS-pM-nS configuration leads to slower recombination and correspondingly higher lifetime, gain, R, and τf. For varying VMG and No-VSG. d R and τf data. e R vs τf trade-off indicating a slope of 4.2 A/Ws.

Next, we present and analyse the conventional case of varying VMG without any applied VSG (No-VSG) in Fig. 4d, e. Figure 4d shows R and τf data for VMG varying from −0.5 (ON, heavily p-doped channel) to 0.4 V (OFF, low n-doped channel). R decreases as VMG increases towards 0.4 V from −0.5 V. τf also decreases indicating faster switching. These trends, consistent with published reports8,9,21, are explained in detail in Supplementary note 9, and band diagram schematics under light for VMG at (1) −0.5 V, and, (2) 0.4 V are shown in Supplementary Fig. 11. Figure 4e plots the R vs τf trade-off indicating a slope of 4.2 A/Ws.

Comparison of Figs. 4b and 4e indicates a 2x increase in the R vs τf slope (9.8 vs 4.2 A/Ws) when VSG is applied. This indicates that the lateral p–n junction enables higher R for the same speed of operation, a better R vs τf trade-off as compared to conventional means of varying VMG, trap density, and other physical8 or chemical9 processes. It is worth noting that the modulation in R at 5 kHz is smaller than under DC operation (R and D* as a function of operating frequency are shown in Supplementary note 11). This is due to the absence of photogating in the MG, SG, and MG-SG depletion regions at high frequency (discussed in Supplementary note 12)22,23. Reduced photogating results in less efficient photogeneration of holes due to a higher recombination rate. The reduction in photogenerated hole concentration in the MG region, as well as in the number of holes travelling from SG regions to the MG area, results in lower Iph and R under AC operation. Nevertheless, increasing VSG allows an additional knob, besides reduced trap density, for increasing R under AC operation through enhanced photogenerated hole movement into the MG region. Further, the rise or response time (τr) reduces from 23.8 to 21 µs, when VSG is increased from 0 to 2 V with VMG = −0.5 V (see Supplementary Fig. 9b). τr represents the time required for the photogenerated carriers to reach steady-state by trapping and de-trapping in the energetically distributed trap states within the WSe2 bandgap inside the WSe2 channel and at the WSe2/hBN interface24. At VSG = 2 V the photogenerated channel hole concentration is much higher than at VSG = 0 V. Hence the available trap states get filled up faster to reach a steady state. Additionally, a monotonic increase in α with VSG (see Supplementary Fig. 8b) indicates decreasing an effective number of participating traps, thereby reducing τr. Because of both these reasons, τr is the lowest for VSG = 2 V.

Supplementary note 10 details the methodology for calculating carrier lifetimes (τlife), transit times (τtransit), photoconductive gain (G), and EQE. Figure 5a shows that τlife and G = τlife/τtransit increase when VSG is increased from 0 to 2 V at fixed VMG = −0.5 V. This is due to reduced recombination of e-h pairs as the device configuration changes from pS–pM–pS to nS–pM–nS. Figure 5b shows a much smaller increase in G for roughly the same change in τlife as in Fig. 5a, when VMG is decreased from 0.4 to −0.5 V without VSG. This observation is consistent with the larger change in R for the same change in τf with varying VSG as compared to varying VMG (Fig. 4b, e). Although the mobility is relatively low for this device, the high responsivity reported in this study can be attributed to high photoabsorption and photogating effect in WSe2, as reported for other TMD-based phototransistors25,26,27. Higher mobility with lower S/D resistance via S/D contact engineering could further improve the τtransit, G, and R values. Figures 5c and 5d show EQE vs VSG and EQE vs VMG respectively. A maximum EQE of 21.2% is obtained at VSG = 1 V for VMG = −0.5 V, similar to the No-VSG case, since the lateral p–n junction does not affect the fundamental photon absorption and photogeneration processes.

a Carrier lifetimes (τlife) extracted from photoconductive decay fits and calculated photoconductive gain (G) are plotted against VSG for fixed VMG = −0.5 V. Minority electron ejection from and majority hole injection into the S/D channel under nS–pM–nS configuration increases e-h recombination time thereby increasing τlife and G (nearly 2x) vs the pS–pM–pS case. b τlife and G vs VMG, without VSG. The increase in G is much smaller compared to the increase seen for varying VSG, for nearly the same change in τlife. c EQE vs VSG for VMG = −0.5 V. d EQE vs VMG without VSG. Maximum EQE of 21.5 % is obtained for VSG = 1 V, VMG = −0.5 V. The error bars indicate variability (s.e) in photoswitching data.

Figure 6a demonstrates low power photoswitching data for measurements carried out for VSG = 2 V and No-VSG at 1 Hz frequency for a laser power of 0.25 pW. Clear switching behaviour was observed for VSG = 2 V, unlike the No-VSG case, reinforcing the benefit of a lateral p–n junction in enhancing D* of the phototransistor. D* is another important parameter that represents the detector’s ability to measure signals with reference to its noise level. Here in this study D* is calculated using

a. Photoswitching observed for VSG = 2 V at an ultra-low laser power of 0.25 pW, unlike the No-VSG case. b Noise power spectral density (S) from flicker noise measurement for No-VSG and VSG = 2 V shows lower noise floor (by nearly 10x) for VSG = 2 V. c Specific detectivity (D*) at VMG = ± 0.4 V for No-VSG and VSG = 2 V shows 25x enhancement in D* with VSG. Benchmarking plots of (d) R and (e) D* vs fall time (τf).

In the above equation, A is the channel area over the MG. NEP is the noise equivalent power, which is extracted from the measured noise power spectral density (S) data at 1 Hz shown in Fig. 6b and Iph vs Pin plots (shown in Supplementary Figure 15). The S data was determined from the Fourier transform of the dark current time traces measured for fixed drain and varying VMG and VSG voltages, on a similar device (see Supplementary note 14). Figure 6c shows the comparison of D* for No-VSG and VSG = 2 V, at VMG = + /− 0.4 V (OFF/ON conditions). A 25x enhancement in D* is obtained for VSG = 2 V, at VMG = 0.4 V. This can be attributed to a substantial reduction in NEP due to i) enhanced R (~1.45x) resulting from efficient photogenerated hole separation, as well as, ii) decrease in Idark (greater than 10x, see Supplementary note 14) resulting in a decrease in S by nearly an order of magnitude12,13 at 1 Hz for VSG = 2 V when compared to No-VSG. The reduction in NEP due to both these factors increases D*. A maximum D* value of 1.1 × 1012 Jones is obtained.

Finally, Figs. 6d and 6e benchmark responsivity and D* values vs speed respectively, for the WSe2 phototransistor reported in this work with other single 2D material-based (such as MoS2, MoSe2, WSe2, InSe, SnS2, etc.) phototransistors that report the values of all three parameters (R, D* and τf). A clear trade-off between R and τf is observed over a wide range of R (10−3 A/W to 105 A/W) and τf (μs to seconds) (Fig. 6d)10,11,28,29,30,31,32,33,34,35,36,37,38,39,40,41,42,43,44,45,46. When R is high, τf also tends to be very high10,28 indicating slow detector speed. On the other hand, fast speed (low τf) phototransistors show lower R37,40. Our work shows the benefit of high R without slowing down the phototransistor by employing a lateral p–n homojunction. Figure 6e benchmarks both flicker noise- and shot noise-limited (theoretical maximum) D* vs τf values for the same set of reports as shown in Fig. 6d. With high flicker noise-limited (1.1 × 1012 Jones) and shot noise-limited (5 × 1013 Jones) D*, high R (94 A/W) and low τf (14 μs) data, this work reports one of the best combination of R, D* and τf values, enabled by a lateral p–n junction.

Discussion

This work demonstrates a high-performance all-2D layered materials (WSe2/hBN) based phototransistor with a responsivity of 170 A/W at 300 pW laser power, and µs speed of operation, along with the flicker noise-limited measured specific detectivity of 1.1 × 1012 Jones. These high-performance metrics are enabled by a facile electrostatic doping technique that employs a lateral p–n homojunction to control photocarrier population and the width of the conducting channel thereby improving the fundamental responsivity-speed trade-off by nearly 2x. The combined effect of enhanced responsivity and reduction in dark current also improves the detectivity as seen in the ability to detect sub-1 pW laser switching with the help of the lateral p–n junction. From a broader perspective, this study demonstrates a simple optoelectronic device architecture for achieving high responsivity and detectivity without compromising speed, which can be realized in any optically active 2D layered or thin-film semiconductor material that is amenable to electrostatic doping. Further, a lateral heterojunction device with different n and p-type materials could additionally enable a broader spectral response and wavelength selectivity to achieve enhanced performance. This can have promising applications in integrated photonics and optoelectronic devices.

Methods

Device fabrication

A single side polished 4” p+-Si wafer with 285 nm SiO2 grown on top was used as the substrate. Side gates (SG) and a middle gate (MG) were patterned first on top of the Si/SiO2 wafer by electron beam lithography (EBL, Raith 150-Two). This was followed by metal (Cr 2 nm/ Au 30 nm) sputtering (AJA, ATC sputter system) and lift-off. The length and width of the MG channel were 14 and 2 µm respectively. The MG had 3 µm long, 1 µm wide and 3 µm apart leads extending on either side. A total of six such leads (three on each side) were fabricated on both sides of the MG channel to form an inter-digited structure with similar SG leads. The separation between the MG and SG leads was 1.5 µm. Bulk and single-crystal WSe2 and hBN were purchased from SPI supplies. An hBN flake was exfoliated using the micro-mechanical exfoliation technique with 3 M magic scotch tape. The hBN flake was then transferred from the scotch tape onto a polydimethylsiloxane (PDMS) stamp. The PDMS stamp was fixed onto a glass slide and the glass slide was attached to a micromanipulator. The hBN was transferred selectively on top of the pre-fabricated MG and SG structure using the micromanipulator under an Olympus BX-63 microscope. During the transfer process, the Si/SiO2 substrate with its MG and SG pattern was kept on top of a microheater. After the hBN was aligned and placed on top of the SG and MG pattern, the entire structure - Si/SiO2 substrate and the hBN flake along with the PDMS stamp and the glass slide, was heated to 60 °C to weaken the adhesion between the PDMS stamp and hBN. The temperature was then allowed to come down to 50 °C to release the glass slide and the PDMS stamp from the Si/SiO2 substrate, so that only hBN stays on top of the MG and the SG pattern. The same transfer process was followed for aligning and placing WSe2 on top of hBN. The WSe2 flake was placed in such a way, that it covered the entire MG and SG area without touching the extended MG leads going to the source/drain contact pads. Next, source and drain contacts were patterned using EBL on top of WSe2 with an MG overlap such that the actual, physical source-to-drain channel length remained at ~10 µm. Finally, source/drain sputter metallization (Cr 2 nm/ Pt 30 nm/ Au 80 nm) and lift-off were carried out to complete the device fabrication. On a separate sample (Supplementary Information Fig. 3a), two additional lateral contacts on top of the WSe2 transistor, and overlapping with the SG area, were fabricated along with the source/drain contacts, to demonstrate a p–n junction between the source (or drain) and SG contacts.

Device characterization

Before optoelectrical characterization, the device was placed on a PCB with gold contact pads on it. It was then wire bonded using gold wire from the device contact pads to the large PCB contact pads using a wedge bond system. All electrical measurements were done in ambient conditions under a BX-63 Olympus microscope using a Keysight B1500A semiconductor device analyzer. The photo-response measurements were carried out using a 532 nm fiber-coupled diode laser. Steady-state photo-response was measured using Keysight B1500A and the temporal response was measured using a 4 GHz Keysight DSOS404A oscilloscope and current probe (Keysight 2825A). Input laser power was modulated from off to on using square pulses of 1 V peak-to-peak to the laser power controller unit from an Agilent 33220A function generator. The laser was incident on the device through the objective lens of the BX-63 Olympus microscope. Input optical power was varied by inserting suitable optical density filters from HOLMARC in the path of the 532 nm laser beam.

Data availability

All relevant data that support the findings of this study are available from the corresponding authors upon request.

References

Pudasaini, P. R. et al. High-performance multilayer WSe2 field-effect transistors with carrier type control. Nano Res. 11, 722–730 (2018).

Jariwala, D., Davoyan, A. R., Wong, J. & Atwater, H. A. Van der Waals materials for atomically-thin photovoltaics: promise and outlook. ACS Photonics 4, 2962–2970 (2017).

Tosun, M. et al. Air-stable n-doping of WSe2 by anion vacancy formation with mild plasma treatment. ACS Nano 10, 6853–6860 (2016).

Island, J. O., Steele, G. A., Van Der Zant, H. S. J. & Castellanos-Gomez, A. Environmental instability of few-layer black phosphorus. 2D Mater. 2, 011002 (2015).

Koenig, S. P., Doganov, R. A., Schmidt, H., Castro Neto, A. H. & Özyilmaz, B. Electric field effect in ultrathin black phosphorus. Appl. Phys. Lett. 104, 103106 (2014).

Nan, H. et al. Producing air-stable InSe nanosheet through mild oxygen plasma treatment. Semicond. Sci. Technol. 33, 074002 (2018).

Shi, L. et al. Oxidation mechanism and protection strategy of ultrathin indium selenide: insight from theory. J. Phys. Chem. Lett. 8, 4368–4373 (2017).

Thakar, K. et al. Multilayer ReS2 photodetectors with gate tunability for high responsivity and high-speed applications. ACS Appl. Mater. Interfaces 10, 36512–36522 (2018).

Zhao, Q. et al. The role of traps in the photocurrent generation mechanism in thin InSe photodetectors. Mater. Horiz. 7, 252–262 (2019).

Lopez-Sanchez, O., Lembke, D., Kayci, M., Radenovic, A. & Kis, A. Ultrasensitive photodetectors based on monolayer MoS2. Nat. Nanotechnol. 8, 497–501 (2013).

Wang, T. et al. High-performance WSe2 phototransistors with 2D/2D Ohmic contacts. Nano Lett. 18, 2766–2771 (2018).

Kaushik, N., Ghosh, S. & Lodha, S. Low-frequency noise in supported and suspended MoS2 transistors. IEEE Trans. Electron Devices 65, 4135–4140 (2018).

Ghosh, S., Bhatt, P., Tiwari, Y., Joishi, C. & Lodha, S. Temperature and field dependent low frequency noise characterization of Ge n-FETs. J. Appl. Phys.120, 1–5 (2016).

Huo, N. & Konstantatos, G. Ultrasensitive all-2D MoS2 phototransistors enabled by an out-of-plane MoS2 PN homojunction. Nat. Commun. 8, 1–6 (2017).

Wang, Y. et al. Does p-type ohmic contact exist in WSe2-metal interfaces? Nanoscale 8, 1179–1191 (2016).

Li, J. et al. A tunable floating-base bipolar transistor based on a 2D material homojunction realized using a solid ionic dielectric material. Nanoscale 11, 22531–22538 (2019).

Bie, Y. Q. et al. MoTe2-based light-emitting diode and photodetector for silicon photonic integrated circuits. Nat. Nanotechnol. 12, 1124–1129 (2017).

Frisenda, R., Molina-Mendoza, A. J., Mueller, T., Castellanos-Gomez, A. & van der Zant, H. S. J. Atomically thin p–n junctions based on two-dimensional materials. Chem. Soc. Rev. 47, 3339–3358 (2018).

Stehle, Y. et al. Synthesis of hexagonal boron nitride monolayer: control of nucleation and crystal morphology. Chem. Mater. 27, 8041–8047 (2015).

Wang, X. et al. Controllable growth of two-dimensional WSe2 using salt as co-solvent. Cryst. Eng. Comm. 20, 6267–6272 (2018).

Lee, H., Ahn, J., Im, S., Kim, J. & Choi, W. High-responsivity multilayer MoSe2 phototransistors with fast response time. Sci. Rep. 8, 11545 (2018).

Furchi, M. M., Polyushkin, D. K., Pospischil, A. & Mueller, T. Mechanisms of photoconductivity in atomically thin MoS2. ACS Nano. Lett. 14, 6165–6170 (2014).

Hsu, H. P., Lin, D. Y., Jheng, J. J., Lin, P. C. & Ko, T. S. High optical response of niobium-doped WSe2 layered crystal. Materials 12, 1–8 (2019).

Chow, P. C. Y. et al. Dual-gate organic phototransistor with high-gain and linear photoresponse. Nat. Commun. 9, 1–8 (2018).

Cao, Z., Harb, M., Lardhi, S. & Cavallo, L. Impact of interfacial defects on the properties of monolayer transition metal dichalcogenide lateral heterojunctions. J. Phys. Chem. Letts. 8, 1664–1669 (2017).

Liu, E. et al. High responsivity phototransistors based on few-layer ReS2 for weak signal detection. Adv. Func. Mater. 26, 1938–1944 (2016).

Buscema, M. et al. Photocurrent generation with two-dimensional van der Waals semiconductors. Chem. Soc. Rev. 44, 3691 (2015).

Choi, W. et al. High-detectivity multilayer MoS2 phototransistors with spectral response from ultraviolet to infrared. Adv. Mater. 24, 5832–5836 (2012).

Yang, Y., Huo, N. & Li, J. Sensitized monolayer MoS2 phototransistors with ultrahigh responsivity. J. Mater. Chem. C. 5, 11614–11619 (2017).

Choi, M. S. et al. Lateral MoS2 p-n junction formed by chemical doping for use in high-performance optoelectronics. ACS Nano 8, 9332–9340 (2014).

Krishna, M., Kallatt, S. & Majumdar, K. Substrate effects in high gain, low operating voltage SnSe2 photoconductor. Nanotechnology 29, 035205 (2018).

Su, G. et al. Chemical vapor deposition of thin crystals of layered semiconductor SnS2 for fast photodetection application. Nano Lett. 15, 506–513 (2015).

Hafeez, M., Gan, L., Li, H., Ma, Y. & Zhai, T. Large-area bilayer ReS2 film/multilayer ReS2 flakes synthesized by chemical vapor deposition for high performance photodetectors. Adv. Funct. Mater. 26, 4551–4560 (2016).

Feng, W. et al. Ultrahigh photo-responsivity and detectivity in multilayer InSe nanosheets phototransistors with broadband response. J. Mater. Chem. C. 3, 7022–7028 (2015).

Hu, P. et al. Highly responsive ultrathin GaS nanosheet photodetectors on rigid and flexible substrates. Nano Lett. 13, 1649–1654 (2013).

Island, J. O., Blanter, S. I., Buscema, M., Van Der Zant, H. S. J. & Castellanos-Gomez, A. Gate controlled photocurrent generation mechanisms in high-gain In2Se3 phototransistors. Nano Lett. 15, 7853–7858 (2015).

Huang, H. et al. Highly sensitive visible to infrared MoTe2 photodetectors enhanced by the photogating effect. Nanotechnology 27, 445201 (2016).

Ghosh, S. et al. Fast photoresponse and high detectivity in copper indium selenide (CuIn7Se11) phototransistors. 2D Mater. 5, 015001 (2018).

Jacobs-Gedrim, R. B. et al. Extraordinary photoresponse in two-dimensional In2Se3 nanosheets. ACS Nano 8, 514–521 (2014).

Huang, H. et al. Ferroelectric polymer tuned two dimensional layered MoTe2 photodetector. RSC Adv. 6, 87416–87421 (2016).

Tsai, D. S. et al. Few-layer MoS2 with high broadband photogain and fast optical switching for use in harsh environments. ACS Nano 7, 3905–3911 (2013).

Li, S. et al. Enhanced performance of a CVD MoS2 photodetector by chemical in situ n-type doping. ACS Appl. Mater. Interfaces 11, 11636–11644 (2019).

Zhang, W. et al. Role of metal contacts in high-performance phototransistors based on WSe2 monolayers. ACS Nano 8, 8653–8661 (2014).

Xu, H. et al. Spatially bandgap ‑ graded MoS2(1−x)Se2x homojunctions for self ‑ powered visible – near ‑ infrared phototransistors. Nano-Micro Lett.12, 1–14 (2020).

Liang, Q. et al. High-performance, room temperature, ultra-broadband photodetectors based on air-stable PdSe2. Adv. Mater. 31, 1–9 (2019).

Saenz, G. A., Karapetrov, G., Curtis, J. & Kaul, A. B. Ultra-high photoresponsivity in suspended metal-semiconductor-metal mesoscopic multilayer MoS2 broadband detector from UV-to-IR with low schottky barrier contacts. Sci. Rep. 8, 1–11 (2018).

Acknowledgements

The authors thank Shankar Kesarwani for wire bonding the samples and Himani Jawa for her contribution in device fabrication and simulation. The authors also thank Prof. Ageeth Bol and Prof. Peter Steeneken for useful discussions. A.V. thanks the IITB-Monash Research Academy for his fellowship. K.T. acknowledges the Visvesvaraya PhD Scheme from the Ministry of Electronics and Information Technology (MeitY), Govt. of India for his fellowship. The authors acknowledge the Indian Institute of Technology Bombay Nanofabrication Facility (IITBNF) for the usage of its facilities for device fabrication and characterization. This work was funded by the Department of Science and Technology, Govt. of India through the grant DST/SJF/ETA-01/2016-17 and is part of the project ‘Agricultural and environmental 2D gas sensors’ with project number 483.20.029 of the research programme “Science for Diplomacy’’ which is (partly) financed by the Dutch Research Council (NWO).

Author information

Authors and Affiliations

Contributions

S.G. and S.L. conceived the idea. S.G., A.V., and S.D. created the experiment plan and fabricated the WSe2 phototransistors. S.G., A.V., and S.D. carried out the steady-state and temporal photoresponse measurements. K.T. did the AFM measurements for the hBN and WSe2 flakes and participated in technical discussions. S.G. and K.T. simulated the device structure. S.G., K.T., and S.L. analysed the simulated data. S.G. and S.L. analysed the experimental data and benchmarked it against previous reports. All authors contributed to the technical discussion and S.G. and S.L. wrote the manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Peer review information: Nature Communications thanks the anonymous reviewers for their contribution to the peer review of this work. Peer review reports are available.

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Ghosh, S., Varghese, A., Thakar, K. et al. Enhanced responsivity and detectivity of fast WSe2 phototransistor using electrostatically tunable in-plane lateral p-n homojunction. Nat Commun 12, 3336 (2021). https://doi.org/10.1038/s41467-021-23679-8

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41467-021-23679-8

This article is cited by

-

Photogating-assisted tunneling boosts the responsivity and speed of heterogeneous WSe2/Ta2NiSe5 photodetectors

Nature Communications (2024)

-

Ultra-high on-current in two-dimensional Tl2O TFETs with tunneling width modulation

Science China Materials (2024)

-

Effect of Cr doping and photoresponse properties of photodiode based on CdO thin films

Journal of Materials Science: Materials in Electronics (2024)

-

Regulating the conductance of tungsten diselenide by oxygen plasma and improving its electrical stability by encapsulation

Nano Research (2024)

-

Ultra-low power neuromorphic obstacle detection using a two-dimensional materials-based subthreshold transistor

npj 2D Materials and Applications (2023)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.