Abstract

Atomically thin two-dimensional semiconducting materials integrated into van der Waals heterostructures have enabled architectures that hold great promise for next generation nanoelectronics. However, challenges still remain to enable their applications as compliant materials for integration in logic devices. Here, we devise a reverted stacking technique to intercalate a wrinkle-free boron nitride tunnel layer between MoS2 channel and source drain electrodes. Vertical tunnelling of electrons therefore makes it possible to suppress the Schottky barriers and Fermi level pinning, leading to homogeneous gate-control of the channel chemical potential across the bandgap edges. The observed features of ambipolar pn to np diode, which can be reversibly gate tuned, paves the way for future logic applications and high performance switches based on atomically thin semiconducting channel.

Similar content being viewed by others

Introduction

A decade after the first isolation and study of two-dimensional (2D) materials, their atomically precise integration into van der Waals (vdW) planar heterostructures1, 2 is now forming an outstanding platform for developing novel nanoelectronic devices3,4,5. Such platform has been the source of many recent advances in electrical engineering that takes the advantages of the coupling of mono- or few-layered two-dimensional (2D) materials such as graphene, hexagonal boron nitride (h-BN), and transition metal dichalcogenides (TMDCs). It has thus far thrived a rich variety of physical phenomena, including metal oxide semiconductor field effect transistors (FETs)1, spintronics memory devices6, photovoltaics5, and atomically thin superconductors7. Although doping control by an electrostatic gate in those devices has enabled tremendous opportunities, the lack of gapped 2D channel with complementary (p and n) polarities has hampered its application in logic units based on the co-manipulation of diodes and field effect transistors, each has been the core of modern electronics. MoS2 is among the most studied TMDC compounds for both its outstanding electronics and optoelectronics properties as it combines well-defined bandgap, stability in ambient conditions and relatively high charge carrier mobility. Indeed 2H-type molybdenum disulfide (2H-MoS2) has a thickness-dependent bandgap of 1.3 eV indirect gap ~1.9 eV direct gap from bulk down to single layer, respectively8. It therefore holds great promise not only for fundamental studies7, 9, 10, but also for future applications such as high performance FETs and opto-electronics11,12,13,14,15,16,17. Field effect transistors involving atomically thin MoS2 11 as the active channel have enabled original architectures which unlock new features such as sub-thermionic inter-band tunnelling exhibiting unprecedented minimum sub-threshold swing12, or ultra-short gate-length FETs13, opening promising pathways for further enhanced integration.

To fulfill the desired performances of CMOS-type logics using MoS2 FETs, one of the key (yet evasive) goals has been achieving programmable ambipolar operation (i.e., obtaining easily reconfigurable same-chip n- and p-doping in MoS2 FETs). However, to date, only few experiments18,19,20 reported hole transport in MoS2, which was achieved through gate dielectric engineering with high gate voltage operation19 or in an ionic liquid gating environment20. Great efforts have been conducted to pursue ambipolar field effect and further gate tunable rectifying characteristics in MoS2 based heterostructures, including MoS2 coupled with other materials such as carbon nanotube films21. Similar effects can also be found in n-type TMDCs vdW interfaced with p-type TMDCs22, 23 or with organic crystal thin films24.

Here, we show an alternative route based on architecture-engineering: on the basis of the well known technique of vdW heterostructure but with a crucial refinement of the so-called reverted transfer, we enable the fabrication of very reliable high quality h-BN tunnel barriers which gives rise to gate tunable rectification and reversible pn to np diode behaviuor in tunnel-contacted few layer MoS2 transistors.

Results

h-BN as an ultra-thin dielectrics for carrier injection via tunelling

In this work, we demonstrate the design and room temperature operation of FETs based on a tunnel-contacted (TC) MoS2 channel. The tunnel barrier insulating layer is implemented by an ultra-thin capping layer that enables the vertical tunnelling of electrons from the top deposited electrodes. Ultra-thin (one or few monolayer) BN has been identified in the past as an efficient dielectric essential to a number of vertical transport devices, including graphene tunnel transistors25,26,27,28,29,30, and excitonic super-fluid double layer systems31, 32.

As the few-layers h-BN is used as the top most layer, it assumes the role of an atomically uniform potential barrier, across which electrons are coupled through the tunnelling process. For that purpose it is required to be contaminant- and wrinkle-free. Recent results on shot noise measurements in metal–hBN–metal tunnel junctions confirm that h-BN behaves as an ideal tunnel barrier33.

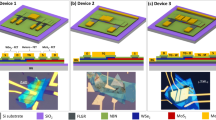

With the conventional scheme of metal/MoS2 contact, Fermi level pinning at the contact interface usually leads to a gate-dependent Schottky barrier (SB)34, which results in extra contact resistance that interferes with device performance (Fig. 1a, c). Here, by using the reverted vdW stacking method (Supplementary Figs. 1 and 2 show the experimental details of the reverted vdW process), large-area and wrinkle-free few-layered h-BN can be inserted between metal contacts and 2D semiconductor channel. We found that the presence of tunnel barriers in the form of two to four layer h-BN can suppress the SB, and chemical potential of the MoS2 layer can be adjusted in a uniform manner across the entire channel, achieving precise electrostatic control of the Fermi level of the 2D layer (Fig. 1b, d). Ambipolar field effect at finite source–drain bias, and consequently fully reversible pn to np diodes by gating was obtained.

Comparison between metal-contacted and metal/insulator tunnel-contacted MoS2 FETs. a Schematics of a metal-contacted MoS2 film leading to a Schottky barrier field effect transistor (SB-FET). b Schematics of a tunnel-contacted MoS2 field effect transistor (TC-FET). c, d Semiconductor representation of the energy levels respectively for SB-FET and TC-FET showing the absence of band bending in TC-FETs. e Schematics cross section of the device showing SB-FET and TC-FET side by side on the same MoS2 flake. f Optical micrograph of a typical TC-FET device. Red dashed line highlights the two to four layer tunnel top h-BN, which covers half the MoS2. Scale bar is 10 μm. g Scanning electron microscopy (SEM) image of the cross-section of the graphite-gated MoS2 vertical tunnel device, with its boxed area zoomed in transmission electron microscopy (TEM) images in h, i

Schematic together with an optical image of a typical TC device is shown in Fig. 1e, f. Same flake of few-layered MoS2 is contacted by normal metal contacts, and TC electrodes. Atomic force microscopy image confirms that devices made by our reverted vdW stacking method exhibit atomically flat top tunnel layer, which is free of wrinkles nor ruptures over 10 × 10 μm2 area (Supplementary Fig. 3). The cross-sectional transmission electron microscopy specimen prepared by focused ion beam of the sample in a local area under metal electrodes is shown in Fig. 1g–i. Typical width of the electrodes are around 1 μm, with the MoS2 channel beneath having dimensions L × W of 1 μm × 1–5 μm for the tested devices. The multi-layered vdW heterostructure can be clearly seen with a tunnel h-BN on top of few-layered MoS2. To improve the gate efficiency and uniformity35, graphite flakes with thickness of about 4–6 nm are used as electrostatic gate spaced by a ~10 nm h-BN under the MoS2 channel (Fig. 1i).

Ambipolar field effect at certain bias condition in MoS2 TC-FETs

First, we characterize the MoS2 FET with conventional Au (50 nm) electrodes. As shown in Supplementary Fig. 4, transport measurements of them show typical n-type FET behaviour. Color map of IV characteristics at fixed gate voltages (V g) indicates ON states at positive and negative bias voltages (V ds) on the electron side, while the channel turns off on the hole side. IV curves at fixed V g slightly deviate from linear behaviour, while the transfer curves at fixed bias voltage V ds show typical n-type unipolar field effect (Supplementary Note 1). These behaviours are standard in MoS2 FET, agree with previously reported9, 11, 15.

A striking consequence of the insertion of an ultra-thin h-BN below metal contact is the dramatic change in the color map of IV curves at fixed gate voltages, as shown in Fig. 2a. Instead of the rather symmetric V ds polarization with ON state only seen in the electron side for metal-contacted MoS2 FET, the vertical TC-FET on the same piece of MoS2 flake, as well as in the same gate range, features strongly asymmetric V ds polarization in the whole gate range. Surprisingly, when V ds is larger than a threshold value of about 1 V, the device starts to exhibit ambipolar transfer curves, with ON state observed on both electron and hole sides at source–drain bias above +1 V. A typical such ambipolar field effect curve is shown in Fig. 2b. A detailed comparison of transfer curves between MoS2 normal FET and TC-FET, as well as data from various samples are given in Supplementary Figs. 5–7 and Supplementary Note 2. We note that recent report shows that a monolayer chemical vapor deposited h-BN spacing layer can diminish SB at the metal contact, giving rise to a tripled output current in the transistor36. However, we did not see such behaviour in our vertical tunnel devices, which may be a result of the less-defected and thicker tunnel h-BN crystals used in this work.

Transport characteristics of MoS2 TC-FETs. a Color map of output curves (I ds vs V ds) at different gate voltages for a typical tunnel-contacted device (room temperature operation). Red and blue-boxed areas highlight the operation range in gate voltage for pn and np diodes, respectively. b Typical ambipolar field effect curve at V ds = +2 V measured in samples fabricated by the reverted vdW stacking method. Inset: same data in a semilog plot

To better understand the obtained result in Fig. 2a, we now plot the line cuts of IV along fixed V g. It is found that, at the largest negative gate voltage of about −3 V (all V g and V ds in the measurements were pushed to the limit which keeps gate leakage negligible), the output curves behave as typical pn diode with rectification characteristics (Fig. 3a), and on/off ratio over 105 (Fig. 2b). When gate voltage is brought into the range of −1 to +2 V, it is seen that the diode behaviour is inverted into np type by solely tuning the gate (Fig. 3b). The ON side is now in the negative bias voltage direction, as marked by boxes in Fig. 2a. Upon further doping to the electron side, i.e., at larger positive gate voltages, the output curves gradually shift from the diode behaviour into an asymmetric IV with the low bias range following the conventional semiconducting trend, but rather linear at large positive bias. Strikingly, the linear parts can be extrapolated into a single crossing point on the zero-current axis, with a crossing voltage V C of about −1.25 V (Fig. 3c). This extrapolated crossing point of IV curves is not readily understood and provides food for further experimental and theoretical studies.

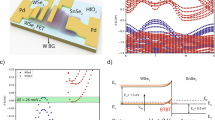

Room temperature gate-controlled reversible rectifying diode in a TC-FET. a–c IV curves showing perfect rectifying behaviour with reversible polarity characteristics of MoS2 TC-FETs. a–c are linecuts of Fig. 2a, with output curves along fixed gate voltages of −3, 0, and 4–7 V, respectively. While d–f are the corresponding schematic band alignment pictures. g–l Simulations of rectifying characteristics of tunnel-contacted MoS2 FET. g–i Simulated IV characteristics of the MoS2 vertical tunnel FET at hole doping, neutral, and electron doping, respectively. At these corresponding doping level, their simulated PLDOS at V ds = +1 V are shown in j–l

Discussion

We propose a simple band alignment model to explain the observed behaviour of gate-induced switching between pn to np diodes. In conventional metal-contacted MoS2 devices, due to the work function mismatch, SB forms at the interface of metal and 2D materials, as a result of Fermi level pinning and band bending near the interface (Fig. 1a, c). However, tunnel h-BN in our case overcomes this problem, leading to a relatively free moving conduction and valence bands (Fig. 1b, d). At each stage of electrostatic doping in Fig. 3a–c, Fermi level sits at a fixed energy between the minimum of conduction band and the maximum of valence band, respectively. This free band alignment model offers a good description of the pn to np diode inversion in a V ds range of ±2 V, as illustrated in Fig. 3d–f. Moreover, when Fermi level enters conduction band from the band gap, a slope of unity in V ds vs V g can be extracted in Fig. 2a in the negative V ds regime, indicating a strong energetic coupling of chemical potential from the electrostatic gate to the electronic band in the few-layered MoS2 channel. Once the Fermi level enters the conduction band, the gate becomes capacitively coupled owing to the large density of states, giving rise to a significantly reduced slope of V ds vs V g.

In the following, we compare the measured data with first-principles simulations. For simplicity, we consider the simplest scenario of monolayer MoS2 tunnel device with a channel length of about 6 nm and two-layered tunnel h-BN (computational details can be found in Supplementary Figs. 8–11 and Supplementary Note 3). Compared to Fig. 3a–c, first-principles calculations based on the simplified model give qualitative agreement with experimental observations. As shown in Fig. 3g–i, the two-layered h-BN TC MoS2 FET in our calculated model shows pn, np, and asymmetrical full pass rectifying characteristics at hole doping, neutral, and electron doping, respectively. Their corresponding projected local density states (PLDOS) at V ds = +1 V are shown in Fig. 3j–l. One can see in the LDOS that the effective transmission forbidden region Δ in TC device is about 2.5 eV, which is largely enhanced due to the existence of h-BN tunnel barrier (Δ ~ 1.8 eV in normal contacted device, shown in Supplementary Fig. 10). The simulated results echo our hypothesis of free band alignment model in Fig. 3d–f. Fermi level pinning in metal-contacted devices are suppressed by ultra thin tunnel contact, resulting in the observed finite-bias ambipolar field effect, as well as gate tunable rectifying characteristics with multiple operation states.

It is of fundamental interest to study the temperature dependence of tunnelling current in the MoS2 TC-FETs. Figure 4a, b plots the transfer curves of the same device in Fig. 2a, with V ds = ±2 V at different temperatures from 300 K down to 5 K. It can be seen in Fig. 4a that bipolar transfer curves at V ds = +2 V show very weak temperature dependence. A plot of the transfer curve at 300 K is plotted in the inset of Fig. 4a, the sub-threshold swing is extracted on the hole side to be about 230 mV decade−1, higher than the 60 mV decade−1 theoretical limit37. On the contrary, at V ds = −2 V, the transfer curves show rather strong temperature dependence (Fig. 4b), with the I ds decreasing upon lowering the temperature. Single traces of I ds–T monitored at +2V ds with −5V g, and −2V ds with +7V g are plotted in Fig. 4c, colors are picked according to the dashed lines in Fig. 4a, b, respectively. The negatively source–drain biased I ds–T curve at +7V g (red curve) can be fitted by a phonon-assisted tunnelling model38:

where \(\gamma = \alpha \sqrt {2{m^*}{\rm{/}}{\varepsilon _{\rm{T}}}} \frac{{\hbar {\omega ^2}}}{{eE}}\left( {2{{\left[ {{\rm{exp}}\left( {\hbar \omega {\rm{/}}{k_{{\rm{BT}}}}} \right) - 1} \right]}^{ - 1}} + 1} \right)\), and Ω = (1 + γ 2)1/2, with α being a fitting parameter, E the electrical field strength, ε T the tunnel energetic depth, m * the electron effective mass, ħω the energy of the phonon taking part in the tunneling process, e and k B the element charge and Boltzmann’s constant, respectively. Using an effective mass of about 0.018m e 39, the best fit in the black solid line Fig. 4c gives ε T = 0.6 eV and \(\hbar \omega \sim 11\) meV.

Temperature dependence of transfer curves in a MoS2 TC-FET. a, b Transfer curves at different temperatures for the device shown in Fig. 2, at drain source voltages V ds = +2 and −2 V, respectively. Inset in a is a log scale of the field effect curve. c Line traces of temperature dependence of I ds at fixed gate voltage along the blue and red dashed lines in Fig. 5a, b, respectively. Gray solid line indicates the gate leakage current during the same measurement. Solid fitting line in Fig. 5c is fitted using Eq. (1) in the main text

Finally, as a proof of principle for realizing gate-tunable rectifier in the MoS2 TC-FET, we used a simple diode circuit with load resistor of 1 MΩ and output to a 100 MΩ impedance voltage amplifier (1× amplification was used in the measurement), as illustrated in the schematics in Fig. 5a. As seen in Fig. 5b, when a sinusoidal wave is input in the MoS2 TC-FET, output wave starts from a positively rectified half wave in the largest hole doping side, and can be first gate tuned into an intermediate OFF state, followed by a negatively rectified half wave in the electron doping side. Further electron doping recovers both positive and negative half output wave, with different amplitude. This gate-tunable rectification inversion with a π phase shift phenomenon, together with multiple states of output level (e.g., pn diode, OFF, np diode, and full pass), has not been reported before, and can be of great use in future gate-tunable logic circuits with atomically thin conduction channels. As discussed in Supplementary Note 4, it is noteworthy that in a device directly fabricated on SiO2, we obtained a cut-off frequency in such MoS2 TC-FET of about 20 kHz when the Si gate is heavily doped (Supplementary Fig. 12). Moreover, stability and reliability in 2D materials based devices have been a timely topic40, 41, which is crucial from the application point of view. For example, the thin h-BN layer intercalated between the metal contacts and MoS2 channel can cause extra charge trapping that may lead to inferior reliability as compared to conventional metal-contacted MoS2 FETs (Supplementary Note 5). We rule out this possibility based on the hysteresis measurements, as shown in Supplementary Fig. 13.

Reversal rectification of an analog harmonic signal in MoS2 TC-FET. a Schematics of the gate-control rectifier device placed in a measurement and biasing circuit. The MoS2 TC-FET is symbolized as a polarity-switchable diode. b Input (harmonic signal ~13 Hz) and output waves of the gate-controlled diode. A π phase shift, together with multiple states of output level (e.g., pn diode, OFF, np diode, and full pass), in the rectified output wave can be seen via gating. Each measured curve was averaged over 150 recorded traces

To conclude, we have developed a reverted vdW stacking method for high yield fabrication of resist-free pristine vdW heterostructure with ultra-thin top layer. This method itself opens new routes to a number of applications such as scanning tunnelling microscope on pristine 2D materials supported by another, as well as the high quality spacing layer for tunnelling electrodes. Using this technique, we have demonstrated a vertical TC MoS2 transistor, in which suppression of band bending and Fermi level pinning is realized. The so called TC Field Effect Transistor hence gives rise to gate tunable rectification with fully reversible pn to np diode, leading to multiple operation states of output level (e.g., positive-pass, OFF, negative-pass, and full-pass). The observed ambipolar field effect at finite positive V ds shows on/off ratio up to 105 in such MoS2 FETs, with an output current reaching the order of 100 nA on both electron and hole sides. We proposed a free moving band alignment model to explain the behaviour of the MoS2 TC-FET, which is further qualitatively supported by a simplified first-principles simulation model. This work paves the way for future application in gate-tunable logic devices with atomically thin semiconducting channels.

Methods

Reverted vdW heterostructures fabrication process

In order to have resist-free pristine vdW heterostructures, one of the limitations is its stacking sequence: a thick enough h-BN has to be picked up first by polymer (Propylene-Carbonate, PPC, for example) to serve as a top layer. When the top layer is too thin (<5 layers), ruptures and wrinkles increase significantly, thus reduce the quality of the final device. We solved this problem by developing a reverted vdW stacking method: few-layered MoS2 is sandwiched by a thick (~10 nm) BN (crystals from HQ Graphene) and thin (two to four layer) BN, respectively, with the resulted top later picked up lastly (Supplementary Methods). vdW heterostructures were fabricated using an integrated system E-Stack-One from Eoulu Co., Ltd., Suzhou, China. When the whole stack is collected, the PPC stamp will be flipped upside down, peeled off with care from the PDMS substrate, and slowly landed onto a hot plate of about 100 °C (Supplementary Methods). At this stage, the stack will be floating on the PPC film, which can be completely evaporated in a vacuum annealer at 350 °C for around 20 min. Followed by standard lithography and metallization. MoS2 flake is half covered by two to four layer h-BN, and Au electrode with thickness of 20 nm is deposited onto the stack, forming conventional direct contacts and tunnel contacts, respectively. Electronic transport was measured on a Cascade probe station at room temperature, and in a Quantum Design PPMS system with a home-made sample probe interfaced with external measurement setup at low temperatures, respectively.

First-principles simulations

The device simulations in this work are carried out by using the first-principles software package Atomistix ToolKit, which is based on density-functional theory in combination with the non-equilibrium Greens function42. The exchange-correlation potential is described by the local density approximation and the wave function is expanded by the Hartwigsen–Goedecker–Hutter (HGH) basis in this work. More computational details are discussed in Supplementary Note 3. The real space grid techniques are used with the energy cutoff of 150 Ry in numerical integrations. The geometries are optimized until all residual force on each atom is smaller than 0.05 eV Å−1. The current can be calculated by the Landauer formula43:

Here, V ds is the bias voltage between the drain and the source, T(E, V ds) is the transmission coefficient, f S (E, V ds) and f D (E, V ds) are the Fermi-Dirac distribution functions of the source and drain, respectively. The transmission coefficient T(E, V ds) as a function of the energy level E at a certain V ds can be calculated by the formula:

where G R(E) and G A(E) are the advanced and retarded Greens functions of the scattering region, respectively.

Data availability

The data that support the findings of this study are available from the corresponding authors upon reasonable request.

References

Dean, C. R. et al. Boron nitride substrates for high-quality graphene electronics. Nat. Nanotechnol. 5, 722–726 (2010).

Wang, L. et al. One-dimensional electrical contact to a two-dimensional material. Science 342, 614–617 (2013).

Geim, A. K. & Grigorieva, I. V. Van der Waals heterostructures. Nature 499, 419–425 (2013).

Novoselov, K. S., Mishchenko, A., Carvalho, A. & Neto, A. H. C. 2D materials and van der Waals heterostructures. Science 353, 461 (2016).

Liu, Y. et al. Van der Waals heterostructures and devices. Nat. Rev. Mater. 1, 1–17 (2016).

Guimaráes, M.-H.-D., Zomer, P.-J., Ingla-Aynés, J. J.-C., Brant, N. T. & van Wees, B.-J. Controlling spin relaxation in hexagonal BN-encapsulated graphene with a transverse electric field. Phys. Rev. Lett. 113, 086602 (2014).

Ye, J. T. et al. Superconducting dome in a gate-tuned band insulator. Science 338, 1193–1196 (2012).

Mak, K. F., Lee, C., Hone, J., Shan, J. & Heinz, T. F. Atomically thin MoS2: a new direct-gap semiconductor. Phys. Rev. Lett. 105, 136805 (2010).

Cui, X. et al. Multi-terminal transport measurements of MoS2 using a van der Waals heterostructure device platform. Nat. Nanotechnol. 10, 534–540 (2015).

Mak, K. F., McGill, K. L., Park, J. & McEuen, P. L. The valley Hall effect in MoS2 transistors. Science 344, 1489–1492 (2014).

Radisavlijevic, B., Radenovic, A., Brivio, J., Giacometti, V. & Kis, A. Single-layer MoS2 transistors. Nat. Nanotechnol. 6, 147–150 (2011).

Sakar, D. et al. A subthermionic tunnel field-effect transistor with an atomically thin channel. Nature 526, 91–95 (2015).

Desai, S. B. et al. MoS2 transistors with 1-nanometer gate lengths. Science 354, 99–102 (2016).

Wu, W. et al. Piezoelectricity of single-atomic-layer MoS2 for energy conversion and piezotronics. Nature 514, 470–474 (2014).

Kim, K. et al. High-mobility and low-power thin-film transistors based on multilayer MoS2 crystals. Nat. Commun. 3, 1011 (2012).

Yu, W. J. et al. Highly efficient gate-tunable photocurrent generation in vertical heterostructures of layered materials. Nat. Nanotechnol. 8, 952–958 (2013).

Wang, X. et al. Ultrasensitive and broadband MoS2 photodetector driven by ferroelectrics. Adv. Mater. 27, 6575–6581 (2015).

Chuang, S. et al. MoS2 P-type transistors and diodes enabled by high workfunction MoO x contacts. Nano Lett. 14, 1337–1342 (2014).

Bao, W. Z., Cai, X., Kim, D., Sridhara, K. & Fuhrer, M. S. High mobility ambipolar MoS2 field-effect transistors: substrate and dielectric effects. Appl. Phys. Lett. 102, 042104 (2013).

Zhang, Y., Ye, J., Matsuhashi, Y. & Iwasa, Y. Ambipolar MoS2 thin flake transistors. Nano Lett. 12, 1136–1140 (2012).

Jariwalaa, D. et al. Gate-tunable carbon nanotube-MoS2 heterojunction p-n diode. Proc. Natl Acad. Sci. USA 110, 18076–18080 (2013).

Vélez, S. et al. Gate-tunable diode and photovoltaic effect in an organic-2D layered material p-n junction. Nanoscale 7, 15442–15449 (2015).

Roy, T. et al. Dual-gated MoS2/WSe2 van der Waals tunnel diodes and transistors. ACS Nano 9, 2071–2079 (2015).

Wang, C. et al. Gate-tunable diode-like current rectification and ambipolar transport in multilayer van der Waals ReSe2/WS2 p-n heterojunctions. Phys. Chem. Chem. Phys. 18, 27750–27753 (2016).

Britnell, L. et al. BN tunnel electron tunneling through ultrathin boron nitride crystalline barriers. Nano Lett. 12, 1707–1710 (2012).

Britnell, L. et al. Field-effect tunneling transistor based on vertical graphene heterostructures. Science 335, 947–950 (2012).

Mishchenko, A. et al. Twist controlled resonant tunnelling in graphene boron nitride graphene heterostructures. Nat. Nanotechnol. 9, 808–813 (2014).

Chandni, U., Watanabe, K., Taniguchi, T. & Eisenstein, J. P. Signatures of phonon and defect-assisted tunneling in planar metal-hexagonal boron nitride-graphene junctions. Nano Lett. 16, 7982–7987 (2016).

Lee, G. H. et al. Electron tunneling through atomically flat and ultrathin hexagonal boron nitride. Appl. Phys. Lett. 99, 243114 (2011).

Amet, F. et al. Tunneling spectroscopy of graphene-boron-nitride heterostructures. Phys. Rev. B 85, 073405 (2012).

Li, J., Taniguchi, T., Watanabe, K., Hone, J. & Dean, C. R. Excitonic superfluid phase in double bilayer graphene. Nat. Phys. 13, 751755 (2017).

Liu, X., Watanabe, K., Taniguchi, T., Halperin, B. I. & Kim, P. Quantum hall drag of exciton superfluid in graphene. Nat. Phys. 13, 746750 (2017).

Zhou, P., Hardy, W. J., Watanabe, K., Taniguchi, T. & Natelson, D. Shot noise detection in hBN-based tunnel junctions. Appl. Phys. Lett. 110, 133106 (2017).

Kim, C. et al. Fermi level pinning at electrical metal contacts of monolayer molybdenum dichalcogenides. ACS Nano 11, 1588–1596 (2017).

Li, L. K. et al. Quantum Hall effect in black phosphorus two-dimensional electron system. Nat. Nanotechnol. 11, 593–597 (2016).

Wang, J. et al. High mobility MoS2 transistor with low Schottky barrier contact by using atomic thick h-BN as a tunneling layer. Adv. Mater. 28, 8302–8308 (2016).

Sze, S. M. Physics of Semiconductor Devices (Wiley, 1981).

Pipinys, P. & Kiveris, A. Variable range hopping andor phonon-assisted tunneling mechanism of electronic transport in polymers and carbon nanotubes. Cent. Eur. J. Phys. 10, 271–281 (2012).

Nguyen, L. N. et al. Resonant tunneling through discrete quantum states in stacked atomic-layered MoS2. Nano Lett. 14, 2381–2386 (2014).

Illarionov, Y. Y. et al. Long-term stability and reliability of black phosphorus field-effect transistors. ACS Nano 10, 95439549 (2016).

Illarionov, Y. Y. et al. The role of charge trapping in MoS2/SiO2 and MoS2/hBN field-effect transistors. 2D Mater. 3, 035004 (2016).

Brandbyge, M., Mozos, J. L., Ordejón, P., Taylor, J. & Stokbro, K. Density-functional method for nonequilibrium electron transport. Phys. Rev. B 65, 165401 (2002).

Büttiker, M. Y., Imry, R. L. & Pinhas, S. Generalized many-channel conductance formula with application to small rings. Phys. Rev. B 31, 6207–6215 (1985).

Acknowledgements

This work is supported by the National Key R&D Program of China (2017YFA0206302), the National Basic Research Program of China (973 Grant Nos. 2013CB921900, 2014CB920900), and the National Natural Science Foundation of China (NSFC, Nos. 11504385 and 51627801). X.-W.J. acknowledges supports by the NSFC Grant 11574304, Chinese Academy of Sciences-Peking University Pioneer Cooperation Team (CAS-PKU Pioneer Cooperation Team), and the Youth Innovation Promotion Association CAS (grand 2016109). D.-M.S. thanks the NSFC grant 51272256, 61422406, 61574143, and MSTC grant 2016YFB04001100. X.L. and J.-H.C. acknowledges support from the NSFC Grant 11374021 and 11774010. Z.-D.Z. acknowledges supports from the NSFC with grant 51331006 and the CAS under the project KJZD-EW-M05-3. V.B. acknowledges support from the EU FP7 Graphene Flagship (project no. 604391), J2D project grant (ANR-15-CE24-0017) from Agence Nationale de la Recherche (ANR), and the Hsun Lee Award program of the Institute of Metal Research, CAS. The authors are grateful for helpful discussions with Prof. Benjamin Sacépé, Prof. Vasili Perebeinos, Prof. Antanas Kiveris, and Prof. Ji Feng.

Author information

Authors and Affiliations

Contributions

Z.H. and Z.-D.Z. conceived the experiment and supervised the overall project. X.-X.L. fabricated the samples. X.-X.L., V.B., and Z.H. carried out experimental measurements; D.-M.S. and M.-L.C. provided clean room support for the experiment; X.L. and J.-H.C. contributed to electron beam lithography and device fabrication. X.-W.J. and Z.-Q.F. conducted the theoretical simulations. J.-J.G. and P.-Z.L. carried out the TEM characterizations. Data analysis and interpretation were done by Z.H., X.-X.L., V.B., and C.-K.J.; the manuscript was written by Z.H. with discussion and inputs from all authors.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing financial interests.

Additional information

Publisher's note: Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Electronic supplementary material

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Li, XX., Fan, ZQ., Liu, PZ. et al. Gate-controlled reversible rectifying behaviour in tunnel contacted atomically-thin MoS2 transistor. Nat Commun 8, 970 (2017). https://doi.org/10.1038/s41467-017-01128-9

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41467-017-01128-9

This article is cited by

-

Reliable wafer-scale integration of two-dimensional materials and metal electrodes with van der Waals contacts

Nature Communications (2024)

-

Low Ohmic contact resistance and high on/off ratio in transition metal dichalcogenides field-effect transistors via residue-free transfer

Nature Nanotechnology (2024)

-

Contact-engineered reconfigurable two-dimensional Schottky junction field-effect transistor with low leakage currents

Nature Communications (2023)

-

Two-dimensional complementary gate-programmable PN junctions for reconfigurable rectifier circuit

Nano Research (2023)

-

Imaging tunable quantum Hall broken-symmetry orders in graphene

Nature (2022)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.