Abstract

Closely following the rapid development of artificial intelligence, studies of the human brain and neurobiology are focusing on the biological mechanisms of neurons and synapses. Herein, a memory system employing a nanoporous double-layer structure for simulation of synaptic functions is described. The sponge-like double-layer porous (SLDLP) oxide stack of Pt/porous LiCoO2/porous SiO2/Si is designed as presynaptic and postsynaptic membranes. This bionic structure exhibits high ON–OFF ratios up to 108 during the stability test, and data can be maintained for 105 s despite a small read voltage of 0.5 V. Typical synaptic functions, such as nonlinear transmission characteristics, spike-timing-dependent plasticity, and learning-experience behaviors, are achieved simultaneously with this device. Based on the hydrodynamic transport mechanism of water molecules in porous sponges and the principle of water storage, the synaptic behavior of the device is discussed. The SLDLP oxide memristor is very promising due to its excellent synaptic performance and potential in neuromorphic computing.

Similar content being viewed by others

Introduction

The development of deep learning is closely associated with the advancement of artificial intelligence, which is inseparable from brain science and neurobiology. Many recent research activities are fog on the biological mechanisms of neurons and synapses1,2, and a good understanding of the biological brain is crucial to the design of intelligent machines3,4,5,6. The synaptic signal is transmitted from one neuron to the next, while the signal passing through the neural pathway is remembered through the stimulation of a pulsed signal7,8. Memristors with a small size, low energy consumption, and nonvolatile performance are vital to many applications related to information storage, analog circuits, artificial intelligence, and analog neural networks9,10. Because of the similarity between the memristor and synapse, studies on the mechanisms and materials simulating the behavior and functions of nerve cells are crucial to the development of biologically inspired devices and prototypes10,11.

Materials suitable for memristors mainly include oxides12, sulfides13, perovskites14,15, two-dimensional materials16,17, and related materials18,19, and in particular, oxide-based memristors have been widely studied due to their high switching speed, large density, and compatibility with complementary metal–oxide–semiconductor processing20,21. The conduction mechanism of most of these materials is based on the formation and breakage of conductive metallic filaments via the accumulation of oxygen vacancies or metal atoms, such as Cu or Ag22,23,24,25. However, the stochastic and unpredictable formation process results in device variability, fluctuation of resistance states, and excessive “write” noise, consequently undermining the stability of the materials23,25. Therefore, it is necessary to control the switching filament formation and dynamics of memristors. To overcome these hurdles, approaches, including stoichiometry control26, thermal annealing27, and insertion of thin metal layers28, have been suggested, and the control of filaments and their formation at desirable locations must be improved and better understood. Introducing a porous structure into the resistive layer is one of the viable methods to provide channels for ion transport. For example, Wang et al. prepared multiple nanoporous (NP) SiOx layers to control filament formation29,30, and Tour et al. proposed a three-dimensional NP Ta2O5−x structure with graphene boasting high-density storage and low power consumption31,32. Obviously, a porous structure can regulate the conducting channel and enhance the device performance33.

Combining bionic ideas with device design is an effective way to study defects in electronic devices and the underlying mechanisms. Zhang et al. proposed a three-dimensional spiral microstructure as the basic unit and constructed bionic soft three-dimensional mesh materials with defect-insensitive characteristics, by varying the spatial topology to reproduce the anisotropic nonlinear mechanical response of biological tissues34. Fan et al. prepared perovskite nanowires for an electrochemical eye with a hemispherical retina that can imitate the photoreceptors in the human retina11. Furthermore, the transport characteristics of water in a natural cave structure have been combined with hydrodynamics and ion transport to design a karst-like hierarchical porous structure with good characteristics35. However, the nonuniform pore diameters in the silicon oxide layer cause large variations in the essential switching elements, and random and nonuniform ion migration in LiCoO2 hampers the optimal switching functionalities. Lithium ion migration in LiCoO2-based memristors is similar to the information exchange process between synapses and neurons in the brain36,37,38,39,40. LiCoO2 is used in Li-ion batteries to improve the capacity and mitigate the volume expansion during deintercalation of lithium ions under repetitive charging and discharging41,42,43. It is also important to investigate the relationship between the device performance and NP structure, as well as potential device applications. In fact, it is advisable to adopt the bionic route in designing and utilizing the functions of natural porous structures in memristor devices to better simulate the functions of synapses and elucidate the associated mechanisms.

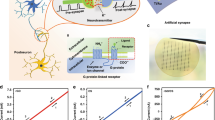

In this work, a bionic double-layer NP structure comprising a Pt/porous LiCoO2/porous SiO2/Si stack is designed. The device delivers high memristive performance due to the unique electrochemical properties of porous SiO2 (PSiO2) and porous LiCoO2 (PLiCoO2), such as a high ON–OFF ratio44,45,46,47,48. The typical synaptic functions of the sponge-like double-layer porous (SLDLP) memristor are simulated, and a model is proposed to describe the mechanism of the synaptic behavior by considering the hydrodynamic transport of water molecules in porous spongy structures, as well as the principle of water storage. The memristor with the SLDLP structure has great potential in areas, such as artificial intelligence and neuromorphic computing (Scheme 1).

Results and discussion

The microstructure of the materials determines the device characteristics49,50. Oxide-based memristors with a porous structure have recently been demonstrated to have promising functionalities that improve the device performance, such as scalability51,52. Based on the bionic structure and principle, it is meaningful to design and construct a device with a porous structure. Natural sponges have many interesting and unique properties, such as porosity, elasticity, pressure resistance, water absorption, and water penetration. Hence, a buffer layer of porous silicon oxide is designed and fabricated according to the structure of a sponge. PLiCoO2 is incorporated into the PSiO2 structure by radio frequency (RF) magnetron sputtering to provide conduction channels for ion transport53,54. Moreover, a porous interface is fabricated between the PSiO2 layer and PLiCoO2 layer to provide conduction channels to enhance the electrochemical reactions.

The preparation process of the double-layer porous device is illustrated in Fig. 1. Figure 1a shows a diagram of the primary functionalized materials, and the lower right picture depicts the sponge and enlarged microstructure. Figure 1b, c illustrates the preparation process of PSiO2, and thorough mixing of the two solutions is shown in Fig. 1d. The SiO2 solution is spin-coated on a highly doped p-type Si (100) wafer, and annealed at a reduced pressure of 10−1 Pa and a temperature of 400 °C. The 3D spongy SiO2 structure (~70 nm) is prepared as shown in Fig. 1e, and Fig. 1f presents the structure of the memristor. The PLiCoO2 film (~100 nm) and Pt electrode film (~80 nm) are prepared by magnetron sputtering.

The dependence of the memristive behavior on the double-layer porous structure is investigated. A TEM image of the Pt/PLiCoO2/PSiO2/Si memristor is displayed in Fig. 2a, and Fig. 2b presents a cross-sectional image of PLiCoO2, revealing that pores with sizes of 2–20 nm are distributed throughout the LiCoO2 layer. Figure 2c shows a cross-sectional TEM image of the porous SiO2, and pores 2–5 nm in size are evenly distributed throughout the SiO2 layer. The porous structure in each oxide layer is similar to that in Fig. 2d, which shows an electron micrograph of the natural sponge structure55. To evaluate whether the device has basic synaptic functions, the storage and memory functions are studied in the direct current (DC) mode using a Keithley S4200. To characterize the electrochemical performance of the PSiO2/PLiCoO2 memristor, the current–voltage (I–V) characteristics, stability, and retention are determined and shown in Fig. 2e–g, respectively. As shown in Fig. 2e, the device does not show a forming process. The switching parameters for various porous-based memristors, such as single porous, array porous, and NP memristors, are compared. The Vset, Vreset, endurance cycles, ON–OFF ratio and retention are summarized in Table S1 as Supporting Information. Interestingly, the minimum currents in the switching I–V plot exist at certain positive and negative voltages, but not at zero voltage, indicating that the electric field through the porous layer becomes a minimum when a voltage is applied, so charge transfer can be suppressed31,32. No electrical shorts are found in the device, as there is no direct contact between Pt and Si. In the experiment, different positive voltages from 5 to 14 V are applied, and the voltage step and current compliance are 0.01 and 0.01 A, respectively. As Vapplied is increased, Vmin increases, as shown in Fig. S1a. The linear relationship confirms the idea that the switching mechanism is related to lithium ions in the pores and depends on the external electric field, because a larger Vset drives more lithium ions to the pores31,35. A larger applied voltage traps a mass of charges and produces a higher internal electric field during programming. Therefore, a higher external electric field is needed to control the charge transfer and neutralize it through the porous silicon oxide31,35,50. The nanopores with nonuniform diameters affect the device-to-device uniformity, causing a large variation in the essential switching elements, and programming paths and restricting the optimal switching functionalities.

To further analyze the uniformity of switching in the PSiO2/PLiCoO2 memristor, we statistically investigate the relationship of Vapplied–Vmin for >40 devices by sweeping the voltage from −8 to 0 V. The Vmin range is from −0.21 to −3.51 V, and the fitting parameter is 0.98 ≈ 1, as shown in the plot in Fig. S1b. The maximum resistance is ~1012 Ω, as shown in Fig. S1c. The durability is determined to study the stability of the PSiO2/PLiCoO2 memristor. The voltage is swept from 10 to −10 V in the DC mode, and the voltage step and current compliance are ±0.01 and 0.01 A, respectively. The high resistive state (HRS) and low resistive state (LRS) during 128 switching cycles show a high ON–OFF ratio of up to 108, as shown in Fig. 2f. The retention of the HRS and LRS is measured at a low voltage of 0.5 V, and the retention time is up to 105 s, as shown in Fig. 2g, showing alleviation of short data retention. The memristor properties of the nonporous structure are determined and shown in Fig. S2. The device exhibits an obvious forming behavior at a voltage of 6.55 V, mainly due to the disordered movement of lithium ions in the silicon oxide layer, as shown in Fig. S2a. The ON–OFF ratio is ~105, and the LRS retention time increases gradually with time, reaching a stable value of 107 Ω, as shown in Fig. S2b,c. Field-emission scanning electron microscopy (FE-SEM) images of the nonporous SiO2 and porous SiO2 are depicted in Fig. S3a, b. The porous structure has the following advantages. The porous structure in the LiCoO2 layer and SiO2 layer can relieve the volume expansion of LiCoO2 and SiO2 during cycling, and the pores in the LiCoO2 layer provide channels for ion transport and increase the concentration of lithium ions under the action of the same electric field. The pores in SiO2 provide channels for fast ion transport, and adequate contact between lithium ions and silicon oxide; by removing the external electric field, the porous channels increase the diffusion path of lithium ions, and the retention of the LRS is longer.

There are small pores in a piece of sponge, and upon exposure to water, water infiltrates along the tubular walls. When the upward pulling force is equal to the gravity of the liquid, the liquid stops rising according to the capillary phenomenon, and water fills the sponge gaps. Because the sponge has many small voids, it is originally filled with air. When water is applied, the sponge experiences a pressure that expels air, and when the pressure is released, the sponge returns to its original shape by taking in air. The water is subjected to atmospheric pressure, and at times, the pressure in the sponge is relatively small such that water enters the sponge. In our device, the porous layer also has many small pores. Under the action of an electric field, the electric field is concentrated around the pores, and ions migrate along the pores. After the electric field is removed, the small tortuous pores resemble the porous structure of a sponge, the ions can be stably stored in the porous layer, and the device exhibits stable performance. Therefore, the PSiO2/PLiCoO2 device is quite stable, and repeated charging–discharging ensures that sufficient lithium ions react with PSiO2, so that the device reaches a lower resistance state compared to the nonporous structure. After the external voltage is turned off, the porous structure has a negative charge, thus providing more adsorption sites for lithium ions and making it difficult for them to diffuse out of the silicon oxide layer, consequently improving the retention time of the device50.

The flexibility of the memory functions of the memristor is similar to that of the synapse of organisms. While transmitting a signal, the segment is processed, and the signal is memorized. Because many functions of the memristor are very close to those of biological synapses, the memristor works like synapses and can form the basis for a simulated neural network. Accordingly, the use of memristors to conduct biological synapse simulation is desirable because the density of synapses in artificial neural networks is close to that in biological neural networks, thereby achieving low power consumption and high integration in neural network simulation56,57,58. Biological research shows that the strength of the synaptic weights is closely related to neural memory, and in our device, the top and bottom electrodes can be regarded as presynaptic and postsynaptic neurons, respectively, with the PLiCoO2 layer and PSiO2 being the presynaptic and postsynaptic membranes, respectively.

The increase/decrease in synaptic weights is controlled by the concentration of ions, and release/suppression of these ions is associated with release/suppression under certain conditions. Here, the conductivity is considered a synaptic weight, and behavior similar to the nonlinear transmission characteristics of biological synapses is simulated. The changes in conductance are indirectly related to the current. Figure 3 shows the current modification in response to a stimulus. Under the stimulation of positive voltage pulses (8 V, 5 ms), the current of the device increases as the pulse sequence is applied. Conversely, under the stimulation of negative voltage pulses (−8 V, 5 ms), the current of the device decreases as the pulse sequence is applied. Regulation of the current is considered to be associated with migration of lithium ions in the lithium cobalt oxide layer and silicon oxide layer, as well as the electrochemical reaction process with silicon oxide. With a gradual increase in the stimulation pulse frequency, lithium ions are released from the PLiCoO2 layer, and holes are formed in the t2g orbital of LixCoO2 and PLiCoO2, causing a change from insulating to semiconducting or even conducting58,59,60,61. Lithium ions migrate along the porous channels of the LiCoO2 layer and SiO2 layer, and react electrochemically with SiO2 to form LiySiO2. The conductance increases gradually under stimulation by positive voltage pulses, but when a negative voltage pulse is applied, lithium ions are released from the PSiO2 layer to recombine with holes in the t2g valence band of LixCoO2. The conductance decreases gradually under the stimulation of negative voltage pulses37.

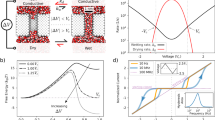

Plasticity is an important characteristic of a synapse. Synaptic plasticity is time dependent when applying different pulse signals. Here, different tests are performed to simulate the changes in the synaptic weights, as shown in Fig. 4. Figure 4a, b shows that longer pulse widths produce larger changes in the synaptic weights for the same pulse interval of 5 ms and pulse voltage of 8 V. Figure 4c, d shows that shorter pulse intervals result in larger changes in the device synaptic weights for the same pulse width of 5 ms. Figure 4e, f shows that a larger pulse amplitude causes larger changes in the synaptic weights for the same pulse interval of 10 ms and pulse width of 5 ms. The adjustment of synaptic weights is associated with the migration of lithium ions between the PLiCoO2 layer and PSiO2 layer, as well as the reaction rate with PSiO2. In the case of larger voltage or longer stimulation, the larger flow in the ion conductive channels from one electrode to another causes larger changes in the synaptic weights.

According to memory retention, synaptic plasticity can be classified as short-term plasticity (STP) and long-term plasticity (LTP), consistent with short-term memory and long-term memory in biology. By applying a continuous voltage pulse signal to the synaptic device to complete the learning process and then a small read voltage pulse to the device to complete the forgetting process, the device can be changed from STP to LTP62,63. The memory retention characteristics of our device are shown in Fig. 5. Figure 5a shows that as the synaptic device is stimulated sequentially with 100 positive voltage pulses, the synaptic weights increase gradually. There is an interesting phenomenon that after turning off the external electric field, the synaptic weights decay spontaneously with time. In the beginning, the decay is rapid and then slows gradually. This phenomenon is similar to the learning–forgetting process of the brain63. The synaptic weights do not return to the initial state but rather remain in a stable intermediate state. This means that the change in the synaptic weights consists of two parts: STP and LTP. A model is thus proposed to explain the phenomenon. Figure 5b, c corresponds to rectangular areas (1) and (2) in Fig. 5a, respectively. By applying positive pulses continuously, lithium ions are released from the PLiCoO2 layer and transported along the pore channels. At the PSiO2/PLiCoO2 interface, the small holes are surrounded by large holes, as shown in Fig. 6a, b, corresponding to the rectangular area in Fig. 6a. Under the electric field, the porous structure concentrates the electric field, and the field strength is the strongest at the tangent point of two holes. Hence, ions migrate along the field strength direction, and an ion current is formed at the interface of the double-layer porous structure. A model is proposed to explain ion migration at this interface, as shown in Fig. S4a, with ions entering the PSiO2 layer and reacting with SiO2. When a positive voltage is applied to the device, it can be clearly seen that there exists a higher electric field density around the area of the pores at the PLiCoO2/PSiO2 interface. At the tangent point between pores at the interface of the two layers of porous materials, the electric field exhibits a high field strength due to superposition, confirming the electrical field concentration capability around the nanopores. Then, ions migrate around the pores50. After turning off the electric field, the partly free lithium ions in the porous silicon oxide layer diffuse to the lithium cobalt oxide layer, and the device exhibits STP behavior, as shown in Fig. S4b. The model in Fig. 5d corresponding to rectangular area (3) in Fig. 5a explains the phenomenon. The main reason for the water storage capacity of the sponge structure is that the many small pores act as capillaries. The combined effects of surface tension, cohesion, and adhesion of the liquid allow water to be stored in the sponge. In the PSiO2 layer, owing to the small pores, the diffusion path of lithium ions adsorbed around the porous channel increases. At the PSiO2/PLiCoO2 interface, small pores surround large pores, and under capillary action, ions are adsorbed at the interfaces. Hence, there are more adsorption sites for ions and hindrance of diffusion of lithium ions, resulting in the improved lithium storage capacity and stable LTP behavior.

Preservation of the memory information in the brain is related to time and learning frequency. After repeated and timely learning of input information, short-term memory can become long-term memory and remain in the human brain for a long time63. Herein, a repeat learning process is tested. Figure 7 shows the learning experience for a four repetitive pulse stimulation. The time interval between each pulse is 20 s, and the synaptic weight corresponds to the amount of memory information. First, 100 consecutive positive voltage pulses are applied to the device, and the voltage pulses are turned off for 20 s. Afterward, 80 consecutive positive voltage pulses are applied, and the synaptic weight changes by 18.09%. By applying 60 and 40 consecutive positive voltage pulses, the synaptic weight changes by 4.16% and 7.82%, respectively. After the four consecutive voltage pulse stimulation, the synaptic weight is maintained >60%. The learning experience is similar to the repeated learning and memory process in the human brain.

Spike-timing-dependent plasticity (STDP) is another important performance indicator of biological synapses according to the Hebbian learning rule64,65. To implement STDP, a pair of pulses is applied to the top and bottom electrodes as presynaptic and postsynaptic spikes with V+/V− = 8 V/−8 V, as shown in Fig. 8. There is an interval of 3 s between V+ and V−, and the time interval between the spikes is denoted Δt > 0 (Δt < 0; where Δt is the time interval of the pulse stimulations before and after the synapse. According to the asymmetric Hebbian learning rule, when the activity of presynaptic neurons precedes that of postsynaptic neurons, Δt > 0; otherwise, Δt < 0). The STDP characteristics of the PSiO2/PLiCoO2 memristor are shown in Fig. 8a, and the synaptic weight changes are presented in Fig. 8b. Figure 8b also shows the fitted curves of the STDP synaptic weight change ∆W, which is defined as the percentage change in the cell conductance after the STDP event. The fitting curve is described by Eq. (1).

where A and τ are the scale factor and time constant of the STDP function, respectively, and ΔW0 is a constant representing unassociated synaptic regulation. The prespike is sent to the Pt electrode, and the postspike is sent to the Si electrode. It takes ~1–3 ms to complete the STDP function, which is similar to the time consumed by the biological neural circuit to complete the STDP function (10 ms).

Conclusion

The Pt/PLiCoO2/PSiO2/Si stack delivers good electrical performance and exhibits typical synaptic functions under stimulation. The migration mechanism of lithium ions in the PLiCoO2 layer and PSiO2 layer is investigated. Electrical tests show that the SLDLP structure has improved stability, an ON–OFF ratio of 108, and a retention time of 105 s. The typical synaptic functions, such as LTP, STP, STDP, and learning experience, are achieved. The device provides pathways for transport of lithium ions and retains lithium ions in the porous structure to improve the device characteristics. The conductance can be regulated by changing the external conditions, such as pulse voltage or stimulation time. The device with the NP structure that exhibits uniform switching characteristics has great potential in scalable memristor arrays, and the memristor with the bionic SLDLP structure can be readily implemented in neuromorphic computing.

Experimental section

Preparation of the porous silicon oxide solutions

Solution A was prepared with 1.6 ml of C2H5OH, 0.16 ml of HCl (3 × 10−3 mol), and 2 ml of tetraethyl orthosilicate (C8H20O4Si). They were mixed and stirred at room temperature for 24 h. Solution B was prepared with 0.3 g of cetyltrimethylammonium chloride (C19H42Cl N), 8.88 ml of C2H5OH, and 0.16 ml of HCl (5.5 × 10−2 mol). They were mixed and stirred at room temperature for 24 h until the powder dissolved. Solution C was prepared by stirring solutions A and B at room temperature for 24 h. Mother liquor C was prepared with 1 mL of solution C and 7 mL of C2H5OH, and stirred at room temperature for 1 h.

Preparation of the porous silicon oxide films

A highly doped p-type Si (100) wafer (2 × 2 cm2) was put into equal volumes of hydrogen peroxide, acetone, and anhydrous ethanol, sonicated for 30 min to remove surface impurities, and dried with nitrogen gas. It was then rinsed with DI water, dried with nitrogen, and spin-coated by pipetting 200 μL of solution D onto the substrate. A PSiO2 film was formed by spin coating (9000 r.p.m. for 16 min) and annealing at 400 °C at a reduced pressure of 10−1 Pa under a 10 s.c.c.m. Ar flow for 1 h.

Preparation of the porous LiCoO2 films

A LiCoO2 (~100 nm) film was deposited on PSiO2/Si by magnetron sputtering. The PSiO2/Si substrate was fixed on the sample stage, and a crystalline (003) lithium cobaltite target was the target positioned at a distance of 6 cm from the substrate. The equipment was evacuated to a pressure of 10−4 Pa, and a mixture of Ar:O2 (3:1) was introduced at a flow rate of 30 s.c.c.m. to reach a working pressure of 2.0 Pa. Deposition was carried out at an RF power of 200 W and a rotation speed of 30 r.p.m. for 1 h.

Preparation of the Pt electrodes

Pt (~80 nm) films were deposited on PLiCoO2/PSiO2/Si by magnetron sputtering. A mask with an aperture of 200 μm, an array structure of 8 × 8, and an area of 2 × 2 cm2 was fixed on the PLiCoO2/PSiO2/Si surface. A high-purity Pt target was placed 6 cm from the substrate. The vacuum chamber was evacuated to 10−4 Pa after Ar was blown into the chamber at a flow rate of 30 s.c.c.m. to reach a working pressure of 2 Pa. The sputtering current was 0.45 A, the sample rotation speed was 30 r.p.m., and the deposition time was 3 min.

Device characterization

The morphology and structure of PSiO2, PLiCoO2, and nonporous SiO2 were investigated by FE-SEM, and the cross-section of Pt/PLiCoO2/PSiO2/Si was prepared with a focused ion beam. The morphology and porous features of LiCoO2 and SiO2 were examined by taking bright-field images at 200 keV on a field-emission TEM (FEI TECNAI-F20). The electrical properties and synapse behavior were determined using a Keithley 4200 semiconductor parameter analyzer and an arbitrary function generator (AFG31000, Tektronix), respectively.

References

Zhu, J. D., Zhang, T., Yang, Y. C. & Huang, R. A comprehensive review on emerging artificial neuromorphic devices. Appl. Phys. Rev. 7, 011312 (2020).

Yu, F. et al. Artificial tactile perceptual neuron with nociceptive and pressure decoding abilities. ACS Appl. Mater. Interfaces 12, 26258–26266 (2020).

Zhu, L. Q., Wan, C. J., Guo, L. Q., Shi, Y. & Wan, Q. Artificial synapse network on inorganic proton conductor for neuromorphic systems. Nat. Commun. 5, 315 (2014).

Zhang, X. Z., Huang, A. P., Hu, Q., Xiao, Z. S. & Chu, P. K. Neuromorphic computing with memristor crossbar. Phys. Status Solidi A, 215, 1700875 (2018).

Tang, J. et al. Bridging biological and artificial neural networks with emerging neuromorphic devices: fundamentals, progress, and challenges. Adv. Mater. 31, 1902761 (2019).

La, TorreC., Zurhelle, A. F., Breuer, T., Waser, R. & Menzel, S. Compact modeling of complementary switching in oxide-based ReRAM devices. IEEE Trans. Electron. Devices 66, 1268–1275 (2019).

Turing, A. M. Computing machinery and intelligence. Mind 59, 433–460 (1950).

Hebb, D. O. The Organization Of Behavior: a Neuropsychological Theory (Psychology Press, 2005).

Zidan, M. A., Strachan, J. P. & Lu, W. D. The future of electronics based on memristive systems. Nat. Electron. 1, 22–29 (2018).

Sangwan, V. K. & Hersam, M. C. Neuromorphic nanoelectronic materials. Nat. Nanotechnol., 15, 517–528 (2020).

Gu, L. L. et al. A biomimetic eye with a hemispherical perovskite nanowire array retina. Nature 581, 278–282 (2020).

Yin, J. et al. Adaptive crystallite kinetics in homogenous bilayer oxide memristor for emulating diverse synaptic plasticity. Adv. Funct. Mater. 28, 1706927 (2018).

Li, D. et al. MoS2 memristors exhibiting variable switching characteristics toward biorealistic synaptic emulation. ACS Nano 12, 9240–9252 (2018).

Ge, S. P. et al. Low‐dimensional lead‐free inorganic perovskites for resistive switching with ultralow bias. Adv. Funct. Mater. 30, 2002110 (2020).

Guan, X. et al. A monolithic artificial iconic memory based on highly stable perovskite-metal multilayers. Appl. Phys. Rev. 7, 031401 (2020).

Cao, W. et al. 2-D layered materials for next-generation electronics: opportunities and challenges. IEEE Trans. Electron. Devices 65, 4109–4121 (2018).

Zhu, J. et al. Ion gated synaptic transistors based on 2D van der Waals crystals with tunable diffusive dynamics. Adv. Mater. 30, 1800195 (2018).

Kim, S. et al. Scaling effect on silicon nitride memristor with highly doped Si substrate. Small 14, 1704062 (2018).

Mazur, T., Zawal, P. & Szaciłowski, K. Synaptic plasticity, metaplasticity and memory effects in hybrid organic–inorganic bismuth-based materials. Nanoscale 11, 1080–1090 (2019).

Shaarawy, N. et al. Design and analysis of 2T2M hybrid CMOS-memristor based RRAM. Microelectron. J. 73, 75–85 (2018).

Xia, Q. et al. Memristor-CMOS hybrid integrated circuits for reconfigurable logic. Nano Lett. 9, 3640–3645 (2009).

He, X. et al. Memristive properties of hexagonal WO3 nanowires induced by oxygen vacancy migration. Nanoscale Res. Lett. 8, 50 (2013).

Nandakumar, S. R., Minvielle, M., Nagar, S., Dubourdieu, C. & Rajendran, B. A 250 mv Cu/SiO2/W memristor with half-integer quantum conductance states. Nano Lett. 16, 1602–1608 (2016).

Paris, A. & Taioli, S. Multiscale investigation of oxygen vacancies in TiO2 anatase and their tole in memristor’s behavior. J. Phys. Chem. C 120, 22045–22053 (2016).

Liu, D., Cheng, H., Zhu, X., Wang, G. & Wang, N. Analog memristors based on thickening/thinning of Ag nanofilaments in amorphous manganite thin films. ACS Appl. Mater. Interfaces 5, 11258–11264 (2013).

Wang, Y. et al. Resistive switching mechanism in silicon highly rich SiOx (x< 0.75) films based on silicon dangling bonds percolation model. Appl. Phys. Lett. 102, 042103 (2013).

Yao, J., Sun, Z., Zhong, L., Natelson, D. & Tour, J. M. Resistive switches and memories from silicon oxide. Nano Lett. 10, 4105–4110 (2010).

Choi, B. J. et al. Electrical performance and scalability of Pt dispersed SiO2 nanometallic resistance switch. Nano Lett. 13, 3213–3217 (2013).

Kwon, S. et al. Controllable switching filaments prepared via tunable and well-defined single truncated conical nanopore structures for fast and scalable SiOx memory. Nano Lett. 17, 7462–7470 (2017).

Wang, G. et al. Nanoporous silicon oxide memory. Nano Lett. 14, 4694–4699 (2014).

Wang, G. et al. Three-dimensional networked nanoporous Ta2O5-x memory system for ultrahigh density storage. Nano Lett. 15, 6009–6014 (2015).

Kwon, S. et al. Structurally engineered nanoporous Ta2O5–x selector-less memristor for high uniformity and low power consumption. ACS Appl. Mater. Interfaces 9, 34015–34023 (2017).

Wang, T. Y. et al. Three-dimensional nanoscale flexible memristor networks with ultralow power for information transmission and processing application. Nano Lett. 20, 4111–4120 (2020).

Yan, D. et al. Soft three-dimensional network materials with rational bio-mimetic designs. Nat. Commun. 11, 1–11 (2020).

Gao, Q. et al. Stability and repeatability of a karst-like hierarchical porous silicon oxide-based memristor. ACS Appl. Mater. Interfaces 11, 21734–21740 (2019).

Mai, V. H. et al. Memristive and neuromorphic behavior in a LixCoO2 nanobattery. Sci. Rep. 5, 7761 (2015).

Choi, Y. et al. Structural engineering of Li-based electronic synapse for high reliability. IEEE Electron. Device Lett. 40, 1992–1995 (2019).

Donders, M. E. et al. Atomic layer deposition of LiCoO2 thin-film electrodes for all-solid-state Li-ion micro-batteries. J. Electrochem. Soc. 160, A3066 (2013).

Xie, J. et al. Engineering the surface of LiCoO2 electrodes using atomic layer deposition for stable high-voltage lithium ion batteries. Nano Res. 10, 3754–3764 (2017).

Nguyen, V. S. et al. Direct evidence of lithium ion migration in resistive switching of lithium cobalt oxide nanobatteries. Small 14, 1801038 (2018).

Bezza, I. et al. LiCoO2 with double porous structure obtained by electrospray deposition and its evaluation as an electrode for lithium-ion batteries. J. Alloy. Comp. 805, 19–25 (2019).

Choi, Y. M. & Pyun, S. I. Effects of intercalation-induced stress on lithium transport through porous LiCoO2 electrode. Solid State Ion. 99, 173–183 (1997).

Xue, L., Savilov, S. V., Lunin, V. V. & Xia, H. Self‐standing porous LiCoO2 nanosheet arrays as 3D cathodes for flexible Li‐ion batteries. Adv. Funct. Mater. 28, 1705836 (2018).

Chang, W. S. et al. Quartz (SiO2): a new energy storage anode material for Li-ion batteries. Energy Environ. Sci. 5, 6895–6899 (2012).

Ariel, N., Ceder, G., Sadoway, D. R. & Fitzgerald, E. A. Electrochemically controlled transport of lithium through ultrathin SiO2. J. Appl. Phys. 98, 023516 (2005).

Mu, G. et al. Microsphere‐like SiO2/MXene hybrid material enabling high performance anode for lithium ion batteries. Small 16, 1905430 (2020).

Mehonic, A. et al. Silicon oxide (SiOx): a promising material for resistance switching? Adv. Mater. 30, 1801187 (2018).

Hu, Q. et al. Lithium ion trapping mechanism of SiO2 in LiCoO2 based memristor. Sci. Rep. 9, 5081 (2019).

Zhou, J. Resistive switching characteristics of PECVD-deposited porous SiO2-based electrochemical metallisation memory cells. Electron. Lett. 52, 965–966 (2016).

Tsai, T. M. et al. Performance and characteristics of double layer porous silicon oxide resistance random access memory. Appl. Phys. Lett. 102, 253509 (2013).

Shi, C. et al. Silk flexible electronics: from Bombyx mori Silk Ag nanoclusters hybrid materials to mesoscopic memristors and synaptic emulators. Adv. Funct. Mater. 29, 1904777 (2019).

Guo, Z. et al. Spontaneous preparation of hierarchically porous silica monoliths with uniform spherical mesopores confined in a well-defined macroporous framework. Dalton Trans. 44, 13592–13601 (2015).

Feng, J. et al. Self‐aligned anisotropic plasmonic nanostructures. Adv. Mater. 31, 1900789 (2019).

Xia, Y., Xiong, Y., Lim, B. & Skrabalak, S. E. Shape‐controlled synthesis of metal nanocrystals: simple chemistry meets complex physics? Angew. Chem. Int. Ed. 48, 60–103 (2009).

Household sponge, mailto: https://m.quanjing.com/imgbuy/QJ9113240495.html.

Erokhin, V. et al. Material memristive device circuits with synaptic plasticity: learning and memory. BioNanoScience 1, 24–30 (2011).

Chen, L., Li, C., Huang, T., Ahmad, H. G. & Chen, Y. A phenomenological memristor model for short-term/long-term memory. Phys. Lett. A 378, 2924–2930 (2014).

Amsalem, O. et al. An efficient analytical reduction of detailed nonlinear neuron models. Nat. Commun. 11, 1–13 (2020).

Ménétrier, M., Saadoune, I., Levasseur, S. & Delmas, C. The insulator-metal transition upon lithium deintercalation from LiCoO2: electronic properties and 7Li NMR study. J. Mater. Chem. 9, 1135–1140 (1999).

Milewska, A. et al. The nature of the nonmetal–metal transition in LixCoO2 oxide. Solid State Ion. 263, 110–118 (2014).

Greenlee, J. D., Petersburg, C. F., Daly, W. G., Alamgir, F. M. & Alan Doolittle, W. In situ investigation of the channel conductance of a Li1-xCoO2 (0 < x < 0.5) ionic-electronic transistor. Appl. Phys. Lett. 102, 213502 (2013).

Yu, Y. et al. Synthesis of donor–acceptor gridarenes with tunable electronic structures for synaptic learning memristor. ACS Omega 4, 5863–5869 (2019).

Murre, J. M. & Dros, J. Replication and analysis of Ebbinghaus’ forgetting curve. PloS ONE 10, e0120644 (2015).

Linares-Barranco, B. et al. On spike-timing-dependent-plasticity, memristive devices, and building a self-learning visual cortex. Front. Neurosci. 5, 26 (2011).

Wang, Y. F., Lin, Y. C., Wang, I. T., Lin, T. P. & Hou, T. H. Characterization and modeling of nonfilamentary Ta/TaOx/TiO2/Ti analog synaptic device. Sci. Rep. 5, 10150 (2015).

Acknowledgements

This research was supported by the National Natural Science Foundation of China (Grant Nos. 51872010, 11574017, 11574021, and 11604007), Special Foundation of Beijing Municipal Science & Technology Commission (Grant No. Z161100000216149), and City University of Hong Kong Strategic Research Grant (SRG) No. 7005105.

Author information

Authors and Affiliations

Contributions

Q.G. designed and performed the experiments, and wrote the manuscript. A.H., Y.J., Jingjing Zhang, X.C., X.G., Q.H., M.W., and Z.X. assisted in data analysis. Jing Zhang assisted in measurement and device fabrication. P.K.C. corrected the manuscript. All authors interpreted the data and wrote the manuscript. A.H. planned and supervised all phases of the project and corrected the manuscript.

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that they have no conflict of interest.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Gao, Q., Huang, A., Zhang, J. et al. Artificial synapses with a sponge-like double-layer porous oxide memristor. NPG Asia Mater 13, 3 (2021). https://doi.org/10.1038/s41427-020-00274-9

Received:

Revised:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41427-020-00274-9