Abstract

Sophisticated three-dimensional (3D) forms are expected to be one of the significant development trends in next-generation microelectronics because of their capabilities of rendering substantially enhanced performances, a high degree of integration, and novel functionalities. To date, a diversity of manufacturing methods has been developed for 3D microelectronic devices with different structural and functional features. Most of these methods fall into two categories, i.e., micromanufacturing technologies and mechanically guided 3D assembly approaches. From this perspective, we review the different manufacturing methods and their specific features as well as their limitations. At present, there is still no universal method that can deterministically form 3D microelectronic devices with very high geometric complexity and nanoscale precision. We offer an outlook on future developments in the manufacturing of 3D multifunctional microelectronics devices and provide some perspectives on the remaining challenges as well as possible solutions. Mechanically guided 3D assembly based on compressive buckling is proposed as a versatile platform that can be merged with micromanufacturing technologies and/or other assembly methods to provide access to microelectronic devices with more types of integrated functions and highly increased densities of functional components.

Similar content being viewed by others

The formation of three-dimensional (3D) microdevices in advanced materials with feature sizes ranging from nanometers to millimeters has important implications in a diversity of areas, from energy storage/harvesting1, photonic sensing2,3, and micro/nanoelectromechanical systems (MEMS/NEMS)4,5 to transistors6, because of their advantages (e.g., smaller footprint, lower weight, higher functional performance, lower power consumption, high productivity, and potentially lower cost) over planar 2D counterparts. In the last couple of decades, many different approaches have been explored and/or developed to deterministically form 3D microelectronic components and devices. These approaches can be classified into two broad classes: modern micromanufacturing approaches and mechanically guided assembly approaches. Modern micromanufacturing technologies, including lithographic patterning, etching, and deposition, can fabricate 3D microelectronics consisting of simple constructions (e.g., suspended/stacked components) in a relatively direct manner. In contrast, mechanically guided 3D assembly leverages the mature planar processing techniques available in the semiconductor industries to fabricate 2D precursor structures, which are then transformed into well-controlled 3D forms with the aid of various mechanical forces (e.g., capillary forces7,8,9, residual stresses1,2,10, constraint forces in active materials11,12,13). Here, we summarize the advantages and limitations of the aforementioned approaches and provide some perspectives on the remaining challenges as well as possible solutions in the manufacturing of multifunctional 3D microelectronic devices.

Micromachining, which represents one of the first explored micromanufacturing approaches, was initially developed for building 3D MEMS. A diversity of micromachining technologies are now available, including bulk/surface micromachining, deep reactive ion etching (DRIE), hot embossing, laser and focused ion-beam machining. Among these technologies, the first two (bulk/surface micromachining and DRIE) have thus far been widely exploited in the electronics industries. Bulk micromachining involving the selective removal of the substrate material to obtain 3D components could be achieved by chemical or physical means. Here, chemical wet etching is more popularly used than physical means owing to its higher etch rates, selectivity, and modifiability. According to the directionality of etching, there are two general types—isotropic and anisotropic wet etching—masked with lithography patterning. Surface micromachining techniques offer more precise dimensional and structural control than bulk techniques. These techniques typically include step-by-step deposition and patterning of sacrificial and structural layers, followed by selective removal of the underlying sacrificial layer to release the 3D structural layer14, as illustrated in Fig. 1a. For 3D MEMS with high aspect-ratio features, DRIE (also termed the ‘Bosch process’) was developed by alternately etching Si and depositing etch-resistant material on the sidewalls, which can avoid the etching of sidewalls. Recent studies extended this technology to a wider range of materials (e.g., silicon carbide, titanium, tungsten, glass, and polymers), which demonstrates it as a cost-effective method of deep etching with high selectivity and precision. Although the frequent switching of gases and etching parameters makes the equipment quite complicated and expensive, DRIE is still one of the most widely used techniques to accurately realize high aspect-ratio etching. According to the specific requirements of different applications, various micromachining technologies can be combined to manifest the feature of each technology, enabling the manufacture of 3D MEMS with diverse suspension geometries (e.g., the 3D MEMS mirror15 in Fig. 1a). In addition, bottom–up approaches that build smaller units (usually atoms and molecules) into more-complex assemblies based on their chemical properties also represent an important class of manufacturing approaches to the self-assembly of a variety of morphological functional nanomaterials16, ranging from quantum dots, nanowires (NWs), and nanotubes to two-dimensional materials. Integration strategies17 that combine bottom–up nanomaterials with micromachining technologies can facilitate the fabrication of 3D nanodevices. An example shown in Fig. 1b illustrates the fabrication of NW resonator arrays using these bottom–up integration processes18.

a Schematic illustrations of typical 3D cantilever fabrication assisted by etching of the sacrificial layer and SEM images of a 3D MEMS mirror15. a is adapted with permission from ref. 15. (Copyright © 2018 IEEE). b Bottom–up integration process for the fabrication of NW resonator arrays18. b is adapted with permission from ref. 18. (Copyright © 2008 Nature Publishing Group). c, d Schematic illustrations of the fabrication process and SEM images of 3D stacked GAA transistors obtained by selective etching of sacrificial layers19 and alternating etching-passivation steps20. c–d are adapted with permission from refs. 19,20. (Copyright © 2008 & 2014 IEEE). e–g Three types of 3D integration technology and images of some representative examples: e stacked-die with wire bonding and package-on-package stacking22, f memory stacking with TSVs26, g wafer-to-wafer bonding (bumpless)27. e–g are adapted with permission from refs. 22,26,27. (Copyright © 2009 IEEE, 2016 IEEE & 2006 IEEE.)

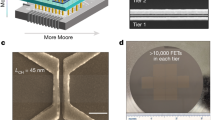

The persistent demand for higher functional density, higher performance, and lower power consumption has been driving the structure of transistors to gradually evolve from the traditional planar layout to the current widely used Fin-FETs (tri-gate) and to the next-generation 3D gate-all-around (GAA) structures. In 2008, T. Ernst et al.19 demonstrated a 3D stacked GAA multichannel CMOS by selective removal of sacrificial SiGe layers from multilayer Si/SiGe superlattices epitaxially grown on top of silicon-on-Insulator (SOI) substrates and gate-stack deposition of Si multichannels all around, as shown in Fig. 1c. By introducing the etch-passivation cycle into DRIE technology, De Marchi et al.20 and Lee et al.21 developed techniques for etching suspended multi-NW GAA FETs on an SOI substrate and on a bulk silicon substrate, respectively, as illustrated in Fig. 1d. According to recent reports from IMEC and Samsung, the 3D GAA FET architecture is a very promising candidate to extend Moore’s Law for future technology with <7 nm nodes. The innovation of 3D transistors through the introduction of new processing technologies will continue to drive the development of the microelectronics industry.

To achieve more diverse functions and a higher degree of integration, beyond those achievable through simple lithography scaling based on a single chip (system on chip), technologies of heterogeneous integrations in 3D architecture have been attracting increasing attention, such as 3D integrated circuit (IC) packaging, 3D IC integration, and 3D Si integration22,23. Invented in the 1980s, 3D IC packaging has now been widely used in industries as a type of mass production technology, a key component of which involves stacking several conventional components in the vertical direction with robust electrical connections (e.g., wire bonding and package-on-package stacking, as shown in Fig. 1e). With the assistance of through-silicon-via (TSV) technology23,24,25 that enable a vertical interconnection completely through a silicon wafer, 3D IC/Si integration technologies were developed to achieve a higher level of integration than are possible with Moore technologies. Compared with 3D IC packaging, 3D IC integration can stack much thinner IC chips with TSVs and microbumps26 (Fig. 1f), thereby offering higher integration, a smaller footprint, higher performance, and lower power consumption. With a bumpless and smaller TSV diameter, 3D Si integration (Fig. 1g) aims to achieve further enhanced integration through direct wafer-to-wafer bonding27 and is considered the best means of competing with Moore’s law. However, there are still many technical issues to be solved to enable batch manufacturing, such as thermal management, vias formation, and thin-wafer handling.

The development of the aforementioned micromanufacturing technologies has offered the capabilities of achieving a variety of 3D suspended MEMS structures, stacked GAA transistors, and 3D ICs. Their relatively high cost and low efficiency, however, represent prevalent issues with these technologies, especially in the fabrication of relatively complex 3D constructions. Moreover, devices with more complex 3D geometries (e.g., conical spirals and hemispherical and polyhedral shapes) are almost inaccessible to these technologies.

The approaches based on mechanically guided 3D assembly represent an alternative route to the formation of 3D microelectronic devices with the ability to build highly complex 3D geometries, including those with multilevel and even hierarchical constructions. As indirect routes that can make full use of the well-established planar technologies in the semiconductor and integrated photonic industries, this class of approaches offers a broad range of applicability, either to most of the different types of materials available (e.g., semiconductors, metals, polymers, ceramics) or over different length scales (from tens of nanometers to centimeters)28. A key aspect of these approaches involves the application of different types of mechanical forces (residual stress1,2, constraint forces in heat/light/solvent-responsive active materials11,13,29, capillary forces7,8, and the compressive forces associated with a soft substrate3,30,31) to deform strategically designed 2D precursor structures into 3D configurations through bending, twisting, or a mixed mode of deformations.

Figure 2a shows a schematic illustration of the residual stress method used to fabricate tubular or helical 3D electronic devices at the nanoscale1. By controlling the relevant fabrication parameters (e.g., deposition rate, temperature, or composition), the misfit strain between the top and bottom layers induces the self-rolling of 2D precursors into deterministic 3D structures after the selective etching of the sacrificial layer32. Using these methods, some impressive 3D electronic devices were fabricated, ranging from rolled-up field effect transistors with higher (by five orders) on-ratios33, 3D tubular infrared photodetectors with a widened visual field2, and 3D radio frequency (RF)/microwave air-core transformers with highly enhanced performance compared with that of their other reported on-chip planar counterparts34. A representative example of a microelectronic device with remarkable cycling performance is shown in Fig. 2a. The heterogeneous integration of multiple electronic components at different in-plane locations (e.g., ICs) remains a challenge.

a Schematic illustration of residual stress-induced rolling and its application to lithium-ion batteries1. a is adapted with permission from ref. 1. (Copyright © 2013 Wiley-VCH Verlag GmbH & Co. KGaA, Weinheim). b Folding-dominated method that relies on the use of active materials and its application in 3D deployable organic thin-film transistors (OTFTs)12. b is adapted with permission from ref. 12. (Copyright © 2014 Wiley-VCH Verlag GmbH & Co. KGaA, Weinheim). c Folding-dominated method induced by capillary forces and a representative microelectronic device with optically active split-ring resonator (SRRs) patterns7. c is adapted with permission from ref. 7. (Copyright © 2011 Wiley-VCH Verlag GmbH & Co. KGaA, Weinheim). d Mechanically guided 3D assembly by compressive forces imparted by a prestrained substrate28 and 3D photodetection systems capable of measuring incident light parameters3. d is adapted with permission from ref. 3. (Copyright © 2018 Macmillan Publishers Limited, part of Springer Nature)

Figure 2b illustrates a strategy that leverages the constraint forces arising from the strain mismatch of active materials (e.g., hydrogels35, shape memory alloys/polymers29, liquid crystal elastomers36) and passive materials to drive 2D-to-3D transformations. In the presence of external stimuli (e.g., high temperature, solvent, or light exposure), the recovery of a programmable SMP/SMA or the swelling of a hydrogel results in spatially nonuniform strains along the out-of-plane direction, thereby leading to bending or folding deformations that can be used as a basis of origami assembly. Some representative devices have been fabricated using this approach, such as 3D deployable organic thin-film transistors (OTFTs)12 and 3D humidity sensors13. In response to a temperature increase, the planar OTFT demonstrated in Fig. 2b can deploy into 3D complex shapes (e.g., helix) with the capability of actively conforming to target objects without any significant electrical degradation. In this approach, the active materials that operate in different particular environments impose certain limitations on the integration of microelectronic devices, and scalability sets practical constraints on industrial applications.

Capillary forces or surface tension serves as another type of mechanical trigger to drive the 3D assembly of microelectronic devices from 2D patterns. Figure 2c schematically illustrates the folding assembly of a 3D structure guided by the capillary forces of the melted solder. These approaches have been exploited to achieve high-performance microelectronic devices, such as 3D photovoltaic devices with a higher conversion efficiency than their planar counterparts8 and cubic plasmonic resonators with optically active split-ring resonator patterns7. However, the presence of water or meltable solder at the folding creases of 3D microelectronic devices places certain limitations on their practical applications. The accessible range of 3D geometries based on this method (Fig. 2c) and those shown in Fig. 2a and b is constrained by the simple mode of deformations, mainly in terms of bending.

Figure 2d presents a strategy that relies on the compressive forces of a prestrained soft substrate to transform 2D microelectronic devices into a 3D configuration through controlled compressive buckling. Since this process involves coordinated bending/twisting deformations as well as translational/rotational motions, a rich diversity of 3D geometries (Fig. 2d) can be formed, together with the kirigami/origami design concepts associated with strategic engineering of the 2D precursor patterns and the substrates. Recent advances have demonstrated the utility of this assembly approach in obtaining a variety of advanced multifunctional devices, such as 3D scaffolds for engineered dorsal root ganglion neural networks37, wearable physiological status-monitoring platforms with 3D interconnected networks of helical microcoils38, 3D photodetection systems capable of measuring incident light parameters (i.e., direction, intensity)3, high-performance hemispherical electrically small antennas with tunable working frequencies39, 3D energy-harvesting devices with broadband operation and high efficiency40, 3D interdigital supercapacitors with solid-state electrolytes41, and 3D RFelectronic devices capable of concealing themselves from external detection42. Although this compressive buckling approach is applicable to a broad range of materials and 3D geometries, it is still very challenging to form freestanding 3D electronic devices without any accessories or those with lateral dimensions down to several hundreds of nanometers. The development of inverse design algorithms that can map targeted 3D configurations onto the initial 2D precursor structures also represents an unsolved problem that is central to this approach.

Although the aforementioned methods each offer specific 3D fabrication features and capabilities, none of them is without limitations, either in terms of material compatibility, accessible feature sizes and 3D layouts or the integrability of diverse functional components. Recent studies suggest that the effective combination of different technologies could provide possible solutions to overcome some of those limitations. For example, 3D IC integration technology enables the construction of an interposer (carrier) microdevice that incorporates fluidic microchannels fabricated through wet etching for thermal management25, as shown in Fig. 3a. Figure 3b demonstrates a TSV-based 3D integration of the chip-scale package of MEMS and ICs, both of which are formed using micromachining technology43. This type of heterogeneous integration of multiple functional components (e.g., logic processors, RF devices, biochips, sensors, MEMS) into a single chip may provide cost-optimized and value-added system solutions, which are a popular research field in both industry and academia. By introducing thin patterned layers with well-defined residual stresses as 2D precursor structures, mechanically guided 3D assembly based on compressive buckling is able to form highly complex 3D geometries that are otherwise inaccessible to a separate approach44. Based on such a combination, 3D configurations that evolve from high-order buckling modes or those that are transformed through concurrent global buckling and local rolling can be achieved, with an example shown in Fig. 3c. In addition, the residual stresses owing to the metal plasticity result in irrecoverable deformations at predefined locations with high strains, which can be utilized to yield freestanding 3D mesostructures assembled through compressive buckling (Fig. 3d)37. Such untethered 3D metallic mesostructures bypass the engineering constraints set by the underlying elastomer substrates and hold promise for applications in flexible microrobotics and biological scaffolds.

a Schematic illustration of an interposer (carrier) device with fluidic microchannels for thermal management25. a is adapted with permission from ref. 25. (Copyright © 2011 IEEE). b Schematic illustration and photograph of chip-scale integrated MEMS and ICs43. b is adapted with permission from ref. 43. (Copyright © 2015 Springer Nature). c Schematic illustration of mechanically guided 3D assembly assisted by residual stresses. This combination enables the formation of a pop-down mode in the central ribbon44. c is adapted with permission from ref. 44. (Copyright © 2017 Wiley-VCH Verlag GmbH & Co. KGaA, Weinheim). d Freestanding 3D structures enabled by the combination of mechanically guided 3D assembly and residual plastic deformations of metals at the locations of highest bending deformations37. d is adapted with permission from ref. 37. (Copyright © 2017 National Academy of Sciences). e Schematic illustration of the approach that merges micromanufacturing technologies and other mechanically guided 3D assembly methods with 3D assembly based on compressive buckling

Because of the broad applicability to nearly any type of materials and the capability of integrating with diverse microelectronic devices, including commercial available platforms (e.g., a flexible printed circuit board), mechanically guided 3D assembly based on compressive buckling has the potential to serve as a fundamental platform for the 3D fabrication of microelectronic devices. Merging the other micromanufacturing technologies and/or assembly approaches with the above fundamental platform is anticipated to offer unprecedented capabilities and scalabilities (Fig. 3e). For example, nanoscale MEMS and GAA transistors with simple 3D configurations formed using micromachining and integration technologies could serve as a generalized, advanced form of 2D precursors in mechanically guided assembly to obtain hierarchical microelectronic devices with increased device densities and/or novel functionalities. The devices formed in this manner could encompass a diversity of 3D functional components over different length scales, targeted for the integration of multiple functionalities into a single system. Vast opportunities also exist in the development of viable technologies and experimental equipment that can precisely apply additional types of mechanical forces (e.g., residual stresses, constraint forces in heat/light/solvent-responsive active materials) based on the assembly platform of compressive buckling. Further research along this direction could follow by exploring the extended capabilities of 3D assembly and the reconfigurability of 3D microelectronic devices.

References

Deng, J. et al. Naturally rolled-up C/Si/C trilayer nanomembranes as stable anodes for lithium-ion batteries with remarkable cycling performance. Angew. Chem. Int. Ed. 52, 2326–2330 (2013).

Han, W. et al. Self-rolling and light-trapping in flexible quantum well–embedded nanomembranes for wide-angle infrared photodetectors. Sci. Adv. 2, e1600027 (2016).

Lee, W. et al. Two-dimensional materials in functional three-dimensional architectures with applications in photodetection and imaging. Nat. Commun. 9, 1417 (2018).

Cha, J. & Daraio, C. Electrical tuning of elastic wave propagation in nanomechanical lattices at MHz frequencies. Nat. Nanotechnol. 13, 1016–1020 (2018).

Cha, J., Kim, K. W. & Daraio, C. Experimental realization of on-chip topological nanoelectromechanical metamaterials. Nature 564, 229–233 (2018).

Zhang, C. et al. A review of III–V planar nanowire arrays: selective lateral VLS epitaxy and 3D transistors. J. Phys. D: Appl. Phys. 50, 393001 (2017).

Cho, J. H. et al. Nanoscale origami for 3D optics. Small 7, 1943–1948 (2011).

Guo, X. et al. Two- and three-dimensional folding of thin film single-crystalline silicon for photovoltaic power applications. Proc. Natl Acad. Sci. USA. 106, 20149–20154 (2009).

Liu, Q. & Xu, B. Two- and three-dimensional self-folding of free-standing graphene by liquid evaporation. Soft Matter 14, 5968–5976 (2018).

Karnaushenko, D. D., Karnaushenko, D., Makarov, D. & Schmidt, O. G. Compact helical antenna for smart implant applications. NPG Asia Mater. 7, e188–e188 (2015).

Yu, C. et al. Electronically programmable, reversible shape change in two- and three-dimensional hydrogel structures. Adv. Mater. 25, 1541–1546 (2013).

Reeder, J. et al. Mechanically adaptive organic transistors for implantable electronics. Adv. Mater. 26, 4967–4973 (2014).

Li, X. & Serpe, M. J. Understanding the shape memory behavior of self-bending materials and their use as sensors. Adv. Funct. Mater. 26, 3282–3290 (2016).

Jun-Bo, Y., Byeong-Il, K., Yun-Seok, C. & Yoon, E. 3-D construction of monolithic passive components for RF and microwave ICs using thick-metal surface micromachining technology. IEEE T. Microw. Theory 51, 279–288 (2003).

Wang, H., Zhou, L., Zhang, X. & Xie, H. Thermal reliability study of an electrothermal MEMS mirror. IEEE T. Device Mat. Re. 18, 422–428 (2018).

Dasgupta, N. P. et al. 25th anniversary article: semiconductor nanowires - synthesis, characterization, and applications. Adv. Mater. 26, 2137–2183 (2014).

Lu, W. & Lieber, C. M. Nanoelectronics from the bottom up. Nat. Mater. 6, 841–850 (2007).

Li, M. et al. Bottom-up assembly of large-area nanowire resonator arrays. Nat. Nanotechnol. 3, 88–92 (2008).

Ernst, T. et al. 3D Multichannels and stacked nanowires technologies for new design opportunities in nanoelectronics. In 2008 IEEE International Conference on IC Design & Technology, Proceedings, 265–268 (IEEE 2008).

De Marchi, M. et al. Top–down fabrication of gate-all-around vertically stacked silicon nanowire FETs with controllable polarity. IEEE Trans. Nanotechnol. 13, 1029–1038 (2014).

Lee, B. H. et al. Vertically integrated multiple nanowire field effect transistor. Nano Lett. 15, 8056–8061 (2015).

Carson, F. P., Kim, Y. C. & Yoon, I. S. 3-D stacked package technology and trends. Proc. IEEE 97, 31–42 (2009).

Lau, J. H. Overview and outlook of through‐silicon via (TSV) and 3D integrations. Microelectron. Int. 28, 8–22 (2011).

Michailos, J. et al. New challenges and opportunities for 3D Integrations. In 2015 IEEE International Electron Devices Meeting, 8.5.1–8.5.4 (IEEE 2015).

Lau, J. H. Evolution, challenge, and outlook of TSV, 3D IC integration and 3d silicon integration. 2011 International Symposium on Advanced Packaging Materials (APM), 462–488 (IEEE 2011).

Kirihata, T. et al. Three-dimensional dynamic random access memories using through-silicon-vias. IEEE J. Emerg. and Selected Top. Circ. Sys. 6, 373–384 (2016).

Burns, J. A. et al. A wafer-scale 3-D circuit integration technology. IEEE Trans. Electron Devices 53, 2507–2516 (2006).

Zhang, Y. et al. Printing, folding and assembly methods for forming 3D mesostructures in advanced materials. Nat. Rev. Mater. 2, 17019 (2017).

Janbaz, S., Hedayati, R. & Zadpoor, A. A. Programming the shape-shifting of flat soft matter: from self-rolling/self-twisting materials to self-folding origami. Mater. Horiz. 3, 536–547 (2016).

Yan, Z. et al. Mechanical assembly of complex, 3D mesostructures from releasable multilayers of advanced materials. Sci. Adv. 2, e1601014 (2016).

Xu, S. et al. Assembly of micro/nanomaterials into complex, three-dimensional architectures by compressive buckling. Science 347, 154–159 (2015).

Xu, B., Zhang, B., Wang, L., Huang, G. & Mei, Y. Tubular Micro/Nanomachines: From the Basics to Recent Advances. Adv. Funct. Mater. 28, 1705872 (2015).

Grimm, D. et al. Rolled-up nanomembranes as compact 3D architectures for field effect transistors and fluidic sensing applications. Nano Lett. 13, 213–218 (2013).

Huang, W. et al. Three-dimensional radio-frequency transformers based on a self-rolled-up membrane platform. Nat. Electron. 1, 305–313 (2018).

Palleau, E., Morales, D., Dickey, M. D. & Velev, O. D. Reversible patterning and actuation of hydrogels by electrically assisted ionoprinting. Nat. Commun. 4, 2257 (2013).

Agrawal, A., Yun, T., Pesek, S. L., Chapman, W. G. & Verduzco, R. Shape-responsive liquid crystal elastomer bilayers. Soft Matter 10, 1411–1415 (2014).

Yan, Z. et al. Three-dimensional mesostructures as high-temperature growth templates, electronic cellular scaffolds, and self-propelled microrobots. Proc. Natl Acad. Sci. USA. 114, E9455–E9464 (2017).

Jang, K. I. et al. Self-assembled three dimensional network designs for soft electronics. Nat. Commun. 8, 15894 (2017).

Liu, F. et al. High performance, tunable electrically small antennas through mechanically guided 3D assembly. Small 15, e1804055 (2018).

Han, M. et al. Three-dimensional piezoelectric polymer microsystems for vibrational energy harvesting, robotic interfaces and biomedical implants. Nat. Electron. 2, 26–35 (2019).

Ling, Y. et al. Mechanically assembled, three-dimensional hierarchical structures of cellular graphene with programmed geometries and outstanding electromechanical properties. ACS Nano 12, 12456–12463 (2018).

Fu, H. et al. Morphable 3D mesostructures and microelectronic devices by multistable buckling mechanics. Nat. Mater. 17, 268–276 (2018).

Fischer, A. C. et al. Integrating MEMS and ICs. Microsyst. Nanoeng. 1, 15005 (2015).

Fu, H. et al. Mechanically-guided deterministic assembly of 3D mesostructures assisted by residual stresses. Small 13, 1700151 (2017).

Acknowledgements

Y.Z. acknowledges support from the National Natural Science Foundation of China (Grant nos. 11672152 and 11722217) and the Tsinghua National Laboratory for Information Science and Technology. X.G. acknowledges support from the National Natural Science Foundation of China (Grant no. 11702155). Z.X. acknowledges support from the National Postdoctoral Program for Innovative Talents (Grant No. BX20180157) and the China Postdoctoral Science Foundation (Grant no. 2018M641332).

Author’s contributions

X.G. and Z.X. contributed equally to this work. Y.Z., X.G., and Z.X. wrote the text and designed the figures. Y.Z. guided this work and designed the plan of the whole perspective. All authors commented on the paper.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that they have no conflict of interest.

Additional information

Publisher’s note: Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Guo, X., Xue, Z. & Zhang, Y. Manufacturing of 3D multifunctional microelectronic devices: challenges and opportunities. NPG Asia Mater 11, 29 (2019). https://doi.org/10.1038/s41427-019-0129-7

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41427-019-0129-7

This article is cited by

-

Probability-Based Analyses of the Snap-Through in Cage-Shaped Mesostructures Under Out-of-Plane Compressions

Acta Mechanica Solida Sinica (2023)

-

High-sensitive MIS structures with silicon nanocrystals grown via solid-state dewetting of silicon-on-insulator for solar cell and photodetector applications

Journal of Materials Science: Materials in Electronics (2022)

-

Morphable three-dimensional electronic mesofliers capable of on-demand unfolding

Science China Materials (2022)