Abstract

High-k dielectric oxides are supposedly ideal gate-materials for ultra-high doping in graphene and other 2D-crystals. Here, we report a temperature-dependent electronic transport study on chemical vapor deposited-graphene gated with SrTiO3 (STO) thin film substrate. At carrier densities away from charge neutrality point the temperature-dependent resistivity of our graphene samples on both STO and SiO2/Si substrates show metallic behavior with contributions from Coulomb scattering and flexural phonons attributable to the presence of characteristic quasi-periodic nano-ripple arrays. Significantly, for graphene samples on STO substrates we observe an anomalous ‘slope-break’ in the temperature-dependent resistivity for T = 50 to 100 K accompanied by a decrease in mobility above 30 K. Furthermore, we observe an unusual decrease in the gate-induced doping-rate at low temperatures, despite an increase in dielectric constant of the substrate. We believe that a complex mechanism is at play as a consequence of the structural phase transition of the underlying substrate showing an anomalous transport behavior in graphene on STO. The anomalies are discussed in the context of Coulomb as well as phonon scattering.

Similar content being viewed by others

Introduction

Graphene1, a 2-dimensional (2D) sheet of carbon atoms in a honeycomb lattice, is poised to transform the electronic industry thus promising a unique platform for many novel device applications, such as, nanoelectronics, optoelectronics and flexible transparent devices2,3,4. As a single-atom-thick layer, the transport property of graphene is highly influenced by the supporting substrate1,5,6. SiO2/Si, a conventional substrate that provides an excellent optical contrast, has been extensively used to understand the charge transport phenomena in graphene in terms of momentum relaxation from charge impurities and interfacial phonons. Wafer-scale growth of graphene by chemical vapor deposition (CVD) methods7 has made it increasingly feasible to explore a variety of novel functional substrates for engineering specific applications by means of tuning substrate-induced screening and by inducing strain5,8,9,10,11.

Replacement of SiO2/Si substrate by hexagonal boron nitride improves the carrier mobility by several orders of magnitude while limiting the maximum carrier density (~3 × 1012 cm−2). Interestingly, at ultra-high doping the possibility of superconductivity in graphene has been theoretically predicted12,13 while experimentally the optimal doping has still not been achieved to explore such phenomena. In the process, introduction of substrates with high dielectric constant6,8,9,14 or gating with polymer electrolyte15 has increased the carrier density by one-to-two orders in magnitude with fascinating electronic transport that can be attributed to screening as well as many-body interactions. The inability to reach expected high carrier densities for graphene gated with high-k dielectrics remains a puzzle-6,8,9,16,17 and points to the need to understand substrate-graphene interaction in detail beyond the expected crucial role of the electron-phonon scattering at the interface17. Non-linear temperature-dependence of resistance particularly at higher temperatures have been variously attributed to scattering from adatoms or defects, charge impurities, surface optical (SO) phonons of the underlying SiO2/Si substrate and to the out-of-plane flexural phonons of graphene17. However, the strength of the coupling between SO phonons or the flexural modes and graphene electrons remains not well understood.

A high-k dielectric substrate (e.g. Al2O3, HfO2, Pb1-xZrxTiO3 and STO to name a few) is an ideal platform to investigate several aspects relating to the electronic transport in graphene at ultra-high carrier densities. STO has a dielectric constant of ~300 at room temperature where softening of a low-energy phonon with decreasing temperature brings the material to ferroelectric instability thus dramatically increasing the dielectric constant to about 104 (in bulk) at very low temperatures which makes it a promising candidate as gate-dielectric in order to achieve ultra-high carrier densities. Surprisingly, the reported maximum carrier densities achieved in graphene field-effect transistor (FET) gated with STO is ~1 × 1013 cm-2.6 Similarly, graphene devices gated with the various high-k dielectrics are also limited to a range of 1012 to 1013 cm−2.9,18,19,20,21,22 Though it is believed to be the interfacial adsorbates and defect states that play an important role, the microscopic picture and the mechanism behind is still a matter of debate. In the present work we would like to address and bring out the microscopic details at the interface that may be held responsible for such limitations. We have performed temperature-dependent transport studies on STO-gated graphene FETs and observed an unusual slope-break in resistivity between ~ 50 to 100 K, in concomitant with a decline in the carrier injection at lower temperatures. We propose that in addition to the impurity scattering, the structural phase transitions of STO significantly change phonon density of states as well as the interface between graphene and the substrate which are expected to have a strong effect on doping of graphene as well as the transport properties.

Results

PLD grown thin films of STO on Nb:STO were examined by x-ray diffraction (XRD), atomic force microscopy (AFM) and dielectric measurements. As shown in Figure 1a, the XRD data suggest an epitaxial growth of the thin films while the AFM image in Figure 1b shows the typical roughness (<1 nm). The voltage-dependent polarization (P-Vg curve) of the thin films was measured at various temperatures as shown in Figure 1c for four different temperatures. The dielectric constant (εr) was extracted from the slope of P-Vg data: at room temperature εr ~ 300 and rises to ~600 by 10 K. However, the dielectric constant measured using graphene as an electrode is found to be lower than that actually measured using Au-electrode (see Figures S1 and S2) which may be due to contribution from quantum capacitance of graphene23,24 or charge traps/impurities as well as surface dipoles at the graphene-STO interface25. The Raman spectrum of graphene on STO, shown in the top panel of Figure 1d, has the characteristic G and 2D bands with very weak D-band merged with weak signatures of STO Raman phonons, shown in the bottom panel of Figure 1d. The Raman signature of graphene, therefore, suggests the CVD-graphene to be a single layer with minimal defects.

(a) XRD data of SrTiO3/Nb:SrTiO3 thin film substrate, (b) Typical morphology (roughness) of the thin film substrates as measured by Atomic Force Microscopy, (c) The linear voltage-dependent polarization (P-Vg) of the thin films at a few temperatures measuring the dielectric constant (εr), shown in the inset, (d) Raman signatures of graphene on SrTiO3 (STO) thin film and the STO substrate.

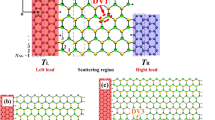

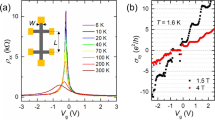

A schematic of the Hall-bar geometry of graphene FET is depicted in Figure 2a (an SEM image of which is shown in the inset of Figure 2c). The typical gate dependence of graphene resistivity (at room temperature) is shown in Figure 2b. A carrier density of about n = I(ΔB/ΔVH)/e = 9 × 1012 cm−2 can be achieved at nearly all temperatures, (where I is the current, B is the applied magnetic field, VH is the Hall voltage and e is the electronic charge) while at low temperatures (below 50 K) it reaches to about 12 × 1012 cm−2. However, surprisingly the carrier density saturates at this value (~12 × 1012 cm−2) at a gate-voltage of ~5 V (i.e. an electric field of ~150 kVcm−1) and becomes unresponsive to any higher applied gate-voltage (as shown in Figure 2c). It is to be noted that a similar observation may be made from ferroelectric Pb(ZrTi)O3 gated9 as well as bulk-STO gated6 graphene devices where the reported maximum carrier density is close to what is observed in our STO thin film gated devices (Figure 2c). Such saturation may seem unexpected since the dielectric constant of STO (and also in our STO thin film) increases with decreasing temperature. Possible explanations for this process are discussed later. Temperature-dependent resistivity of STO gated graphene has been measured on six devices fabricated on three different substrates. Data from two different devices (samples), showing distinct characteristics are shown in Figure 3 over a temperature range of ~2 K to 300 K at various carrier densities. The resistivity at all carrier densities increases monotonically with increasing temperature in confirmation with the metallic nature of doped graphene. However, an unusual response that appears as a ‘slope-break’ in the temperature range of 50–100 K can be clearly noticed which is absent for devices gated with SiO2/Si, as shown in Figure 3c (an AFM image of CVD graphene on SiO2/Si is shown in Figure S3). In another representation, this unusual behavior may also be noted in the temperature-dependent Temperature-Coefficient-of-Resistivity (TCR), defined as: TCR = 1/ρ(dρ/dT). The normalized TCR (i.e., TCR/TCRMax) as a function of temperature also shows a broad peak in the same temperature range (as shown in Figure S4) corroborating the ‘slope-break’ in resistivity.

(a) A schematic of the graphene FET on SrTiO3/Nb:SrTiO3 in Hall-bar geometry, (b) Gate-voltage-dependent resistivity of graphene on SrTiO3 at 300 K, (c) Gate-voltage-dependent carrier density at 10 K. Inset shows an SEM image of a typical graphene FET on SrTiO3. The (yellow colored) bar indicates a length-scale of 1 micron.

Temperature-dependent resistivity (ρ) of CVD-graphene supported on STO (Sample-1 in (a) and Sample-2 in (b)) at a few electron densities and on SiO2/Si substrate (c) at an electron density of 2.5 × 1012/cm2. The dashed lines in (a) represent the typical T2-dependence. A clear ‘slope-change’ can be seen in STO-gated ‘ρ vs T’ data deviating from the T2-dependence in the 50-100 K range, as shown by shaded-region, as also seen in the simulated data for two different carrier densities (n1 by dashed lines and 2n1by solid lines) in (d), whereas no such ‘slope-change’ is observed in SiO2/Si-gated device (see inset) in the temperature range.

These anomalies in the resistivity as well as TCR data may be associated with the structural phase transition of the underlying substrate, STO/Nb:STO, near 105 K and another at 55 K. At temperatures below ~ 50 K, the resistivity in our STO gated graphene devices is carrier dependent and shows metallic behavior down to the lowest temperature while in SiO2 gated device it shows an upturn undergoing metal to insulator transition owing to activation of Coulomb impurities – viz. electron-hole puddles26. Figure 4 shows the temperature dependence of mobility at a few carrier (electron) densities (2 × 1012, 3 × 1012 and 4 × 1012/cm2). It can be seen that the mobility remains nearly independent of temperature from 2 to ~ 30 K and decreases with increasing temperature until ~ 150 K above which it again becomes nearly temperature-independent. We believe that the temperature dependence of mobility may be related to screening, structural phase transition and the SO phonons of STO.

The carrier density in graphene FET can be tuned by sweeping the gate-voltage which, however, depends on the dielectric constant of the gate-dielectric. Unlike the case in conventional SiO2/Si substrate where the dielectric constant (εr) is almost temperature-independent, the ‘εr’ of our STO thin film increases with decreasing temperature, even down to ~ 10 K (Figure 1c inset and Figure S2). This, in principle, should imply that the rate of carrier injection (i.e. α = dn/dVg) on to graphene should increase with decreasing temperature, down to the lowest temperature. The temperature dependence of the doping-rate (i.e. α vs T), shown in Figure 5a & 5b (for sample-1 & 2), shows an expected overlap with the ‘εr vs T’-trend at higher temperatures but surprisingly reveals a decline at low temperatures with a peak in the temperature range of 50–100 K. The observed behavior of resistivity (Figure 3), mobility (Figure 4) and the doping rate (α) (Figure 5) as a function of temperature suggest a possible disruption of the interface between graphene and STO in the temperature range of 50–100 K which is driven by the structural phase transition of STO at ~105 K.

The rate of carrier density injection (dn/dVg) as a function of temperature for the two different samples (1 in (a) and 2 in (b), respectively).

The solid circles are experimental data while the dashed lines are guide to eye. The solid lines represent the expected dn/dVg in proportion to the temperature-dependent dielectric constant of SrTiO3 thin film.

Discussion

The behavior of carrier transport in graphene has been variously attributed to resonant scatterers, long-range Coulomb impurities, acoustic and flexural phonons of graphene as well as the SO phonons of the underlying substrate. Unlike graphene on SiO2/Si, the transport through graphene on STO in our devices show unique characteristic features, such as, (a) hysteresis and saturation in carrier density (Figure 2), (b) slope-break in ‘ρ vs T’ in the temperature range of 50–100 K for all carrier densities (Figure 3), (c) drop in mobility by ~40% at temperatures above ~30 K (Figure 4) and (d) reduction in the rate-of-carrier-doping (α = dn/dVg) at temperatures below ~100 K (Figure 5). These features suggest that a model based on any single scattering mechanism cannot fully explain the transport data. We will discuss the role of each of the mechanisms below to understand the transport through graphene on STO.

Resonant and Coulomb impurity scattering

In the light of the findings by Couto et al.6 and the model later proposed by Das Sarma et al.27, both resonant and Coulomb impurity scattering mechanisms are at play in the transport through graphene on STO at temperatures below 50 K down to 250 mK. The resonant scattering mechanism alone cannot explain the transport at carrier densities near charge neutrality point. Therefore, at carrier densities close to charge neutrality point, Coulomb impurity scattering dominates. Couto et al. observed a sublinear density-dependent conductivity which remains temperature-independent thus attributing to a combination of resonant and Coulomb impurity scattering. Our transport data as well reveal a sublinear density-dependent conductivity (see Figure S5) thus implying the role played by the resonant and Coulomb impurity scatterers. Furthermore, we observe a drop in mobility with increasing temperature which may partly be attributed to screening of the Coulomb scattering under the influence of the temperature-dependent dielectric constant of STO. However, surprisingly, our experimental data reveal a clear temperature-dependent resistivity right from the lowest temperature (~2 K). One would expect such a behavior in STO-gated graphene devices, as also pointed by Couto et al., as STO has very low energy (3–5 meV) SO phonons. We, therefore, believe that in addition to the short-ranged and long-ranged scatterers, the SO phonons play crucial role in our transport data at high carrier densities, away from neutrality point.

Phonon scattering

In conventional SiO2 gated devices, the resistivity of mechanically exfoliated graphene shows linear-temperature-dependence with a universal slope of 0.1 ΩK−1 below ~150 K, which is independent of carrier density17. Such temperature dependence arises from scattering from acoustic phonon of graphene at low carrier densities and near charge neutrality point contributing a resistance change (Δρ) of up to ~30 Ω from ~4 K to 300 K. However, we do not see such a universal behavior in our devices suggesting an insignificant contribution from acoustic phonon scattering and indicating a clear role of flexural phonons and/or SO phonons.

At room temperature, STO is in cubic phase having SO phonons28 at 57 and 92 meV. However, STO undergoes a structural phase transition to tetragonal phase below ~105 K where low energy optical phonons are also excited due to the structural transition. The optical phonons of STO in low temperature phase as obtained from infrared and Raman spectroscopic studies29 are at ~5 and 20 meV in addition to the high energy phonons observed at room temperature. Therefore, at low temperatures it may be anticipated that the charge carriers in graphene will be scattered by the low energy optical phonons of STO as well as the charge impurities leading to an increase in resistivity right above ~10 K varying as  where gi is the coupling strength with the phonon ωi, n is the carrier density and αi ≅ 1 is the fitting parameter17. The phonon density of state undergoes a change as STO undergoes a structural phase transition from low temperature tetragonal to high temperature cubic phase at ~105 K. The lowest energy phonon in tetragonal phase is ~5 meV while that in cubic phase is ~20 meV. The ‘slope-break’ observed in our ‘ρ vs T’ in between 50–100 K as shown in Figure 3 may be, therefore, attributed to the change in distribution of phonon density of states across the structural phase transition of STO. Furthermore, the change in resistivity over the entire temperature range (2–300 K) and the ‘slope-break’ near 105 K also show carrier density dependence, i.e., the resistivity change and the ‘slope-break’ become higher for lower carrier densities and lower for higher carrier densities thus indicating an effect of charge impurity scattering in addition to the SO phonon scattering. We have simulated the resistivity as a function of temperature considering the dependence on carrier density and optical phonons of STO (shown in Figure 3d) as stated above:

where gi is the coupling strength with the phonon ωi, n is the carrier density and αi ≅ 1 is the fitting parameter17. The phonon density of state undergoes a change as STO undergoes a structural phase transition from low temperature tetragonal to high temperature cubic phase at ~105 K. The lowest energy phonon in tetragonal phase is ~5 meV while that in cubic phase is ~20 meV. The ‘slope-break’ observed in our ‘ρ vs T’ in between 50–100 K as shown in Figure 3 may be, therefore, attributed to the change in distribution of phonon density of states across the structural phase transition of STO. Furthermore, the change in resistivity over the entire temperature range (2–300 K) and the ‘slope-break’ near 105 K also show carrier density dependence, i.e., the resistivity change and the ‘slope-break’ become higher for lower carrier densities and lower for higher carrier densities thus indicating an effect of charge impurity scattering in addition to the SO phonon scattering. We have simulated the resistivity as a function of temperature considering the dependence on carrier density and optical phonons of STO (shown in Figure 3d) as stated above:  . The dashed (blue) lines correspond to the temperature dependence of resistivity below and above 105 K at a carrier density of n1 while at double the carrier density (2n1) the resistivity behaviors are represented by solid (green) lines. The net resistivity across 105 K (STO phase transition) is represented by the dashed (red)/solid (red) arrows. A similar ‘slope-break’ in ‘ρ vs T’ can be seen in our simulation across the structural phase transition of STO (105 K) (for further details see supplementary information). The simulated resistivity and the ‘slope-break’ are found to be higher for low carrier density (n1) and lower for high carrier density (2n1), manifesting the effect of impurity and SO phonon scattering17. Here we have assumed that below 105 K the dominant phonons29 are from 2–20 meV while above 105 K they are from 20–100 meV. Scattering from the optical phonons will suppress the carrier mobility as observed in exfoliated graphene on SiO2-gated devices17. We have observed a decrease in the carrier mobility as a function of temperature as shown in Figure 4 above ~30 K, thus further indicating SO phonon scattering being at play in addition to the impurity scattering. Furthermore, we observe a sub-linear carrier density-dependent conductivity at both high (300 K) and low (10 K) temperatures, as shown in Figure S5, suggesting that impurity scattering as well as SO phonon scattering play crucial role in determining the transport through graphene on STO in our devices.

. The dashed (blue) lines correspond to the temperature dependence of resistivity below and above 105 K at a carrier density of n1 while at double the carrier density (2n1) the resistivity behaviors are represented by solid (green) lines. The net resistivity across 105 K (STO phase transition) is represented by the dashed (red)/solid (red) arrows. A similar ‘slope-break’ in ‘ρ vs T’ can be seen in our simulation across the structural phase transition of STO (105 K) (for further details see supplementary information). The simulated resistivity and the ‘slope-break’ are found to be higher for low carrier density (n1) and lower for high carrier density (2n1), manifesting the effect of impurity and SO phonon scattering17. Here we have assumed that below 105 K the dominant phonons29 are from 2–20 meV while above 105 K they are from 20–100 meV. Scattering from the optical phonons will suppress the carrier mobility as observed in exfoliated graphene on SiO2-gated devices17. We have observed a decrease in the carrier mobility as a function of temperature as shown in Figure 4 above ~30 K, thus further indicating SO phonon scattering being at play in addition to the impurity scattering. Furthermore, we observe a sub-linear carrier density-dependent conductivity at both high (300 K) and low (10 K) temperatures, as shown in Figure S5, suggesting that impurity scattering as well as SO phonon scattering play crucial role in determining the transport through graphene on STO in our devices.

Reduction of doping-rate at low temperatures

As shown in Figure 1c (and also in Figure S2), the dielectric constant (εr) of our STO thin film increases with decreasing temperature, down to 10 K. It is, therefore, expected that the doping-rate (α = dn/dVg) will increase with lowering temperature, even down to the lowest temperatures. Surprisingly, we observe that the doping-rate declines as the temperature decreases below ~105 K. The decline in doping-rate cannot be attributed to Coulomb impurities as we do not observe any unusual change in impurity concentration with decreasing temperatures (Figure S6). Furthermore, it is to be noted that the ‘εr’ of STO is known to undergo a small decrease or saturation at low temperatures under high electric fields arising from electrostriction caused by alignment/rotation of tetragonal domains leading to a small decrease or saturation of total available charge for injection22,30. However, we observe a similar ‘α vs T’ at various electric fields ranging from ~0 kVcm−1 to 150 kVcm−1 thus ruling out any role of the electric field-induced decrease in dielectric constant (see Figure S7 in supplementary information). The origin of this decline, therefore, is not very clear at present. However, the drop in doping-rate may be due to a possible disruption at the graphene-substrate interface. In a recent experimental report31 on x-ray reflectivity, x-ray diffraction and atomic force microscopy studies of STO single crystal presents the observation of surface-rumpling (surface becomes wavy) of more-than-micron length scales upon cooling below 105 K which is correlated with the structural phase transition. At the same time, the roughness gradually increases up to about 200% as the temperature decreases well below 105 K which is associated with a severe degradation of the mosaic quality of the substrate-surface. These changes are notably reversible upon heating back to room temperature. It is possible that the unusual behavior of ‘α vs T’ in our data may arise due to a partial suspension of graphene in nanoscale dimensions owing to an increase in surface roughness at temperatures below STO structural phase transition. Further experimental evidences probing the morphology at the Graphene-STO interface at low temperatures will be necessary to understand the anomalous transport and is beyond the scope of this work.

Furthermore, other important observations are the hysteresis of graphene-resistance (Figure 2b) and carrier density as well as saturation of carrier density (~12 × 1012 cm−2) beyond an applied electric field of ~150 kVcm−1, i.e., a gate-voltage of ~5 V (shown in Figure 2c). In high quality SiO2 on silicon one can observe trapped charge states of the order of ~1011 cm−2 while on the STO surface this hysteresis translates to a trapped charge state of the order of ~1012 cm−2. Therefore, the possible candidates that are likely to contribute to the observed hysteresis are the trapped charge states and surface dipoles23 of STO. These may pre-screen the field-induced surface polarization change leading to the observed hysteresis in graphene-resistance as well as carrier density (as shown in Figure 2b&c), similar to that seen in carbon nanotube and graphene FETs gated by SiO232 and ferroelectrics21,33. However, the interfacial impurities should not lead to the observed ‘slope-break’ in resistivity. We find that the total charge impurity density at the interface remains nearly independent of temperature (see Figure S6) with minimal change thus suggesting that the structural phase transition of STO does not have any significant effect on the charge traps, STO surface dipoles and the adsorbates at the interface. We, therefore, logically rule out any significant role of these interfacial impurities in the observed ‘slope break’ in resistivity and the other anomalies (Figures 3, 4, & 5).

Conclusion

In conclusion, we have observed an anomalous ‘slope-break’ in the temperature-dependent resistivity of CVD-graphene on STO/Nb:STO substrates in the range of 50–100 K, concomitant with a decrease in the gate induced field-effect at lower temperatures. We further observe temperature-dependent mobility dropping at temperatures above ~30 K. These anomalies may be attributed to a change in the SO phonon scattering as a consequence of the structural phase transition of STO at 105 K. In addition, at low temperatures STO surface is known to become significantly rumpled with a gradual increase in roughness31 which may lead to a partial detachment of graphene from the substrate-surface thus reducing the gate-induced field-effect at low temperatures. However, further experimental evidences will be necessary to understand the morphology change-induced effects in graphene transport. We believe that our experimental observations demonstrate the sensitivity of electronic properties of graphene to structural phase transitions of the underlying substrate and its changing morphology and motivate further experimental and theoretical studies.

Methods

Substrate preparation

Thin films of epitaxial STO (thickness ~300 nm ± 10%) have been grown using Pulsed Laser Deposition (PLD) technique on Nb (0.05%):STO (100) single crystal substrates at an oxygen partial-pressure of 100 mTorr and substrate-temperature of 700°C at a repetition rate of 5 Hz following a deposition at 1 Hz to improve the surface roughness down to less than 1 nm. Subsequently, the films were annealed at 400°C in oxygen ambience at a pressure of 500 Torr for 1 hour to minimize oxygen vacancy. The films have been characterized using x-ray diffraction and atomic force microscopy followed by measurement of the dielectric constant using a Ferroelectric tester (Radiant Technologies). The films were found to have a dielectric constant of about 300 at room temperature.

Device fabrication and measurement

CVD-graphene grown on Cu substrates has been transferred on to the STO/Nb:STO substrates using the standard wet process where Cu is etched away using ammonium persulfate solution7. A two-step electron beam lithography, oxygen-plasma etching and thermal evaporation techniques have been used to fabricate devices in standard Hall-bar geometry. The resistance of the graphene channel has been measured at low frequency (~13 Hz) using SRS-380 lock-in amplifier while the gate-voltage was swept using Keithley-6430 Source Meter. The samples were first cooled down to the lowest temperature without any applied gate voltage and then were gate-swept (from 0 V to +5 V, then from +5 V to −5 V and then return to 0 V, at a step of 0.04 V) at every fixed temperatures from 2 K to 300 K. The maximum voltage during gate-sweep was kept at ± 5 V as otherwise the carrier density saturates at higher gate voltages.

References

Geim, A. K. Graphene: Status and Prospects. Science 324, 1530–1534 (2009).

Castro Neto, A. H., Guinea, F., Peres, N. M. R., Novoselov, K. S. & Geim, A. K. The electronic properties of graphene. Rev. Mod. Phys. 81, 109–162 (2009).

Bonaccorso, F., Sun, Z., Hasan, T. & Ferrari, A. C. Graphene photonics and optoelectronics. Nat. Photonic; 4, 611–622 (2010).

Zheng, Y. et al. Gate-controlled nonvolatile graphene-ferroelectric memory. Appl. Phys. Lett. 94, 163505 (2009).

Gannett, W. et al. Boron nitride substrates for high mobility chemical vapor deposited graphene. Appl. Phys. Lett. 98, 242105 (2011).

Couto, N. J. G., Sacépé, B. & Morpurgo, A. F. Transport through Graphene on SrTiO3 . Phys. Rev. Lett. 107, 225501 (2011).

Bae, S. et al. Roll-to-roll production of 30-inch graphene films for transparent electrodes. Nat. Nanotechnol. 5, 574–578 (2010).

Zheng, Y. et al. Graphene Field-Effect Transistors with Ferroelectric Gating. Phys. Rev. Lett. 105, 166602 (2010).

Zheng, Y. et al. Wafer-scale graphene/ferroelectric hybrid devices for low-voltage electronics. Europhys. Lett. 93, 17002 (2011).

Pereira, V. M. & Castro Neto, A. H. Strain Engineering of Graphene's Electronic Structure. Phys. Rev. Lett. 103, 046801 (2009).

Low, T., Guinea, F. & Katsnelson, M. I. Gaps tunable by electrostatic gates in strained graphene. Phys. Rev. B 83, 195436 (2011).

Pathak, S., Shenoy, V. B. & Baskaran, G. Possible high-temperature superconducting state with a d+id pairing symmetry in doped graphene. Phys. Rev. B 81, 085431 (2010).

Profeta, G., Calandra, M. & Mauri, F. Phonon-mediated superconductivity in grapheneby lithium deposition. Nature Phys. 8, 131–134 (2012).

Ni, G.-X. et al. Graphene Ferroelectric Hybrid Structure for Flexible Transparent Electrodes. ACSNano 6, 3935–3942 (2012).

Pachoud, A., Jaiswal, M., Ang, P. K., Loh, K. P. & Oezyilmaz, B. Graphene transport at high carrier densities using a polymer electrolyte gate. Europhys. Lett. 92, 27001 (2010).

Hollander, M. J. et al. Enhanced Transport and Transistor Performance with Oxide Seeded High-κ Gate Dielectrics on Wafer-Scale Epitaxial Graphene. Nano Lett. 11, 3601–3607 (2011).

Chen, J. H., Jang, C., Xiao, S., Ishigami, M. & Fuhrer, M. S. Intrinsic and extrinsic performance limits of graphene devices on SiO2 . Nature Nanotechnol. 3, 206–209 (2008).

Nam, Y., Lindvall, N., Sun, J., Park, Y. W. & Yurgens, A. Graphene p–n–p junctions controlled by local gates made of naturally oxidized thin aluminium films. Carbon 50, 1987–1992 (2012).

Oliveira Jr, M. H. et al. Mono- and few-layer nanocrystalline graphene grown on Al2O3(0001) by molecular beam epitaxy. Carbon 56, 339–350 (2013).

Zou, K., Hong, X., Keefer, D. & Zhu, J. Deposition of High-Quality HfO2 on Graphene and the Effect of Remote Oxide Phonon Scattering. Phys. Rev. Lett. 105, 126601 (2010).

Paruch, P., Posadas, A. B., Dawber, M., Ahn, C. H. & McEuen, P. L. Polarization switching using single-walled carbon nanotubes grown on epitaxial ferroelectric thin films. Appl. Phys. Lett. 93, 132901 (2008).

Hong, X. et al. Unusual resistance hysteresis in n-layer graphene field effect transistors fabricated on ferroelectric Pb(Zr0.2Ti0.8)O3 . Appl. Phys. Lett. 97, 033114 (2010).

Tian, F., Aniruddha, K., Huili, X. & Debdeep, J. Carrier statistics and quantum capacitance of graphene sheets and ribbons. Appl. Phys. Lett. 91, 092109 (2007).

Ryota, I., Kosuke, N., Tomonori, N. & Akira, T. The density of states of graphene underneath a metal electrode and its correlation with the contact resistivity. Appl. Phys. Lett. 103, 033514 (2013).

Sachs, R., Lin, Z. & Shi, J. Ferroelectric-like SrTiO3 surface dipoles probed by graphene. arXiv: CondMat/1401.2222.

Heo, J. et al. Non-monotonic temperature-dependent transport in graphene grown by chemical vapor deposition. Phys. Rev. B 84, 035421 (2011).

Das Sarma, S. & Li, Q. Graphene on SrTiO3 . Sol. Stat. Comm. 152, 1795–1799 (2012).

Baden, A. D., Cox, P. A., Egdell, R. G., Orchard, A. F. & Willmer, R. J. D. Observation of surface optical phonons on SrTiO3(100). J. Phys. C: Solid State Phys. 14, L1081–L1084 (1981).

Petzelt, J. et al. Dielectric, infrared and Raman response of undoped SrTiO3 ceramics: Evidence of polar grain boundaries. Phys. Rev. B 64, 184111 (2001).

Ang, C., Yu, Z., Cross, L. E., Guo, R. & Bhalla, A. S. Dielectric relaxation and conduction in SrTiO3 thin films under dc bias. Appl. Phys. Lett. 79, 818 (2001).

Singh, S., Chien, T. Y., Guest, J. R. & Fitzsimmons, M. R. Correlation between surface rumpling and structural phase transformation in SrTiO3 . Phys. Rev. B 85, 115450 (2012).

Ochoaa, H., Castro, E. V., Katsnelson, M. I. & Guinea, F. Scattering by flexural phonons in suspended graphene under back gate induced strain. Physica E 44, 963–966 (2012).

Kim, W. et al. Hysteresis Caused by Water Molecules in Carbon Nanotube Field-Effect Transistors. Nano Letters 3, 193–198 (2003).

Acknowledgements

We would like to acknowledge for financial support from NRF-CRP “Tailoring Oxide Electronics by Atomic Control” Grant No. NRF2008NRFCRP002-024, CRP Award No. NRF-CRP9-2011-3, NUS cross-faculty grant, FRC, BMBF, the Singapore National Research Foundation [grants NRF-RF2008-07, NRF-CRP(R-144-000-295-281), SMF-NUS Research Horizon (Phase II), NUS-Young Investor Award (R144-000-283-101), IMRE/10-1C0109 and NUS/SMF], U.S. Office of Naval Research (ONR and ONR Global) and the National Research Foundation of Korea (NRF) funded by the Ministry of Education, Science and Technology (Global Research Lab. 20110021972, 2011K000615, 20110017587, 20110006268 and Global Frontier Research Program 20110031629).

Author information

Authors and Affiliations

Contributions

S.S. & O.K. designed the experiments, prepared the samples and performed the AFM, ferroelectric, Raman and transport measurements. A.S. & A.A. assisted in PLD, XRD & AFM. characterizations. M.J., A.P., C.T. & J.B. assisted in data analysis. J.B. fabricated and measured the SiO2/Si based device. Insight of the physical mechanism was provided by S.S., O.K., M.J., A.P., T.V. & B.O. The manuscript was prepared by S.S., O.K., M.J., T.V. & B.O. with assistance from B.H. & J.A. All authors reviewed the manuscript.

Ethics declarations

Competing interests

The authors declare no competing financial interests.

Electronic supplementary material

Supplementary Information

Supplementary info

Rights and permissions

This work is licensed under a Creative Commons Attribution-NonCommercial-NoDerivs 4.0 International License. The images or other third party material in this article are included in the article's Creative Commons license, unless indicated otherwise in the credit line; if the material is not included under the Creative Commons license, users will need to obtain permission from the license holder in order to reproduce the material. To view a copy of this license, visit http://creativecommons.org/licenses/by-nc-nd/4.0/

About this article

Cite this article

Saha, S., Kahya, O., Jaiswal, M. et al. Unconventional Transport through Graphene on SrTiO3: A Plausible Effect of SrTiO3 Phase-Transitions. Sci Rep 4, 6173 (2014). https://doi.org/10.1038/srep06173

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/srep06173

This article is cited by

-

Out-of-plane interface dipoles and anti-hysteresis in graphene-strontium titanate hybrid transistor

npj 2D Materials and Applications (2018)

-

Growth of Epitaxial Oxide Thin Films on Graphene

Scientific Reports (2016)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.