Abstract

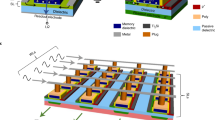

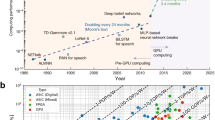

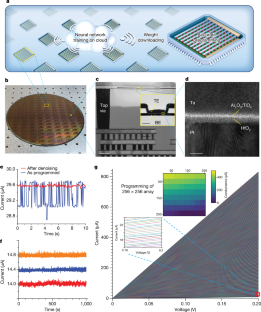

Neural networks based on memristive devices1,2,3 have the ability to improve throughput and energy efficiency for machine learning4,5 and artificial intelligence6, especially in edge applications7,8,9,10,11,12,13,14,15,16,17,18,19,20,21. Because training a neural network model from scratch is costly in terms of hardware resources, time and energy, it is impractical to do it individually on billions of memristive neural networks distributed at the edge. A practical approach would be to download the synaptic weights obtained from the cloud training and program them directly into memristors for the commercialization of edge applications. Some post-tuning in memristor conductance could be done afterwards or during applications to adapt to specific situations. Therefore, in neural network applications, memristors require high-precision programmability to guarantee uniform and accurate performance across a large number of memristive networks22,23,24,25,26,27,28. This requires many distinguishable conductance levels on each memristive device, not only laboratory-made devices but also devices fabricated in factories. Analog memristors with many conductance states also benefit other applications, such as neural network training, scientific computing and even ‘mortal computing’25,29,30. Here we report 2,048 conductance levels achieved with memristors in fully integrated chips with 256 × 256 memristor arrays monolithically integrated on complementary metal–oxide–semiconductor (CMOS) circuits in a commercial foundry. We have identified the underlying physics that previously limited the number of conductance levels that could be achieved in memristors and developed electrical operation protocols to avoid such limitations. These results provide insights into the fundamental understanding of the microscopic picture of memristive switching as well as approaches to enable high-precision memristors for various applications.

This is a preview of subscription content, access via your institution

Access options

Access Nature and 54 other Nature Portfolio journals

Get Nature+, our best-value online-access subscription

$29.99 / 30 days

cancel any time

Subscribe to this journal

Receive 51 print issues and online access

$199.00 per year

only $3.90 per issue

Buy this article

- Purchase on Springer Link

- Instant access to full article PDF

Prices may be subject to local taxes which are calculated during checkout

Similar content being viewed by others

Data availability

The data that support the findings of this study are available from the corresponding author upon reasonable request.

Code availability

The algorithm for memristor high-precision programming is included in the Supplementary Information. The code for physical modelling and simulations is available at GitHub (https://github.com/htang113/HfO2-memristor-denoise/tree/main).

References

Chua, L. O. Memristor—the missing circuit element. IEEE Trans. Circuit Theory 18, 507–519 (1971).

Valov, I., Waser, R., Jameson, J. R. & Kozicki, M. N. Electrochemical metallization memories—fundamentals, applications, prospects. Nanotechnology 22, 254003 (2011).

Yang, Y. & Huang, R. Probing memristive switching in nanoionic devices. Nat. Electron. 1, 274–287 (2018).

Wen, W., Wu, C., Wang, Y., Chen, Y. & Li, H. Learning structured sparsity in deep neural networks. In Advances in Neural Information Processing Systems 29 (eds Lee, D. D., et al.), 2082–2090 (Curan Associates, 2016).

Wan, W. et al. A compute-in-memory chip based on resistive random-access memory. Nature 608, 504–512 (2022).

Kumar, S., Wang, X., Strachan, J. P., Yang, Y. & Lu, W. D. Dynamical memristors for higher-complexity neuromorphic computing.Nat. Rev. Mater. 7, 575–591 (2022).

Xue, C.-X. et al. A CMOS-integrated compute-in-memory macro based on resistive random-access memory for AI edge devices. Nat. Electron. 4, 81–90 (2021).

Lanza, M. et al. Memristive technologies for data storage, computation, encryption, and radio-frequency communication. Science 376, eabj9979 (2022).

Yao, P. et al. Fully hardware-implemented memristor convolutional neural network. Nature 577, 641–646 (2020).

Zhang, W. et al. Neuro-inspired computing chips. Nat. Electron. 3, 371–382 (2020).

Ielmini, D. & Wong, H.-S. P. In-memory computing with resistive switching devices. Nat. Electron. 1, 333–343 (2018).

Zidan, M. A., Strachan, J. P. & Lu, W. D. The future of electronics based on memristive systems. Nat. Electron. 1, 22–29 (2018).

Yu, S. Neuro-inspired computing with emerging nonvolatile memorys. Proc. IEEE 106, 260–285 (2018).

Jung, S. et al. A crossbar array of magnetoresistive memory devices for in-memory computing. Nature 601, 211–216 (2022).

Sangwan, V. K. & Hersam, M. C. Neuromorphic nanoelectronic materials. Nat. Nanotechnol. 15, 517–528 (2020).

Burr, G. W. A role for analogue memory in AI hardware. Nat. Mach. Intell. 1, 10–11 (2019).

Chen, S. et al. Wafer-scale integration of two-dimensional materials in high-density memristive crossbar arrays for artificial neural networks. Nat. Electron. 3, 638–645 (2020).

Fuller, E. J. et al. Parallel programming of an ionic floating-gate memory array for scalable neuromorphic computing. Science 364, 570–574 (2019).

Choi, C. et al. Reconfigurable heterogeneous integration using stackable chips with embedded artificial intelligence.Nat. Electron. 5, 386–393 (2022).

Lim, D.-H. et al. Spontaneous sparse learning for PCM-based memristor neural networks. Nat. Commun. 12, 319 (2021).

Xu, X. et al. Scaling for edge inference of deep neural networks. Nat. Electron. 1, 216–222 (2018).

Sun, Y. et al. A Ti/AlOx/TaOx/Pt analog synapse for memristive neural network. IEEE Electron Device Lett. 39, 1298–1301 (2018).

Stathopoulos, S. et al. Multibit memory operation of metal-oxide bi-layer memristors. Sci. Rep. 7, 17532 (2017).

Kim, H., Mahmoodi, M. R., Nili, H. & Strukov, D. B. 4K-memristor analog-grade passive crossbar circuit. Nat. Commun. 12, 5198 (2021).

Zidan, M. A. et al. A general memristor-based partial differential equation solver. Nat. Electron. 1, 411–420 (2018).

Li, C. et al. Analogue signal and image processing with large memristor crossbars. Nat. Electron. 1, 52–59 (2018).

Mackin, C. et al. Optimised weight programming for analogue memory-based deep neural networks. Nat. Commun. 13, 3765 (2022).

Choi, S. et al. SiGe epitaxial memory for neuromorphic computing with reproducible high performance based on engineered dislocations. Nat. Mater. 17, 335–340 (2018).

Yao, P. et al. Face classification using electronic synapses. Nat. Commun. 8, 15199 (2017).

Hinton, G. The forward–forward algorithm: some preliminary investigations. Preprint at https://arxiv.org/abs/2212.13345 (2022).

Yan, Z., Hu, X. S. & Shi, Y. SWIM: Selective write-verify for computing-in-memory neural accelerators. Preprint at https://arxiv.org/abs/2202.08395 (2022).

Chen, B. et al. A memristor-based hybrid analog-digital computing platform for mobile robotics. Sci. Robot. 5, eabb6938 (2020).

Choi, S., Yang, Y. & Lu, W. Random telegraph noise and resistance switching analysis of oxide based resistive memory. Nanoscale 6, 400–404 (2014).

Ielmini, D., Nardi, F. & Cagli, C. Resistance-dependent amplitude of random telegraph-signal noise in resistive switching memories. Appl. Phys. Lett. 96, 053503 (2010).

Puglisi, F. M., Pavan, P., Padovani, A., Larcher, L. & Bersuker, G. Random telegraph signal noise properties of HfOx RRAM in high resistive state. In 2012 Proc. European Solid-State Device Research Conference (ESSDERC), 274–277 (IEEE, 2012).

Lee, J.-K. et al. Extraction of trap location and energy from random telegraph noise in amorphous TiOx resistance random access memories. Appl. Phys. Lett. 98, 143502 (2011).

Puglisi, F. M., Padovani, A., Larcher, L. & Pavan, P. Random telegraph noise: measurement, data analysis, and interpretation. In 2017 IEEE 24th International Symposium on the Physical and Failure Analysis of Integrated Circuits (IPFA), 1–9 (IEEE, 2017).

Puglisi, F. M., Zagni, N., Larcher, L. & Pavan, P. Random telegraph noise in resistive random access memories: compact modeling and advanced circuit design. IEEE Trans. Electron Devices 65, 2964–2972 (2018).

Yang, Y. et al. Probing nanoscale oxygen ion motion in memristive systems. Nat. Commun. 8, 15173 (2017).

Puglisi, F. M. Noise in Nanoscale Semiconductor Devices (ed. Grassor, T.), 87–133 (Springer, 2020).

Hui, F. & Lanza, M. Scanning probe microscopy for advanced nanoelectronics. Nat. Electron. 2, 221–229 (2019).

Celano, U. et al. Three-dimensional observation of the conductive filament in nanoscaled resistive memory devices. Nano Lett. 14, 2401–2406 (2014).

Du, H. et al. Nanosized conducting filaments formed by atomic-scale defects in redox-based resistive switching memories. Chem. Mater. 29, 3164–3173 (2017).

Puglisi, F. M., Larcher, L., Padovani, A. & Pavan, P. A complete statistical investigation of RTN in HfO2-based RRAM in high resistive state. IEEE Trans. Electron Devices 62, 2606–2613 (2015).

Ambrogio, S. et al. Statistical fluctuations in HfOx resistive-switching memory: part II—random telegraph noise. IEEE Trans. Electron Devices 61, 2920–2927 (2014).

Becker, T. et al. An electrical model for trap coupling effects on random telegraph noise. IEEE Electron Device Lett. 41, 1596–1599 (2020).

Brivio, S., Frascaroli, J., Covi, E. & Spiga, S. Stimulated ionic telegraph noise in filamentary memristive devices. Sci. Rep. 9, 6310 (2019).

Miao, F. et al. Anatomy of a nanoscale conduction channel reveals the mechanism of a high‐performance memristor. Adv. Mater. 23, 5633–5640 (2011).

Zhou, Y. et al. The effects of oxygen vacancies on ferroelectric phase transition of HfO2-based thin film from first-principle. Comput. Mater. Sci. 167, 143–150 (2019).

Kresse, G. & Joubert, D. From ultrasoft pseudopotentials to the projector augmented-wave method. Phys. Rev. B 59, 1758–1775 (1999).

Kresse, G. & Furthmüller, J. Efficient iterative schemes for ab initio total-energy calculations using a plane-wave basis set. Phys. Rev. B 54, 11169–11186 (1996).

Perdew, J. P., Burke, K. & Ernzerhof, M. Generalized gradient approximation made simple. Phys. Rev. Lett. 77, 3865–3868 (1996).

Monkhorst, H. J. & Pack, J. D. Special points for Brillouin-zone integrations. Phys. Rev. B 13, 5188–5192 (1976).

Lyons, J. L., Janotti, A. & Van de Walle, C. G. The role of oxygen-related defects and hydrogen impurities in HfO2 and ZrO2. Microelectron. Eng. 88, 1452–1456 (2011).

Monaghan, S., Hurley, P. K., Cherkaoui, K., Negara, M. A. & Schenk, A. Determination of electron effective mass and electron affinity in HfO2 using MOS and MOSFET structures. Solid State Electron. 53, 438–444 (2009).

Zhao, X. & Vanderbilt, D. First-principles study of structural, vibrational, and lattice dielectric properties of hafnium oxide. Phys. Rev. B 65, 233106 (2002).

Acknowledgements

J.J.Y., W.S. and Y.Z. were partially supported by a subcontract (GR1055585 53-4502-0003) from the University of Massachusetts Amherst, with the sponsor being TetraMem. R.M., Q.X. and J.J.Y. were partially supported by the Air Force Office of Scientific Research through the Multidisciplinary University Research Initiative programme under contract no. FA9550-19-1-0213, the US Air Force Research Laboratory (prime contract nos. FA8650-21-C-5405 and FA8750-22-1-0501) and by the National Science Foundation under contract no. 2023752. J.W. and H.W. acknowledge the support by the Army Research Office (grant no. W911NF2120128) and the National Science Foundation (grant no. CMMI-2240407). H.T. and J.L. acknowledge the support by the National Science Foundation (grant no. CMMI-1922206). We thank A. Tan for proofreading the manuscript.

Author information

Authors and Affiliations

Contributions

J.J.Y. and M.R. conceived the concept. J.J.Y. and Q.X. supervised the entire project. J.J.Y., M.R., Q.X., H.T., J.W. and W.S. designed the experiments and simulations. M.R., M.Z., R.M. and H.J. fabricated the devices. M.R., W.S., Y.Z., B.C., X.J. and Z.W. carried out the electrical measurements. H.T., M.R. and J.L. designed and carried out the simulation. J.W., M.R., H.L., H.-Y.C. and H.W. designed and carried out the C-AFM studies. W.Y., F.K., F.Y., Z.W., M.W., M.H., Q.X., N.G. and J.J.Y. helped with experiments and data analysis. M.R., H.T. and J.J.Y. wrote the paper. All authors discussed the results and implications and commented on the manuscript at all stages.

Corresponding author

Ethics declarations

Competing interests

J.J.Y. and Q.X. are co-founders and paid consultants of TetraMem.

Peer review

Peer review information

Nature thanks Yiyu Shi, Ilia Valov and Yuchao Yang for their contribution to the peer review of this work. Peer reviewer reports are available.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Supplementary Information

This file contains Supplementary Figs. 1–15, a discussion on the probable RTN-responsible defect and an analysis of electronic and atomic noise effects.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Rao, M., Tang, H., Wu, J. et al. Thousands of conductance levels in memristors integrated on CMOS. Nature 615, 823–829 (2023). https://doi.org/10.1038/s41586-023-05759-5

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1038/s41586-023-05759-5

This article is cited by

-

Memristor-based hardware accelerators for artificial intelligence

Nature Reviews Electrical Engineering (2024)

-

Local prediction-learning in high-dimensional spaces enables neural networks to plan

Nature Communications (2024)

-

Multi-level, forming and filament free, bulk switching trilayer RRAM for neuromorphic computing at the edge

Nature Communications (2024)

-

Solution-processed memristors: performance and reliability

Nature Reviews Materials (2024)

-

Transforming edge hardware with in situ learning features

Nature Reviews Electrical Engineering (2024)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.